Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFI

| Becano                     |                                                                                 |

|----------------------------|---------------------------------------------------------------------------------|

| Product Status             | Active                                                                          |

| Core Processor             | PIC                                                                             |

| Core Size                  | 16-Bit                                                                          |

| Speed                      | 40 MIPs                                                                         |

| Connectivity               | CANbus, I <sup>2</sup> C, IrDA, LINbus, SPI, UART/USART                         |

| Peripherals                | Brown-out Detect/Reset, DMA, POR, PWM, WDT                                      |

| Number of I/O              | 85                                                                              |

| Program Memory Size        | 128KB (43K x 24)                                                                |

| Program Memory Type        | FLASH                                                                           |

| EEPROM Size                | -                                                                               |

| RAM Size                   | 8K x 8                                                                          |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 3.6V                                                                       |

| Data Converters            | A/D 32x10b/12b                                                                  |

| Oscillator Type            | Internal                                                                        |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                               |

| Mounting Type              | Surface Mount                                                                   |

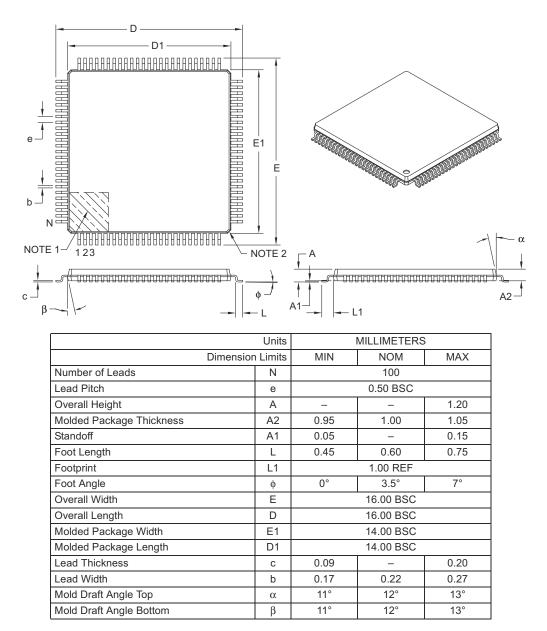

| Package / Case             | 100-TQFP                                                                        |

| Supplier Device Package    | 100-TQFP (14x14)                                                                |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic24hj128gp510a-i-pf |

|                            |                                                                                 |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

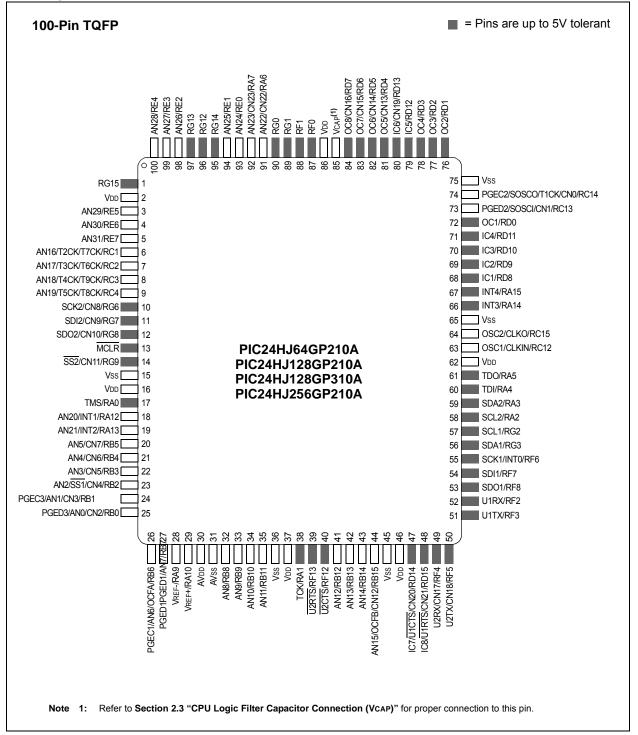

#### Pin Diagrams (Continued)

#### 2.5 ICSP Pins

The PGECx and PGEDx pins are used for In-Circuit Serial Programming<sup>TM</sup> (ICSP<sup>TM</sup>) and debugging purposes. It is recommended to keep the trace length between the ICSP connector and the ICSP pins on the device as short as possible. If the ICSP connector is expected to experience an ESD event, a series resistor is recommended, with the value in the range of a few tens of Ohms, not to exceed 100 Ohms.

Pull-up resistors, series diodes, and capacitors on the PGECx and PGEDx pins are not recommended as they will interfere with the programmer/debugger communications to the device. If such discrete components are an application requirement, they should be removed from the circuit during programming and debugging. Alternatively, refer to the AC/DC characteristics and requirements timing information in the "dsPIC33F/PIC24H Flash Programming Specification" (DS70152) for information on capacitive loading limits and pin input voltage high (VIH) and input low (VIL) requirements.

Ensure that the "Communication Channel Select" (i.e., PGECx/PGEDx pins) programmed into the device matches the physical connections for the ICSP to MPLAB<sup>®</sup> ICD 3 or MPLAB REAL ICE<sup>™</sup>.

For more information on ICD 3 and REAL ICE connection requirements, refer to the following documents that are available on the Microchip web site.

- "Using MPLAB<sup>®</sup> ICD 3 In-Circuit Debugger" (poster) DS51765

- "MPLAB<sup>®</sup> ICD 3 Design Advisory" DS51764

- "MPLAB<sup>®</sup> REAL ICE<sup>™</sup> In-Circuit Emulator User's Guide" DS51616

- *"Using MPLAB<sup>®</sup> REAL ICE™"* (poster) DS51749

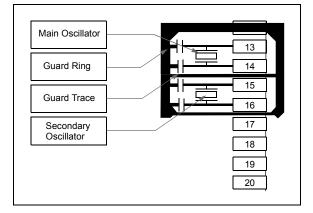

#### 2.6 External Oscillator Pins

Many MCUs have options for at least two oscillators: a high-frequency primary oscillator and a low-frequency secondary oscillator (refer to **Section 9.0 "Oscillator Configuration"** for details).

The oscillator circuit should be placed on the same side of the board as the device. Also, place the oscillator circuit close to the respective oscillator pins, not exceeding one-half inch (12 mm) distance between them. The load capacitors should be placed next to the oscillator itself, on the same side of the board. Use a grounded copper pour around the oscillator circuit to isolate them from surrounding circuits. The grounded copper pour should be routed directly to the MCU ground. Do not run any signal traces or power traces inside the ground pour. Also, if using a two-sided board, avoid any traces on the other side of the board where the crystal is placed. A suggested layout is shown in Figure 2-3.

#### FIGURE 2-3: SUGGESTED PLACEMENT OF THE OSCILLATOR CIRCUIT

#### 3.4 Arithmetic Logic Unit (ALU)

The PIC24HJXXXGPX06A/X08A/X10A ALU is 16 bits wide and is capable of addition, subtraction, bit shifts and logic operations. Unless otherwise mentioned, arithmetic operations are 2's complement in nature. Depending on the operation, the ALU may affect the values of the Carry (C), Zero (Z), Negative (N), Overflow (OV) and Digit Carry (DC) Status bits in the <u>SR register</u>. The <u>C and DC</u> Status bits operate as Borrow and Digit Borrow bits, respectively, for subtraction operations.

The ALU can perform 8-bit or 16-bit operations, depending on the mode of the instruction that is used. Data for the ALU operation can come from the W register array, or data memory, depending on the addressing mode of the instruction. Likewise, output data from the ALU can be written to the W register array or a data memory location.

Refer to the "16-bit MCU and DSC Programmer's Reference Manual" (DS70157) for information on the SR bits affected by each instruction.

The PIC24HJXXXGPX06A/X08A/X10A CPU incorporates hardware support for both multiplication and division. This includes a dedicated hardware multiplier and support hardware for 16-bit divisor division.

#### 3.4.1 MULTIPLIER

Using the high-speed 17-bit x 17-bit multiplier, the ALU supports unsigned, signed or mixed-sign operation in several multiplication modes:

- 16-bit x 16-bit signed

- 16-bit x 16-bit unsigned

- 16-bit signed x 5-bit (literal) unsigned

- 16-bit unsigned x 16-bit unsigned

- 16-bit unsigned x 5-bit (literal) unsigned

- 16-bit unsigned x 16-bit signed

- 8-bit unsigned x 8-bit unsigned

#### 3.4.2 DIVIDER

The divide block supports 32-bit/16-bit and 16-bit/16-bit signed and unsigned integer divide operations with the following data sizes:

- 32-bit signed/16-bit signed divide

- 32-bit unsigned/16-bit unsigned divide

- 16-bit signed/16-bit signed divide

- 16-bit unsigned/16-bit unsigned divide

The quotient for all divide instructions ends up in W0 and the remainder in W1. Sixteen-bit signed and unsigned DIV instructions can specify any W register for both the 16-bit divisor (Wn) and any W register (aligned) pair (W(m + 1):Wm) for the 32-bit dividend. The divide algorithm takes one cycle per bit of divisor, so both 32-bit/16-bit and 16-bit/16-bit instructions take the same number of cycles to execute.

#### 3.4.3 MULTI-BIT DATA SHIFTER

The multi-bit data shifter is capable of performing up to 16-bit arithmetic or logic right shifts, or up to 16-bit left shifts in a single cycle. The source can be either a working register or a memory location.

The shifter requires a signed binary value to determine both the magnitude (number of bits) and direction of the shift operation. A positive value shifts the operand right. A negative value shifts the operand left. A value of '0' does not modify the operand.

#### TABLE 4-17: DMA REGISTER MAP

| File Name | -17:<br>Addr | Bit 15 | Bit 14    | Bit 13 | Bit 12 | Bit 11 | Bit 10 | Bit 9 | Bit 8 | Bit 7    | Bit 6 | Bit 5 | Bit 4  | Bit 3     | Bit 2 | Bit 1 | Bit 0 | All    |

|-----------|--------------|--------|-----------|--------|--------|--------|--------|-------|-------|----------|-------|-------|--------|-----------|-------|-------|-------|--------|

|           |              |        |           |        |        |        |        |       |       |          |       |       |        |           |       |       |       | Resets |

| DMA0CON   | 0380         | CHEN   | SIZE      | DIR    | HALF   | NULLW  | _      |       |       |          | _     | AMOD  |        | —         | —     | MODE  | <1:0> | 0000   |

| DMA0REQ   | 0382         | FORCE  |           |        |        |        |        |       |       |          |       | 0000  |        |           |       |       |       |        |

| DMA0STA   | 0384         |        |           |        |        |        |        |       |       | TA<15:0> |       |       |        |           |       |       |       | 0000   |

| DMA0STB   | 0386         |        |           |        |        |        |        |       |       | TB<15:0> |       |       |        |           |       |       |       | 0000   |

| DMA0PAD   | 0388         |        |           |        |        |        |        | r     | P     | AD<15:0> |       |       |        |           |       |       |       | 0000   |

| DMA0CNT   | 038A         | _      |           | —      | —      | —      | —      |       |       |          |       |       | <9:0>  | -         |       | r     |       | 0000   |

| DMA1CON   | 038C         | CHEN   | SIZE      | DIR    | HALF   | NULLW  | _      |       |       | _        |       | AMOD  |        | _         | —     | MODE  | <1:0> | 0000   |

| DMA1REQ   | 038E         | FORCE  | —         | —      |        | —      | —      |       |       | —        |       |       | I      | RQSEL<6:0 | >     |       |       | 0000   |

| DMA1STA   | 0390         |        | STA<15:0> |        |        |        |        |       |       |          |       |       |        |           | 0000  |       |       |        |

| DMA1STB   | 0392         |        |           |        |        |        |        |       | S     | TB<15:0> |       |       |        |           |       |       |       | 0000   |

| DMA1PAD   | 0394         |        |           |        |        |        |        | 1     | P     | AD<15:0> |       |       |        |           |       |       |       | 0000   |

| DMA1CNT   | 0396         | —      | —         | —      | —      | —      | —      |       |       |          |       | CNT   | <9:0>  | T         |       |       |       | 0000   |

| DMA2CON   | 0398         | CHEN   | SIZE      | DIR    | HALF   | NULLW  | _      |       |       | _        | _     | AMOD  | E<1:0> | —         | —     | MODE  | <1:0> | 0000   |

| DMA2REQ   | 039A         | FORCE  | —         | —      |        | —      | —      |       |       | —        |       |       |        | RQSEL<6:0 | >     |       |       | 0000   |

| DMA2STA   | 039C         |        |           |        |        |        |        |       | S     | TA<15:0> |       |       |        |           |       |       |       | 0000   |

| DMA2STB   | 039E         |        |           |        |        |        |        |       | S     | TB<15:0> |       |       |        |           |       |       |       | 0000   |

| DMA2PAD   | 03A0         |        |           |        |        |        |        |       | Р     | AD<15:0> |       |       |        |           |       |       |       | 0000   |

| DMA2CNT   | 03A2         | —      | —         | —      | —      | —      | —      |       |       |          |       | CNT   | <9:0>  |           |       |       |       | 0000   |

| DMA3CON   | 03A4         | CHEN   | SIZE      | DIR    | HALF   | NULLW  | —      | —     | —     | —        | —     | AMOD  | E<1:0> | —         | —     | MODE  | <1:0> | 0000   |

| DMA3REQ   | 03A6         | FORCE  | —         | —      | —      | —      | —      | —     | —     | —        |       |       | I      | RQSEL<6:0 | >     |       |       | 0000   |

| DMA3STA   | 03A8         |        |           |        |        |        |        |       | S     | TA<15:0> |       |       |        |           |       |       |       | 0000   |

| DMA3STB   | 03AA         |        |           |        |        |        |        |       | S     | TB<15:0> |       |       |        |           |       |       |       | 0000   |

| DMA3PAD   | 03AC         |        |           |        |        |        |        |       | Р     | AD<15:0> |       |       |        |           |       |       |       | 0000   |

| DMA3CNT   | 03AE         | -      | -         | _      | _      | _      | _      |       |       |          |       | CNT   | <9:0>  |           |       |       |       | 0000   |

| DMA4CON   | 03B0         | CHEN   | SIZE      | DIR    | HALF   | NULLW  | _      | _     | _     | —        | _     | AMOD  | E<1:0> | _         | —     | MODE  | <1:0> | 0000   |

| DMA4REQ   | 03B2         | FORCE  | _         | _      | _      | _      | _      | _     | _     | _        |       |       | I      | RQSEL<6:0 | >     |       |       | 0000   |

| DMA4STA   | 03B4         |        |           |        |        |        |        |       | S     | TA<15:0> |       |       |        |           |       |       |       | 0000   |

| DMA4STB   | 03B6         |        |           |        |        |        |        |       | S     | TB<15:0> |       |       |        |           |       |       |       | 0000   |

| DMA4PAD   | 03B8         |        |           |        |        |        |        |       | Р     | AD<15:0> |       |       |        |           |       |       |       | 0000   |

| DMA4CNT   | 03BA         | _      | _         | _      | —      | _      | _      |       |       |          |       | CNT   | <9:0>  |           |       |       |       | 0000   |

| DMA5CON   | 03BC         | CHEN   | SIZE      | DIR    | HALF   | NULLW  | _      | —     | —     | —        | —     | AMOD  | E<1:0> | —         | _     | MODE  | <1:0> | 0000   |

| DMA5REQ   | 03BE         | FORCE  | _         | _      | —      | _      | _      | _     | _     | _        |       | •     | I      | RQSEL<6:0 | >     |       |       | 0000   |

| DMA5STA   | 03C0         |        |           |        |        |        |        |       | S     | TA<15:0> |       |       |        |           |       |       |       | 0000   |

| DMA5STB   | 03C2         |        |           |        |        |        |        |       | S     | TB<15:0> |       |       |        |           |       |       |       | 0000   |

Legend: — = unimplemented, read as '0'. Reset values are shown in hexadecimal for PinHigh devices.

| TABLE 7-1:         INTERRUPT VECTORS |                                      |             |              |                                      |  |  |  |  |

|--------------------------------------|--------------------------------------|-------------|--------------|--------------------------------------|--|--|--|--|

| Vector<br>Number                     | Interrupt<br>Request (IRQ)<br>Number | IVT Address | AIVT Address | Interrupt Source                     |  |  |  |  |

| 8                                    | 0                                    | 0x000014    | 0x000114     | INT0 – External Interrupt 0          |  |  |  |  |

| 9                                    | 1                                    | 0x000016    | 0x000116     | IC1 – Input Capture 1                |  |  |  |  |

| 10                                   | 2                                    | 0x000018    | 0x000118     | OC1 – Output Compare 1               |  |  |  |  |

| 11                                   | 3                                    | 0x00001A    | 0x00011A     | T1 – Timer1                          |  |  |  |  |

| 12                                   | 4                                    | 0x00001C    | 0x00011C     | DMA0 – DMA Channel 0                 |  |  |  |  |

| 13                                   | 5                                    | 0x00001E    | 0x00011E     | IC2 – Input Capture 2                |  |  |  |  |

| 14                                   | 6                                    | 0x000020    | 0x000120     | OC2 – Output Compare 2               |  |  |  |  |

| 15                                   | 7                                    | 0x000022    | 0x000122     | T2 – Timer2                          |  |  |  |  |

| 16                                   | 8                                    | 0x000024    | 0x000124     | T3 – Timer3                          |  |  |  |  |

| 17                                   | 9                                    | 0x000026    | 0x000126     | SPI1E – SPI1 Error                   |  |  |  |  |

| 18                                   | 10                                   | 0x000028    | 0x000128     | SPI1 – SPI1 Transfer Done            |  |  |  |  |

| 19                                   | 11                                   | 0x00002A    | 0x00012A     | U1RX – UART1 Receiver                |  |  |  |  |

| 20                                   | 12                                   | 0x00002C    | 0x00012C     | U1TX – UART1 Transmitter             |  |  |  |  |

| 21                                   | 13                                   | 0x00002E    | 0x00012E     | ADC1 – Analog-to-Digital Converter 1 |  |  |  |  |

| 22                                   | 14                                   | 0x000030    | 0x000130     | DMA1 – DMA Channel 1                 |  |  |  |  |

| 23                                   | 15                                   | 0x000032    | 0x000132     | Reserved                             |  |  |  |  |

| 24                                   | 16                                   | 0x000034    | 0x000134     | SI2C1 – I2C1 Slave Events            |  |  |  |  |

| 25                                   | 17                                   | 0x000036    | 0x000136     | MI2C1 – I2C1 Master Events           |  |  |  |  |

| 26                                   | 18                                   | 0x000038    | 0x000138     | Reserved                             |  |  |  |  |

| 27                                   | 19                                   | 0x00003A    | 0x00013A     | CN - Change Notification Interrupt   |  |  |  |  |

| 28                                   | 20                                   | 0x00003C    | 0x00013C     | INT1 – External Interrupt 1          |  |  |  |  |

| 29                                   | 21                                   | 0x00003E    | 0x00013E     | ADC2 – Analog-to-Digital Converter 2 |  |  |  |  |

| 30                                   | 22                                   | 0x000040    | 0x000140     | IC7 – Input Capture 7                |  |  |  |  |

| 31                                   | 23                                   | 0x000042    | 0x000142     | IC8 – Input Capture 8                |  |  |  |  |

| 32                                   | 24                                   | 0x000044    | 0x000144     | DMA2 – DMA Channel 2                 |  |  |  |  |

| 33                                   | 25                                   | 0x000046    | 0x000146     | OC3 – Output Compare 3               |  |  |  |  |

| 34                                   | 26                                   | 0x000048    | 0x000148     | OC4 – Output Compare 4               |  |  |  |  |

| 35                                   | 27                                   | 0x00004A    | 0x00014A     | T4 – Timer4                          |  |  |  |  |

| 36                                   | 28                                   | 0x00004C    | 0x00014C     | T5 – Timer5                          |  |  |  |  |

| 37                                   | 29                                   | 0x00004E    | 0x00014E     | INT2 – External Interrupt 2          |  |  |  |  |

| 38                                   | 30                                   | 0x000050    | 0x000150     | U2RX – UART2 Receiver                |  |  |  |  |

| 39                                   | 31                                   | 0x000052    | 0x000152     | U2TX – UART2 Transmitter             |  |  |  |  |

| 40                                   | 32                                   | 0x000054    | 0x000154     | SPI2E – SPI2 Error                   |  |  |  |  |

| 41                                   | 33                                   | 0x000056    | 0x000156     | SPI1 – SPI1 Transfer Done            |  |  |  |  |

| 42                                   | 34                                   | 0x000058    | 0x000158     | C1RX – ECAN1 Receive Data Ready      |  |  |  |  |

| 43                                   | 35                                   | 0x00005A    | 0x00015A     | C1 – ECAN1 Event                     |  |  |  |  |

| 44                                   | 36                                   | 0x00005C    | 0x00015C     | DMA3 – DMA Channel 3                 |  |  |  |  |

| 45                                   | 37                                   | 0x00005E    | 0x00015E     | IC3 – Input Capture 3                |  |  |  |  |

| 46                                   | 38                                   | 0x000060    | 0x000160     | IC4 – Input Capture 4                |  |  |  |  |

| 47                                   | 39                                   | 0x000062    | 0x000162     | IC5 – Input Capture 5                |  |  |  |  |

| 48                                   | 40                                   | 0x000064    | 0x000164     | IC6 – Input Capture 6                |  |  |  |  |

| 49                                   | 41                                   | 0x000066    | 0x000166     | OC5 – Output Compare 5               |  |  |  |  |

| 50                                   | 42                                   | 0x000068    | 0x000168     | OC6 – Output Compare 6               |  |  |  |  |

| 51                                   | 43                                   | 0x00006A    | 0x00016A     | OC7 – Output Compare 7               |  |  |  |  |

| 52                                   | 44                                   | 0x00006C    | 0x00016C     | OC8 – Output Compare 8               |  |  |  |  |

| 53                                   | 45                                   | 0x00006E    | 0x00016E     | Reserved                             |  |  |  |  |

TABLE 7-1: INTERRUPT VECTORS

#### REGISTER 7-5: IFS0: INTERRUPT FLAG STATUS REGISTER 0 (CONTINUED)

| bit 2 | OC1IF: Output Compare Channel 1 Interrupt Flag Status bit |

|-------|-----------------------------------------------------------|

|       | <ol> <li>Interrupt request has occurred</li> </ol>        |

|       | 0 = Interrupt request has not occurred                    |

| bit 1 | IC1IF: Input Capture Channel 1 Interrupt Flag Status bit  |

|       | 1 = Interrupt request has occurred                        |

|       | 0 = Interrupt request has not occurred                    |

| bit 0 | INTOIF: External Interrupt 0 Flag Status bit              |

|       | 1 = Interrupt request has occurred                        |

|       | 0 = Interrupt request has not occurred                    |

#### **REGISTER 8-5:** DMAXPAD: DMA CHANNEL x PERIPHERAL ADDRESS REGISTER<sup>(1)</sup>

| R/W-0                             | R/W-0 | R/W-0            | R/W-0 | R/W-0                                   | R/W-0           | R/W-0    | R/W-0 |

|-----------------------------------|-------|------------------|-------|-----------------------------------------|-----------------|----------|-------|

|                                   |       |                  | PAD   | <15:8>                                  |                 |          |       |

| bit 15                            |       |                  |       |                                         |                 |          | bit 8 |

|                                   |       |                  |       |                                         |                 |          |       |

| R/W-0                             | R/W-0 | R/W-0            | R/W-0 | R/W-0                                   | R/W-0           | R/W-0    | R/W-0 |

|                                   |       |                  | PAD   | )<7:0>                                  |                 |          |       |

| bit 7                             |       |                  |       |                                         |                 |          | bit 0 |

|                                   |       |                  |       |                                         |                 |          |       |

| Legend:                           |       |                  |       |                                         |                 |          |       |

| R = Readable bit W = Writable bit |       |                  | bit   | U = Unimplen                            | nented bit, rea | d as '0' |       |

| -n = Value at P                   | OR    | '1' = Bit is set |       | '0' = Bit is cleared x = Bit is unknown |                 |          | nown  |

bit 15-0 PAD<15:0>: Peripheral Address Register bits

**Note 1:** If the channel is enabled (i.e., active), writes to this register may result in unpredictable behavior of the DMA channel and should be avoided.

#### REGISTER 8-6: DMAxCNT: DMA CHANNEL x TRANSFER COUNT REGISTER<sup>(1)</sup>

| U-0    | U-0                     | U-0   | U-0   | U-0   | U-0                       | R/W-0 | R/W-0 |  |  |  |  |  |

|--------|-------------------------|-------|-------|-------|---------------------------|-------|-------|--|--|--|--|--|

| —      | _                       | —     | —     |       | — CNT<9:8> <sup>(2)</sup> |       |       |  |  |  |  |  |

| bit 15 | bit 15 bit 8            |       |       |       |                           |       |       |  |  |  |  |  |

|        |                         |       |       |       |                           |       |       |  |  |  |  |  |

| R/W-0  | R/W-0                   | R/W-0 | R/W-0 | R/W-0 | R/W-0                     | R/W-0 | R/W-0 |  |  |  |  |  |

|        | CNT<7:0> <sup>(2)</sup> |       |       |       |                           |       |       |  |  |  |  |  |

| Legend:           |                  |                       |                    |

|-------------------|------------------|-----------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit | , read as '0'      |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared  | x = Bit is unknown |

bit 15-10 Unimplemented: Read as '0'

bit 9-0 CNT<9:0>: DMA Transfer Count Register bits<sup>(2)</sup>

- **Note 1:** If the channel is enabled (i.e., active), writes to this register may result in unpredictable behavior of the DMA channel and should be avoided.

- 2: Number of DMA transfers = CNT<9:0> + 1.

bit 7

bit 0

| R/W-0                 | R/W-0          | R/W-0                               | R/W-0                 | U-0               | U-0           | U-0            | U-0                  |

|-----------------------|----------------|-------------------------------------|-----------------------|-------------------|---------------|----------------|----------------------|

| T9MD                  | T8MD           | T7MD                                | T6MD                  |                   | _             | _              | _                    |

| bit 15                | - I            |                                     | 1                     |                   |               |                | bit 8                |

|                       |                |                                     |                       |                   |               |                |                      |

| U-0                   | U-0            | U-0                                 | U-0                   | U-0               | U-0           | R/W-0          | R/W-0                |

| _                     |                | —                                   | —                     | —                 | —             | I2C2MD         | AD2MD <sup>(1)</sup> |

| bit 7                 |                |                                     |                       |                   |               |                | bit (                |

| Logondi               |                |                                     |                       |                   |               |                |                      |

| Legend:<br>R = Readal | ble bit        | W = Writable                        | hit                   | U = Unimplem      | ented bit rea | ad as '0'      |                      |

| -n = Value a          |                | '1' = Bit is set                    |                       | '0' = Bit is clea |               | x = Bit is unk | nown                 |

|                       |                |                                     |                       |                   |               |                | -                    |

| bit 15                | T9MD: Timer    | 9 Module Disab                      | ole bit               |                   |               |                |                      |

|                       | 1 = Timer9 m   | odule is disable                    | ed                    |                   |               |                |                      |

|                       | 0 = Timer9 m   | odule is enable                     | d                     |                   |               |                |                      |

| bit 14                | T8MD: Timer    | 8 Module Disab                      | ole bit               |                   |               |                |                      |

|                       |                | odule is disable                    |                       |                   |               |                |                      |

|                       |                | odule is enable                     |                       |                   |               |                |                      |

| bit 13                | T7MD: Timer    | 7 Module Disab                      | ole bit               |                   |               |                |                      |

|                       | -              | odule is disable                    |                       |                   |               |                |                      |

|                       |                | odule is enable                     | -                     |                   |               |                |                      |

| bit 12                |                | 6 Module Disat                      |                       |                   |               |                |                      |

|                       |                | odule is disable<br>odule is enable |                       |                   |               |                |                      |

| bit 11-2              |                | ted: Read as '                      |                       |                   |               |                |                      |

| bit 1                 | •              | 2 Module Disat                      |                       |                   |               |                |                      |

|                       |                | lule is disabled                    |                       |                   |               |                |                      |

|                       |                | lule is enabled                     |                       |                   |               |                |                      |

| bit 0                 |                | 2 Module Disab                      | le bit <sup>(1)</sup> |                   |               |                |                      |

|                       |                | ule is disabled                     |                       |                   |               |                |                      |

|                       | $0 = AD2 \mod$ |                                     |                       |                   |               |                |                      |

**Note 1:** The PCFGx bits will have no effect if the ADC module is disabled by setting this bit. In this case, all port pins multiplexed with ANx will be in Digital mode.

#### 11.2 Open-Drain Configuration

In addition to the PORT, LAT and TRIS registers for data control, some port pins can also be individually configured for either digital or open-drain output. This is controlled by the Open-Drain Control register, ODCx, associated with each port. Setting any of the bits configures the corresponding pin to act as an open-drain output.

The open-drain feature allows the generation of outputs higher than VDD (e.g., 5V) on any desired 5V tolerant pins by using external pull-up resistors. The maximum open-drain voltage allowed is the same as the maximum VIH specification.

See the "**Pin Diagrams**" section for the available pins and their functionality.

#### 11.3 Configuring Analog Port Pins

The use of the ADxPCFGH, ADxPCFGL and TRIS registers control the operation of the Analog-to-Digital port pins. The port pins that are desired as analog inputs must have their corresponding TRIS bit set (input). If the TRIS bit is cleared (output), the digital output level (VOH or VOL) is converted.

Clearing any bit in the ADxPCFGH or ADxPCFGL register configures the corresponding bit to be an analog pin. This is also the Reset state of any I/O pin that has an analog (ANx) function associated with it.

| Note: | In devices with two ADC modules, if the     |

|-------|---------------------------------------------|

|       | corresponding PCFG bit in either            |

|       | AD1PCFGH(L) and AD2PCFGH(L) is              |

|       | cleared, the pin is configured as an analog |

|       | input.                                      |

When reading the PORT register, all pins configured as analog input channels will read as cleared (a low level).

Pins configured as digital inputs will not convert an analog input. Analog levels on any pin that is defined as a digital input (including the ANx pins) can cause the input buffer to consume current that exceeds the device specifications.

| Note: | The voltage on an analog input pin can be |

|-------|-------------------------------------------|

|       | between -0.3V to (VDD + 0.3 V).           |

#### 11.4 I/O Port Write/Read Timing

One instruction cycle is required between a port direction change or port write operation and a read operation of the same port. Typically, this instruction would be a NOP.

#### 11.5 Input Change Notification

The input change notification function of the I/O ports allows the PIC24HJXXXGPX06A/X08A/X10A devices to generate interrupt requests to the processor in response to a change-of-state on selected input pins. This feature is capable of detecting input change-of-states even in Sleep mode, when the clocks are disabled. Depending on the device pin count, there are up to 24 external signals (CN0 through CN23) that can be selected (enabled) for generating an interrupt request on a change-of-state.

There are four control registers associated with the CN module. The CNEN1 and CNEN2 registers contain the CN interrupt enable (CNxIE) control bits for each of the CN input pins. Setting any of these bits enables a CN interrupt for the corresponding pins.

Each CN pin also has a weak pull-up connected to it. The pull-ups act as a current source that is connected to the pin and eliminate the need for external resistors when push button or keypad devices are connected. The pull-ups are enabled separately using the CNPU1 and CNPU2 registers, which contain the weak pull-up enable (CNxPUE) bits for each of the CN pins. Setting any of the control bits enables the weak pull-ups for the corresponding pins.

Note: Pull-ups on change notification pins should always be disabled whenever the port pin is configured as a digital output.

#### EXAMPLE 11-1: PORT WRITE/READ EXAMPLE

| MOV  | OxFF00, WO | ; Configure PORTB<15:8> as inputs |

|------|------------|-----------------------------------|

| MOV  | W0, TRISBB | ; and PORTB<7:0> as outputs       |

| NOP  |            | ; Delay 1 cycle                   |

| btss | PORTB, #13 | ; Next Instruction                |

|      |            |                                   |

| R/W-0         | U-0                                                        | R/W-0            | U-0            | U-0                    | U-0             | U-0                | U-0 |  |  |  |  |  |  |

|---------------|------------------------------------------------------------|------------------|----------------|------------------------|-----------------|--------------------|-----|--|--|--|--|--|--|

| TON           |                                                            | TSIDL            |                | —                      |                 | —                  |     |  |  |  |  |  |  |

| bit 15        |                                                            |                  |                |                        |                 |                    | bit |  |  |  |  |  |  |

| U-0           | R/W-0                                                      | R/W-0            | R/W-0          | R/W-0                  | U-0             | R/W-0              | U-0 |  |  |  |  |  |  |

| 0-0           | TGATE                                                      |                  | S<1:0>         | T32                    | 0-0             | TCS <sup>(1)</sup> | 0-0 |  |  |  |  |  |  |

| <br>bit 7     | IGAIE                                                      | TCKP             | 5<1.0>         | 132                    | _               | 1030               | bit |  |  |  |  |  |  |

|               |                                                            |                  |                |                        |                 |                    |     |  |  |  |  |  |  |

| Legend:       |                                                            |                  |                |                        |                 |                    |     |  |  |  |  |  |  |

| R = Readable  | e bit                                                      | W = Writable     | bit            | U = Unimplem           | nented bit, rea | d as '0'           |     |  |  |  |  |  |  |

| -n = Value at | POR                                                        | '1' = Bit is se  | t              | '0' = Bit is clea      | ared            | x = Bit is unkno   | own |  |  |  |  |  |  |

| bit 15        | TON: Timerx                                                | On bit           |                |                        |                 |                    |     |  |  |  |  |  |  |

|               | When T32 = 1                                               | L:               |                |                        |                 |                    |     |  |  |  |  |  |  |

|               | 1 = Starts 32-<br>0 = Stops 32-                            |                  |                |                        |                 |                    |     |  |  |  |  |  |  |

|               |                                                            | When $T32 = 0$ : |                |                        |                 |                    |     |  |  |  |  |  |  |

|               | 1 = Starts 16-bit Timerx<br>0 = Stops 16-bit Timerx        |                  |                |                        |                 |                    |     |  |  |  |  |  |  |

| bit 14        |                                                            |                  | ٠́ ()'         |                        |                 |                    |     |  |  |  |  |  |  |

| bit 13        | Unimplemented: Read as '0'<br>TSIDL: Stop in Idle Mode bit |                  |                |                        |                 |                    |     |  |  |  |  |  |  |

|               | •                                                          | ue module ope    | eration when d | evice enters Idl<br>de | e mode          |                    |     |  |  |  |  |  |  |

| bit 12-7      | Unimplemen                                                 | -                |                |                        |                 |                    |     |  |  |  |  |  |  |

| bit 6         | TGATE: Timerx Gated Time Accumulation Enable bit           |                  |                |                        |                 |                    |     |  |  |  |  |  |  |

|               | When TCS = 1:                                              |                  |                |                        |                 |                    |     |  |  |  |  |  |  |

|               | This bit is ignored.                                       |                  |                |                        |                 |                    |     |  |  |  |  |  |  |

|               | When TCS = 0:<br>1 = Gated time accumulation enabled       |                  |                |                        |                 |                    |     |  |  |  |  |  |  |

|               | 0 = Gated time accumulation disabled                       |                  |                |                        |                 |                    |     |  |  |  |  |  |  |

| bit 5-4       | TCKPS<1:0>: Timerx Input Clock Prescale Select bits        |                  |                |                        |                 |                    |     |  |  |  |  |  |  |

|               | 11 = 1:256                                                 |                  |                |                        |                 |                    |     |  |  |  |  |  |  |

|               | 10 = 1:64                                                  |                  |                |                        |                 |                    |     |  |  |  |  |  |  |

|               | 01 = 1:8<br>00 = 1:1                                       |                  |                |                        |                 |                    |     |  |  |  |  |  |  |

| bit 3         | <b>T32:</b> 32-bit Timer Mode Select bit                   |                  |                |                        |                 |                    |     |  |  |  |  |  |  |

|               | 1 = Timerx an<br>0 = Timerx an                             |                  |                |                        |                 |                    |     |  |  |  |  |  |  |

| bit 2         | Unimplemen                                                 | -                |                |                        |                 |                    |     |  |  |  |  |  |  |

| bit 1         | TCS: Timerx                                                |                  |                |                        |                 |                    |     |  |  |  |  |  |  |

|               | 1 = External c<br>0 = Internal cl                          | clock from pin   |                | rising edge)           |                 |                    |     |  |  |  |  |  |  |

|               |                                                            | · · /            |                |                        |                 |                    |     |  |  |  |  |  |  |

#### REGISTER 13-1: TxCON (T2CON, T4CON, T6CON OR T8CON) CONTROL REGISTER

Note 1: The TxCK pin is not available on all timers. Refer to the "Pin Diagrams" section for the available pins.

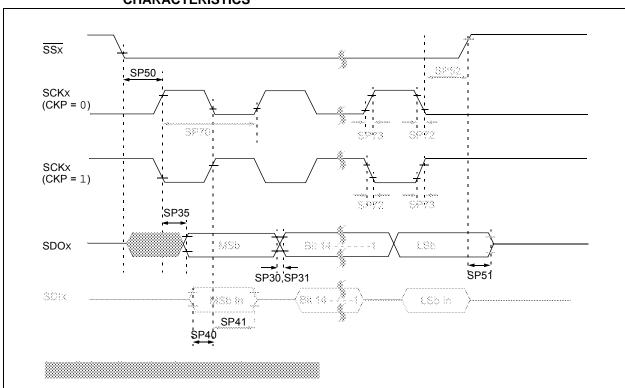

#### REGISTER 16-2: SPIXCON1: SPIX CONTROL REGISTER 1 (CONTINUED)

- bit 4-2 SPRE<2:0>: Secondary Prescale bits (Master mode)<sup>(2)</sup>

- 111 = Secondary prescale 1:1

- 110 = Secondary prescale 2:1

- •

- •

- 000 = Secondary prescale 8:1

- bit 1-0 **PPRE<1:0>:** Primary Prescale bits (Master mode)<sup>(2)</sup>

- 11 = Primary prescale 1:1

- 10 = Primary prescale 4:1

- 01 = Primary prescale 16:1

- 00 = Primary prescale 64:1

- **Note 1:** The CKE bit is not used in the Framed SPI modes. The user should program this bit to '0' for the Framed SPI modes (FRMEN = 1).

- **2:** Do not set both Primary and Secondary prescalers to a value of 1:1.

- **3:** This bit must be cleared when FRMEN = 1.

#### **REGISTER 18-1: UXMODE: UARTX MODE REGISTER (CONTINUED)**

| bit 4   | <b>URXINV:</b> Receive Polarity Inversion bit<br>1 = UxRX Idle state is '0'<br>0 = UxRX Idle state is '1'                                                                          |

|---------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| bit 3   | BRGH: High Baud Rate Enable bit                                                                                                                                                    |

|         | <ul> <li>1 = BRG generates 4 clocks per bit period (4x baud clock, High-Speed mode)</li> <li>0 = BRG generates 16 clocks per bit period (16x baud clock, Standard mode)</li> </ul> |

| bit 2-1 | PDSEL<1:0>: Parity and Data Selection bits                                                                                                                                         |

|         | <ul> <li>11 = 9-bit data, no parity</li> <li>10 = 8-bit data, odd parity</li> <li>01 = 8-bit data, even parity</li> <li>00 = 8-bit data, no parity</li> </ul>                      |

| bit 0   | STSEL: Stop Bit Selection bit                                                                                                                                                      |

|         | 1 = Two Stop bits<br>0 = One Stop bit                                                                                                                                              |

- **Note 1:** Refer to **Section 17. "UART**" (DS70188) in the *"dsPIC33F/PIC24H Family Reference Manual"* for information on enabling the UART module for receive or transmit operation.

- 2: This feature is only available for the 16x BRG mode (BRGH = 0).

| U-0                  | U-0                                                                                                                                      | R-0                                                                                                                             | R-0                                                                                           | R-0              | R-0                                           | R-0             | R-0   |  |  |  |  |  |

|----------------------|------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------|------------------|-----------------------------------------------|-----------------|-------|--|--|--|--|--|

|                      | _                                                                                                                                        | ТХВО                                                                                                                            | TXBP                                                                                          | RXBP             | TXWAR                                         | RXWAR           | EWARN |  |  |  |  |  |

| bit 15               |                                                                                                                                          |                                                                                                                                 |                                                                                               | 1                | 1                                             |                 | bit 8 |  |  |  |  |  |

|                      |                                                                                                                                          |                                                                                                                                 |                                                                                               |                  |                                               |                 |       |  |  |  |  |  |

| R/C-0                | R/C-0                                                                                                                                    | R/C-0                                                                                                                           | U-0                                                                                           | R/C-0            | R/C-0                                         | R/C-0           | R/C-0 |  |  |  |  |  |

| IVRIF                | WAKIF                                                                                                                                    | ERRIF                                                                                                                           | —                                                                                             | FIFOIF           | RBOVIF                                        | RBIF            | TBIF  |  |  |  |  |  |

| bit 7                | ·                                                                                                                                        |                                                                                                                                 |                                                                                               |                  | ·                                             | ÷               | bit ( |  |  |  |  |  |

|                      |                                                                                                                                          |                                                                                                                                 |                                                                                               |                  |                                               |                 |       |  |  |  |  |  |

| Legend:              |                                                                                                                                          | C = Clear onl                                                                                                                   | y bit                                                                                         |                  |                                               |                 |       |  |  |  |  |  |

| R = Readable         | bit                                                                                                                                      | W = Writable                                                                                                                    | bit                                                                                           | U = Unimpler     | mented bit, read                              | d as '0'        |       |  |  |  |  |  |

| -n = Value at I      | POR                                                                                                                                      | '1' = Bit is set                                                                                                                |                                                                                               | '0' = Bit is cle | ared                                          | x = Bit is unkr | nown  |  |  |  |  |  |

| bit 15-14            | Unimplomon                                                                                                                               | ted. Dood oo '                                                                                                                  | 0'                                                                                            |                  |                                               |                 |       |  |  |  |  |  |

| bit 13               | -                                                                                                                                        | ited: Read as '<br>mitter in Error                                                                                              |                                                                                               | hit              |                                               |                 |       |  |  |  |  |  |

| bit 15               |                                                                                                                                          | er is in Bus Of                                                                                                                 |                                                                                               | bit              |                                               |                 |       |  |  |  |  |  |

|                      | 0 = Transmitt                                                                                                                            | er is not in Bus                                                                                                                | Off state                                                                                     |                  |                                               |                 |       |  |  |  |  |  |

| bit 12               |                                                                                                                                          | mitter in Error                                                                                                                 |                                                                                               | sive bit         |                                               |                 |       |  |  |  |  |  |

|                      |                                                                                                                                          | er is in Bus Pa                                                                                                                 |                                                                                               | -                |                                               |                 |       |  |  |  |  |  |

| bit 11               |                                                                                                                                          | er is not in Bus<br>iver in Error Sta                                                                                           |                                                                                               |                  |                                               |                 |       |  |  |  |  |  |

|                      |                                                                                                                                          | is in Bus Pass                                                                                                                  |                                                                                               | vebil            |                                               |                 |       |  |  |  |  |  |

|                      | 0 = Receiver                                                                                                                             | is not in Bus P                                                                                                                 | assive state                                                                                  |                  |                                               |                 |       |  |  |  |  |  |

| bit 10               | TXWAR: Transmitter in Error State Warning bit                                                                                            |                                                                                                                                 |                                                                                               |                  |                                               |                 |       |  |  |  |  |  |

|                      | 1 = Transmitter is in Error Warning state                                                                                                |                                                                                                                                 |                                                                                               |                  |                                               |                 |       |  |  |  |  |  |

| bit 9                | 0 = Transmitter is not in Error Warning state                                                                                            |                                                                                                                                 |                                                                                               |                  |                                               |                 |       |  |  |  |  |  |

| DIL 9                | RXWAR: Receiver in Error State Warning bit<br>1 = Receiver is in Error Warning state                                                     |                                                                                                                                 |                                                                                               |                  |                                               |                 |       |  |  |  |  |  |

|                      | 0 = Receiver is not in Error Warning state                                                                                               |                                                                                                                                 |                                                                                               |                  |                                               |                 |       |  |  |  |  |  |

| bit 8                | EWARN: Transmitter or Receiver in Error State Warning bit                                                                                |                                                                                                                                 |                                                                                               |                  |                                               |                 |       |  |  |  |  |  |

|                      |                                                                                                                                          |                                                                                                                                 | er or receiver is in Error Warning state                                                      |                  |                                               |                 |       |  |  |  |  |  |

| <b>h</b> :+ <b>7</b> |                                                                                                                                          | er or receiver i                                                                                                                |                                                                                               | •                |                                               |                 |       |  |  |  |  |  |

| bit 7                |                                                                                                                                          | IVRIF: Invalid Message Received Interrupt Flag bit<br>1 = Interrupt request has occurred                                        |                                                                                               |                  |                                               |                 |       |  |  |  |  |  |

|                      | 0 = Interrupt request has not occurred                                                                                                   |                                                                                                                                 |                                                                                               |                  |                                               |                 |       |  |  |  |  |  |

| bit 6                | WAKIF: Bus                                                                                                                               | Wake-up Activ                                                                                                                   | ity Interrupt F                                                                               | lag bit          |                                               |                 |       |  |  |  |  |  |

|                      | 1 = Interrupt request has occurred                                                                                                       |                                                                                                                                 |                                                                                               |                  |                                               |                 |       |  |  |  |  |  |

| L:1 F                | •                                                                                                                                        | request has no                                                                                                                  |                                                                                               |                  |                                               |                 |       |  |  |  |  |  |

| bit 5                |                                                                                                                                          |                                                                                                                                 |                                                                                               | ources in Clin   | F<13:8> regist                                | ter)            |       |  |  |  |  |  |

|                      |                                                                                                                                          | request has oc<br>request has no                                                                                                |                                                                                               |                  |                                               |                 |       |  |  |  |  |  |

| bit 4                | •                                                                                                                                        | ted: Read as '                                                                                                                  |                                                                                               |                  |                                               |                 |       |  |  |  |  |  |

| bit 3                | •                                                                                                                                        | Almost Full In                                                                                                                  |                                                                                               | it               |                                               |                 |       |  |  |  |  |  |

| bit 5                | 1 = Interrupt                                                                                                                            | request has oc                                                                                                                  | curred                                                                                        |                  |                                               |                 |       |  |  |  |  |  |

|                      | 0 = Interrupt I                                                                                                                          | roquest has no                                                                                                                  | t occurred                                                                                    |                  |                                               |                 |       |  |  |  |  |  |

|                      |                                                                                                                                          | •                                                                                                                               |                                                                                               |                  | RBOVIF: RX Buffer Overflow Interrupt Flag bit |                 |       |  |  |  |  |  |

| bit 2                |                                                                                                                                          | Buffer Overflo                                                                                                                  | w Interrupt Fla                                                                               | ag bit           |                                               |                 |       |  |  |  |  |  |

| bit 2                | 1 = Interrupt                                                                                                                            | Buffer Overflor<br>request has oc                                                                                               | w Interrupt Fla<br>curred                                                                     | ag bit           |                                               |                 |       |  |  |  |  |  |

|                      | 1 = Interrupt                                                                                                                            | Buffer Overflo<br>request has oc<br>request has no                                                                              | w Interrupt Fla<br>curred<br>t occurred                                                       | ag bit           |                                               |                 |       |  |  |  |  |  |

| bit 2<br>bit 1       | 1 = Interrupt i<br>0 = Interrupt i<br><b>RBIF:</b> RX Bu                                                                                 | Buffer Overflor<br>request has oc                                                                                               | w Interrupt Fla<br>curred<br>t occurred<br>ag bit                                             | ag bit           |                                               |                 |       |  |  |  |  |  |

| bit 1                | 1 = Interrupt (<br>0 = Interrupt (<br><b>RBIF:</b> RX But<br>1 = Interrupt (<br>0 = Interrupt (                                          | Buffer Overflo<br>request has oc<br>request has no<br>ffer Interrupt Fl<br>request has oc<br>request has no                     | w Interrupt Fla<br>curred<br>t occurred<br>ag bit<br>curred<br>t occurred                     | ag bit           |                                               |                 |       |  |  |  |  |  |

|                      | 1 = Interrupt i<br>0 = Interrupt i<br><b>RBIF:</b> RX Bu<br>1 = Interrupt i<br>0 = Interrupt i<br><b>TBIF:</b> TX Buf                    | Buffer Overflo<br>request has oc<br>request has no<br>ffer Interrupt Fl<br>request has oc<br>request has no<br>fer Interrupt Fl | w Interrupt Fla<br>curred<br>t occurred<br>ag bit<br>curred<br>t occurred<br>ag bit           | ag bit           |                                               |                 |       |  |  |  |  |  |

| bit 1                | 1 = Interrupt i<br>0 = Interrupt i<br><b>RBIF:</b> RX Bu<br>1 = Interrupt i<br>0 = Interrupt i<br><b>TBIF:</b> TX Buf<br>1 = Interrupt i | Buffer Overflo<br>request has oc<br>request has no<br>ffer Interrupt Fl<br>request has oc<br>request has no                     | w Interrupt Fla<br>curred<br>t occurred<br>ag bit<br>curred<br>t occurred<br>ag bit<br>curred | ag bit           |                                               |                 |       |  |  |  |  |  |

#### 20.6 ADC Control Registers

#### **REGISTER 20-1:** ADxCON1: ADCx CONTROL REGISTER 1(where x = 1 or 2)

| R/W-0  | U-0       | R/W-0  | R/W-0   | U-0    | R/W-0 | R/W-0     | R/W-0  |

|--------|-----------|--------|---------|--------|-------|-----------|--------|

| ADON   | _         | ADSIDL | ADDMABM |        | AD12B | FORM<1:0> |        |

| bit 15 |           |        |         |        |       |           | bit 8  |

|        |           |        |         |        |       |           |        |

| R/W-0  | R/W-0     | R/W-0  | U-0     | R/W-0  | R/W-0 | R/W-0     | R/C-0  |

|        |           |        |         |        |       | HC,HS     | HC, HS |

|        | SSRC<2:0> |        | —       | SIMSAM | ASAM  | SAMP      | DONE   |

| bit 7  |           |        |         |        |       |           | bit 0  |

| Legend:           | HC = Cleared by hardware HS = Set by hardware |                                    |                    |  |

|-------------------|-----------------------------------------------|------------------------------------|--------------------|--|

| R = Readable bit  | W = Writable bit                              | U = Unimplemented bit, read as '0' |                    |  |

| -n = Value at POR | '1' = Bit is set                              | '0' = Bit is cleared               | x = Bit is unknown |  |

| bit 15  | ADON: ADC Operating Mode bit                                                                                                                                                                                   |

|---------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|         | 1 = ADC module is operating                                                                                                                                                                                    |

|         | 0 = ADC module is off                                                                                                                                                                                          |

| bit 14  | Unimplemented: Read as '0'                                                                                                                                                                                     |

| bit 13  | ADSIDL: Stop in Idle Mode bit                                                                                                                                                                                  |

|         | 1 = Discontinue module operation when device enters Idle mode                                                                                                                                                  |

|         | 0 = Continue module operation in Idle mode                                                                                                                                                                     |

| bit 12  | ADDMABM: DMA Buffer Build Mode bit                                                                                                                                                                             |

|         | 1 = DMA buffers are written in the order of conversion. The module will provide an address to the DMA channel that is the same as the address used for the non-DMA stand-alone buffer                          |

|         | <ul> <li>DMA buffers are written in Scatter/Gather mode. The module will provide a scatter/gather address to the DMA channel, based on the index of the analog input and the size of the DMA buffer</li> </ul> |

| bit 11  | Unimplemented: Read as '0'                                                                                                                                                                                     |

| bit 10  | AD12B: 10-Bit or 12-Bit Operation Mode bit                                                                                                                                                                     |

|         | 1 = 12-bit, 1-channel ADC operation                                                                                                                                                                            |

|         | 0 = 10-bit, 4-channel ADC operation                                                                                                                                                                            |

| bit 9-8 | FORM<1:0>: Data Output Format bits                                                                                                                                                                             |

|         | For 10-bit operation:                                                                                                                                                                                          |

|         | 11 = Reserved                                                                                                                                                                                                  |

|         | 10 = Reserved                                                                                                                                                                                                  |

|         | 01 = Signed integer (Dout = ssss sssd dddd dddd, where s = .NOT.d<9>)<br>00 = Integer (Dout = 0000 00dd dddd dddd)                                                                                             |

|         | For 12-bit operation:                                                                                                                                                                                          |