Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFl

| Details                    |                                                                                 |

|----------------------------|---------------------------------------------------------------------------------|

| Product Status             | Obsolete                                                                        |

| Core Processor             | PIC                                                                             |

| Core Size                  | 16-Bit                                                                          |

| Speed                      | 20 MIPS                                                                         |

| Connectivity               | I <sup>2</sup> C, IrDA, LINbus, SPI, UART/USART                                 |

| Peripherals                | Brown-out Detect/Reset, DMA, POR, PWM, WDT                                      |

| Number of I/O              | 53                                                                              |

| Program Memory Size        | 256KB (85.5K x 24)                                                              |

| Program Memory Type        | FLASH                                                                           |

| EEPROM Size                | -                                                                               |

| RAM Size                   | 16K x 8                                                                         |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 3.6V                                                                       |

| Data Converters            | A/D 18x10b/12b                                                                  |

| Oscillator Type            | Internal                                                                        |

| Operating Temperature      | -40°C ~ 150°C (TA)                                                              |

| Mounting Type              | Surface Mount                                                                   |

| Package / Case             | 64-VFQFN Exposed Pad                                                            |

| Supplier Device Package    | 64-VQFN (9x9)                                                                   |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic24hj256gp206a-h-mr |

|                            |                                                                                 |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

### 3.3 CPU Control Registers

### REGISTER 3-1: SR: CPU STATUS REGISTER

| U-0                  | U-0                                         | U-0                                  | U-0              | U-0                      | U-0                 | U-0               | R/W-0          |

|----------------------|---------------------------------------------|--------------------------------------|------------------|--------------------------|---------------------|-------------------|----------------|

|                      | _                                           | _                                    | _                |                          |                     |                   | DC             |

| bit 15               | •                                           |                                      | •                |                          |                     |                   | bit 8          |

| R/W-0 <sup>(1)</sup> | R/W-0 <sup>(2)</sup>                        | R/W-0 <sup>(2)</sup>                 | R-0              | R/W-0                    | R/W-0               | R/W-0             | R/W-0          |

|                      | IPL<2:0> <sup>(2)</sup>                     |                                      | RA               | Ν                        | OV                  | Z                 | С              |

| bit 7                |                                             |                                      |                  |                          |                     |                   | bit (          |

| Legend:              |                                             |                                      |                  |                          |                     |                   |                |

| C = Clear only       | y bit                                       | R = Readabl                          | e bit            | U = Unimplei             | mented bit, read    | l as '0'          |                |

| S = Set only b       | bit                                         | W = Writable                         | bit              | -n = Value at            | POR                 |                   |                |

| '1' = Bit is set     |                                             | '0' = Bit is cle                     | ared             | x = Bit is unk           | nown                |                   |                |

| bit 15-9             | Unimpleme                                   | nted: Read as                        | ʻ0'              |                          |                     |                   |                |

| bit 8                | DC: MCU AL                                  | U Half Carry/B                       | orrow bit        |                          |                     |                   |                |

|                      | •                                           |                                      | low-order bit (  | for byte sized           | data) or 8th low-   | order bit (for wo | ord sized data |

|                      |                                             | sult occurred                        | 14b law and an k | it (far buta aim         | ad data) as Oth     | law and an bit (  | for word since |

|                      |                                             | the result occu                      |                  | Dit (for byte siz        | ed data) or 8th     | iow-order bit (   | for word sized |

| bit 7-5              |                                             | PU Interrupt Pr                      |                  | atus bits <sup>(2)</sup> |                     |                   |                |

|                      |                                             | nterrupt Priority                    |                  |                          | ots disabled        |                   |                |

|                      | 110 = CPU I                                 | nterrupt Priority                    | /Level is 6 (14  | +)                       |                     |                   |                |

|                      |                                             | nterrupt Priority                    |                  |                          |                     |                   |                |

|                      |                                             | nterrupt Priority                    |                  |                          |                     |                   |                |

|                      |                                             | nterrupt Priority                    |                  |                          |                     |                   |                |

|                      |                                             | nterrupt Priority                    |                  |                          |                     |                   |                |

|                      |                                             | nterrupt Priority                    |                  |                          |                     |                   |                |

| bit 4                | <b>RA:</b> REPEAT                           | Loop Active bi                       | t                |                          |                     |                   |                |

|                      |                                             | loop in progres                      |                  |                          |                     |                   |                |

| bit 3                |                                             | J Negative bit                       | -                |                          |                     |                   |                |

|                      | 1 = Result w                                | as negative                          |                  |                          |                     |                   |                |

| 1.11.0               |                                             | as non-negativ                       |                  | tive)                    |                     |                   |                |

| bit 2                |                                             | U Overflow bit                       |                  |                          |                     |                   |                |

|                      |                                             | ed for signed ar<br>ign bit to chang | · ·              | omplement). It           | indicates an ove    | erflow of the ma  | agnitude whici |

|                      |                                             | <b>U U</b>                           | ·                | ic (in this arith        | metic operation)    |                   |                |

|                      | 0 = No overf                                |                                      | .g               |                          |                     |                   |                |

| bit 1                | Z: MCU ALU                                  | I Zero bit                           |                  |                          |                     |                   |                |

|                      | •                                           |                                      |                  |                          | e time in the pa    |                   | oult)          |

| bit 0                |                                             | J Carry/Borrow                       |                  | Jo line ∠ Dil Na         | s cleared it (i.e., | a 11011-2010 10   | suit)          |

| 2.00                 |                                             |                                      |                  | oit (MSb) of the         | e result occurred   | 1                 |                |

|                      |                                             | -out from the M                      |                  |                          |                     | -                 |                |

|                      |                                             |                                      |                  |                          | RCON<3>) to for     |                   |                |

|                      | <pre>vei. The value i _&lt;3&gt; = 1.</pre> | in parentneses                       | indicates the I  | rl     rl<3> =           | 1. User interrup    |                   |                |

|                      |                                             |                                      |                  |                          |                     |                   |                |

2: The IPL<2:0> Status bits are read only when NSTDIS = 1 (INTCON1<15>).

### 4.0 MEMORY ORGANIZATION

Note: This data sheet summarizes the features of the PIC24HJXXXGPX06A/X08A/X10A family of devices. However, it is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to **Section 3.** "**Data Memory**" (DS70202) of the "dsPIC33F/PIC24H Family Reference Manual", which is available from the Microchip web site (www.microchip.com).

The PIC24HJXXXGPX06A/X08A/X10A architecture features separate program and data memory spaces and buses. This architecture also allows the direct access of program memory from the data space during code execution.

### 4.1 Program Address Space

The program address memory space of the PIC24HJXXXGPX06A/X08A/X10A devices is 4M instructions. The space is addressable by a 24-bit value derived from either the 23-bit Program Counter (PC) during program execution, or from table operation or data space remapping as described in **Section 4.4** "Interfacing Program and Data Memory Spaces".

User access to the program memory space is restricted to the lower half of the address range (0x000000 to 0x7FFFFF). The exception is the use of TBLRD/TBLWT operations, which use TBLPAG<7> to permit access to the Configuration bits and Device ID sections of the configuration memory space.

Memory maps for the PIC24HJXXXGPX06A/X08A/ X10A family of devices are shown in Figure 4-1.

|                            | PIC24HJ64XXXXXA                                    | PIC24HJ128XXXXXA                      | PIC24HJ256XXXXXA                      |                                  |

|----------------------------|----------------------------------------------------|---------------------------------------|---------------------------------------|----------------------------------|

| <b>▲</b>                   | GOTO Instruction                                   | <br>GOTO Instruction                  | <br>GOTO Instruction                  | 0x000000<br>- 0x000002           |

|                            | Reset Address                                      | <br>Reset Address                     | <br>Reset Address                     | 0x000004                         |

|                            | Interrupt Vector Table                             | Interrupt Vector Table                | Interrupt Vector Table                | 0x0000FE                         |

|                            | Reserved                                           | <br>Reserved                          | <br>Reserved                          | 0x000100                         |

|                            | Alternate Vector Table                             | Alternate Vector Table                | Alternate Vector Table                | 0x000104<br>0x0001FE             |

| User Memory Space          | User Program<br>Flash Memory<br>(22K instructions) | <br>User Program<br>Flash Memory      | <br>User Program<br>Flash Memory      | 0x000200                         |

| emory                      |                                                    | (44K instructions)                    | (88K instructions)                    | 0x0157FE                         |

| ser Mo                     |                                                    |                                       | <br>                                  | 0x015800                         |

| Š                          | Unimplemented<br>(Read '0's)                       | Unimplemented<br>(Read '0's)          |                                       | 0x02ABFE<br>0x02AC00             |

|                            |                                                    |                                       | Unimplemented<br>(Read '0's)          |                                  |

|                            |                                                    |                                       |                                       | 0x7FFFE<br>0x800000              |

| ry Space                   | Reserved                                           | Reserved                              | Reserved                              | 0×F7FFE                          |

| IOU                        | Device Configuration<br>Registers                  | <br>Device Configuration<br>Registers | <br>Device Configuration<br>Registers | 0xF80000                         |

| Configuration Memory Space | Reserved                                           | <br>Reserved                          | <br>Reserved                          | 0xF80017<br>0xF80010             |

|                            | DEVID (2)                                          | <br>DEVID (2)                         | <br>DEVID (2)                         | 0xFEFFFE<br>0xFF0000<br>0xFFFFFE |

#### FIGURE 4-1: PROGRAM MEMORY MAP FOR PIC24HJXXXGPX06A/X08A/X10A FAMILY DEVICES

### TABLE 4-24: PORTA REGISTER MAP<sup>(1)</sup>

|           |      |         |         |         |         |        | -       | -      |       |        | -      |        |        |        |        |        |        |               |

|-----------|------|---------|---------|---------|---------|--------|---------|--------|-------|--------|--------|--------|--------|--------|--------|--------|--------|---------------|

| File Name | Addr | Bit 15  | Bit 14  | Bit 13  | Bit 12  | Bit 11 | Bit 10  | Bit 9  | Bit 8 | Bit 7  | Bit 6  | Bit 5  | Bit 4  | Bit 3  | Bit 2  | Bit 1  | Bit 0  | All<br>Resets |

| TRISA     | 02C0 | TRISA15 | TRISA14 | TRISA13 | TRISA12 | —      | TRISA10 | TRISA9 | -     | TRISA7 | TRISA6 | TRISA5 | TRISA4 | TRISA3 | TRISA2 | TRISA1 | TRISA0 | F6FF          |

| PORTA     | 02C2 | RA15    | RA14    | RA13    | RA12    | _      | RA10    | RA9    | _     | RA7    | RA6    | RA5    | RA4    | RA3    | RA2    | RA1    | RA0    | xxxx          |

| LATA      | 02C4 | LATA15  | LATA14  | LATA13  | LATA12  | _      | LATA10  | LATA9  | _     | LATA7  | LATA6  | LATA5  | LATA4  | LATA3  | LATA2  | LATA1  | LATA0  | xxxx          |

| ODCA      | 06C0 | ODCA15  | ODCA14  | _       | _       |        | _       | _      | -     |        |        | ODCA5  | ODCA4  | ODCA3  | ODCA2  | ODCA1  | ODCA0  | 0000          |

Legend: x = unknown value on Reset, — = unimplemented, read as '0'. Reset values are shown in hexadecimal for PinHigh devices.

Note 1: The actual set of I/O port pins varies from one device to another. Please refer to the corresponding pinout diagrams.

### TABLE 4-25: PORTB REGISTER MAP<sup>(1)</sup>

| File Name | Addr | Bit 15  | Bit 14  | Bit 13  | Bit 12  | Bit 11  | Bit 10  | Bit 9  | Bit 8  | Bit 7  | Bit 6  | Bit 5  | Bit 4  | Bit 3  | Bit 2  | Bit 1  | Bit 0  | All<br>Resets |

|-----------|------|---------|---------|---------|---------|---------|---------|--------|--------|--------|--------|--------|--------|--------|--------|--------|--------|---------------|

| TRISB     | 02C6 | TRISB15 | TRISB14 | TRISB13 | TRISB12 | TRISB11 | TRISB10 | TRISB9 | TRISB8 | TRISB7 | TRISB6 | TRISB5 | TRISB4 | TRISB3 | TRISB2 | TRISB1 | TRISB0 | FFFF          |

| PORTB     | 02C8 | RB15    | RB14    | RB13    | RB12    | RB11    | RB10    | RB9    | RB8    | RB7    | RB6    | RB5    | RB4    | RB3    | RB2    | RB1    | RB0    | xxxx          |

| LATB      | 02CA | LATB15  | LATB14  | LATB13  | LATB12  | LATB11  | LATB10  | LATB9  | LATB8  | LATB7  | LATB6  | LATB5  | LATB4  | LATB3  | LATB2  | LATB1  | LATB0  | xxxx          |

Legend: x = unknown value on Reset, — = unimplemented, read as '0'. Reset values are shown in hexadecimal for PinHigh devices.

Note 1: The actual set of I/O port pins varies from one device to another. Please refer to the corresponding pinout diagrams.

### TABLE 4-26: PORTC REGISTER MAP<sup>(1)</sup>

| File Name | Addr | Bit 15  | Bit 14  | Bit 13  | Bit 12  | Bit 11 | Bit 10 | Bit 9 | Bit 8 | Bit 7 | Bit 6 | Bit 5 | Bit 4  | Bit 3  | Bit 2  | Bit 1  | Bit 0 | All<br>Resets |

|-----------|------|---------|---------|---------|---------|--------|--------|-------|-------|-------|-------|-------|--------|--------|--------|--------|-------|---------------|

| TRISC     | 02CC | TRISC15 | TRISC14 | TRISC13 | TRISC12 | _      | _      | —     | _     | _     | _     |       | TRISC4 | TRISC3 | TRISC2 | TRISC1 | —     | F01E          |

| PORTC     | 02CE | RC15    | RC14    | RC13    | RC12    | _      | —      | _     | _     | _     | _     | —     | RC4    | RC3    | RC2    | RC1    | —     | xxxx          |

| LATC      | 02D0 | LATC15  | LATC14  | LATC13  | LATC12  | _      | _      | _     | _     | _     | _     | -     | LATC4  | LATC3  | LATC2  | LATC1  | —     | xxxx          |

Legend: x = unknown value on Reset, — = unimplemented, read as '0'. Reset values are shown in hexadecimal for PinHigh devices.

Note 1: The actual set of I/O port pins varies from one device to another. Please refer to the corresponding pinout diagrams.

### TABLE 4-27: PORTD REGISTER MAP<sup>(1)</sup>

| File Name | Addr | Bit 15  | Bit 14  | Bit 13  | Bit 12  | Bit 11  | Bit 10  | Bit 9  | Bit 8  | Bit 7  | Bit 6  | Bit 5  | Bit 4  | Bit 3  | Bit 2  | Bit 1  | Bit 0  | All<br>Resets |

|-----------|------|---------|---------|---------|---------|---------|---------|--------|--------|--------|--------|--------|--------|--------|--------|--------|--------|---------------|

| TRISD     | 02D2 | TRISD15 | TRISD14 | TRISD13 | TRISD12 | TRISD11 | TRISD10 | TRISD9 | TRISD8 | TRISD7 | TRISD6 | TRISD5 | TRISD4 | TRISD3 | TRISD2 | TRISD1 | TRISD0 | FFFF          |

| PORTD     | 02D4 | RD15    | RD14    | RD13    | RD12    | RD11    | RD10    | RD9    | RD8    | RD7    | RD6    | RD5    | RD4    | RD3    | RD2    | RD1    | RD0    | xxxx          |

| LATD      | 02D6 | LATD15  | LATD14  | LATD13  | LATD12  | LATD11  | LATD10  | LATD9  | LATD8  | LATD7  | LATD6  | LATD5  | LATD4  | LATD3  | LATD2  | LATD1  | LATD0  | xxxx          |

| ODCD      | 06D2 | ODCD15  | ODCD14  | ODCD13  | ODCD12  | ODCD11  | ODCD10  | ODCD9  | ODCD8  | ODCD7  | ODCD6  | ODCD5  | ODCD4  | ODCD3  | ODCD2  | ODCD1  | ODCD0  | 0000          |

Legend: x = unknown value on Reset, - = unimplemented, read as '0'. Reset values are shown in hexadecimal for PinHigh devices.

Note 1: The actual set of I/O port pins varies from one device to another. Please refer to the corresponding pinout diagrams.

| Flag Bit          | Setting Event                                        | Clearing Event               |

|-------------------|------------------------------------------------------|------------------------------|

| TRAPR (RCON<15>)  | Trap conflict event                                  | POR, BOR                     |

| IOPUWR (RCON<14>) | Illegal opcode or uninitialized<br>W register access | POR, BOR                     |

| EXTR (RCON<7>)    | MCLR Reset                                           | POR                          |

| SWR (RCON<6>)     | RESET instruction                                    | POR, BOR                     |

| WDTO (RCON<4>)    | WDT time-out                                         | PWRSAV instruction, POR, BOR |

| SLEEP (RCON<3>)   | PWRSAV #SLEEP instruction                            | POR, BOR                     |

| IDLE (RCON<2>)    | PWRSAV #IDLE instruction                             | POR, BOR                     |

| BOR (RCON<1>)     | BOR, POR                                             | _                            |

| POR (RCON<0>)     | POR                                                  | _                            |

### TABLE 6-1:RESET FLAG BIT OPERATION

Note: All Reset flag bits may be set or cleared by the user software.

### 6.1 Clock Source Selection at Reset

If clock switching is enabled, the system clock source at device Reset is chosen, as shown in Table 6-2. If clock switching is disabled, the system clock source is always selected according to the oscillator Configuration bits. Refer to **Section 9.0** "Oscillator Configuration" for further details.

# TABLE 6-2:OSCILLATOR SELECTION vs.TYPE OF RESET (CLOCK<br/>SWITCHING ENABLED)

| Reset Type | Clock Source Determinant      |

|------------|-------------------------------|

| POR        | Oscillator Configuration bits |

| BOR        | (FNOSC<2:0>)                  |

| MCLR       | COSC Control bits             |

| WDTR       | (OSCCON<14:12>)               |

| SWR        | ]                             |

### 6.2 Device Reset Times

The Reset times for various types of device Reset are summarized in Table 6-3. The system Reset signal is released after the POR and PWRT delay times expire.

The time at which the device actually begins to execute code also depends on the system oscillator delays, which include the Oscillator Start-up Timer (OST) and the PLL lock time. The OST and PLL lock times occur in parallel with the applicable reset delay times.

The FSCM delay determines the time at which the FSCM begins to monitor the system clock source after the reset signal is released.

| R/W-0           | R/W-0           | R/W-0                            | R/W-0          | R/W-0            | R/W-0            | R/W-0          | R/W-0   |

|-----------------|-----------------|----------------------------------|----------------|------------------|------------------|----------------|---------|

| U2TXIF          | U2RXIF          | INT2IF                           | T5IF           | T4IF             | OC4IF            | OC3IF          | DMA21IF |

| bit 15          |                 | 1                                |                |                  |                  |                | bit 8   |

| R/W-0           | R/W-0           | R/W-0                            | R/W-0          | R/W-0            | U-0              | R/W-0          | R/W-0   |

| IC8IF           | IC7IF           | AD2IF                            | INT1IF         | CNIF             | _                | MI2C1IF        | SI2C1IF |

| bit 7           |                 |                                  |                |                  |                  |                | bit 0   |

| Legend:         |                 |                                  |                |                  |                  |                |         |

| R = Readable    | bit             | W = Writable                     | bit            | U = Unimpler     | mented bit, rea  | d as '0'       |         |

| -n = Value at F | POR             | '1' = Bit is set                 |                | '0' = Bit is cle | ared             | x = Bit is unk | nown    |

|                 |                 |                                  |                |                  |                  |                |         |

| bit 15          |                 | RT2 Transmitte                   | •              | g Status bit     |                  |                |         |

|                 |                 | request has oc<br>request has no |                |                  |                  |                |         |

| bit 14          |                 | RT2 Receiver li                  |                | Statue hit       |                  |                |         |

|                 |                 | request has oc                   |                |                  |                  |                |         |

|                 |                 | request has no                   |                |                  |                  |                |         |

| bit 13          | INT2IF: Exter   | nal Interrupt 2                  | Flag Status b  | it               |                  |                |         |

|                 |                 | request has oc<br>request has no |                |                  |                  |                |         |

| bit 12          | T5IF: Timer5    | Interrupt Flag                   | Status bit     |                  |                  |                |         |

|                 |                 | request has oc<br>request has no |                |                  |                  |                |         |

| bit 11          | T4IF: Timer4    | Interrupt Flag                   | Status bit     |                  |                  |                |         |

|                 |                 | request has oc<br>request has no |                |                  |                  |                |         |

| bit 10          | OC4IF: Outpu    | ut Compare Ch                    | annel 4 Interr | upt Flag Status  | s bit            |                |         |

|                 |                 | request has oc<br>request has no |                |                  |                  |                |         |

| bit 9           | OC3IF: Outpu    | ut Compare Ch                    | annel 3 Interr | upt Flag Status  | s bit            |                |         |

|                 |                 | request has oc<br>request has no |                |                  |                  |                |         |

| bit 8           | •               | •                                |                | Complete Inte    | rrupt Flag Statu | ıs bit         |         |

|                 | 1 = Interrupt r | request has oc                   | curred         | ·                |                  |                |         |

| bit 7           | •               | request has no<br>Capture Chann  |                | Flag Status hit  |                  |                |         |

|                 |                 | request has oc                   | -              | nag otatus bit   |                  |                |         |

|                 |                 | equest has no                    |                |                  |                  |                |         |

| bit 6           |                 | Capture Chann                    |                | Flag Status bit  |                  |                |         |

|                 |                 | request has oc<br>request has no |                |                  |                  |                |         |

| bit 5           | •               | •                                |                | rupt Flag Statu  | s bit            |                |         |

|                 |                 | request has oc                   | -              | apt i lag oldtu  |                  |                |         |

|                 |                 | request has no                   |                |                  |                  |                |         |

| bit 4           | INT1IF: Exter   | nal Interrupt 1                  | Flag Status b  | it               |                  |                |         |

|                 |                 | equest has oc                    |                |                  |                  |                |         |

|                 | 0 = Interrupt r | request has no                   | toccurred      |                  |                  |                |         |

### REGISTER 7-27: IPC12: INTERRUPT PRIORITY CONTROL REGISTER 12

| U-0           | R/W-1                | R/W-0                                    | R/W-0           | U-0              | R/W-1            | R/W-0           | R/W-0  |

|---------------|----------------------|------------------------------------------|-----------------|------------------|------------------|-----------------|--------|

| _             |                      | T8IP<2:0>                                |                 | _                |                  | MI2C2IP<2:0>    |        |

| bit 15        |                      |                                          |                 |                  |                  |                 | bit    |

| U-0           | R/W-1                | R/W-0                                    | R/W-0           | U-0              | R/W-1            | R/W-0           | R/W-0  |

|               | 10,00-1              | SI2C2IP<2:0>                             | 10,00-0         |                  |                  | T7IP<2:0>       | 1000-0 |

| bit 7         |                      | 0120211 12:04                            |                 |                  |                  | 1111 -2.0-      | bit    |

|               |                      |                                          |                 |                  |                  |                 |        |

| Legend:       |                      |                                          |                 |                  |                  |                 |        |

| R = Readabl   | e bit                | W = Writable                             | bit             | U = Unimple      | mented bit, read | d as '0'        |        |

| -n = Value at | POR                  | '1' = Bit is set                         |                 | '0' = Bit is cle | ared             | x = Bit is unkr | nown   |

| bit 15        | Unimpleme            | ented: Read as '                         | 0'              |                  |                  |                 |        |

| bit 14-12     | -                    | Timer8 Interrupt                         |                 |                  |                  |                 |        |

|               |                      | rupt is priority 7 (                     | -               | y interrupt)     |                  |                 |        |

|               | •                    |                                          |                 |                  |                  |                 |        |

|               | •                    |                                          |                 |                  |                  |                 |        |

|               | 001 = Interi         | rupt is priority 1                       |                 |                  |                  |                 |        |

|               | 000 = Interi         | rupt source is dis                       | abled           |                  |                  |                 |        |

| bit 11        | Unimpleme            | ented: Read as '                         | 0'              |                  |                  |                 |        |

| bit 10-8      |                      | :0>: I2C2 Master                         |                 | •                | 6                |                 |        |

|               | 111 = Interi         | rupt is priority 7 (                     | highest priorit | y interrupt)     |                  |                 |        |

|               | •                    |                                          |                 |                  |                  |                 |        |

|               | •                    |                                          |                 |                  |                  |                 |        |

|               |                      | rupt is priority 1<br>rupt source is dis | abled           |                  |                  |                 |        |

| bit 7         |                      | ented: Read as '                         |                 |                  |                  |                 |        |

| bit 6-4       | -                    | :0>: I2C2 Slave E                        |                 | pt Priority bits |                  |                 |        |

|               |                      | rupt is priority 7 (I                    |                 | • •              |                  |                 |        |

|               | •                    |                                          |                 |                  |                  |                 |        |

|               | •                    |                                          |                 |                  |                  |                 |        |

|               | 001 = Interi         | rupt is priority 1                       |                 |                  |                  |                 |        |

|               | 000 <b>= Inter</b> i | rupt source is dis                       | abled           |                  |                  |                 |        |

| bit 3         | Unimpleme            | ented: Read as '                         | 0'              |                  |                  |                 |        |

| bit 2-0       |                      | Timer7 Interrupt                         | -               |                  |                  |                 |        |

|               | 111 = Interi         | rupt is priority 7 (I                    | highest priorit | y interrupt)     |                  |                 |        |

|               | •                    |                                          |                 |                  |                  |                 |        |

|               | •                    |                                          |                 |                  |                  |                 |        |

|               |                      | rupt is priority 1                       | a la la al      |                  |                  |                 |        |

|               | 000 = Interi         | rupt source is dis                       | abled           |                  |                  |                 |        |

| U-0          | R/W-1            | R/W-0                 | R/W-0          | U-0              | R/W-1           | R/W-0           | R/W-0 |

|--------------|------------------|-----------------------|----------------|------------------|-----------------|-----------------|-------|

| _            |                  | C2RXIP<2:0>           |                | _                |                 | INT4IP<2:0>     |       |

| bit 15       | •                |                       |                |                  | •               |                 | bit   |

|              |                  |                       |                |                  |                 |                 |       |

| U-0          | R/W-1            | R/W-0                 | R/W-0          | U-0              | R/W-1           | R/W-0           | R/W-0 |

|              |                  | INT3IP<2:0>           |                | —                |                 | T9IP<2:0>       |       |

| bit 7        |                  |                       |                |                  |                 |                 | bit   |

| Legend:      |                  |                       |                |                  |                 |                 |       |

| R = Readab   | le bit           | W = Writable          | bit            | U = Unimplei     | mented bit, rea | ad as '0'       |       |

| -n = Value a | t POR            | '1' = Bit is set      |                | '0' = Bit is cle | ared            | x = Bit is unkr | nown  |

|              |                  |                       |                |                  |                 |                 |       |

| bit 15       | -                | ented: Read as 'o     |                |                  |                 |                 |       |

| bit 14-12    |                  | :0>: ECAN2 Rece       |                |                  | iority bits     |                 |       |

|              | 111 = Inter      | rupt is priority 7 (I | highest priori | ty interrupt)    |                 |                 |       |

|              | •                |                       |                |                  |                 |                 |       |

|              | •                |                       |                |                  |                 |                 |       |

|              |                  | rupt is priority 1    |                |                  |                 |                 |       |

|              |                  | rupt source is dis    |                |                  |                 |                 |       |

| bit 11       | Unimpleme        | ented: Read as '      | כ'             |                  |                 |                 |       |

| bit 10-8     | INT4IP<2:0       | >: External Interr    | upt 4 Priority | bits             |                 |                 |       |

|              | 111 = Inter      | rupt is priority 7 (I | nighest priori | ty interrupt)    |                 |                 |       |

|              | •                |                       |                |                  |                 |                 |       |

|              | •                |                       |                |                  |                 |                 |       |

|              | 001 = Inter      | rupt is priority 1    |                |                  |                 |                 |       |

|              | 000 = Inter      | rupt source is dis    | abled          |                  |                 |                 |       |

| bit 7        | Unimpleme        | ented: Read as 'o     | o'             |                  |                 |                 |       |

| bit 6-4      | INT3IP<2:0       | >: External Interr    | upt 3 Priority | bits             |                 |                 |       |

|              | 111 = Inter      | rupt is priority 7 (I | highest priori | ty interrupt)    |                 |                 |       |

|              | •                |                       |                |                  |                 |                 |       |

|              | •                |                       |                |                  |                 |                 |       |

|              | 001 = Inter      | rupt is priority 1    |                |                  |                 |                 |       |

|              |                  | rupt source is dis    | abled          |                  |                 |                 |       |

| bit 3        | Unimpleme        | ented: Read as '      | o'             |                  |                 |                 |       |

| bit 2-0      | -                | Timer9 Interrupt      |                |                  |                 |                 |       |

|              |                  | rupt is priority 7 (I | -              | ty interrupt)    |                 |                 |       |

|              | •                |                       | 5              |                  |                 |                 |       |

|              | •                |                       |                |                  |                 |                 |       |

|              |                  |                       |                |                  |                 |                 |       |

|              | •<br>001 - Inter | rupt is priority 1    |                |                  |                 |                 |       |

### REGISTER 7-28: IPC13: INTERRUPT PRIORITY CONTROL REGISTER 13

### REGISTER 8-3: DMAXSTA: DMA CHANNEL x RAM START ADDRESS OFFSET REGISTER A

| R/W-0                              | R/W-0 | R/W-0          | R/W-0 | R/W-0            | R/W-0           | R/W-0           | R/W-0 |

|------------------------------------|-------|----------------|-------|------------------|-----------------|-----------------|-------|

|                                    |       |                | STA   | <15:8>           |                 |                 |       |

| bit 15                             |       |                |       |                  |                 |                 | bit 8 |

|                                    |       |                |       |                  |                 |                 |       |

| R/W-0                              | R/W-0 | R/W-0          | R/W-0 | R/W-0            | R/W-0           | R/W-0           | R/W-0 |

|                                    |       |                | STA   | <7:0>            |                 |                 |       |

| bit 7                              |       |                |       |                  |                 |                 | bit 0 |

|                                    |       |                |       |                  |                 |                 |       |

| Legend:                            |       |                |       |                  |                 |                 |       |

| R = Readable                       | bit   | W = Writable I | bit   | U = Unimpler     | nented bit, rea | d as '0'        |       |

| -n = Value at POR '1' = Bit is set |       |                |       | '0' = Bit is cle | ared            | x = Bit is unkr | nown  |

bit 15-0 STA<15:0>: Primary DMA RAM Start Address bits (source or destination)

#### REGISTER 8-4: DMAxSTB: DMA CHANNEL x RAM START ADDRESS OFFSET REGISTER B

| R/W-0                              | R/W-0 | R/W-0          | R/W-0 | R/W-0            | R/W-0           | R/W-0           | R/W-0 |

|------------------------------------|-------|----------------|-------|------------------|-----------------|-----------------|-------|

|                                    |       |                | STB   | <15:8>           |                 |                 |       |

| bit 15                             |       |                |       |                  |                 |                 | bit 8 |

|                                    |       |                |       |                  |                 |                 |       |

| R/W-0                              | R/W-0 | R/W-0          | R/W-0 | R/W-0            | R/W-0           | R/W-0           | R/W-0 |

|                                    |       |                | STE   | 3<7:0>           |                 |                 |       |

| bit 7                              |       |                |       |                  |                 |                 | bit 0 |

| Legend:                            |       |                |       |                  |                 |                 |       |

| R = Readable                       | bit   | W = Writable b | it    | U = Unimpler     | mented bit, rea | ad as '0'       |       |

| -n = Value at POR '1' = Bit is set |       |                |       | '0' = Bit is cle | ared            | x = Bit is unkı | nown  |

bit 15-0 STB<15:0>: Secondary DMA RAM Start Address bits (source or destination)

NOTES:

### 11.6 I/O Helpful Tips

- 1. In some cases, certain pins as defined in TABLE 24-9: "DC Characteristics: I/O Pin Input Specifications" under "Injection Current", have internal protection diodes to VDD and Vss. The term "Injection Current" is also referred to as "Clamp Current". On designated pins, with sufficient external current limiting precautions by the user, I/O pin input voltages are allowed to be greater or less than the data sheet absolute maximum ratings with nominal VDD with respect to the VSS and VDD supplies. Note that when the user application forward biases either of the high or low side internal input clamp diodes, that the resulting current being injected into the device that is clamped internally by the VDD and VSS power rails, may affect the ADC accuracy by four to six counts.

- I/O pins that are shared with any analog input pin, 2. (i.e., ANx), are always analog pins by default after any reset. Consequently, any pin(s) configured as an analog input pin, automatically disables the digital input pin buffer. As such, any attempt to read a digital input pin will always return a '0' regardless of the digital logic level on the pin if the analog pin is configured. To use a pin as a digital I/O pin on a shared ANx pin, the user application needs to configure the analog pin configuration registers in the ADC module, (i.e., ADxPCFGL, AD1PCFGH), by setting the appropriate bit that corresponds to that I/O port pin to a '1'. On devices with more than one ADC, both analog pin configurations for both ADC modules must be configured as a digital I/O pin for that pin to function as a digital I/O pin.

- **Note:** Although it is not possible to use a digital input pin when its analog function is enabled, it is possible to use the digital I/O output function, TRISx = 0x0, while the analog function is also enabled. However, this is not recommended, particularly if the analog input is connected to an external analog voltage source, which would create signal contention between the analog signal and the output pin driver.

- 3. Most I/O pins have multiple functions. Referring to the device pin diagrams in the data sheet, the priorities of the functions allocated to any pins are indicated by reading the pin name from left-to-right. The left most function name takes precedence over any function to its right in the naming convention. For example: AN16/T2CK/T7CK/RC1. This indicates that AN16 is the highest priority in this example and will supersede all other functions to its right in the list. Those other functions to its right, even if enabled, would not work as long as any other function to its left was enabled. This rule applies to all of the functions listed for a given pin.

- 4. Each CN pin has a configurable internal weak pull-up resistor. The pull-ups act as a current source connected to the pin, and eliminates the need for external resistors in certain applications. The internal pull-up is to ~(VDD-0.8) not VDD. This is still above the minimum VIH of CMOS and TTL devices.

- 5. When driving LEDs directly, the I/O pin can source or sink more current than what is specified in the VOH/IOH and VOL/IOL DC characteristic specification. The respective IOH and IOL current rating only applies to maintaining the corresponding output at or above the VOH and at or below the VOL levels. However, for LEDs unlike digital inputs of an externally connected device, they are not governed by the same minimum VIH/VIL levels. An I/O pin output can safely sink or source any current less than that listed in the absolute maximum rating section of the data sheet. For example:

VOH = 2.4v @ IOH = -8 mA and VDD = 3.3V

The maximum output current sourced by any 8 mA I/O pin = 12 mA.

LED source current < 12 mA is technically permitted. Refer to the VOH/IOH graphs in Section 24.0 "Electrical Characteristics" for additional information.

### 11.7 I/O Resources

Many useful resources related to I/O are provided on the main product page of the Microchip web site for the devices listed in this data sheet. This product page, which can be accessed using this link, contains the latest updates and additional information.

Note: In the event you are not able to access the product page using the link above, enter this URL in your browser: http://www.microchip.com/wwwproducts/ Devices.aspx?dDocName=en546061

### 11.7.1 KEY RESOURCES

- Section 10. "I/O Ports" (DS70193)

- Code Samples

- Application Notes

- Software Libraries

- Webinars

- All related dsPIC33F/PIC24H Family Reference Manuals Sections

- Development Tools

| R/W-0         | U-0                               | R/W-0           | U-0            | U-0                    | U-0             | U-0                | U-0 |

|---------------|-----------------------------------|-----------------|----------------|------------------------|-----------------|--------------------|-----|

| TON           |                                   | TSIDL           |                | —                      | _               | —                  |     |

| bit 15        |                                   |                 |                |                        |                 |                    | bit |

| U-0           | R/W-0                             | R/W-0           | R/W-0          | R/W-0                  | U-0             | R/W-0              | U-0 |

| 0-0           | TGATE                             | 1               | S<1:0>         | T32                    | 0-0             | TCS <sup>(1)</sup> | 0-0 |

| <br>bit 7     | IGAIE                             | TCKP            | 5<1.0>         | 132                    | _               | 1030               | bit |

|               |                                   |                 |                |                        |                 |                    |     |

| Legend:       |                                   |                 |                |                        |                 |                    |     |

| R = Readable  | e bit                             | W = Writable    | bit            | U = Unimplem           | nented bit, rea | d as '0'           |     |

| -n = Value at | POR                               | '1' = Bit is se | t              | '0' = Bit is clea      | ared            | x = Bit is unkno   | own |

| bit 15        | TON: Timerx                       | On bit          |                |                        |                 |                    |     |

|               | When T32 = 1                      | L:              |                |                        |                 |                    |     |

|               | 1 = Starts 32-<br>0 = Stops 32-   |                 |                |                        |                 |                    |     |

|               | <u>When T32 = 0</u>               |                 |                |                        |                 |                    |     |

|               | 1 = Starts 16-<br>0 = Stops 16-   |                 |                |                        |                 |                    |     |

| bit 14        | Unimplemen                        |                 | ٠́ ()'         |                        |                 |                    |     |

| bit 13        | TSIDL: Stop i                     |                 |                |                        |                 |                    |     |

|               | •                                 | ue module ope   | eration when d | evice enters Idl<br>de | e mode          |                    |     |

| bit 12-7      | Unimplemen                        | -               |                |                        |                 |                    |     |

| bit 6         | TGATE: Time                       | rx Gated Time   | e Accumulatior | n Enable bit           |                 |                    |     |

|               | When TCS =                        |                 |                |                        |                 |                    |     |

|               | This bit is igno                  |                 |                |                        |                 |                    |     |

|               | When TCS =<br>1 = Gated tim       |                 | n enabled      |                        |                 |                    |     |

|               | 0 = Gated tim                     |                 |                |                        |                 |                    |     |

| bit 5-4       | TCKPS<1:0>                        | : Timerx Input  | Clock Presca   | le Select bits         |                 |                    |     |

|               | 11 = 1:256                        |                 |                |                        |                 |                    |     |

|               | 10 = 1:64                         |                 |                |                        |                 |                    |     |

|               | 01 = 1:8<br>00 = 1:1              |                 |                |                        |                 |                    |     |

| bit 3         | T32: 32-bit Ti                    | mer Mode Sel    | ect bit        |                        |                 |                    |     |

|               | 1 = Timerx an<br>0 = Timerx an    |                 |                |                        |                 |                    |     |

| bit 2         | Unimplemen                        | -               |                |                        |                 |                    |     |

| bit 1         | TCS: Timerx                       |                 |                |                        |                 |                    |     |

|               | 1 = External c<br>0 = Internal cl | clock from pin  |                | rising edge)           |                 |                    |     |

|               |                                   | · · /           |                |                        |                 |                    |     |

### REGISTER 13-1: TxCON (T2CON, T4CON, T6CON OR T8CON) CONTROL REGISTER

Note 1: The TxCK pin is not available on all timers. Refer to the "Pin Diagrams" section for the available pins.

### REGISTER 19-8: CIEC: ECAN™ MODULE TRANSMIT/RECEIVE ERROR COUNT REGISTER

| R-0                                | R-0 | R-0            | R-0  | R-0               | R-0            | R-0             | R-0   |

|------------------------------------|-----|----------------|------|-------------------|----------------|-----------------|-------|

|                                    |     |                | TERR | CNT<7:0>          |                |                 |       |

| bit 15                             |     |                |      |                   |                |                 | bit 8 |

| R-0                                | R-0 | R-0            | R-0  | R-0               | R-0            | R-0             | R-0   |

|                                    |     |                | RERR | CNT<7:0>          |                |                 |       |

| bit 7                              |     |                |      |                   |                |                 | bit 0 |

| Legend:                            |     |                |      |                   |                |                 |       |

| R = Readable b                     | oit | W = Writable b | bit  | U = Unimplen      | nented bit, re | ad as '0'       |       |

| -n = Value at POR '1' = Bit is set |     |                |      | '0' = Bit is clea | ared           | x = Bit is unkr | nown  |

bit 15-8 TERRCNT<7:0>: Transmit Error Count bits

bit 7-0 RERRCNT<7:0>: Receive Error Count bits

## REGISTER 19-31: CITRBnSTAT: ECAN™ MODULE RECEIVE BUFFER n STATUS

|                | (n = 0, | 1,, 31)                                             |             |       |       |       |       |  |

|----------------|---------|-----------------------------------------------------|-------------|-------|-------|-------|-------|--|

| U-0            | U-0     | U-0                                                 | R/W-x       | R/W-x | R/W-x | R/W-x | R/W-x |  |

| —              | —       | —                                                   | FILHIT<4:0> |       |       |       |       |  |

| bit 15         |         |                                                     |             |       |       |       | bit 8 |  |

|                |         |                                                     |             |       |       |       |       |  |

| U-0            | U-0     | U-0                                                 | U-0         | U-0   | U-0   | U-0   | U-0   |  |

|                |         |                                                     | _           | —     | —     | —     |       |  |

| bit 7          |         |                                                     |             |       |       |       | bit 0 |  |

|                |         |                                                     |             |       |       |       |       |  |

| Legend:        |         |                                                     |             |       |       |       |       |  |

| R = Readable I | bit     | W = Writable bit U = Unimplemented bit, read as '0' |             |       |       |       |       |  |

bit 15-13 **Unimplemented:** Read as '0'

-n = Value at POR

'1' = Bit is set

bit 12-8 **FILHIT<4:0>:** Filter Hit Code bits (only written by module for receive buffers, unused for transmit buffers) Encodes number of filter that resulted in writing this buffer.

'0' = Bit is cleared

bit 7-0 Unimplemented: Read as '0'

x = Bit is unknown

| REGISTER     | 20-5. ADXC    | 13123: ADC)      |                | ANNEL $I, Z,$    | SELECT RE                       | GIGIER         |         |

|--------------|---------------|------------------|----------------|------------------|---------------------------------|----------------|---------|

| U-0          | U-0           | U-0              | U-0            | U-0              | R/W-0                           | R/W-0          | R/W-0   |

| _            | —             | _                | _              | —                | CH123N                          | NB<1:0>        | CH123SB |

| bit 15       |               |                  |                |                  |                                 |                | bit 8   |

|              |               |                  |                |                  |                                 |                |         |

| U-0          | U-0           | U-0              | U-0            | U-0              | R/W-0                           | R/W-0          | R/W-0   |

| _            |               |                  | _              |                  | CH123N                          | VA<1:0>        | CH123SA |

| bit 7        |               |                  |                |                  |                                 |                | bit 0   |

|              |               |                  |                |                  |                                 |                |         |

| Legend:      |               |                  |                |                  |                                 |                |         |

| R = Readab   | ole bit       | W = Writable     | bit            | U = Unimple      | mented bit, read                | d as '0'       |         |

| -n = Value a | It POR        | '1' = Bit is set |                | '0' = Bit is cle | eared                           | x = Bit is unl | known   |

|              |               |                  |                |                  |                                 |                |         |

| bit 15-11    | -             | ted: Read as '   |                |                  |                                 |                |         |

| bit 10-9     |               |                  | •              | •                | or Sample B bit                 | S              |         |

|              |               | B = 1, CHxNB i   |                |                  |                                 | 1              | N144    |

|              |               | , ,              | · U            |                  | N10, CH3 nega<br>N7, CH3 negati |                |         |

|              | -             | I2, CH3 negati   | -              |                  | intr, en le negati              |                |         |

| bit 8        |               | nannel 1, 2, 3 F | •              |                  | ple B bit                       |                |         |

|              | When AD12E    | s = 1, CHxSB i   | s: U-0, Unim   | plemented, Re    | ad as '0'                       |                |         |

|              |               |                  | · ·            |                  | , CH3 positive i                |                |         |

|              | •             | •                | •              | e input is AN1   | , CH3 positive i                | nput is AN2    |         |

| bit 7-3      | •             | ted: Read as '   |                |                  |                                 |                |         |

| bit 2-1      |               |                  | •              | •                | or Sample A bit                 | S              |         |

|              |               | B = 1, CHxNA i   |                |                  |                                 |                |         |

|              |               | , ,              | · U            |                  | N10, CH3 nega<br>N7, CH3 negati |                |         |

|              |               | I2, CH3 negati   |                |                  | in, cho negati                  |                | 10      |

| bit 0        |               | nannel 1, 2, 3 F | •              |                  | ple A bit                       |                |         |

| -            |               | B = 1, CHxSA i   | •              |                  | •                               |                |         |

|              | 1 = CH1 posit | ive input is AN  | 3, CH2 positiv | e input is AN4   | , CH3 positive i                |                |         |

|              | 0 = CH1 posit | ive input is AN  | 0, CH2 positiv | e input is AN1   | , CH3 positive i                | nput is AN2    |         |

|              |               |                  |                |                  |                                 |                |         |

### REGISTER 20-5: ADxCHS123: ADCx INPUT CHANNEL 1, 2, 3 SELECT REGISTER

### **REGISTER 20-10:** ADxPCFGL: ADCx PORT CONFIGURATION REGISTER LOW<sup>(1,2,3,4)</sup>

| PCFG15         PCFG14         PCFG13         PCFG12         PCFG11         PCFG10         PCFG9         PCFG8           bit 15         bit 8 | R/W-0  | R/W-0  | R/W-0  | R/W-0  | R/W-0  | R/W-0  | R/W-0 | R/W-0 |

|----------------------------------------------------------------------------------------------------------------------------------------------|--------|--------|--------|--------|--------|--------|-------|-------|

| bit 15 bit 8                                                                                                                                 | PCFG15 | PCFG14 | PCFG13 | PCFG12 | PCFG11 | PCFG10 | PCFG9 | PCFG8 |

|                                                                                                                                              | bit 15 |        |        |        |        |        |       | bit 8 |

| R/W-0 |

|-------|-------|-------|-------|-------|-------|-------|-------|

| PCFG7 | PCFG6 | PCFG5 | PCFG4 | PCFG3 | PCFG2 | PCFG1 | PCFG0 |

| bit 7 |       |       |       |       |       |       | bit 0 |

| Legend:           |                  |                            |                    |

|-------------------|------------------|----------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, rea | d as '0'           |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared       | x = Bit is unknown |

bit 15-0 PCFG<15:0>: ADC Port Configuration Control bits

1 = Port pin in Digital mode, port read input enabled, ADC input multiplexer connected to AVss 0 = Port pin in Analog mode, port read input disabled, ADC samples pin voltage

- **Note 1:** On devices without 16 analog inputs, all PCFG bits are R/W by user. However, PCFG bits are ignored on ports without a corresponding input on device.

- 2: On devices with 2 analog-to-digital modules, both AD1PCFGL and AD2PCFGL will affect the configuration of port pins multiplexed with AN0-AN15.

- **3:** PCFGx = ANx, where x = 0 through 15.

- 4: PCFGx bits will have no effect if ADC module is disabled by setting ADxMD bit in the PMDx register. In this case all port pins multiplexed with ANx will be in Digital mode.

### TABLE 24-17: PLL CLOCK TIMING SPECIFICATIONS (VDD = 3.0V TO 3.6V)

| АС СНА       | AC CHARACTERISTICS |                                                                                    |                | $\begin{array}{llllllllllllllllllllllllllllllllllll$ |     |     |       |                              |  |

|--------------|--------------------|------------------------------------------------------------------------------------|----------------|------------------------------------------------------|-----|-----|-------|------------------------------|--|

| Param<br>No. | Symbol             | Characteris                                                                        | Characteristic |                                                      |     | Max | Units | Conditions                   |  |

| OS50         | Fplli              | PLL Voltage Controlled<br>Oscillator (VCO) Input<br>Frequency Range <sup>(2)</sup> |                | 0.8                                                  | _   | 8   | MHz   | ECPLL, HSPLL, XTPLL<br>modes |  |

| OS51         | Fsys               | On-Chip VCO System<br>Frequency                                                    |                | 100                                                  | —   | 200 | MHz   | _                            |  |

| OS52         | TLOCK              | PLL Start-up Time (Lock Time)                                                      |                | 0.9                                                  | 1.5 | 3.1 | mS    | —                            |  |

| OS53         | DCLK               | CLKO Stability (Jitter                                                             | .)             | -3                                                   | 0.5 | 3   | %     | Measured over 100 ms period  |  |

**Note 1:** Data in "Typ" column is at 3.3V, 25°C unless otherwise stated. Parameters are for design guidance only and are not tested.

2: These parameters are characterized by similarity but are not tested in manufacturing. This specification is based on clock cycle by clock cycle measurements. To calculate the effective jitter for individual time base or communication clocks used by peripherals use the formula:

Peripheral Clock Jitter = DCLK /  $\sqrt{(Fosc/Peripheral bit rate clock)}$

Example Only: Fosc = 80 MHz, DCLK = 3%, SPI bit rate clock, (i.e. SCK), is 5 MHz

SPI SCK Jitter = [ DCLK / \(\lambda(80 MHz/5 MHz))] = [3\(\lambda / 16] = [3\(\lambda / 4] = 0.75\)

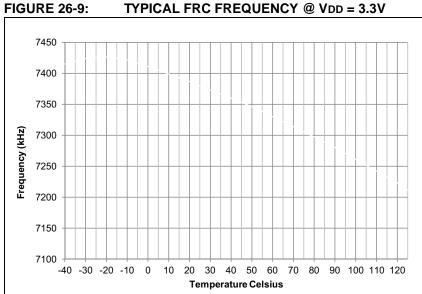

### TABLE 24-18: AC CHARACTERISTICS: INTERNAL FRC ACCURACY

| AC CHA       | RACTERISTICS                                      | $\begin{array}{llllllllllllllllllllllllllllllllllll$ |     |     |       |                                          |                |  |  |

|--------------|---------------------------------------------------|------------------------------------------------------|-----|-----|-------|------------------------------------------|----------------|--|--|

| Param<br>No. | Characteristic                                    | Min                                                  | Тур | Max | Units | Conditions                               |                |  |  |

|              | Internal FRC Accuracy @ 7.3728 MHz <sup>(1)</sup> |                                                      |     |     |       |                                          |                |  |  |

| F20a         | FRC                                               | -2                                                   | _   | +2  | %     | $-40^{\circ}C \leq TA \leq +85^{\circ}C$ | VDD = 3.0-3.6V |  |  |

| F20b         | FRC                                               | -5                                                   | _   | +5  | %     | $-40^\circ C \le T A \le +125^\circ C$   | VDD = 3.0-3.6V |  |  |

Note 1: Frequency calibrated at 25°C and 3.3V. TUN bits can be used to compensate for temperature drift.

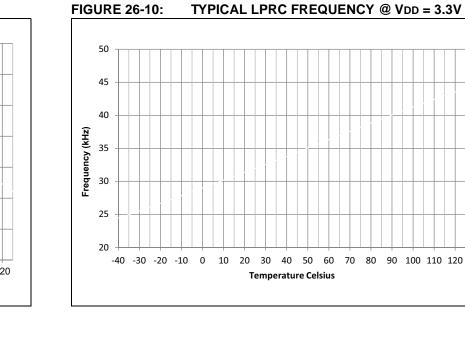

#### TABLE 24-19: INTERNAL LPRC ACCURACY

| AC CH        | ARACTERISTICS                    | $\begin{array}{llllllllllllllllllllllllllllllllllll$ |     |     |       |                                        |   |  |

|--------------|----------------------------------|------------------------------------------------------|-----|-----|-------|----------------------------------------|---|--|

| Param<br>No. | Characteristic                   | Min                                                  | Тур | Max | Units | Conditions                             |   |  |

|              | LPRC @ 32.768 kHz <sup>(1)</sup> |                                                      |     |     |       |                                        |   |  |

| F21a         | LPRC                             | -30                                                  | _   | +30 | %     | $-40^\circ C \le T A \le +85^\circ C$  | — |  |

| F21b         | LPRC                             | -35                                                  | —   | +35 | %     | $-40^\circ C \le T A \le +125^\circ C$ | _ |  |

**Note 1:** Change of LPRC frequency as VDD changes.

# TABLE 24-21: RESET, WATCHDOG TIMER, OSCILLATOR START-UP TIMER, POWER-UP TIMER TIMING REQUIREMENTS

| AC CHARACTERISTICS |        |                                                                |      | $\begin{array}{l} \mbox{Standard Operating Conditions: 3.0V to 3.6V} \\ \mbox{(unless otherwise stated)} \\ \mbox{Operating temperature} & -40^\circ C \leq TA \leq +85^\circ C \mbox{ for Industrial} \\ & -40^\circ C \leq TA \leq +125^\circ C \mbox{ for Extended} \end{array}$ |     |       |                                                                                        |  |  |

|--------------------|--------|----------------------------------------------------------------|------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|-------|----------------------------------------------------------------------------------------|--|--|

| Param<br>No.       | Symbol | Characteristic <sup>(1)</sup>                                  | Min  | Тур <sup>(2)</sup>                                                                                                                                                                                                                                                                  | Max | Units | Conditions                                                                             |  |  |

| SY10               | ТмсL   | MCLR Pulse Width (low)                                         | 2    | _                                                                                                                                                                                                                                                                                   |     | μS    | -40°C to +85°C                                                                         |  |  |

| SY11               | Tpwrt  | Power-up Timer Period                                          | _    | 2<br>4<br>8<br>16<br>32<br>64<br>128                                                                                                                                                                                                                                                | _   | ms    | -40°C to +85°C<br>User programmable                                                    |  |  |

| SY12               | TPOR   | Power-on Reset Delay                                           | 3    | 10                                                                                                                                                                                                                                                                                  | 30  | μS    | -40°C to +85°C                                                                         |  |  |

| SY13               | Tioz   | I/O High-Impedance from<br>MCLR Low or Watchdog<br>Timer Reset | 0.68 | 0.72                                                                                                                                                                                                                                                                                | 1.2 | μS    | _                                                                                      |  |  |

| SY20               | Twdt1  | Watchdog Timer Time-out<br>Period                              | —    | _                                                                                                                                                                                                                                                                                   | —   | —     | See Section 21.4 "Watchdog<br>Timer (WDT)" and LPRC<br>specification F21 (Table 24-19) |  |  |