Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFI

| Details                    |                                                                                  |

|----------------------------|----------------------------------------------------------------------------------|

| Product Status             | Active                                                                           |

| Core Processor             | PIC                                                                              |

| Core Size                  | 16-Bit                                                                           |

| Speed                      | 40 MIPs                                                                          |

| Connectivity               | I²C, IrDA, LINbus, SPI, UART/USART                                               |

| Peripherals                | Brown-out Detect/Reset, DMA, POR, PWM, WDT                                       |

| Number of I/O              | 53                                                                               |

| Program Memory Size        | 256KB (85.5K x 24)                                                               |

| Program Memory Type        | FLASH                                                                            |

| EEPROM Size                |                                                                                  |

| RAM Size                   | 16K x 8                                                                          |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 3.6V                                                                        |

| Data Converters            | A/D 18x10b/12b                                                                   |

| Oscillator Type            | Internal                                                                         |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                                |

| Mounting Type              | Surface Mount                                                                    |

| Package / Case             | 64-TQFP                                                                          |

| Supplier Device Package    | 64-TQFP (10x10)                                                                  |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic24hj256gp206at-i-pt |

|                            |                                                                                  |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

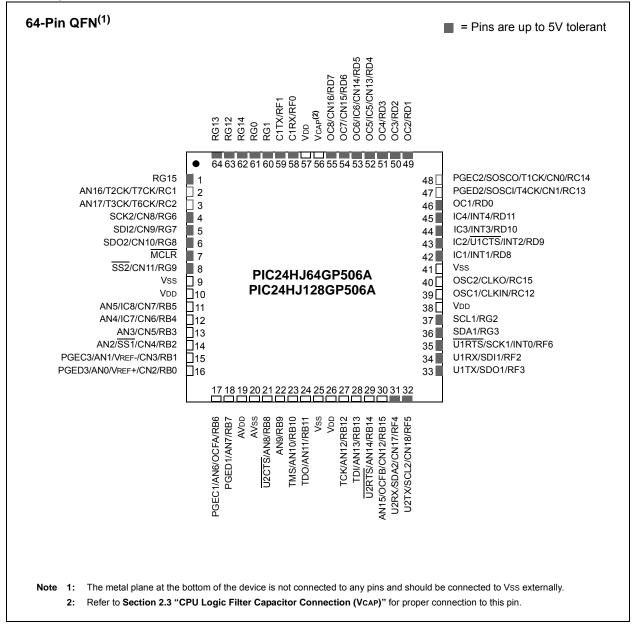

#### **Pin Diagrams (Continued)**

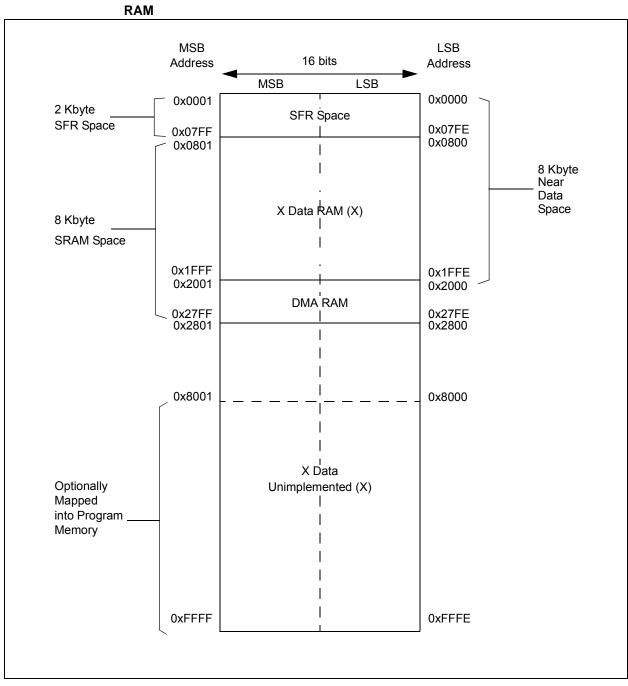

#### FIGURE 4-3: DATA MEMORY MAP FOR PIC24HJXXXGPX06A/X08A/X10A DEVICES WITH 8 KB

#### TABLE 4-17: DMA REGISTER MAP

| File Name | -17:<br>Addr | Bit 15 | Bit 14 | Bit 13 | Bit 12 | Bit 11 | Bit 10 | Bit 9 | Bit 8 | Bit 7    | Bit 6 | Bit 5 | Bit 4  | Bit 3     | Bit 2 | Bit 1 | Bit 0 | All    |

|-----------|--------------|--------|--------|--------|--------|--------|--------|-------|-------|----------|-------|-------|--------|-----------|-------|-------|-------|--------|

|           |              |        |        |        |        |        |        |       |       |          |       |       |        |           |       |       |       | Resets |

| DMA0CON   | 0380         | CHEN   | SIZE   | DIR    | HALF   | NULLW  | _      |       |       |          | _     | AMOD  |        | —         | —     | MODE  | <1:0> | 0000   |

| DMA0REQ   | 0382         | FORCE  | —      | —      |        | —      | —      |       |       | —        |       |       |        | RQSEL<6:0 | >     |       |       | 0000   |

| DMA0STA   | 0384         |        |        |        |        |        |        |       |       | TA<15:0> |       |       |        |           |       |       |       | 0000   |

| DMA0STB   | 0386         |        |        |        |        |        |        |       |       | TB<15:0> |       |       |        |           |       |       |       | 0000   |

| DMA0PAD   | 0388         |        |        |        |        |        |        | r     | P     | AD<15:0> |       |       |        |           |       |       |       | 0000   |

| DMA0CNT   | 038A         | _      |        | —      | —      | —      | —      |       |       |          |       |       | <9:0>  | -         |       | r     |       | 0000   |

| DMA1CON   | 038C         | CHEN   | SIZE   | DIR    | HALF   | NULLW  | _      |       |       | _        |       | AMOD  |        | _         | —     | MODE  | <1:0> | 0000   |

| DMA1REQ   | 038E         | FORCE  | —      | —      |        | —      | —      |       |       | —        |       |       | I      | RQSEL<6:0 | >     |       |       | 0000   |

| DMA1STA   | 0390         |        |        |        |        |        |        |       | S     | TA<15:0> |       |       |        |           |       |       |       | 0000   |

| DMA1STB   | 0392         |        |        |        |        |        |        |       | S     | TB<15:0> |       |       |        |           |       |       |       | 0000   |

| DMA1PAD   | 0394         |        |        |        |        |        |        | 1     | P     | AD<15:0> |       |       |        |           |       |       |       | 0000   |

| DMA1CNT   | 0396         | —      | —      | —      | —      | —      | —      |       |       |          |       | CNT   | <9:0>  | T         |       |       |       | 0000   |

| DMA2CON   | 0398         | CHEN   | SIZE   | DIR    | HALF   | NULLW  | _      |       |       | _        | _     | AMOD  | E<1:0> | —         | —     | MODE  | <1:0> | 0000   |

| DMA2REQ   | 039A         | FORCE  | —      | —      |        | —      | —      |       |       | —        |       |       |        | RQSEL<6:0 | >     |       |       | 0000   |

| DMA2STA   | 039C         |        |        |        |        |        |        |       | S     | TA<15:0> |       |       |        |           |       |       |       | 0000   |

| DMA2STB   | 039E         |        |        |        |        |        |        |       | S     | TB<15:0> |       |       |        |           |       |       |       | 0000   |

| DMA2PAD   | 03A0         |        |        |        |        |        |        |       | Р     | AD<15:0> |       |       |        |           |       |       |       | 0000   |

| DMA2CNT   | 03A2         | —      | —      | —      | —      | —      | —      |       |       |          |       | CNT   | <9:0>  |           |       |       |       | 0000   |

| DMA3CON   | 03A4         | CHEN   | SIZE   | DIR    | HALF   | NULLW  | —      | —     | —     | —        | —     | AMOD  | E<1:0> | —         | —     | MODE  | <1:0> | 0000   |

| DMA3REQ   | 03A6         | FORCE  | —      | —      | —      | —      | —      | —     | —     | —        |       |       | I      | RQSEL<6:0 | >     |       |       | 0000   |

| DMA3STA   | 03A8         |        |        |        |        |        |        |       | S     | TA<15:0> |       |       |        |           |       |       |       | 0000   |

| DMA3STB   | 03AA         |        |        |        |        |        |        |       | S     | TB<15:0> |       |       |        |           |       |       |       | 0000   |

| DMA3PAD   | 03AC         |        |        |        |        |        |        |       | Р     | AD<15:0> |       |       |        |           |       |       |       | 0000   |

| DMA3CNT   | 03AE         | -      | -      | _      | _      | _      | _      |       |       |          |       | CNT   | <9:0>  |           |       |       |       | 0000   |

| DMA4CON   | 03B0         | CHEN   | SIZE   | DIR    | HALF   | NULLW  | _      | _     | _     | —        | _     | AMOD  | E<1:0> | _         | —     | MODE  | <1:0> | 0000   |

| DMA4REQ   | 03B2         | FORCE  | _      | _      | _      | _      | _      | _     | _     | _        |       |       | I      | RQSEL<6:0 | >     |       |       | 0000   |

| DMA4STA   | 03B4         |        |        |        |        |        |        |       | S     | TA<15:0> |       |       |        |           |       |       |       | 0000   |

| DMA4STB   | 03B6         |        |        |        |        |        |        |       | S     | TB<15:0> |       |       |        |           |       |       |       | 0000   |

| DMA4PAD   | 03B8         |        |        |        |        |        |        |       | Р     | AD<15:0> |       |       |        |           |       |       |       | 0000   |

| DMA4CNT   | 03BA         | _      | _      | _      | —      | _      | _      |       |       |          |       | CNT   | <9:0>  |           |       |       |       | 0000   |

| DMA5CON   | 03BC         | CHEN   | SIZE   | DIR    | HALF   | NULLW  | _      | —     | —     | —        | —     | AMOD  | E<1:0> | —         | _     | MODE  | <1:0> | 0000   |

| DMA5REQ   | 03BE         | FORCE  | _      | _      | —      | _      | _      | _     | _     | _        |       | •     | I      | RQSEL<6:0 | >     |       |       | 0000   |

| DMA5STA   | 03C0         |        |        |        |        |        |        |       | S     | TA<15:0> |       |       |        |           |       |       |       | 0000   |

| DMA5STB   | 03C2         |        |        |        |        |        |        |       | S     | TB<15:0> |       |       |        |           |       |       |       | 0000   |

Legend: — = unimplemented, read as '0'. Reset values are shown in hexadecimal for PinHigh devices.

#### 7.0 INTERRUPT CONTROLLER

- **Note 1:** This data sheet summarizes the features of the PIC24HJXXXGPX06A/X08A/X10A family of devices. However, it is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to Section 6. "Interrupts" (DS70184) of the "dsPIC33F/PIC24H Familv Reference Manual", which is available from the Microchip web site (www.microchip.com).

- 2: Some registers and associated bits described in this section may not be available on all devices. Refer to Section 4.0 "Memory Organization" in this data sheet for device-specific register and bit information.

The PIC24HJXXXGPX06A/X08A/X10A interrupt controller reduces the numerous peripheral interrupt request signals to a single interrupt request signal to the PIC24HJXXXGPX06A/X08A/X10A CPU. It has the following features:

- · Up to 8 processor exceptions and software traps

- 7 user-selectable priority levels

- Interrupt Vector Table (IVT) with up to 118 vectors

- A unique vector for each interrupt or exception source

- · Fixed priority within a specified user priority level

- Alternate Interrupt Vector Table (AIVT) for debug support

- Fixed interrupt entry and return latencies

#### 7.1 Interrupt Vector Table

The Interrupt Vector Table (IVT) is shown in Figure 7-1. The IVT resides in program memory, starting at location 000004h. The IVT contains 126 vectors consisting of 8 nonmaskable trap vectors plus up to 118 sources of interrupt. In general, each interrupt source has its own vector. Each interrupt vector contains a 24-bit wide address. The value programmed into each interrupt vector location is the starting address of the associated Interrupt Service Routine (ISR).

Interrupt vectors are prioritized in terms of their natural priority; this priority is linked to their position in the vector table. All other things being equal, lower addresses have a higher natural priority. For example, the interrupt associated with vector 0 will take priority over interrupts at any other vector address.

PIC24HJXXXGPX06A/X08A/X10A devices implement up to 61 unique interrupts and 5 nonmaskable traps. These are summarized in Table 7-1 and Table 7-2.

#### 7.1.1 ALTERNATE VECTOR TABLE

The Alternate Interrupt Vector Table (AIVT) is located after the IVT, as shown in Figure 7-1. Access to the AIVT is provided by the ALTIVT control bit (INTCON2<15>). If the ALTIVT bit is set, all interrupt and exception processes use the alternate vectors instead of the default vectors. The alternate vectors are organized in the same manner as the default vectors.

The AIVT supports debugging by providing a means to switch between an application and a support environment without requiring the interrupt vectors to be reprogrammed. This feature also enables switching between applications for evaluation of different software algorithms at run time. If the AIVT is not needed, the AIVT should be programmed with the same addresses used in the IVT.

#### 7.2 Reset Sequence

A device Reset is not a true exception because the interrupt controller is not involved in the Reset process. The PIC24HJXXXGPX06A/X08A/X10A device clears its registers in response to a Reset which forces the PC to zero. The digital signal controller then begins program execution at location 0x000000. The user programs a GOTO instruction at the Reset address which redirects program execution to the appropriate start-up routine.

**Note:** Any unimplemented or unused vector locations in the IVT and AIVT should be programmed with the address of a default interrupt handler routine that contains a RESET instruction.

#### REGISTER 7-12: IEC2: INTERRUPT ENABLE CONTROL REGISTER 2

| R/W-0         | R/W-0           | U-0                             | R/W-0          | R/W-0            | R/W-0            | R/W-0           | R/W-0   |

|---------------|-----------------|---------------------------------|----------------|------------------|------------------|-----------------|---------|

| T6IE          | DMA4IE          | —                               | OC8IE          | OC7IE            | OC6IE            | OC5IE           | IC6IE   |

| bit 15        |                 |                                 |                |                  | •                |                 | bit 8   |

| R/W-0         | R/W-0           | R/W-0                           | R/W-0          | R/W-0            | R/W-0            | R/W-0           | R/W-0   |

| IC5IE         | IC4IE           | IC3IE                           | DMA3IE         | C1IE             | C1RXIE           | SPI2IE          | SPI2EIE |

| bit 7         |                 |                                 |                | 0                |                  |                 | bit (   |

| Legend:       |                 |                                 |                |                  |                  |                 |         |

| R = Readable  | e bit           | W = Writable                    | bit            | U = Unimpler     | mented bit, read | l as '0'        |         |

| -n = Value at | POR             | '1' = Bit is set                |                | '0' = Bit is cle | eared            | x = Bit is unki | nown    |

| bit 15        | T6IE: Timer6    | Interrupt Enabl                 | e bit          |                  |                  |                 |         |

|               |                 | request enable                  |                |                  |                  |                 |         |

|               | 0 = Interrupt r | equest not ena                  | bled           |                  |                  |                 |         |

| bit 14        |                 | A Channel 4 D                   |                | Complete Interi  | rupt Enable bit  |                 |         |

|               |                 | equest enable<br>equest not ena |                |                  |                  |                 |         |

| bit 13        | •               | ted: Read as '                  |                |                  |                  |                 |         |

| bit 12        | •               | ut Compare Ch                   |                | unt Enable bit   |                  |                 |         |

| 511 12        | •               | request enable                  |                |                  |                  |                 |         |

|               |                 | equest not ena                  |                |                  |                  |                 |         |

| bit 11        | OC7IE: Outpu    | ut Compare Ch                   | annel 7 Interr | upt Enable bit   |                  |                 |         |

|               |                 | equest enable<br>equest not ena |                |                  |                  |                 |         |

| bit 10        | OC6IE: Outpu    | ut Compare Ch                   | annel 6 Interr | upt Enable bit   |                  |                 |         |

|               |                 | equest enable<br>equest not ena |                |                  |                  |                 |         |

| bit 9         | OC5IE: Outpu    | ut Compare Ch                   | annel 5 Interr | upt Enable bit   |                  |                 |         |

|               |                 | equest enable<br>equest not ena |                |                  |                  |                 |         |

| bit 8         |                 | Capture Channe                  |                | Enable bit       |                  |                 |         |

|               |                 | equest enable<br>equest not ena |                |                  |                  |                 |         |

| bit 7         |                 | Capture Channe                  |                | Enable bit       |                  |                 |         |

|               | -               | equest enable                   |                |                  |                  |                 |         |

|               | •               | request not ena                 |                |                  |                  |                 |         |

| bit 6         | -               | Capture Channe                  |                | Enable bit       |                  |                 |         |

|               |                 | equest enable<br>equest not ena |                |                  |                  |                 |         |

| bit 5         | •               | Capture Channe                  |                | -nable bit       |                  |                 |         |

|               | -               | equest enable                   | -              |                  |                  |                 |         |

|               | 0 = Interrupt r | equest not ena                  | bled           |                  |                  |                 |         |

| bit 4         | DMA3IE: DM      | A Channel 3 D                   | ata Transfer C | Complete Interi  | rupt Enable bit  |                 |         |

|               |                 | equest enable<br>equest not ena |                |                  |                  |                 |         |

| bit 3         | -               | Event Interrup                  |                |                  |                  |                 |         |

| bit J         |                 | equest enable                   |                |                  |                  |                 |         |

|               |                 | equest not ena                  |                |                  |                  |                 |         |

| R/W-0         | U-0                                              | R/W-0                                               | U-0           | U-0              | U-0              | U-0             | U-0 |  |  |  |  |

|---------------|--------------------------------------------------|-----------------------------------------------------|---------------|------------------|------------------|-----------------|-----|--|--|--|--|

| TON           |                                                  | TSIDL                                               | —             | _                | _                | _               | _   |  |  |  |  |

| bit 15        |                                                  |                                                     |               |                  |                  |                 | bit |  |  |  |  |

|               |                                                  |                                                     |               |                  |                  |                 |     |  |  |  |  |

| U-0           | R/W-0                                            | R/W-0                                               | R/W-0         | U-0              | R/W-0            | R/W-0           | U-0 |  |  |  |  |

| _             | TGATE                                            | TCKP                                                | S<1:0>        | —                | TSYNC            | TCS             | —   |  |  |  |  |

| bit 7         |                                                  |                                                     |               |                  |                  |                 | bit |  |  |  |  |

| Legend:       |                                                  |                                                     |               |                  |                  |                 |     |  |  |  |  |

| R = Readabl   | e bit                                            | W = Writable                                        | bit           | U = Unimple      | mented bit, read | l as '0'        |     |  |  |  |  |

| -n = Value at | POR                                              | '1' = Bit is set                                    | t             | '0' = Bit is cle | eared            | x = Bit is unkn | own |  |  |  |  |

|               |                                                  |                                                     |               |                  |                  |                 |     |  |  |  |  |

| bit 15        | TON: Timer1                                      | On bit                                              |               |                  |                  |                 |     |  |  |  |  |

|               | 1 = Starts 16                                    | -bit Timer1                                         |               |                  |                  |                 |     |  |  |  |  |

|               | 0 = Stops 16                                     | -bit Timer1                                         |               |                  |                  |                 |     |  |  |  |  |

| bit 14        | Unimplemer                                       | nted: Read as '                                     | 0'            |                  |                  |                 |     |  |  |  |  |

| bit 13        | TSIDL: Stop                                      | in Idle Mode bi                                     | t             |                  |                  |                 |     |  |  |  |  |

|               |                                                  | nue module ope<br>e module operat                   |               |                  | dle mode         |                 |     |  |  |  |  |

| bit 12-7      | Unimplemer                                       | nted: Read as '                                     | 0'            |                  |                  |                 |     |  |  |  |  |

| bit 6         | TGATE: Timer1 Gated Time Accumulation Enable bit |                                                     |               |                  |                  |                 |     |  |  |  |  |

|               | When TCS =<br>This bit is igr                    |                                                     |               |                  |                  |                 |     |  |  |  |  |

|               |                                                  | <u>: 0:</u><br>ne accumulatio<br>ne accumulatio     |               |                  |                  |                 |     |  |  |  |  |

| bit 5-4       | TCKPS<1:0                                        | >: Timer1 Input                                     | Clock Presca  | ale Select bits  |                  |                 |     |  |  |  |  |

|               | 11 <b>= 1:256</b>                                |                                                     |               |                  |                  |                 |     |  |  |  |  |

|               | 10 <b>= 1:64</b>                                 |                                                     |               |                  |                  |                 |     |  |  |  |  |

|               | 01 = 1:8<br>00 = 1:1                             |                                                     |               |                  |                  |                 |     |  |  |  |  |

| L:1 0         |                                                  | stad. Daad as '                                     | 0'            |                  |                  |                 |     |  |  |  |  |

| bit 3         | -                                                | nted: Read as '                                     |               | a hranization C  | alaat hit        |                 |     |  |  |  |  |

| bit 2         | When TCS =                                       | er1 External Cl                                     | ock input Syr | ichronization 5  | elect bit        |                 |     |  |  |  |  |

|               | 1 = Synchror                                     | <u>· ⊥.</u><br>nize external clo<br>ynchronize exte |               | out              |                  |                 |     |  |  |  |  |

|               | When TCS =<br>This bit is igr                    | <u>= 0:</u>                                         |               |                  |                  |                 |     |  |  |  |  |

| bit 1         | TCS: Timer1                                      | Clock Source                                        | Select bit    |                  |                  |                 |     |  |  |  |  |

|               | 1 = External                                     | clock from pin                                      | T1CK (on the  | risina edae)     |                  |                 |     |  |  |  |  |

|               | 0 = Internal o                                   |                                                     | - (           | 3 - 3 - 9        |                  |                 |     |  |  |  |  |

NOTES:

#### **REGISTER 15-1:** OCxCON: OUTPUT COMPARE x CONTROL REGISTER (x = 1, 2)

| U-0    | U-0 | R/W-0  | U-0     | U-0    | U-0   | U-0      | U-0   |

|--------|-----|--------|---------|--------|-------|----------|-------|

| _      | —   | OCSIDL |         | —      | —     | —        | —     |

| bit 15 |     |        | •       |        |       |          | bit 8 |

|        |     |        |         |        |       |          |       |

| U-0    | U-0 | U-0    | R-0, HC | R/W-0  | R/W-0 | R/W-0    | R/W-0 |

|        | —   | —      | OCFLT   | OCTSEL |       | OCM<2:0> |       |

| bit 7  |     |        | •       |        |       |          | bit 0 |

|        |     |        |         |        |       |          |       |

| Legend:           | HC = Hardware Clearable bit |                           |                    |

|-------------------|-----------------------------|---------------------------|--------------------|

| R = Readable bit  | W = Writable bit            | U = Unimplemented bit, re | ead as '0'         |

| -n = Value at POR | '1' = Bit is set            | '0' = Bit is cleared      | x = Bit is unknown |

| bit 15-14 | Unimplemented: Read as '0'                                                          |

|-----------|-------------------------------------------------------------------------------------|

| bit 13    | OCSIDL: Stop Output Compare in Idle Mode Control bit                                |

|           | 1 = Output Compare x halts in CPU Idle mode                                         |

|           | 0 = Output Compare x continues to operate in CPU Idle mode                          |

| bit 12-5  | Unimplemented: Read as '0'                                                          |

| bit 4     | OCFLT: PWM Fault Condition Status bit                                               |

|           | 1 = PWM Fault condition has occurred (cleared in hardware only)                     |

|           | 0 = No PWM Fault condition has occurred (this bit is only used when OCM<2:0> = 111) |

| bit 3     | OCTSEL: Output Compare Timer Select bit                                             |

|           | 1 = Timer3 is the clock source for Compare x                                        |

|           | 0 = Timer2 is the clock source for Compare x                                        |

| bit 2-0   | OCM<2:0>: Output Compare Mode Select bits                                           |

|           | 111 = PWM mode on OCx, Fault pin enabled                                            |

|           | 110 = PWM mode on OCx, Fault pin disabled                                           |

|           | 101 = Initialize OCx pin low, generate continuous output pulses on OCx pin          |

|           | 100 = Initialize OCx pin low, generate single output pulse on OCx pin               |

|           | 011 = Compare event toggles OCx pin                                                 |

|           | 010 = Initialize OCx pin high, compare event forces OCx pin low                     |

|           | 001 = Initialize OCx pin low, compare event forces OCx pin high                     |

|           | 000 = Output compare channel is disabled                                            |

REGISTER 16-3: SPIxCON2: SPIx CONTROL REGISTER 2

| R/W-0                        | R/W-0                                                                                                                                                                           | R/W-0                                                                                                                                                                                                             | U-0                                                                                                                                                               | U-0                             | U-0                  | U-0                | U-0 |  |

|------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------|----------------------|--------------------|-----|--|

| FRMEN                        | SPIFSD                                                                                                                                                                          | FRMPOL                                                                                                                                                                                                            | _                                                                                                                                                                 | _                               | _                    | _                  | _   |  |

| pit 15                       |                                                                                                                                                                                 |                                                                                                                                                                                                                   |                                                                                                                                                                   |                                 |                      |                    | bit |  |

|                              |                                                                                                                                                                                 |                                                                                                                                                                                                                   |                                                                                                                                                                   |                                 |                      |                    |     |  |

| U-0                          | U-0                                                                                                                                                                             | U-0                                                                                                                                                                                                               | U-0                                                                                                                                                               | U-0                             | U-0                  | R/W-0              | U-0 |  |

| —                            | —                                                                                                                                                                               | _                                                                                                                                                                                                                 | —                                                                                                                                                                 | —                               | —                    | FRMDLY             | —   |  |

| bit 7                        |                                                                                                                                                                                 |                                                                                                                                                                                                                   |                                                                                                                                                                   |                                 |                      |                    | bit |  |

| Legend:                      |                                                                                                                                                                                 |                                                                                                                                                                                                                   |                                                                                                                                                                   |                                 |                      |                    |     |  |

| R = Readable                 | e bit                                                                                                                                                                           | W = Writable                                                                                                                                                                                                      | bit                                                                                                                                                               | U = Unimplem                    | nented bit, rea      | ad as '0'          |     |  |

| -n = Value at                | POR                                                                                                                                                                             | -n = Value at POR '1' = Bit is set                                                                                                                                                                                |                                                                                                                                                                   |                                 |                      | x = Bit is unknown |     |  |

| bit 15                       | 1 = Framed S                                                                                                                                                                    |                                                                                                                                                                                                                   | abled ( <del>SSx</del> p                                                                                                                                          | oin used as fram                | ared<br>e sync pulse | input/output)      |     |  |

| bit 15                       | 1 = Framed S                                                                                                                                                                    | SPIx support en                                                                                                                                                                                                   | abled ( <del>SSx</del> p                                                                                                                                          | oin used as fram                |                      | input/output)      |     |  |

| bit 15<br>bit 14             | 1 = Framed S<br>0 = Framed S<br><b>SPIFSD:</b> Fran                                                                                                                             | SPIx support en<br>SPIx support dis<br>me Sync Pulse                                                                                                                                                              | abled ( <mark>SSx</mark> p<br>abled<br>Direction Co                                                                                                               |                                 |                      | input/output)      |     |  |

| bit 14                       | 1 = Framed S<br>0 = Framed S<br><b>SPIFSD:</b> Fran<br>1 = Frame sy<br>0 = Frame sy                                                                                             | SPIx support en<br>SPIx support dis<br>me Sync Pulse<br>nc pulse input (<br>nc pulse output                                                                                                                       | abled ( <del>SSx</del> p<br>sabled<br>Direction Co<br>(slave)<br>t (master)                                                                                       | ntrol bit                       |                      | input/output)      |     |  |

|                              | 1 = Framed S<br>0 = Framed S<br><b>SPIFSD:</b> Fran<br>1 = Frame sy<br>0 = Frame sy<br><b>FRMPOL:</b> Fran                                                                      | SPIx support en<br>SPIx support dis<br>me Sync Pulse<br>nc pulse input (                                                                                                                                          | abled (SSx p<br>sabled<br>Direction Co<br>(slave)<br>t (master)<br>e Polarity bit                                                                                 | ntrol bit                       |                      | input/output)      |     |  |

| bit 14                       | 1 = Framed S<br>0 = Framed S<br><b>SPIFSD:</b> Fran<br>1 = Frame sy<br>0 = Frame sy<br><b>FRMPOL:</b> Fran<br>1 = Frame sy                                                      | SPIx support en<br>SPIx support dis<br>me Sync Pulse<br>nc pulse input (<br>nc pulse output<br>ame Sync Pulse                                                                                                     | abled (SSx p<br>sabled<br>Direction Co<br>(slave)<br>t (master)<br>e Polarity bit<br>ve-high                                                                      | ntrol bit                       |                      | input/output)      |     |  |

| bit 14                       | 1 = Framed S<br>0 = Framed S<br>SPIFSD: France<br>1 = Frame sy<br>0 = Frame sy<br>FRMPOL: France sy<br>0 = Frame sy                                                             | SPIx support en<br>SPIx support dis<br>me Sync Pulse<br>nc pulse input (<br>nc pulse output<br>ame Sync Pulse<br>nc pulse is activ                                                                                | abled (SSx p<br>sabled<br>Direction Co<br>(slave)<br>t (master)<br>e Polarity bit<br>ve-high<br>ve-low                                                            | ntrol bit                       |                      | input/output)      |     |  |

| bit 14<br>bit 13             | 1 = Framed S<br>0 = Framed S<br>SPIFSD: Fran<br>1 = Frame sy<br>0 = Frame sy<br>FRMPOL: Fran<br>1 = Frame sy<br>0 = Frame sy<br>Unimplemen                                      | Plx support en<br>Plx support dis<br>me Sync Pulse<br>nc pulse input (<br>nc pulse output<br>ame Sync Pulse<br>nc pulse is acti<br>nc pulse is acti                                                               | abled (SSx p<br>sabled<br>Direction Co<br>(slave)<br>t (master)<br>e Polarity bit<br>ve-high<br>ve-low<br>o'                                                      | ntrol bit                       |                      | input/output)      |     |  |

| bit 14<br>bit 13<br>bit 12-2 | 1 = Framed S<br>0 = Framed S<br>SPIFSD: France<br>1 = Frame sy<br>0 = Frame sy<br>0 = Frame sy<br>0 = Frame sy<br>Unimplement<br>FRMDLY: France<br>1 = Frame sy                 | SPIx support en<br>SPIx support dis<br>me Sync Pulse<br>nc pulse input (<br>nc pulse output<br>ame Sync Pulse<br>nc pulse is actir<br>nc pulse is actir<br>ated: Read as '(<br>ame Sync Pulse<br>nc pulse coincir | abled (SSx p<br>sabled<br>Direction Co<br>(slave)<br>t (master)<br>e Polarity bit<br>ve-high<br>ve-low<br>o'<br>e Edge Selec<br>des with first                    | ntrol bit<br>t bit<br>bit clock |                      | input/output)      |     |  |

| bit 14<br>bit 13<br>bit 12-2 | 1 = Framed S<br>0 = Framed S<br>SPIFSD: France<br>1 = Frame sy<br>0 = Frame sy<br>0 = Frame sy<br>0 = Frame sy<br>Unimplement<br>FRMDLY: France<br>1 = Frame sy<br>0 = Frame sy | SPIx support en<br>SPIx support dis<br>me Sync Pulse<br>nc pulse input (<br>nc pulse output<br>ame Sync Pulse<br>nc pulse is actir<br>nc pulse is actir<br>ted: Read as '(<br>ame Sync Pulse                      | abled (SSx p<br>sabled<br>Direction Co<br>(slave)<br>t (master)<br>e Polarity bit<br>ve-high<br>ve-low<br>p'<br>e Edge Selec<br>des with first<br>des first bit c | ntrol bit<br>t bit<br>bit clock |                      | input/output)      |     |  |

#### 17.0 INTER-INTEGRATED CIRCUIT™ (I<sup>2</sup>C™)

- Note 1: This data sheet summarizes the features of the PIC24HJXXXGPX06A/X08A/X10A family of devices. However, it is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to Section 19. "Inter-Integrated Circuit™ (I<sup>2</sup>C™)" (DS70195) of the "dsPIC33F/ PIC24H Family Reference Manual", which is available from the Microchip web site (www.microchip.com).

- Some registers and associated bits described in this section may not be available on all devices. Refer to Section 4.0 "Memory Organization" in this data sheet for device-specific register and bit information.

The Inter-Integrated Circuit ( $I^2C$ ) module provides complete hardware support for both Slave and Multi-Master modes of the  $I^2C$  serial communication standard, with a 16-bit interface.

The PIC24HJXXXGPX06A/X08A/X10A devices have up to two I<sup>2</sup>C interface modules, denoted as I2C1 and I2C2. Each I<sup>2</sup>C module has a 2-pin interface: the SCLx pin is clock and the SDAx pin is data.

Each  $I^2C$  module 'x' (x = 1 or 2) offers the following key features:

- I<sup>2</sup>C interface supporting both master and slave operation

- I<sup>2</sup>C Slave mode supports 7-bit and 10-bit addressing

- I<sup>2</sup>C Master mode supports 7-bit and 10-bit addressing

- I<sup>2</sup>C Port allows bidirectional transfers between master and slaves

- Serial clock synchronization for I<sup>2</sup>C port can be used as a handshake mechanism to suspend and resume serial transfer (SCLREL control)

- I<sup>2</sup>C supports multi-master operation; detects bus collision and will arbitrate accordingly

#### 17.1 Operating Modes

The hardware fully implements all the master and slave functions of the  $l^2C$  Standard and Fast mode specifications, as well as 7 and 10-bit addressing.

The I<sup>2</sup>C module can operate either as a slave or a master on an I<sup>2</sup>C bus.

The following types of I<sup>2</sup>C operation are supported:

- I<sup>2</sup>C slave operation with 7-bit addressing

- I<sup>2</sup>C slave operation with 10-bit addressing

- I<sup>2</sup>C master operation with 7-bit or 10-bit addressing

For details about the communication sequence in each of these modes, please refer to the *"dsPIC33F/PIC24H Family Reference Manual"*.

#### REGISTER 19-2: CiCTRL2: ECAN™ MODULE CONTROL REGISTER 2

| U-0           | U-0                | U-0                               | U-0             | U-0              | U-0              | U-0                | U-0   |  |

|---------------|--------------------|-----------------------------------|-----------------|------------------|------------------|--------------------|-------|--|

| _             | _                  | _                                 |                 | _                | —                |                    | —     |  |

| bit 15        |                    |                                   |                 |                  | •                |                    | bit 8 |  |

|               |                    |                                   |                 |                  |                  |                    |       |  |

| U-0           | U-0                | U-0                               | R-0             | R-0              | R-0              | R-0                | R-0   |  |

| _             | —                  | _                                 |                 |                  | DNCNT<4:0>       |                    |       |  |

| bit 7         |                    |                                   |                 |                  |                  |                    | bit 0 |  |

|               |                    |                                   |                 |                  |                  |                    |       |  |

| Legend:       |                    |                                   |                 |                  |                  |                    |       |  |

| R = Readable  | e bit              | W = Writable                      | bit             | U = Unimpler     | mented bit, read | as '0'             |       |  |

| -n = Value at | POR                | '1' = Bit is set                  | :               | '0' = Bit is cle | ared             | x = Bit is unknown |       |  |

|               |                    |                                   |                 |                  |                  |                    |       |  |

| bit 15-5      | Unimplemen         | ted: Read as '                    | 0'              |                  |                  |                    |       |  |

| bit 4-0       | DNCNT<4:0>         | •: DeviceNet™                     | Filter Bit Num  | ber bits         |                  |                    |       |  |

|               | 10010-1111         | 1 = Invalid sel                   | ection          |                  |                  |                    |       |  |

|               | 10001 <b>= Con</b> | npare up to dat                   | a byte 3, bit 6 | with EID<17>     |                  |                    |       |  |

|               | •                  |                                   |                 |                  |                  |                    |       |  |

|               | •                  |                                   |                 |                  |                  |                    |       |  |

|               | •                  |                                   |                 |                  |                  |                    |       |  |

|               |                    | npare up to dat<br>not compare da |                 | with EID<0>      |                  |                    |       |  |

|               |                    |                                   |                 |                  |                  |                    |       |  |

#### REGISTER 19-15: CIBUFPNT4: ECAN™ MODULE FILTER 12-15 BUFFER POINTER REGISTER

| R/W-0         | R/W-0                             | R/W-0                                                   | R/W-0         | R/W-0         | R/W-0          | R/W-0           | R/W-0 |

|---------------|-----------------------------------|---------------------------------------------------------|---------------|---------------|----------------|-----------------|-------|

|               | F15BF                             | o<3:0>                                                  |               |               | F14B           | P<3:0>          |       |

| bit 15        |                                   |                                                         |               |               |                |                 | bit 8 |

|               |                                   |                                                         |               |               |                |                 |       |

| R/W-0         | R/W-0                             | R/W-0                                                   | R/W-0         | R/W-0         | R/W-0          | R/W-0           | R/W-0 |

|               | F13BF                             | P<3:0>                                                  |               |               | F12B           | P<3:0>          |       |

| bit 7         |                                   |                                                         |               |               |                |                 | bit ( |

| Legend:       |                                   |                                                         |               |               |                |                 |       |

| R = Readable  | e bit                             | W = Writable                                            | bit           | U = Unimpleme | ented bit, rea | d as '0'        |       |

| -n = Value at | n = Value at POR '1' = Bit is set |                                                         |               |               | ed             | x = Bit is unkr | nown  |

| bit 15-12     | 1111 = Filter                     | : RX Buffer Wri<br>hits received ir<br>hits received ir | n RX FIFO bu  | uffer         |                |                 |       |

|               | •                                 |                                                         |               |               |                |                 |       |

|               | •                                 |                                                         |               |               |                |                 |       |

|               | •                                 |                                                         |               |               |                |                 |       |

|               |                                   | hits received ir hits received ir                       |               |               |                |                 |       |

| bit 11-8      | 1111 = Filter                     | : RX Buffer Wri<br>hits received ir<br>hits received ir | ו RX FIFO bu  | uffer         |                |                 |       |

|               | •                                 |                                                         |               |               |                |                 |       |

|               | •                                 |                                                         |               |               |                |                 |       |

|               |                                   | hits received ir hits received ir                       |               |               |                |                 |       |

| bit 7-4       | 1111 = Filter                     | : RX Buffer Wri<br>hits received ir<br>hits received ir | n RX FIFO bu  | uffer         |                |                 |       |

|               | •                                 |                                                         |               |               |                |                 |       |

|               | •                                 |                                                         |               |               |                |                 |       |

|               |                                   | hits received ir hits received ir                       |               |               |                |                 |       |

| bit 3-0       |                                   | : RX Buffer Wri                                         |               |               |                |                 |       |

|               | 1111 = Filter                     | hits received ir<br>hits received ir                    | n RX FIFO bu  | uffer         |                |                 |       |

|               | •                                 |                                                         |               |               |                |                 |       |

|               | •                                 |                                                         |               |               |                |                 |       |

|               | 0001 = Filter                     | hits received in                                        | n RX Buffer 1 |               |                |                 |       |

#### REGISTER 19-22: CIRXFUL1: ECAN™ MODULE RECEIVE BUFFER FULL REGISTER 1

| R/C-0   | R/C-0   | R/C-0   | R/C-0   | R/C-0   | R/C-0   | R/C-0  | R/C-0  |

|---------|---------|---------|---------|---------|---------|--------|--------|

| RXFUL15 | RXFUL14 | RXFUL13 | RXFUL12 | RXFUL11 | RXFUL10 | RXFUL9 | RXFUL8 |

| bit 15  |         |         |         |         |         |        | bit 8  |

| R/C-0  |

|--------|--------|--------|--------|--------|--------|--------|--------|

| RXFUL7 | RXFUL6 | RXFUL5 | RXFUL4 | RXFUL3 | RXFUL2 | RXFUL1 | RXFUL0 |

| bit 7  | •      |        |        | •      |        |        | bit 0  |

| Legend:           | C = Clear only bit |                       |                    |

|-------------------|--------------------|-----------------------|--------------------|

| R = Readable bit  | W = Writable bit   | U = Unimplemented bit | , read as '0'      |

| -n = Value at POR | '1' = Bit is set   | '0' = Bit is cleared  | x = Bit is unknown |

bit 15-0 **RXFUL15:RXFUL0:** Receive Buffer n Full bits

1 = Buffer is full (set by module)

0 = Buffer is empty (clear by application software)

#### REGISTER 19-23: CiRXFUL2: ECAN™ MODULE RECEIVE BUFFER FULL REGISTER 2

| R/C-0   |

|---------|---------|---------|---------|---------|---------|---------|---------|

| RXFUL31 | RXFUL30 | RXFUL29 | RXFUL28 | RXFUL27 | RXFUL26 | RXFUL25 | RXFUL24 |

| bit 15  |         |         |         |         |         |         | bit 8   |

| R/C-0   |

|---------|---------|---------|---------|---------|---------|---------|---------|

| RXFUL23 | RXFUL22 | RXFUL21 | RXFUL20 | RXFUL19 | RXFUL18 | RXFUL17 | RXFUL16 |

| bit 7   |         |         |         |         |         |         | bit 0   |

| Legend:           | C = Clear only bit |                       |                    |

|-------------------|--------------------|-----------------------|--------------------|

| R = Readable bit  | W = Writable bit   | U = Unimplemented bit | t, read as '0'     |

| -n = Value at POR | '1' = Bit is set   | '0' = Bit is cleared  | x = Bit is unknown |

bit 15-0 **RXFUL31:RXFUL16:** Receive Buffer n Full bits

1 = Buffer is full (set by module)

0 = Buffer is empty (clear by application software)

#### REGISTER 19-24: CiRXOVF1: ECAN™ MODULE RECEIVE BUFFER OVERFLOW REGISTER 1

| R/C-0   | R/C-0   | R/C-0   | R/C-0   | R/C-0   | R/C-0   | R/C-0  | R/C-0  |

|---------|---------|---------|---------|---------|---------|--------|--------|

| RXOVF15 | RXOVF14 | RXOVF13 | RXOVF12 | RXOVF11 | RXOVF10 | RXOVF9 | RXOVF8 |

| bit 15  |         |         |         |         |         |        | bit 8  |

| R/C-0  |

|--------|--------|--------|--------|--------|--------|--------|--------|

| RXOVF7 | RXOVF6 | RXOVF5 | RXOVF4 | RXOVF3 | RXOVF2 | RXOVF1 | RXOVF0 |

| bit 7  |        |        |        |        |        |        | bit 0  |

| Legend:           | C = Clear only bit |                       |                    |

|-------------------|--------------------|-----------------------|--------------------|

| R = Readable bit  | W = Writable bit   | U = Unimplemented bit | , read as '0'      |

| -n = Value at POR | '1' = Bit is set   | '0' = Bit is cleared  | x = Bit is unknown |

bit 15-0 **RXOVF15:RXOVF0:** Receive Buffer n Overflow bits

1 = Module pointed a write to a full buffer (set by module)

0 = Overflow is cleared (clear by application software)

#### REGISTER 19-25: CIRXOVF2: ECAN™ MODULE RECEIVE BUFFER OVERFLOW REGISTER 2

| R/C-0   |

|---------|---------|---------|---------|---------|---------|---------|---------|

| RXOVF31 | RXOVF30 | RXOVF29 | RXOVF28 | RXOVF27 | RXOVF26 | RXOVF25 | RXOVF24 |

| bit 15  | •       |         |         |         |         |         | bit 8   |

| R/C-0   |

|---------|---------|---------|---------|---------|---------|---------|---------|

| RXOVF23 | RXOVF22 | RXOVF21 | RXOVF20 | RXOVF19 | RXOVF18 | RXOVF17 | RXOVF16 |

| bit 7   |         |         |         |         |         |         | bit 0   |

| Legend:           | C = Clear only bit |                       |                    |

|-------------------|--------------------|-----------------------|--------------------|

| R = Readable bit  | W = Writable bit   | U = Unimplemented bit | t, read as '0'     |

| -n = Value at POR | '1' = Bit is set   | '0' = Bit is cleared  | x = Bit is unknown |

bit 15-0 **RXOVF31:RXOVF16:** Receive Buffer n Overflow bits

1 = Module pointed a write to a full buffer (set by module)

0 = Overflow is cleared (clear by application software)

#### Base Assembly # of # of Status Flags Instr Assembly Syntax Description Mnemonic Words Cycles Affected # 47 Relative Call RCALL RCALL 1 2 None Expr RCALL Computed Call 1 2 None Wn 48 REPEAT REPEAT #lit14 Repeat Next Instruction lit14 + 1 times 1 1 None REPEAT Repeat Next Instruction (Wn) + 1 times 1 1 None Wn 1 1 49 RESET RESET Software device Reset None 50 RETFIE RETFIE Return from interrupt 1 3 (2) None 51 RETLW #lit10,Wn Return with literal in Wn 1 3 (2) None RETLW 52 1 RETURN RETURN Return from Subroutine 3 (2) None 53 RLC RLC f = Rotate Left through Carry f 1 1 C,N,Z f RLC f,WREG WREG = Rotate Left through Carry f 1 1 C,N,Z RLC Ws,Wd Wd = Rotate Left through Carry Ws 1 1 C,N,Z 54 f = Rotate Left (No Carry) f 1 1 N,Z RLNC RUNC f 1 RLNC f,WREG WREG = Rotate Left (No Carry) f 1 N,Z RLNC Ws,Wd Wd = Rotate Left (No Carry) Ws 1 1 N,Z 55 RRC RRC f = Rotate Right through Carry f 1 1 C,N,Z f WREG = Rotate Right through Carry f 1 1 C,N,Z RRC f,WREG RRC Wd = Rotate Right through Carry Ws 1 1 C,N,Z Ws,Wd 56 RRNC RRNC f = Rotate Right (No Carry) f 1 1 N,Z f WREG = Rotate Right (No Carry) f 1 1 N,Z RRNC f,WREG Wd = Rotate Right (No Carry) Ws 1 1 N,Z RRNC Ws,Wd 1 C,N,Z 57 SE SE Ws,Wnd Wnd = sign-extended Ws 1 58 SETM SETM f f = 0xFFFF1 1 None WREG = 0xFFFF 1 1 SETM WREG None Ws = 0xFFFF 1 SETM Ws 1 None 59 SL SL f f = Left Shift f 1 1 C,N,OV,Z SL f,WREG WREG = Left Shift f 1 1 C,N,OV,Z Wd = Left Shift Ws 1 1 C,N,OV,Z SL Ws,Wd Wnd = Left Shift Wb by Wns 1 1 SL N.Z Wb, Wns, Wnd SL Wb,#lit5,Wnd Wnd = Left Shift Wb by lit5 1 1 N,Z 60 SUB SUB f = f – WREG 1 1 C,DC,N,OV,Z f WREG = f - WREG 1 1 C,DC,N,OV,Z SUB f,WREG Wn = Wn - lit10SUB #lit10,Wn 1 1 C,DC,N,OV,Z SUB Wb,Ws,Wd Wd = Wb - Ws1 1 C,DC,N,OV,Z Wd = Wb - lit5 1 1 C,DC,N,OV,Z SUB Wb,#lit5,Wd 61 SUBB $f = f - WREG - (\overline{C})$ C,DC,N,OV,Z 1 1 SUBB f WREG = $f - WREG - (\overline{C})$ 1 SUBB f,WREG 1 C,DC,N,OV,Z $Wn = Wn - lit10 - (\overline{C})$ 1 C,DC,N,OV,Z 1 SUBB #lit10,Wn SUBB $Wd = Wb - Ws - (\overline{C})$ 1 1 C,DC,N,OV,Z Wb,Ws,Wd SUBB Wb,#lit5,Wd $Wd = Wb - lit5 - (\overline{C})$ 1 1 C,DC,N,OV,Z 62 SUBR f = WREG - f 1 1 C,DC,N,OV,Z SUBR f WREG = WREG - f 1 1 C,DC,N,OV,Z SUBR f,WREG SUBR Wb,Ws,Wd Wd = Ws - Wb 1 1 C,DC,N,OV,Z Wd = lit5 - Wb1 1 C,DC,N,OV,Z SUBR Wb, #lit5, Wd 63 SUBBR $f = WREG - f - (\overline{C})$ 1 1 C,DC,N,OV,Z SUBBR f WREG = WREG - f - $(\overline{C})$ 1 SUBBR f,WREG 1 C,DC,N,OV,Z $Wd = Ws - Wb - (\overline{C})$ 1 1 C,DC,N,OV,Z SUBBR Wb.Ws.Wd $Wd = lit5 - Wb - (\overline{C})$ 1 C,DC,N,OV,Z SUBBR Wb,#lit5,Wd 1 64 1 SWAP SWAP.b Wn Wn = nibble swap Wn 1 None SWAP Wn = byte swap Wn 1 1 None Wn 1 2 65 Read Prog<23:16> to Wd<7:0> TBLRDH TBLRDH Ws,Wd None

#### TABLE 22-2: INSTRUCTION SET OVERVIEW (CONTINUED)

### 24.0 ELECTRICAL CHARACTERISTICS

This section provides an overview of PIC24HJXXXGPX06A/X08A/X10A electrical characteristics. Additional information is provided in future revisions of this document as it becomes available.

Absolute maximum ratings for the PIC24HJXXXGPX06A/X08A/X10A family are listed below. Exposure to these maximum rating conditions for extended periods can affect device reliability. Functional operation of the device at these or any other conditions above the parameters indicated in the operation listings of this specification is not implied.

#### **Absolute Maximum Ratings**

#### (See Note 1)

| Ambient temperature under bias                                                    | 40°C to +125°C |

|-----------------------------------------------------------------------------------|----------------|

| Storage temperature                                                               | 65°C to +160°C |

| Voltage on VDD with respect to Vss                                                |                |

| Voltage on any pin that is not 5V tolerant with respect to Vss <sup>(4)</sup>     |                |

| Voltage on any 5V tolerant pin with respect to Vss when $VDD \ge 3.0V^{(4)}$      | 0.3V to +5.6V  |

| Voltage on any 5V tolerant pin with respect to Vss when VDD < 3.0V <sup>(4)</sup> | 0.3V to 3.6V   |

| Maximum current out of Vss pin                                                    |                |

| Maximum current into Vod pin <sup>(2)</sup>                                       | 250 mA         |

| Maximum current sourced/sunk by any 2x I/O pin <sup>(3)</sup>                     | 8 mA           |

| Maximum current sourced/sunk by any 4x I/O pin <sup>(3)</sup>                     | 15 mA          |

| Maximum current sourced/sunk by any 8x I/O pin <sup>(3)</sup>                     | 25 mA          |

| Maximum current sunk by all ports                                                 | 200 mA         |

| Maximum current sourced by all ports <sup>(2)</sup>                               | 200 mA         |

- **Note 1:** Stresses above those listed under "Absolute Maximum Ratings" can cause permanent damage to the device. This is a stress rating only, and functional operation of the device at those or any other conditions above those indicated in the operation listings of this specification is not implied. Exposure to maximum rating conditions for extended periods can affect device reliability.

- **2:** Maximum allowable current is a function of device maximum power dissipation (see Table 24-2).

- Exceptions are CLKOUT, which is able to sink/source 25 mA, and the VREF+, VREF-, SCLx, SDAx, PGECx and PGEDx pins, which are able to sink/source 12 mA.

- 4: See the "Pin Diagrams" section for 5V tolerant pins.

### 25.0 HIGH TEMPERATURE ELECTRICAL CHARACTERISTICS

This section provides an overview of PIC24HJXXXGPX06A/X08A/X10A electrical characteristics for devices operating in an ambient temperature range of -40°C to +150°C.

The specifications between  $-40^{\circ}$ C to  $+150^{\circ}$ C are identical to those shown in **Section 24.0** "**Electrical Characteristics**" for operation between  $-40^{\circ}$ C to  $+125^{\circ}$ C, with the exception of the parameters listed in this section.

Parameters in this section begin with an H, which denotes High temperature. For example, parameter DC10 in **Section 24.0 "Electrical Characteristics"** is the Industrial and Extended temperature equivalent of HDC10.

Absolute maximum ratings for the PIC24HJXXXGPX06A/X08A/X10A high temperature devices are listed below. Exposure to these maximum rating conditions for extended periods can affect device reliability. Functional operation of the device at these or any other conditions above the parameters indicated in the operation listings of this specification is not implied.

#### Absolute Maximum Ratings

#### (See Note 1)

| Ambient temperature under bias <sup>(4)</sup>                                 | 40°C to +150°C       |

|-------------------------------------------------------------------------------|----------------------|

| Storage temperature                                                           | 65°C to +160°C       |

| Voltage on VDD with respect to Vss                                            | -0.3V to +4.0V       |

| Voltage on any pin that is not 5V tolerant with respect to Vss <sup>(5)</sup> | 0.3V to (VDD + 0.3V) |

| Voltage on any 5V tolerant pin with respect to Vss when $VDD < 3.0V^{(5)}$    |                      |

| Voltage on any 5V tolerant pin with respect to Vss when $VDD \ge 3.0V^{(5)}$  | 0.3V to 5.6V         |

| Voltage on VCAP with respect to Vss                                           | 2.25V to 2.75V       |

| Maximum current out of Vss pin                                                | 60 mA                |

| Maximum current into VDD pin <sup>(2)</sup>                                   | 60 mA                |

| Maximum junction temperature                                                  |                      |

| Maximum current sourced/sunk by any 2x I/O pin <sup>(3)</sup>                 | 2 mA                 |

| Maximum current sourced/sunk by any 4x I/O pin <sup>(3)</sup>                 | 4 mA                 |

| Maximum current sourced/sunk by any 8x I/O pin <sup>(3)</sup>                 | 8 mA                 |

| Maximum current sunk by all ports combined                                    | 10 mA                |

| Maximum current sourced by all ports combined <sup>(2)</sup>                  | 10 mA                |

|                                                                               |                      |

**Note 1:** Stresses above those listed under "Absolute Maximum Ratings" can cause permanent damage to the device. This is a stress rating only, and functional operation of the device at those or any other conditions above those indicated in the operation listings of this specification is not implied. Exposure to maximum rating conditions for extended periods can affect device reliability.

- 2: Maximum allowable current is a function of device maximum power dissipation (see Table 25-2).

- **3:** Unlike devices at 125°C and below, the specifications in this section also apply to the CLKOUT, VREF+, VREF-, SCLx, SDAx, PGECx, and PGEDx pins.

- 4: AEC-Q100 reliability testing for devices intended to operate at 150°C is 1,000 hours. Any design in which the total operating time from 125°C to 150°C will be greater than 1,000 hours is not warranted without prior written approval from Microchip Technology Inc.

- 5: Refer to the "Pin Diagrams" section for 5V tolerant pins.

| DC CHARACTERISTICS       |         |     | Standard Operating Conditions: 3.0V to 3.6V(unless otherwise stated)Operating temperature $-40^{\circ}C \le TA \le +150^{\circ}C$ for High Temperature |            |      |                                                |  |  |

|--------------------------|---------|-----|--------------------------------------------------------------------------------------------------------------------------------------------------------|------------|------|------------------------------------------------|--|--|

| Parameter<br>No.         | Typical | Max | Units                                                                                                                                                  | Conditions |      |                                                |  |  |

| Power-Down Current (IPD) |         |     |                                                                                                                                                        |            |      |                                                |  |  |

| HDC61c                   | 3       | 5   | μA                                                                                                                                                     | +150°C     | 3.3V | Watchdog Timer Current: ΔIWDT <sup>(2,4)</sup> |  |  |

Note 1: Base IPD is measured with all peripherals and clocks shut down. All I/Os are configured as inputs and pulled to Vss. WDT, etc., are all switched off, and VREGS (RCON<8>) = 1.

- 2: The ∆ current is the additional current consumed when the module is enabled. This current should be added to the base IPD current.

- 3: These currents are measured on the device containing the most memory in this family.

- 4: These parameters are characterized, but are not tested in manufacturing.

#### TABLE 25-5: DC CHARACTERISTICS: DOZE CURRENT (IDOZE)

| DC CHARACTERISTICS |                        |     | $\begin{tabular}{lllllllllllllllllllllllllllllllllll$ |       |            |      |         |  |

|--------------------|------------------------|-----|-------------------------------------------------------|-------|------------|------|---------|--|

| Parameter<br>No.   | Typical <sup>(1)</sup> | Max | Doze<br>Ratio                                         | Units | Conditions |      |         |  |

| HDC72a             | 39                     | 45  | 1:2                                                   | mA    |            |      |         |  |

| HDC72f             | 18                     | 25  | 1:64                                                  | mA    | +150°C     | 3.3V | 20 MIPS |  |

| HDC72g             | 18                     | 25  | 1:128                                                 | mA    |            |      |         |  |

Note 1: Parameters with Doze ratios of 1:2 and 1:64 are characterized, but are not tested in manufacturing.

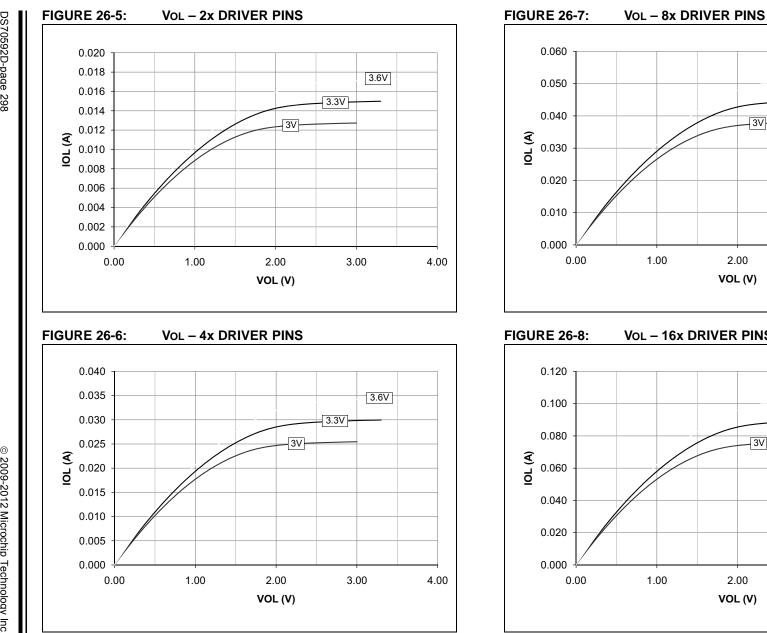

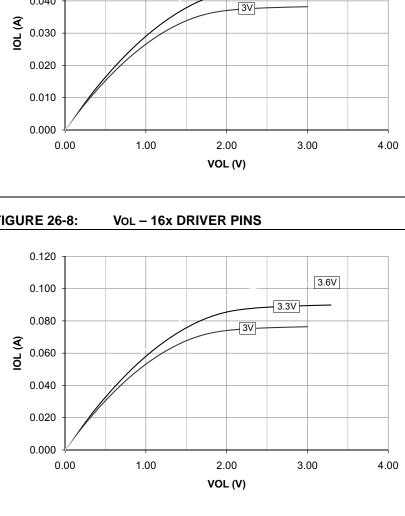

3.6V

3.3V

DS70592D-page 298

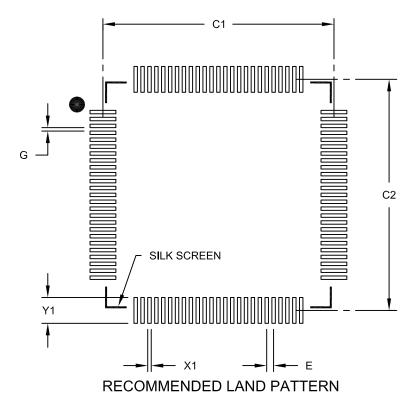

100-Lead Plastic Thin Quad Flatpack (PT)-12x12x1mm Body, 2.00 mm Footprint [TQFP]

**Note:** For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

|                           | Units |          |       | MILLIMETERS |  |  |  |

|---------------------------|-------|----------|-------|-------------|--|--|--|

| Dimensior                 | MIN   | NOM      | MAX   |             |  |  |  |

| Contact Pitch             | E     | 0.40 BSC |       |             |  |  |  |

| Contact Pad Spacing       | C1    |          | 13.40 |             |  |  |  |

| Contact Pad Spacing       | C2    |          | 13.40 |             |  |  |  |

| Contact Pad Width (X100)  | X1    |          |       | 0.20        |  |  |  |

| Contact Pad Length (X100) | Y1    |          |       | 1.50        |  |  |  |

| Distance Between Pads     | G     | 0.20     |       |             |  |  |  |

Notes:

1. Dimensioning and tolerancing per ASME Y14.5M

BSC: Basic Dimension. Theoretically exact value shown without tolerances.

Microchip Technology Drawing No. C04-2100B