Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFl

| Details                    |                                                                                 |

|----------------------------|---------------------------------------------------------------------------------|

| Product Status             | Active                                                                          |

| Core Processor             | PIC                                                                             |

| Core Size                  | 16-Bit                                                                          |

| Speed                      | 40 MIPs                                                                         |

| Connectivity               | I <sup>2</sup> C, IrDA, LINbus, SPI, UART/USART                                 |

| Peripherals                | Brown-out Detect/Reset, DMA, POR, PWM, WDT                                      |

| Number of I/O              | 85                                                                              |

| Program Memory Size        | 256KB (85.5K x 24)                                                              |

| Program Memory Type        | FLASH                                                                           |

| EEPROM Size                | -                                                                               |

| RAM Size                   | 16K x 8                                                                         |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 3.6V                                                                       |

| Data Converters            | A/D 32x10b/12b                                                                  |

| Oscillator Type            | Internal                                                                        |

| Operating Temperature      | -40°C ~ 125°C (TA)                                                              |

| Mounting Type              | Surface Mount                                                                   |

| Package / Case             | 100-TQFP                                                                        |

| Supplier Device Package    | 100-TQFP (14x14)                                                                |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic24hj256gp210a-e-pf |

|                            |                                                                                 |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# **PIC24H PRODUCT FAMILIES**

The PIC24H Family of devices is ideal for a wide variety of 16-bit MCU embedded applications. The device names, pin counts, memory sizes and peripheral availability of each device are listed below, followed by their pinout diagrams.

# **PIC24H Family Controllers**

| Device           | Pins | Program<br>Flash<br>Memory (KB) | RAM <sup>(1)</sup> (KB) | DMA Channels | Timer 16-bit | Input Capture | Output Compare<br>Std. PWM | Codec<br>Interface | ADC             | UART | SPI | I <sup>2</sup> C <sup>TM</sup> | CAN | I/O Pins (Max) <sup>(2)</sup> | Packages |

|------------------|------|---------------------------------|-------------------------|--------------|--------------|---------------|----------------------------|--------------------|-----------------|------|-----|--------------------------------|-----|-------------------------------|----------|

| PIC24HJ64GP206A  | 64   | 64                              | 8                       | 8            | 9            | 8             | 8                          | 0                  | 1 ADC,<br>18 ch | 2    | 2   | 1                              | 0   | 53                            | PT, MR   |

| PIC24HJ64GP210A  | 100  | 64                              | 8                       | 8            | 9            | 8             | 8                          | 0                  | 1 ADC,<br>32 ch | 2    | 2   | 2                              | 0   | 85                            | PF, PT   |

| PIC24HJ64GP506A  | 64   | 64                              | 8                       | 8            | 9            | 8             | 8                          | 0                  | 1 ADC,<br>18 ch | 2    | 2   | 2                              | 1   | 53                            | PT, MR   |

| PIC24HJ64GP510A  | 100  | 64                              | 8                       | 8            | 9            | 8             | 8                          | 0                  | 1 ADC,<br>32 ch | 2    | 2   | 2                              | 1   | 85                            | PF, PT   |

| PIC24HJ128GP206A | 64   | 128                             | 8                       | 8            | 9            | 8             | 8                          | 0                  | 1 ADC,<br>18 ch | 2    | 2   | 2                              | 0   | 53                            | PT, MR   |

| PIC24HJ128GP210A | 100  | 128                             | 8                       | 8            | 9            | 8             | 8                          | 0                  | 1 ADC,<br>32 ch | 2    | 2   | 2                              | 0   | 85                            | PF, PT   |

| PIC24HJ128GP506A | 64   | 128                             | 8                       | 8            | 9            | 8             | 8                          | 0                  | 1 ADC,<br>18 ch | 2    | 2   | 2                              | 1   | 53                            | PT, MR   |

| PIC24HJ128GP510A | 100  | 128                             | 8                       | 8            | 9            | 8             | 8                          | 0                  | 1 ADC,<br>32 ch | 2    | 2   | 2                              | 1   | 85                            | PF, PT   |

| PIC24HJ128GP306A | 64   | 128                             | 16                      | 8            | 9            | 8             | 8                          | 0                  | 1 ADC,<br>18 ch | 2    | 2   | 2                              | 0   | 53                            | PT, MR   |

| PIC24HJ128GP310A | 100  | 128                             | 16                      | 8            | 9            | 8             | 8                          | 0                  | 1 ADC,<br>32 ch | 2    | 2   | 2                              | 0   | 85                            | PF, PT   |

| PIC24HJ256GP206A | 64   | 256                             | 16                      | 8            | 9            | 8             | 8                          | 0                  | 1 ADC,<br>18 ch | 2    | 2   | 2                              | 0   | 53                            | PT, MR   |

| PIC24HJ256GP210A | 100  | 256                             | 16                      | 8            | 9            | 8             | 8                          | 0                  | 1 ADC,<br>32 ch | 2    | 2   | 2                              | 0   | 85                            | PF, PT   |

| PIC24HJ256GP610A | 100  | 256                             | 16                      | 8            | 9            | 8             | 8                          | 0                  | 2 ADC,<br>32 ch | 2    | 2   | 2                              | 2   | 85                            | PF, PT   |

Note 1: RAM size is inclusive of 2 Kbytes DMA RAM.

2: Maximum I/O pin count includes pins shared by the peripheral functions.

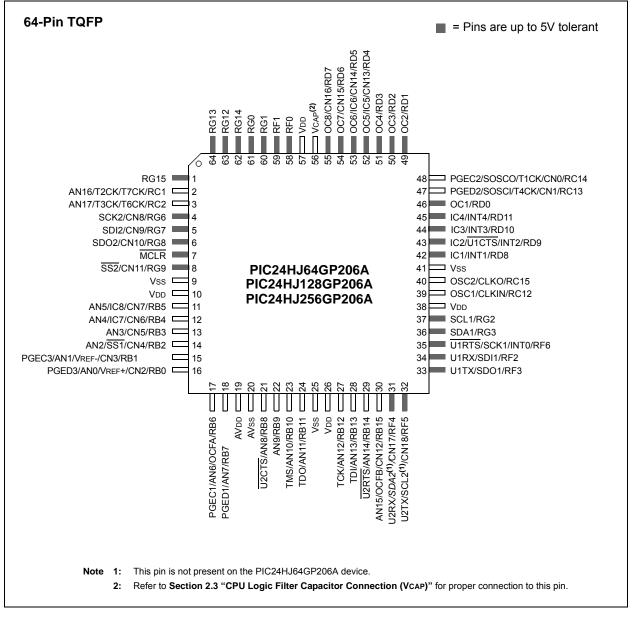

## Pin Diagrams (Continued)

#### Referenced Sources

This device data sheet is based on the following individual chapters of the *"dsPlC33F/PlC24H Family Reference Manual"*. These documents should be considered as the general reference for the operation of a particular module or device feature.

Note: To access the documents listed below, browse to the documentation section of the PIC24HJ256GP610A product page on the Microchip web site (www.microchip.com) or by selecting a family reference manual section from the following list.

In addition to parameters, features, and other documentation, the resulting page provides links to the related family reference manual sections.

- Section 1. "Introduction" (DS70197)

- Section 2. "CPU" (DS70204)

- Section 3. "Data Memory" (DS70202)

- Section 4. "Program Memory" (DS70203)

- Section 5. "Flash Programming" (DS70191)

- Section 6. "Interrupts" (DS70184)

- Section 7. "Oscillator" (DS70186)

- Section 8. "Reset" (DS70192)

- Section 9. "Watchdog Timer and Power-Saving Modes" (DS70196)

- Section 10. "I/O Ports" (DS70193)

- Section 11. "Timers" (DS70205)

- Section 12. "Input Capture" (DS70198)

- Section 13. "Output Compare" (DS70209)

- Section 16. "Analog-to-Digital Converter (ADC)" (DS70183)

- Section 17. "UART" (DS70188)

- Section 18. "Serial Peripheral Interface (SPI)" (DS70206)

- Section 19. "Inter-Integrated Circuit<sup>™</sup> (I2C<sup>™</sup>)" (DS70195)

- Section 20. "Data Converter Interface (DCI)" (DS70288)

- Section 21. "Enhanced Controller Area Network (ECAN™)" (DS70185)

- Section 22. "Direct Memory Access (DMA)" (DS70182)

- Section 23. "CodeGuard™ Security" (DS70199)

- Section 24. "Programming and Diagnostics" (DS70207)

- Section 25. "Device Configuration" (DS70194)

# 1.0 DEVICE OVERVIEW

Note: This data sheet summarizes the features of the PIC24HJXXXGPX06A/X08A/X10A family of devices. However, it is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to the latest family reference sections of the "dsPIC33F/PIC24H Family Reference Manual", which is available from the Microchip web site (www.microchip.com).

This document contains device specific information for the following devices:

- PIC24HJ64GP206A

- PIC24HJ64GP210A

- PIC24HJ64GP506A

- PIC24HJ64GP510A

- PIC24HJ128GP206A

- PIC24HJ128GP210A

- PIC24HJ128GP506A

- PIC24HJ128GP510A

- PIC24HJ128GP306A

- PIC24HJ128GP310A

- PIC24HJ256GP206A

- PIC24HJ256GP210A

- PIC24HJ256GP610A

The PIC24HJXXXGPX06A/X08A/X10A device family includes devices with different pin counts (64 and 100 pins), different program memory sizes (64 Kbytes, 128 Kbytes and 256 Kbytes) and different RAM sizes (8 Kbytes and 16 Kbytes).

This makes these families suitable for a wide variety of high-performance digital signal control applications. The devices are pin compatible with the dsPIC33F family of devices, and also share a very high degree of compatibility with the dsPIC30F family devices. This allows easy migration between device families as may be necessitated by the specific functionality, computational resource and system cost requirements of the application.

The PIC24HJXXXGPX06A/X08A/X10A device family employs a powerful 16-bit architecture, ideal for applications that rely on high-speed, repetitive computations, as well as control.

The 17 x 17 multiplier, hardware support for division operations, multi-bit data shifter, a large array of 16-bit working registers and a wide variety of data addressing modes. together provide the PIC24HJXXXGPX06A/X08A/X10A Central Processing Unit (CPU) with extensive mathematical processing capability. Flexible and deterministic interrupt handling, coupled with a powerful array of peripherals, renders the PIC24HJXXXGPX06A/X08A/X10A devices suitable for control applications. Further, Direct Memory Access (DMA) enables overhead-free transfer of data between several peripherals and a dedicated DMA RAM. Reliable, field programmable Flash program memory ensures scalability of applications that use PIC24HJXXXGPX06A/X08A/X10A devices.

Figure 1-1 shows a general block diagram of the various core and peripheral modules in the PIC24HJXXXGPX06A/X08A/X10A family of devices, while Table 1-1 lists the functions of the various pins shown in the pinout diagrams.

| SFR Name | SFR<br>Addr | Bit 15 | Bit 14                              | Bit 13 | Bit 12 | Bit 11 | Bit 10 | Bit 9 | Bit 8       | Bit 7       | Bit 6        | Bit 5 | Bit 4 | Bit 3  | Bit 2 | Bit 1    | Bit 0 | All<br>Resets |

|----------|-------------|--------|-------------------------------------|--------|--------|--------|--------|-------|-------------|-------------|--------------|-------|-------|--------|-------|----------|-------|---------------|

| OC1RS    | 0180        |        |                                     |        |        |        |        | Out   | tput Compar | e 1 Seconda | ary Register |       |       |        |       |          |       | xxxx          |

| OC1R     | 0182        |        |                                     |        |        |        |        |       | Output Co   | ompare 1 Re | egister      |       |       |        |       |          |       | xxxx          |

| OC1CON   | 0184        | —      | _                                   | OCSIDL | —      | _      | —      | —     | _           | —           | _            | _     | OCFLT | OCTSEL |       | OCM<2:0> |       | 0000          |

| OC2RS    | 0186        |        |                                     |        |        |        |        | Out   | tput Compar | e 2 Seconda | ary Register |       |       |        |       |          |       | xxxx          |

| OC2R     | 0188        |        |                                     |        |        |        |        |       | Output Co   | ompare 2 Re | egister      |       |       |        |       |          |       | xxxx          |

| OC2CON   | 018A        | _      |                                     | OCSIDL |        |        | _      |       |             |             |              |       | OCFLT | OCTSEL |       | OCM<2:0> |       | 0000          |

| OC3RS    | 018C        |        |                                     |        |        |        |        | Out   | tput Compar | e 3 Seconda | ary Register |       |       |        |       |          |       | xxxx          |

| OC3R     | 018E        |        | Output Compare 3 Register           |        |        |        |        |       |             |             |              |       | xxxx  |        |       |          |       |               |

| OC3CON   | 0190        | _      |                                     | OCSIDL |        |        | _      |       |             |             |              |       | OCFLT | OCTSEL |       | OCM<2:0> |       | 0000          |

| OC4RS    | 0192        |        | Output Compare 4 Secondary Register |        |        |        |        |       |             |             |              |       | xxxx  |        |       |          |       |               |

| OC4R     | 0194        |        | Output Compare 4 Register           |        |        |        |        |       |             |             |              |       | xxxx  |        |       |          |       |               |

| OC4CON   | 0196        | —      | -                                   | OCSIDL | —      | _      | —      | -     | —           | —           | _            | _     | OCFLT | OCTSEL |       | OCM<2:0> |       | 0000          |

| OC5RS    | 0198        |        |                                     |        |        |        |        | Out   | tput Compar | e 5 Seconda | ary Register |       |       |        |       |          |       | xxxx          |

| OC5R     | 019A        |        |                                     |        |        |        |        |       | Output Co   | ompare 5 Re | egister      |       |       |        |       |          |       | xxxx          |

| OC5CON   | 019C        | —      | -                                   | OCSIDL | —      | _      | —      | -     | —           | —           | _            | _     | OCFLT | OCTSEL |       | OCM<2:0> |       | 0000          |

| OC6RS    | 019E        |        |                                     |        |        |        |        | Out   | tput Compar | e 6 Seconda | ary Register |       |       |        |       |          |       | xxxx          |

| OC6R     | 01A0        |        |                                     | _      |        |        |        |       | Output Co   | ompare 6 Re | egister      |       |       | _      |       |          |       | xxxx          |

| OC6CON   | 01A2        | —      | _                                   | OCSIDL | —      | —      | _      | —     | —           | —           | —            | —     | OCFLT | OCTSEL |       | OCM<2:0> |       | 0000          |

| OC7RS    | 01A4        |        |                                     |        |        |        |        | Out   | tput Compar | e 7 Seconda | ary Register |       |       |        |       |          |       | xxxx          |

| OC7R     | 01A6        |        |                                     |        |        |        |        |       | Output Co   | ompare 7 Re | egister      |       |       |        |       |          |       | xxxx          |

| OC7CON   | 01A8        | _      |                                     | OCSIDL | —      | _      | _      | _     | —           | —           | —            | -     | OCFLT | OCTSEL |       | OCM<2:0> |       | 0000          |

| OC8RS    | 01AA        |        |                                     |        |        |        |        | Out   | tput Compar | e 8 Seconda | ary Register |       |       |        |       |          |       | xxxx          |

| OC8R     | 01AC        |        |                                     |        |        |        |        |       | Output Co   | ompare 8 Re | egister      |       |       |        |       |          |       | xxxx          |

| OC8CON   | 01AE        | _      |                                     | OCSIDL | _      | _      | —      | _     | _           | _           | _            |       | OCFLT | OCTSEL |       | OCM<2:0> |       | 0000          |

#### TABLE 4-8: OUTPUT COMPARE REGISTER MAP

Legend: x = unknown value on Reset, — = unimplemented, read as '0'. Reset values are shown in hexadecimal for PinHigh devices.

# \_\_\_\_\_

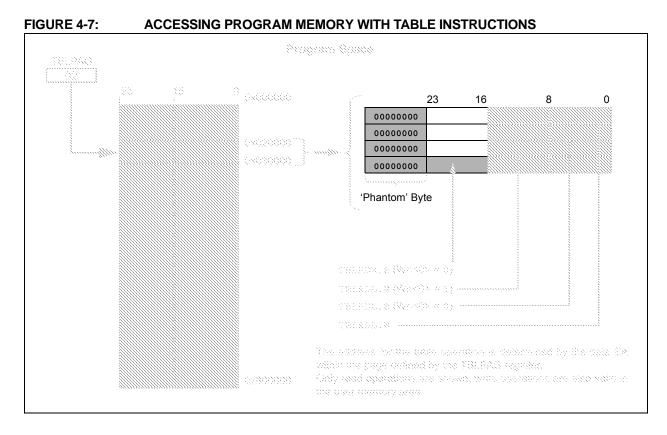

#### 4.4.2 DATA ACCESS FROM PROGRAM MEMORY USING TABLE INSTRUCTIONS

The TBLRDL and TBLWTL instructions offer a direct method of reading or writing the lower word of any address within the program space without going through data space. The TBLRDH and TBLWTH instructions are the only method to read or write the upper 8 bits of a program space word as data.

The PC is incremented by two for each successive 24-bit program word. This allows program memory addresses to directly map to data space addresses. Program memory can thus be regarded as two 16-bit, word wide address spaces, residing side by side, each with the same address range. TBLRDL and TBLWTL access the space which contains the least significant data word and TBLRDH and TBLWTH access the space which contains the upper data byte.

Two table instructions are provided to move byte or word sized (16-bit) data to and from program space. Both function as either byte or word operations.

TBLRDL (Table Read Low): In Word mode, it maps the lower word of the program space location (P<15:0>) to a data address (D<15:0>).

In Byte mode, either the upper or lower byte of the lower program word is mapped to the lower byte of a data address. The upper byte is selected when Byte Select is '1'; the lower byte is selected when it is '0'.  TBLRDH (Table Read High): In Word mode, it maps the entire upper word of a program address (P<23:16>) to a data address. Note that D<15:8>, the 'phantom byte', will always be '0'.

In Byte mode, it maps the upper or lower byte of the program word to D<7:0> of the data address, as above. Note that the data will always be '0' when the upper 'phantom' byte is selected (Byte Select = 1).

In a similar fashion, two table instructions, TBLWTH and TBLWTL, are used to write individual bytes or words to a program space address. The details of their operation are explained in **Section 5.0 "Flash Program Memory"**.

For all table operations, the area of program memory space to be accessed is determined by the Table Page register (TBLPAG). TBLPAG covers the entire program memory space of the device, including user and configuration spaces. When TBLPAG<7> = 0, the table page is located in the user memory space. When TBLPAG<7> = 1, the page is located in configuration space.

# 5.0 FLASH PROGRAM MEMORY

- Note 1: This data sheet summarizes the features of the PIC24HJXXXGPX06A/X08A/X10A family of devices. However, it is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to Section 5. "Flash Programming" (DS70191) of the "dsPIC33F/PIC24H Family Reference Manual", which is available from the Microchip web site (www.microchip.com).

- Some registers and associated bits described in this section may not be available on all devices. Refer to Section 4.0 "Memory Organization" in this data sheet for device-specific register and bit information.

The PIC24HJXXXGPX06A/X08A/X10A devices contain internal Flash program memory for storing and executing application code. The memory is readable, writable and erasable during normal operation over the entire VDD range.

Flash memory can be programmed in two ways:

- In-Circuit Serial Programming<sup>™</sup> (ICSP<sup>™</sup>) programming capability

- 2. Run-Time Self-Programming (RTSP)

ICSP programming capability allows a PIC24HJXXXGPX06A/X08A/X10A device to be serially programmed while in the end application circuit. This is simply done with two lines for programming clock and programming data (one of the alternate programming pin pairs: PGECx/PGEDx, and three other lines for power (VDD), ground (VSS) and Master Clear (MCLR). This allows customers to manufacture boards with unprogrammed devices and then program the digital signal controller just before shipping the product. This also allows the most recent firmware or a custom firmware to be programmed.

RTSP is accomplished using TBLRD (table read) and TBLWT (table write) instructions. With RTSP, the user can write program memory data either in blocks or 'rows' of 64 instructions (192 bytes) at a time, or single instructions and erase program memory in blocks or 'pages' of 512 instructions (1536 bytes) at a time.

# 5.1 Table Instructions and Flash Programming

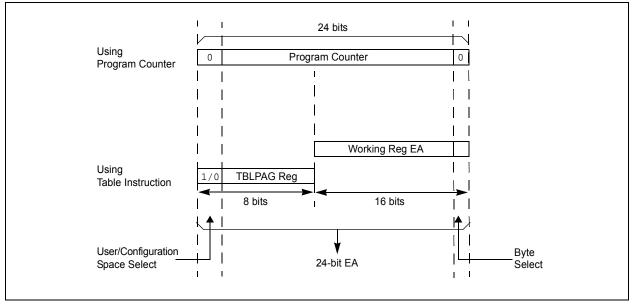

Regardless of the method used, all programming of Flash memory is done with the table read and table write instructions. These allow direct read and write access to the program memory space from the data memory while the device is in normal operating mode. The 24-bit target address in the program memory is formed using bits<7:0> of the TBLPAG register and the Effective Address (EA) from a W register specified in the table instruction, as shown in Figure 5-1.

The TBLRDL and the TBLWTL instructions are used to read or write to bits<15:0> of program memory. TBLRDL and TBLWTL can access program memory in both Word and Byte modes.

The TBLRDH and TBLWTH instructions are used to read or write to bits<23:16> of program memory. TBLRDH and TBLWTH can also access program memory in Word or Byte mode.

#### FIGURE 5-1: ADDRESSING FOR TABLE REGISTERS

#### REGISTER 8-3: DMAXSTA: DMA CHANNEL x RAM START ADDRESS OFFSET REGISTER A

| R/W-0           | R/W-0 | R/W-0            | R/W-0 | R/W-0            | R/W-0           | R/W-0           | R/W-0 |

|-----------------|-------|------------------|-------|------------------|-----------------|-----------------|-------|

|                 |       |                  | STA   | <15:8>           |                 |                 |       |

| bit 15          |       |                  |       |                  |                 |                 | bit 8 |

|                 |       |                  |       |                  |                 |                 |       |

| R/W-0           | R/W-0 | R/W-0            | R/W-0 | R/W-0            | R/W-0           | R/W-0           | R/W-0 |

|                 |       |                  | STA   | <7:0>            |                 |                 |       |

| bit 7           |       |                  |       |                  |                 |                 | bit 0 |

|                 |       |                  |       |                  |                 |                 |       |

| Legend:         |       |                  |       |                  |                 |                 |       |

| R = Readable    | bit   | W = Writable I   | bit   | U = Unimpler     | nented bit, rea | d as '0'        |       |

| -n = Value at P | OR    | '1' = Bit is set |       | '0' = Bit is cle | ared            | x = Bit is unkr | nown  |

bit 15-0 STA<15:0>: Primary DMA RAM Start Address bits (source or destination)

#### REGISTER 8-4: DMAxSTB: DMA CHANNEL x RAM START ADDRESS OFFSET REGISTER B

| R/W-0           | R/W-0 | R/W-0            | R/W-0 | R/W-0            | R/W-0           | R/W-0           | R/W-0 |

|-----------------|-------|------------------|-------|------------------|-----------------|-----------------|-------|

|                 |       |                  | STB   | <15:8>           |                 |                 |       |

| bit 15          |       |                  |       |                  |                 |                 | bit 8 |

|                 |       |                  |       |                  |                 |                 |       |

| R/W-0           | R/W-0 | R/W-0            | R/W-0 | R/W-0            | R/W-0           | R/W-0           | R/W-0 |

|                 |       |                  | STE   | 3<7:0>           |                 |                 |       |

| bit 7           |       |                  |       |                  |                 |                 | bit 0 |

| Legend:         |       |                  |       |                  |                 |                 |       |

| R = Readable    | bit   | W = Writable b   | it    | U = Unimpler     | mented bit, rea | ad as '0'       |       |

| -n = Value at P | POR   | '1' = Bit is set |       | '0' = Bit is cle | ared            | x = Bit is unkı | nown  |

bit 15-0 STB<15:0>: Secondary DMA RAM Start Address bits (source or destination)

## REGISTER 10-2: PMD2: PERIPHERAL MODULE DISABLE CONTROL REGISTER 2 (CONTINUED)

| bit 3 | <b>OC4MD:</b> Output Compare 4 Module Disable bit                                                        |

|-------|----------------------------------------------------------------------------------------------------------|

|       | <ul><li>1 = Output Compare 4 module is disabled</li><li>0 = Output Compare 4 module is enabled</li></ul> |

| bit 2 | <b>OC3MD:</b> Output Compare 3 Module Disable bit                                                        |

|       | <ul><li>1 = Output Compare 3 module is disabled</li><li>0 = Output Compare 3 module is enabled</li></ul> |

| bit 1 | <b>OC2MD:</b> Output Compare 2 Module Disable bit                                                        |

|       | <ul><li>1 = Output Compare 2 module is disabled</li><li>0 = Output Compare 2 module is enabled</li></ul> |

| bit 0 | <b>OC1MD:</b> Output Compare 1 Module Disable bit                                                        |

|       | <ul><li>1 = Output Compare 1 module is disabled</li><li>0 = Output Compare 1 module is enabled</li></ul> |

NOTES:

| R/W-0          | U-0                                                             | R/W-0                                                                                                                         | R/W-1 HC                                | R/W-0              | R/W-0                      | R/W-0             | R/W-0         |  |  |  |  |  |  |

|----------------|-----------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------|--------------------|----------------------------|-------------------|---------------|--|--|--|--|--|--|

| I2CEN          | _                                                               | I2CSIDL                                                                                                                       | SCLREL                                  | IPMIEN             | A10M                       | DISSLW            | SMEN          |  |  |  |  |  |  |

| bit 15         |                                                                 |                                                                                                                               |                                         |                    |                            |                   | bit 8         |  |  |  |  |  |  |

| <b>D</b> 444 0 | DAVA                                                            | <b>D</b> 444 0                                                                                                                |                                         |                    |                            |                   |               |  |  |  |  |  |  |

| R/W-0          | R/W-0                                                           | R/W-0                                                                                                                         | R/W-0 HC                                | R/W-0 HC           | R/W-0 HC                   | R/W-0 HC          | R/W-0 HC      |  |  |  |  |  |  |

| GCEN           | STREN                                                           | ACKDT                                                                                                                         | ACKEN                                   | RCEN               | PEN                        | RSEN              | SEN           |  |  |  |  |  |  |

| bit 7          |                                                                 |                                                                                                                               |                                         |                    |                            |                   | bit (         |  |  |  |  |  |  |

| Legend:        |                                                                 | U = Unimpler                                                                                                                  | nented bit, rea                         | d as '0'           |                            |                   |               |  |  |  |  |  |  |

| R = Readable   | e bit                                                           | W = Writable                                                                                                                  | bit                                     | HS = Set in h      | ardware                    | HC = Cleared      | in hardware   |  |  |  |  |  |  |

| -n = Value at  | POR                                                             | '1' = Bit is se                                                                                                               |                                         | '0' = Bit is cle   | ared                       | x = Bit is unkr   | nown          |  |  |  |  |  |  |

| bit 15         | <b>12CEN:</b> 12Cx                                              | Enable bit                                                                                                                    |                                         |                    |                            |                   |               |  |  |  |  |  |  |

|                |                                                                 |                                                                                                                               | e and configur                          | es the SDAx a      | Ind SCLx pins a            | as serial port pi | าร            |  |  |  |  |  |  |

|                | 0 = Disables                                                    | the I2Cx modu                                                                                                                 | le. All I <sup>2</sup> C pins           | are controlled     | by port functio            | ns.               |               |  |  |  |  |  |  |

| bit 14         | Unimplemen                                                      | ted: Read as                                                                                                                  | 0'                                      |                    |                            |                   |               |  |  |  |  |  |  |

| bit 13         |                                                                 | p in Idle Mode                                                                                                                |                                         |                    |                            |                   |               |  |  |  |  |  |  |

|                |                                                                 |                                                                                                                               | eration when de                         |                    | n Idle mode                |                   |               |  |  |  |  |  |  |

| bit 12         |                                                                 | -                                                                                                                             | ontrol bit (wher                        |                    | l <sup>2</sup> C slave)    |                   |               |  |  |  |  |  |  |

|                | 1 = Release S                                                   |                                                                                                                               |                                         | · op ol a lang a o |                            |                   |               |  |  |  |  |  |  |

|                | 0 = Hold SCL                                                    | 0 = Hold SCLx clock low (clock stretch)                                                                                       |                                         |                    |                            |                   |               |  |  |  |  |  |  |

|                | $\frac{\text{If STREN} = 1}{\text{Dit is } \text{DAV}(i)}$      | If STREN = 1:<br>Bit is R/W (i.e., software may write '0' to initiate stretch and write '1' to release clock). Hardware clear |                                         |                    |                            |                   |               |  |  |  |  |  |  |

|                |                                                                 |                                                                                                                               |                                         |                    | d of slave rece            |                   | lardware clea |  |  |  |  |  |  |

|                | If STREN = 0                                                    |                                                                                                                               |                                         |                    |                            |                   |               |  |  |  |  |  |  |

|                |                                                                 |                                                                                                                               | only write '1'                          | to release cloc    | k). Hardware c             | lear at beginnir  | ig of slave   |  |  |  |  |  |  |

| L:1 44         | transmission.                                                   |                                                                                                                               |                                         | - t. I t f (ID     |                            |                   |               |  |  |  |  |  |  |

| bit 11         |                                                                 | -                                                                                                                             | al Managemer                            | -                  | MI) Enable bit             |                   |               |  |  |  |  |  |  |

|                | $0 = IPMI \mod$                                                 |                                                                                                                               |                                         | CKIIOWIEUyeu       |                            |                   |               |  |  |  |  |  |  |

| bit 10         | A10M: 10-bit                                                    | Slave Address                                                                                                                 | s bit                                   |                    |                            |                   |               |  |  |  |  |  |  |

|                |                                                                 | is a 10-bit slav                                                                                                              |                                         |                    |                            |                   |               |  |  |  |  |  |  |

|                |                                                                 | is a 7-bit slave                                                                                                              |                                         |                    |                            |                   |               |  |  |  |  |  |  |

| bit 9          |                                                                 | able Slew Rate                                                                                                                |                                         |                    |                            |                   |               |  |  |  |  |  |  |

|                |                                                                 | control disable                                                                                                               |                                         |                    |                            |                   |               |  |  |  |  |  |  |

| bit 8          |                                                                 | us Input Levels                                                                                                               |                                         |                    |                            |                   |               |  |  |  |  |  |  |

|                |                                                                 | -                                                                                                                             | ls compliant wi                         | ith SMBus spe      | cification                 |                   |               |  |  |  |  |  |  |

|                |                                                                 | MBus input th                                                                                                                 |                                         |                    |                            |                   |               |  |  |  |  |  |  |

|                |                                                                 |                                                                                                                               | e bit (when ope                         | -                  | -                          |                   |               |  |  |  |  |  |  |

| bit 7          |                                                                 |                                                                                                                               | a deneral call a                        | address is rece    | ived in the I2C            | xRSR              |               |  |  |  |  |  |  |

| bit 7          | 1 = Enable in                                                   |                                                                                                                               |                                         |                    |                            |                   |               |  |  |  |  |  |  |

| bit 7          | (module                                                         | iterrupt when a<br>is enabled for<br>call address di                                                                          | reception)                              |                    |                            |                   |               |  |  |  |  |  |  |

| bit 7<br>bit 6 | (module)<br>0 = General (                                       | is enabled for<br>call address di                                                                                             | reception)                              |                    | as I <sup>2</sup> C slave) |                   |               |  |  |  |  |  |  |

|                | (module)<br>0 = General o<br><b>STREN:</b> SCL<br>Used in conju | is enabled for<br>call address di<br>x Clock Stretcl<br>inction with SC                                                       | reception)<br>sabled<br>n Enable bit (w | hen operating      | as I <sup>2</sup> C slave) |                   |               |  |  |  |  |  |  |

#### **REGISTER 19-4:** CIFCTRL: ECAN™ MODULE FIFO CONTROL REGISTER

| R/W-0         | R/W-0                                                                             | R/W-0                                                                                                                                          | U-0              | U-0              | U-0             | U-0             | U-0    |

|---------------|-----------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------|------------------|------------------|-----------------|-----------------|--------|

|               | DMABS<2:0>                                                                        |                                                                                                                                                |                  | _                | _               | —               | _      |

| bit 15        |                                                                                   |                                                                                                                                                |                  |                  |                 |                 | bit 8  |

| U-0           | U-0                                                                               | U-0                                                                                                                                            | R/W-0            | R/W-0            | R/W-0           | R/W-0           | R/W-0  |

| 0-0           | 0-0                                                                               | 0-0                                                                                                                                            | R/W-U            | K/ VV-U          | FSA<4:0>        | R/W-0           | R/ W-U |

| bit 7         |                                                                                   |                                                                                                                                                |                  |                  | 107.4.02        |                 | bit 0  |

|               |                                                                                   |                                                                                                                                                |                  |                  |                 |                 | bit o  |

| Legend:       |                                                                                   |                                                                                                                                                |                  |                  |                 |                 |        |

| R = Readable  | e bit                                                                             | W = Writable I                                                                                                                                 | oit              | U = Unimpler     | nented bit, rea | d as '0'        |        |

| -n = Value at | POR                                                                               | '1' = Bit is set                                                                                                                               |                  | '0' = Bit is cle | ared            | x = Bit is unkr | nown   |

| bit 12-5      | 100 = 16 buff<br>011 = 12 buff<br>010 = 8 buffe<br>001 = 6 buffe<br>000 = 4 buffe | fers in DMA RA<br>fers in DMA RA<br>fers in DMA RA<br>ers in DMA RAM<br>ers in DMA RAM<br>ers in DMA RAM<br>ers in DMA RAM<br>nted: Read as '0 | M<br>M<br>1<br>1 |                  |                 |                 |        |

| bit 4-0       | -                                                                                 | IFO Area Starts                                                                                                                                |                  | ito              |                 |                 |        |

| UIL 4-U       | FSA<4:0>: F<br>11111 = RB3<br>11110 = RB3<br>•<br>•<br>•<br>•<br>•<br>•           | 31 buffer<br>30 buffer                                                                                                                         | with buller bi   | 15               |                 |                 |        |

#### REGISTER 19-18: CiFMSKSEL1: ECAN™ MODULE FILTER 7-0 MASK SELECTION REGISTER

| R/W-0         | R/W-0               | R/W-0                              | R/W-0            | R/W-0             | R/W-0           | R/W-0           | R/W-   | 0     |

|---------------|---------------------|------------------------------------|------------------|-------------------|-----------------|-----------------|--------|-------|

| F7M           | SK<1:0>             | F6MSł                              | <<1:0>           | F5MS              | K<1:0>          | F4MSI           | K<1:0> |       |

| bit 15        |                     |                                    |                  |                   |                 |                 |        | bit 8 |

| R/W-0         | R/W-0               | R/W-0                              | R/W-0            | R/W-0             | R/W-0           | R/W-0           | R/W-   | .0    |

| -             | SK<1:0>             | F2MSł                              |                  | -                 | K<1:0>          |                 | K<1:0> | 0     |

| bit 7         |                     | 1 2100                             | ( 1.0            | 1 1110            | 11.0            | 1 0100          | -      | bit 0 |

|               |                     |                                    |                  |                   |                 |                 |        |       |

| Legend:       |                     |                                    |                  |                   |                 |                 |        |       |

| R = Readabl   | e bit               | W = Writable                       | bit              | U = Unimplen      | nented bit, rea | d as '0'        |        |       |

| -n = Value at | POR                 | '1' = Bit is set                   |                  | '0' = Bit is clea | ared            | x = Bit is unkr | nown   |       |

|               |                     |                                    |                  |                   |                 |                 |        |       |

| bit 15-14     |                     | : Mask Source                      | e for Filter 7 b | it                |                 |                 |        |       |

|               |                     | ed; do not use<br>ance Mask 2 reg  | nisters contair  | n mask            |                 |                 |        |       |

|               | •                   | ance Mask 1 reg                    |                  |                   |                 |                 |        |       |

|               |                     | ance Mask 0 reg                    |                  |                   |                 |                 |        |       |

| bit 13-12     |                     | : Mask Source                      | e for Filter 6 b | it                |                 |                 |        |       |

|               |                     | ed; do not use<br>ance Mask 2 reg  | nistore contair  | mask              |                 |                 |        |       |

|               |                     | ance Mask 2 reg                    |                  |                   |                 |                 |        |       |

|               | •                   | ance Mask 0 reg                    | •                |                   |                 |                 |        |       |

| bit 11-10     |                     | : Mask Source                      | e for Filter 5 b | it                |                 |                 |        |       |

|               |                     | ed; do not use                     | niatoro contair  | mool              |                 |                 |        |       |

|               |                     | ance Mask 2 reg<br>ance Mask 1 reg |                  |                   |                 |                 |        |       |

|               |                     | ance Mask 0 reg                    |                  |                   |                 |                 |        |       |

| bit 9-8       | F4MSK<1:0>          | . Mask Source                      | e for Filter 4 b | it                |                 |                 |        |       |

|               |                     | ed; do not use                     |                  |                   |                 |                 |        |       |

|               | -                   | ance Mask 2 reg<br>ance Mask 1 reg |                  |                   |                 |                 |        |       |

|               |                     | ance Mask 0 reg                    |                  |                   |                 |                 |        |       |

| bit 7-6       | F3MSK<1:0>          | . Mask Source                      | e for Filter 3 b | it                |                 |                 |        |       |

|               |                     | ed; do not use                     |                  |                   |                 |                 |        |       |

|               |                     | ance Mask 2 reg<br>ance Mask 1 reg |                  |                   |                 |                 |        |       |

|               |                     | ance Mask 0 reg                    |                  |                   |                 |                 |        |       |

| bit 5-4       | -                   | : Mask Source                      | -                |                   |                 |                 |        |       |

|               |                     | ed; do not use                     |                  |                   |                 |                 |        |       |

|               |                     | ance Mask 2 reg<br>ance Mask 1 reg |                  |                   |                 |                 |        |       |

|               |                     | ance Mask 1 reg                    |                  |                   |                 |                 |        |       |

| bit 3-2       |                     | . Mask Source                      |                  |                   |                 |                 |        |       |

|               |                     | ed; do not use                     |                  |                   |                 |                 |        |       |

|               |                     | ance Mask 2 reg                    |                  |                   |                 |                 |        |       |

|               |                     | ance Mask 1 reg<br>ance Mask 0 reg |                  |                   |                 |                 |        |       |

| bit 1-0       | -                   | : Mask Source                      | -                |                   |                 |                 |        |       |

|               |                     | ed; do not use                     |                  |                   |                 |                 |        |       |

|               | 10 <b>= Accepta</b> | ance Mask 2 reg                    |                  |                   |                 |                 |        |       |

|               |                     | ance Mask 1 reg                    |                  |                   |                 |                 |        |       |

|               | 00 = Accepta        | ance Mask 0 reg                    | jisters contair  | IIIIask           |                 |                 |        |       |

| Bit Field | Register | RTSP<br>Effect | Description                                                                                                                                                                                                                                                               |

|-----------|----------|----------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| SSS<2:0>  | FSS      | Immediate      | Secure Segment Program Flash Code Protection Size<br>(FOR 128K and 256K DEVICES)<br>x11 = No Secure program Flash segment                                                                                                                                                 |

|           |          |                | Secure space is 8K IW less BS<br>110 = Standard security; secure program Flash segment starts at End of<br>BS, ends at 0x003FFE<br>010 = High security; secure program Flash segment starts at End of BS,<br>ends at 0x003FFE                                             |

|           |          |                | Secure space is 16K IW less BS<br>101 = Standard security; secure program Flash segment starts at End of<br>BS, ends at 0x007FFE<br>001 = High security; secure program Flash segment starts at End of BS,<br>ends at 0x007FFE                                            |

|           |          |                | Secure space is 32K IW less BS<br>100 = Standard security; secure program Flash segment starts at End of<br>BS, ends at 0x00FFFE<br>000 = High security; secure program Flash segment starts at End of BS,<br>ends at 0x00FFFE                                            |

|           |          |                | (FOR 64K DEVICES)<br>x11 = No Secure program Flash segment                                                                                                                                                                                                                |

|           |          |                | Secure space is 4K IW less BS<br>110 = Standard security; secure program Flash segment starts at End of<br>BS, ends at 0x001FFE<br>010 = High security; secure program Flash segment starts at End of BS,<br>ends at 0x001FFE                                             |

|           |          |                | Secure space is 8K IW less BS<br>101 = Standard security; secure program Flash segment starts at End of<br>BS, ends at 0x003FFE<br>001 = High security; secure program Flash segment starts at End of BS,<br>ends at 0x003FFE                                             |

|           |          |                | Secure space is 16K IW less BS<br>100 = Standard security; secure program Flash segment starts at End of<br>BS, ends at 0x007FFE<br>000 = High security; secure program Flash segment starts at End of BS,<br>ends at 0x007FFE                                            |

| RSS<1:0>  | FSS      | Immediate      | Secure Segment RAM Code Protection<br>11 = No Secure RAM defined<br>10 = Secure RAM is 256 Bytes less BS RAM<br>01 = Secure RAM is 2048 Bytes less BS RAM<br>00 = Secure RAM is 4096 Bytes less BS RAM                                                                    |

| GSS<1:0>  | FGS      | Immediate      | General Segment Code-Protect bit<br>11 = User program memory is not code-protected<br>10 = Standard Security; general program Flash segment starts at End of<br>SS, ends at EOM<br>0x = High Security; general program Flash segment starts at End of ESS,<br>ends at EOM |

| GWRP      | FGS      | Immediate      | General Segment Write-Protect bit<br>1 = User program memory is not write-protected<br>0 = User program memory is write-protected                                                                                                                                         |

#### TABLE 21-2: CONFIGURATION BITS DESCRIPTION (CONTINUED)

# 22.0 INSTRUCTION SET SUMMARY

**Note:** This data sheet summarizes the features of the PIC24HJXXXGPX06A/X08A/X10A families of devices. However, it is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to the related section in the "dsPIC33F/PIC24H Family Reference Manual", which is available from the Microchip web site (www.microchip.com).

The PIC24H instruction set is identical to that of the PIC24F, and is a subset of the dsPIC30F/33F instruction set.

Most instructions are a single program memory word (24 bits). Only three instructions require two program memory locations.

Each single-word instruction is a 24-bit word, divided into an 8-bit opcode, which specifies the instruction type and one or more operands, which further specify the operation of the instruction.

The instruction set is highly orthogonal and is grouped into five basic categories:

- · Word or byte-oriented operations

- · Bit-oriented operations

- · Literal operations

- DSP operations

- · Control operations

Table 22-1 shows the general symbols used in describing the instructions.

The PIC24H instruction set summary in Table 22-2 lists all the instructions, along with the status flags affected by each instruction.

Most word or byte-oriented W register instructions (including barrel shift instructions) have three operands:

- The first source operand which is typically a register 'Wb' without any address modifier

- The second source operand which is typically a register 'Ws' with or without an address modifier

- The destination of the result which is typically a register 'Wd' with or without an address modifier

However, word or byte-oriented file register instructions have two operands:

- · The file register specified by the value 'f'

- The destination, which could either be the file register 'f' or the W0 register, which is denoted as 'WREG'

Most bit-oriented instructions (including simple rotate/shift instructions) have two operands:

- The W register (with or without an address modifier) or file register (specified by the value of 'Ws' or 'f')

- The bit in the W register or file register (specified by a literal value or indirectly by the contents of register 'Wb')

The literal instructions that involve data movement may use some of the following operands:

- A literal value to be loaded into a W register or file register (specified by the value of 'k')

- The W register or file register where the literal value is to be loaded (specified by 'Wb' or 'f')

However, literal instructions that involve arithmetic or logical operations use some of the following operands:

- The first source operand which is a register 'Wb' without any address modifier

- The second source operand which is a literal value

- The destination of the result (only if not the same as the first source operand) which is typically a register 'Wd' with or without an address modifier

The control instructions may use some of the following operands:

- A program memory address

- The mode of the table read and table write instructions

All instructions are a single word, except for certain double word instructions, which were made double word instructions so that all the required information is available in these 48 bits. In the second word, the 8 MSbs are '0's. If this second word is executed as an instruction (by itself), it will execute as a NOP.

Most single-word instructions are executed in a single instruction cycle, unless a conditional test is true, or the program counter is changed as a result of the instruction. In these cases, the execution takes two instruction cycles with the additional instruction cycle(s) executed as a NOP. Notable exceptions are the BRA (unconditional/computed branch), indirect CALL/GOTO, all table reads and writes and RETURN/RETFIE instructions, which are single-word instructions but take two or three cycles. Certain instructions that involve skipping over the subsequent instruction require either two or three cycles if the skip is performed, depending on whether the instruction being skipped is a single-word or double word instruction. Moreover, double word moves require two cycles. The double word instructions execute in two instruction cycles.

Note: For more details on the instruction set, refer to the *"16-bit MCU and DSC Programmer's Reference Manual"* (DS70157).

#### TABLE 22-1: SYMBOLS USED IN OPCODE DESCRIPTIONS

| Field           | Description                                                                                                                   |

|-----------------|-------------------------------------------------------------------------------------------------------------------------------|

| #text           | Means literal defined by "text"                                                                                               |

| (text)          | Means "content of text"                                                                                                       |

| [text]          | Means "the location addressed by text"                                                                                        |

| { }             | Optional field or operation                                                                                                   |

| <n:m></n:m>     | Register bit field                                                                                                            |

| .b              | Byte mode selection                                                                                                           |

| .d              | Double Word mode selection                                                                                                    |

| .S              | Shadow register select                                                                                                        |

| .W              | Word mode selection (default)                                                                                                 |

| bit4            | 4-bit bit selection field (used in word addressed instructions) $\in \{015\}$                                                 |

| C, DC, N, OV, Z | MCU Status bits: Carry, Digit Carry, Negative, Overflow, Sticky Zero                                                          |

| Expr            | Absolute address, label or expression (resolved by the linker)                                                                |

| f               | File register address ∈ {0x00000x1FFF}                                                                                        |

| lit1            | 1-bit unsigned literal $\in \{0,1\}$                                                                                          |

| lit4            | 4-bit unsigned literal ∈ {015}                                                                                                |

| lit5            | 5-bit unsigned literal $\in \{031\}$                                                                                          |

| lit8            | 8-bit unsigned literal ∈ {0255}                                                                                               |

| lit10           | 10-bit unsigned literal ∈ {0255} for Byte mode, {0:1023} for Word mode                                                        |

| lit14           | 14-bit unsigned literal ∈ {016384}                                                                                            |

| lit16           | 16-bit unsigned literal ∈ {065535}                                                                                            |

| lit23           | 23-bit unsigned literal ∈ {08388608}; LSB must be '0'                                                                         |

| None            | Field does not require an entry, may be blank                                                                                 |

| PC              | Program Counter                                                                                                               |

| Slit10          | 10-bit signed literal ∈ {-512511}                                                                                             |

| Slit16          | 16-bit signed literal ∈ {-3276832767}                                                                                         |

| Slit6           | 6-bit signed literal ∈ {-1616}                                                                                                |

| Wb              | Base W register ∈ {W0W15}                                                                                                     |

| Wd              | Destination W register ∈ { Wd, [Wd], [Wd++], [Wd], [++Wd], [Wd] }                                                             |

| Wdo             | Destination W register ∈<br>{ Wnd, [Wnd], [Wnd++], [Wnd], [++Wnd], [Wnd], [Wnd+Wb] }                                          |

| Wm,Wn           | Dividend, Divisor working register pair (direct addressing)                                                                   |

| Wm*Wm           | Multiplicand and Multiplier working register pair for Square instructions ∈<br>{W4 * W4,W5 * W5,W6 * W6,W7 * W7}              |

| Wm*Wn           | Multiplicand and Multiplier working register pair for DSP instructions ∈<br>{W4 * W5,W4 * W6,W4 * W7,W5 * W6,W5 * W7,W6 * W7} |

| Wn              | One of 16 working registers $\in$ {W0W15}                                                                                     |

| Wnd             | One of 16 destination working registers ∈ {W0W15}                                                                             |

| Wns             | One of 16 source working registers ∈ {W0W15}                                                                                  |

| WREG            | W0 (working register used in file register instructions)                                                                      |

| Ws              | Source W register ∈ { Ws, [Ws], [Ws++], [Ws], [++Ws], [Ws] }                                                                  |

| Wso             | Source W register ∈<br>{ Wns, [Wns], [Wns++], [Wns], [++Wns], [Wns], [Wns+Wb] }                                               |

## 23.7 MPLAB SIM Software Simulator

The MPLAB SIM Software Simulator allows code development in a PC-hosted environment by simulating the PIC MCUs and dsPIC<sup>®</sup> DSCs on an instruction level. On any given instruction, the data areas can be examined or modified and stimuli can be applied from a comprehensive stimulus controller. Registers can be logged to files for further run-time analysis. The trace buffer and logic analyzer display extend the power of the simulator to record and track program execution, actions on I/O, most peripherals and internal registers.

The MPLAB SIM Software Simulator fully supports symbolic debugging using the MPLAB C Compilers, and the MPASM and MPLAB Assemblers. The software simulator offers the flexibility to develop and debug code outside of the hardware laboratory environment, making it an excellent, economical software development tool.

#### 23.8 MPLAB REAL ICE In-Circuit Emulator System

MPLAB REAL ICE In-Circuit Emulator System is Microchip's next generation high-speed emulator for Microchip Flash DSC and MCU devices. It debugs and programs PIC<sup>®</sup> Flash MCUs and dsPIC<sup>®</sup> Flash DSCs with the easy-to-use, powerful graphical user interface of the MPLAB Integrated Development Environment (IDE), included with each kit.

The emulator is connected to the design engineer's PC using a high-speed USB 2.0 interface and is connected to the target with either a connector compatible with incircuit debugger systems (RJ11) or with the new high-speed, noise tolerant, Low-Voltage Differential Signal (LVDS) interconnection (CAT5).

The emulator is field upgradable through future firmware downloads in MPLAB IDE. In upcoming releases of MPLAB IDE, new devices will be supported, and new features will be added. MPLAB REAL ICE offers significant advantages over competitive emulators including low-cost, full-speed emulation, run-time variable watches, trace analysis, complex breakpoints, a ruggedized probe interface and long (up to three meters) interconnection cables.

#### 23.9 MPLAB ICD 3 In-Circuit Debugger System

MPLAB ICD 3 In-Circuit Debugger System is Microchip's most cost effective high-speed hardware debugger/programmer for Microchip Flash Digital Signal Controller (DSC) and microcontroller (MCU) devices. It debugs and programs PIC<sup>®</sup> Flash microcontrollers and dsPIC<sup>®</sup> DSCs with the powerful, yet easyto-use graphical user interface of MPLAB Integrated Development Environment (IDE).

The MPLAB ICD 3 In-Circuit Debugger probe is connected to the design engineer's PC using a high-speed USB 2.0 interface and is connected to the target with a connector compatible with the MPLAB ICD 2 or MPLAB REAL ICE systems (RJ-11). MPLAB ICD 3 supports all MPLAB ICD 2 headers.

## 23.10 PICkit 3 In-Circuit Debugger/ Programmer and PICkit 3 Debug Express

The MPLAB PICkit 3 allows debugging and programming of PIC<sup>®</sup> and dsPIC<sup>®</sup> Flash microcontrollers at a most affordable price point using the powerful graphical user interface of the MPLAB Integrated Development Environment (IDE). The MPLAB PICkit 3 is connected to the design engineer's PC using a full speed USB interface and can be connected to the target via an Microchip debug (RJ-11) connector (compatible with MPLAB ICD 3 and MPLAB REAL ICE). The connector uses two device I/O pins and the reset line to implement in-circuit debugging and In-Circuit Serial Programming<sup>™</sup>.

The PICkit 3 Debug Express include the PICkit 3, demo board and microcontroller, hookup cables and CDROM with user's guide, lessons, tutorial, compiler and MPLAB IDE software.

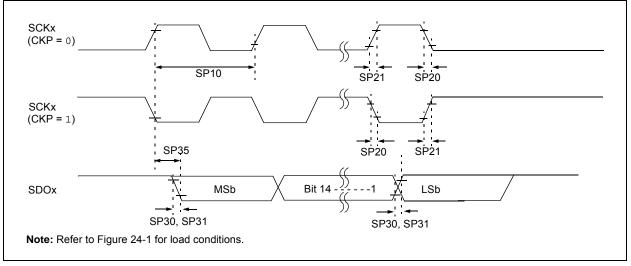

#### TABLE 24-28: SPIx MAXIMUM DATA/CLOCK RATE SUMMARY

| AC CHARAG            | CTERISTICS                     |             | $\begin{tabular}{lllllllllllllllllllllllllllllllllll$ |     |     |     |  |  |

|----------------------|--------------------------------|-------------|-------------------------------------------------------|-----|-----|-----|--|--|

| Maximum<br>Data Rate | Transmit Only Transmit/Receive |             | Slave<br>Transmit/Receive<br>(Full-Duplex)            | CKE | СКР | SMP |  |  |

| 15 MHz               | Table 24-29                    |             | —                                                     | 0,1 | 0,1 | 0,1 |  |  |

| 10 MHz               | —                              | Table 24-30 | —                                                     | 1   | 0,1 | 1   |  |  |

| 10 MHz               | —                              | Table 24-31 | —                                                     | 0   | 0,1 | 1   |  |  |

| 15 MHz               | —                              | —           | Table 24-32                                           | 1   | 0   | 0   |  |  |

| 11 MHz               | —                              | —           | Table 24-33                                           | 1   | 1   | 0   |  |  |

| 15 MHz               | _                              | _           | Table 24-34                                           | 0   | 1   | 0   |  |  |

| 11 MHz               |                                |             | Table 24-35                                           | 0   | 0   | 0   |  |  |

#### FIGURE 24-9: SPIX MASTER MODE (HALF-DUPLEX, TRANSMIT ONLY CKE = 0) TIMING CHARACTERISTICS

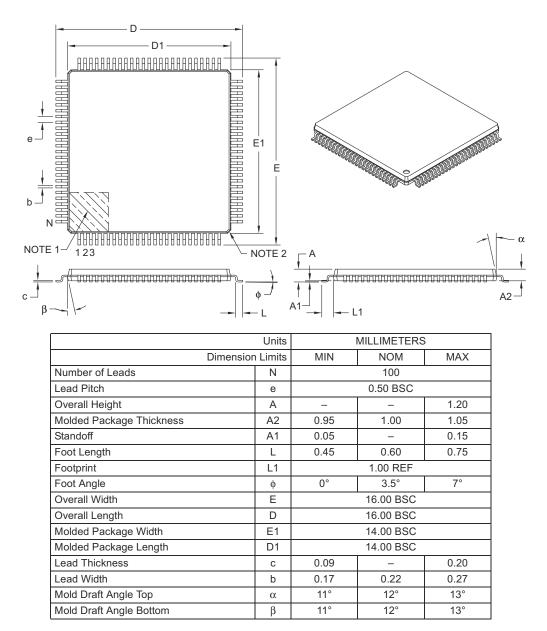

#### 100-Lead Plastic Thin Quad Flatpack (PF) – 14x14x1 mm Body, 2.00 mm Footprint [TQFP]

**Note:** For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

Notes:

1. Pin 1 visual index feature may vary, but must be located within the hatched area.

2. Chamfers at corners are optional; size may vary.

3. Dimensions D1 and E1 do not include mold flash or protrusions. Mold flash or protrusions shall not exceed 0.25 mm per side.

4. Dimensioning and tolerancing per ASME Y14.5M.

BSC: Basic Dimension. Theoretically exact value shown without tolerances.

REF: Reference Dimension, usually without tolerance, for information purposes only.

Microchip Technology Drawing C04-110B

# F

| •                                                  |

|----------------------------------------------------|

| Flash Program Memory59                             |

| Control Registers60                                |

| Operations60                                       |

| Programming Algorithm62                            |

| RTSP Operation60                                   |

| Table Instructions59                               |

| Flexible Configuration                             |

| FSCM                                               |

| Delay for Crystal and PLL Clock Sources            |

| Device Resets                                      |

| н                                                  |

| High Temperature Electrical Characteristics        |

|                                                    |

|                                                    |

| I/O Ports                                          |

| Parallel I/O (PIO)141                              |

| Write/Read Timing                                  |

| l <sup>2</sup> C                                   |

| Operating Modes                                    |

| Registers                                          |

| I <sup>2</sup> C Module                            |

| I2C1 Register Map                                  |

| I2C2 Register Map                                  |

| In-Circuit Debugger                                |

| In-Circuit Emulation                               |

| In-Circuit Serial Programming (ICSP)               |

| Input Capture                                      |

| Registers                                          |

| Input Change Notification Module                   |

| Instruction Addressing Modes                       |

| File Register Instructions                         |

| Fundamental Modes Supported                        |

| MCU Instructions                                   |

| Move and Accumulator Instructions                  |