Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFI

| Betans                     |                                                                                 |

|----------------------------|---------------------------------------------------------------------------------|

| Product Status             | Active                                                                          |

| Core Processor             | PIC                                                                             |

| Core Size                  | 16-Bit                                                                          |

| Speed                      | 40 MIPs                                                                         |

| Connectivity               | I <sup>2</sup> C, IrDA, LINbus, SPI, UART/USART                                 |

| Peripherals                | Brown-out Detect/Reset, DMA, POR, PWM, WDT                                      |

| Number of I/O              | 85                                                                              |

| Program Memory Size        | 256KB (85.5K x 24)                                                              |

| Program Memory Type        | FLASH                                                                           |

| EEPROM Size                |                                                                                 |

| RAM Size                   | 16K x 8                                                                         |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 3.6V                                                                       |

| Data Converters            | A/D 32x10b/12b                                                                  |

| Oscillator Type            | Internal                                                                        |

| Operating Temperature      | -40°C ~ 125°C (TA)                                                              |

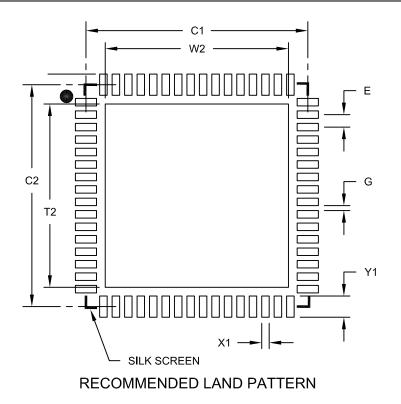

| Mounting Type              | Surface Mount                                                                   |

| Package / Case             | 100-TQFP                                                                        |

| Supplier Device Package    | 100-TQFP (12x12)                                                                |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic24hj256gp210a-e-pt |

|                            |                                                                                 |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

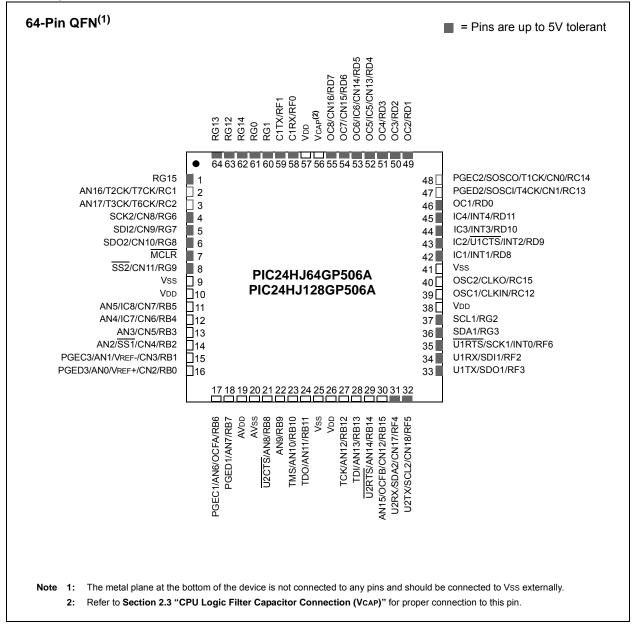

#### **Pin Diagrams (Continued)**

### 2.5 ICSP Pins

The PGECx and PGEDx pins are used for In-Circuit Serial Programming<sup>TM</sup> (ICSP<sup>TM</sup>) and debugging purposes. It is recommended to keep the trace length between the ICSP connector and the ICSP pins on the device as short as possible. If the ICSP connector is expected to experience an ESD event, a series resistor is recommended, with the value in the range of a few tens of Ohms, not to exceed 100 Ohms.

Pull-up resistors, series diodes, and capacitors on the PGECx and PGEDx pins are not recommended as they will interfere with the programmer/debugger communications to the device. If such discrete components are an application requirement, they should be removed from the circuit during programming and debugging. Alternatively, refer to the AC/DC characteristics and requirements timing information in the "dsPIC33F/PIC24H Flash Programming Specification" (DS70152) for information on capacitive loading limits and pin input voltage high (VIH) and input low (VIL) requirements.

Ensure that the "Communication Channel Select" (i.e., PGECx/PGEDx pins) programmed into the device matches the physical connections for the ICSP to MPLAB<sup>®</sup> ICD 3 or MPLAB REAL ICE<sup>™</sup>.

For more information on ICD 3 and REAL ICE connection requirements, refer to the following documents that are available on the Microchip web site.

- "Using MPLAB<sup>®</sup> ICD 3 In-Circuit Debugger" (poster) DS51765

- "MPLAB<sup>®</sup> ICD 3 Design Advisory" DS51764

- "MPLAB<sup>®</sup> REAL ICE<sup>™</sup> In-Circuit Emulator User's Guide" DS51616

- "Using MPLAB<sup>®</sup> REAL ICE™" (poster) DS51749

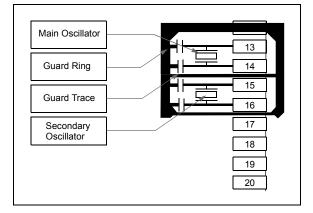

### 2.6 External Oscillator Pins

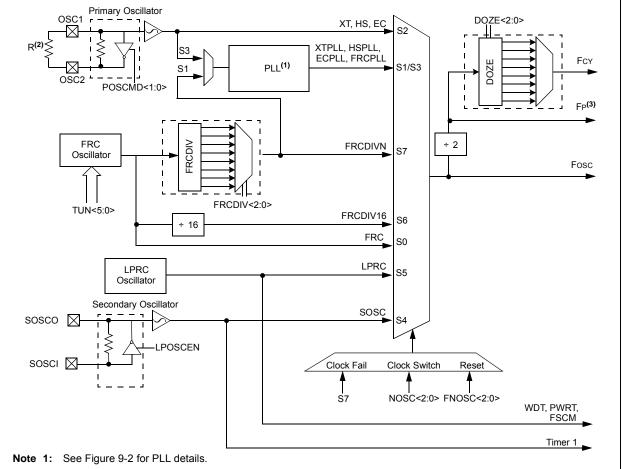

Many MCUs have options for at least two oscillators: a high-frequency primary oscillator and a low-frequency secondary oscillator (refer to **Section 9.0 "Oscillator Configuration"** for details).

The oscillator circuit should be placed on the same side of the board as the device. Also, place the oscillator circuit close to the respective oscillator pins, not exceeding one-half inch (12 mm) distance between them. The load capacitors should be placed next to the oscillator itself, on the same side of the board. Use a grounded copper pour around the oscillator circuit to isolate them from surrounding circuits. The grounded copper pour should be routed directly to the MCU ground. Do not run any signal traces or power traces inside the ground pour. Also, if using a two-sided board, avoid any traces on the other side of the board where the crystal is placed. A suggested layout is shown in Figure 2-3.

#### FIGURE 2-3: SUGGESTED PLACEMENT OF THE OSCILLATOR CIRCUIT

| Reset Type      | Clock Source  | Clock Source SYSRST Delay |              | FSCM<br>Delay | See Notes        |

|-----------------|---------------|---------------------------|--------------|---------------|------------------|

| POR             | EC, FRC, LPRC | TPOR + TSTARTUP + TRST    | —            | _             | 1, 2, 3          |

|                 | ECPLL, FRCPLL | TPOR + TSTARTUP + TRST    | TLOCK        | TFSCM         | 1, 2, 3, 5, 6    |

|                 | XT, HS, SOSC  | TPOR + TSTARTUP + TRST    | Тоѕт         | TFSCM         | 1, 2, 3, 4, 6    |

|                 | XTPLL, HSPLL  | TPOR + TSTARTUP + TRST    | TOST + TLOCK | TFSCM         | 1, 2, 3, 4, 5, 6 |

| MCLR            | Any Clock     | Trst                      | —            | _             | 3                |

| WDT             | Any Clock     | Trst                      | —            | _             | 3                |

| Software        | Any clock     | Trst                      | —            | _             | 3                |

| Illegal Opcode  | Any Clock     | Trst                      | —            | _             | 3                |

| Uninitialized W | Any Clock     | Any Clock TRST            |              | _             | 3                |

| Trap Conflict   | Any Clock     | Trst                      | —            | —             | 3                |

#### TABLE 6-3: RESET DELAY TIMES FOR VARIOUS DEVICE RESETS

**Note 1:** TPOR = Power-on Reset delay (10 μs nominal).

**2:** TSTARTUP = Conditional POR delay of 20 μs nominal (if on-chip regulator is enabled) or 64 ms nominal Power-up Timer delay (if regulator is disabled). TSTARTUP is also applied to all returns from powered-down states, including waking from Sleep mode, only if the regulator is enabled.

- 3: TRST = Internal state Reset time (20 μs nominal).

- **4:** TOST = Oscillator Start-up Timer. A 10-bit counter counts 1024 oscillator periods before releasing the oscillator clock to the system.

- **5:** TLOCK = PLL lock time (20  $\mu$ s nominal).

- **6:** TFSCM = Fail-Safe Clock Monitor delay (100 μs nominal).

#### 6.2.1 POR AND LONG OSCILLATOR START-UP TIMES

The oscillator start-up circuitry and its associated delay timers are not linked to the device Reset delays that occur at power-up. Some crystal circuits (especially low-frequency crystals) have a relatively long start-up time. Therefore, one or more of the following conditions is possible after the Reset signal is released:

- The oscillator circuit has not begun to oscillate

- The Oscillator Start-up Timer has not expired (if a crystal oscillator is used)

- The PLL has not achieved a lock (if PLL is used)

The device will not begin to execute code until a valid clock source has been released to the system. Therefore, the oscillator and PLL start-up delays must be considered when the Reset delay time must be known.

#### 6.2.2 FAIL-SAFE CLOCK MONITOR (FSCM) AND DEVICE RESETS

If the FSCM is enabled, it begins to monitor the system clock source when the Reset signal is released. If a valid clock source is not available at this time, the device automatically switches to the FRC oscillator and the user can switch to the desired crystal oscillator in the Trap Service Routine.

#### 6.2.2.1 FSCM Delay for Crystal and PLL Clock Sources

When the system clock source is provided by a crystal oscillator and/or the PLL, a small delay, TFSCM, is automatically inserted after the POR and PWRT delay times. The FSCM does not begin to monitor the system clock source until this delay expires. The FSCM delay time is nominally 500  $\mu$ s and provides additional time for the oscillator and/or PLL to stabilize. In most cases, the FSCM delay prevents an oscillator failure trap at a device Reset when the PWRT is disabled.

### 6.3 Special Function Register Reset States

Most of the Special Function Registers (SFRs) associated with the CPU and peripherals are reset to a particular value at a device Reset. The SFRs are grouped by their peripheral or CPU function and their Reset values are specified in each section of this manual.

The Reset value for each SFR does not depend on the type of Reset, with the exception of two registers. The Reset value for the Reset Control register, RCON, depends on the type of device Reset. The Reset value for the Oscillator Control register, OSCCON, depends on the type of Reset and the programmed values of the oscillator Configuration bits in the FOSC Configuration register.

#### REGISTER 7-12: IEC2: INTERRUPT ENABLE CONTROL REGISTER 2

| R/W-0         | R/W-0                                                                                        | U-0                                                                                  | R/W-0          | R/W-0            | R/W-0            | R/W-0           | R/W-0   |  |  |  |

|---------------|----------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------|----------------|------------------|------------------|-----------------|---------|--|--|--|

| T6IE          | DMA4IE                                                                                       | —                                                                                    | OC8IE          | OC7IE            | OC6IE            | OC5IE           | IC6IE   |  |  |  |

| bit 15        |                                                                                              |                                                                                      |                |                  | •                |                 | bit 8   |  |  |  |

| R/W-0         | R/W-0                                                                                        | R/W-0                                                                                | R/W-0          | R/W-0            | R/W-0            | R/W-0           | R/W-0   |  |  |  |

| IC5IE         | IC4IE                                                                                        | IC3IE                                                                                | DMA3IE         | C1IE             | C1RXIE           | SPI2IE          | SPI2EIE |  |  |  |

| bit 7         |                                                                                              |                                                                                      |                | 0                |                  |                 | bit (   |  |  |  |

| Legend:       |                                                                                              |                                                                                      |                |                  |                  |                 |         |  |  |  |

| R = Readable  | e bit                                                                                        | W = Writable                                                                         | bit            | U = Unimpler     | mented bit, read | l as '0'        |         |  |  |  |

| -n = Value at | POR                                                                                          | '1' = Bit is set                                                                     |                | '0' = Bit is cle | eared            | x = Bit is unki | nown    |  |  |  |

| bit 15        | T6IE: Timer6                                                                                 | Interrupt Enabl                                                                      | e bit          |                  |                  |                 |         |  |  |  |

|               |                                                                                              | request enable                                                                       |                |                  |                  |                 |         |  |  |  |

|               | 0 = Interrupt r                                                                              | equest not ena                                                                       | bled           |                  |                  |                 |         |  |  |  |

| bit 14        |                                                                                              | A Channel 4 D                                                                        |                | Complete Interi  | rupt Enable bit  |                 |         |  |  |  |

|               |                                                                                              | equest enable<br>equest not ena                                                      |                |                  |                  |                 |         |  |  |  |

| bit 13        | •                                                                                            | ted: Read as '                                                                       |                |                  |                  |                 |         |  |  |  |

| bit 12        | •                                                                                            |                                                                                      |                | unt Enable bit   |                  |                 |         |  |  |  |

| 511 12        | <b>OC8IE:</b> Output Compare Channel 8 Interrupt Enable bit<br>1 = Interrupt request enabled |                                                                                      |                |                  |                  |                 |         |  |  |  |

|               |                                                                                              | equest not ena                                                                       |                |                  |                  |                 |         |  |  |  |

| bit 11        | OC7IE: Output Compare Channel 7 Interrupt Enable bit                                         |                                                                                      |                |                  |                  |                 |         |  |  |  |

|               |                                                                                              | equest enable<br>equest not ena                                                      |                |                  |                  |                 |         |  |  |  |

| bit 10        | OC6IE: Output Compare Channel 6 Interrupt Enable bit                                         |                                                                                      |                |                  |                  |                 |         |  |  |  |

|               |                                                                                              | equest enable<br>equest not ena                                                      |                |                  |                  |                 |         |  |  |  |

| bit 9         | OC5IE: Outpu                                                                                 | OC5IE: Output Compare Channel 5 Interrupt Enable bit                                 |                |                  |                  |                 |         |  |  |  |

|               |                                                                                              | equest enable<br>equest not ena                                                      |                |                  |                  |                 |         |  |  |  |

| bit 8         |                                                                                              | Capture Channe                                                                       |                | Enable bit       |                  |                 |         |  |  |  |

|               |                                                                                              | equest enable<br>equest not ena                                                      |                |                  |                  |                 |         |  |  |  |

| bit 7         |                                                                                              | -                                                                                    |                | Enable bit       |                  |                 |         |  |  |  |

|               | -                                                                                            | IC5IE: Input Capture Channel 5 Interrupt Enable bit<br>1 = Interrupt request enabled |                |                  |                  |                 |         |  |  |  |

|               | •                                                                                            | request not ena                                                                      |                |                  |                  |                 |         |  |  |  |

| bit 6         | -                                                                                            | Capture Channe                                                                       |                | Enable bit       |                  |                 |         |  |  |  |

|               |                                                                                              | equest enable<br>equest not ena                                                      |                |                  |                  |                 |         |  |  |  |

| bit 5         | •                                                                                            | Capture Channe                                                                       |                | -nable bit       |                  |                 |         |  |  |  |

|               | -                                                                                            | equest enable                                                                        | -              |                  |                  |                 |         |  |  |  |

|               | 0 = Interrupt r                                                                              | equest not ena                                                                       | bled           |                  |                  |                 |         |  |  |  |

| bit 4         | DMA3IE: DM                                                                                   | A Channel 3 D                                                                        | ata Transfer C | Complete Interi  | rupt Enable bit  |                 |         |  |  |  |

|               |                                                                                              | equest enable<br>equest not ena                                                      |                |                  |                  |                 |         |  |  |  |

| bit 3         | -                                                                                            | Event Interrup                                                                       |                |                  |                  |                 |         |  |  |  |

| bit J         |                                                                                              | equest enable                                                                        |                |                  |                  |                 |         |  |  |  |

|               |                                                                                              | equest not ena                                                                       |                |                  |                  |                 |         |  |  |  |

#### REGISTER 7-25: IPC10: INTERRUPT PRIORITY CONTROL REGISTER 10

| U-0           | R/W-1                                                                                     | R/W-0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | R/W-0           | U-0               | R/W-1           | R/W-0           | R/W-0 |  |  |  |  |  |

|---------------|-------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------|-------------------|-----------------|-----------------|-------|--|--|--|--|--|

| _             |                                                                                           | OC7IP<2:0>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                 | —                 |                 | OC6IP<2:0>      |       |  |  |  |  |  |

| bit 15        |                                                                                           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                 |                   |                 |                 | bit 8 |  |  |  |  |  |

|               |                                                                                           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                 |                   |                 |                 |       |  |  |  |  |  |

| U-0           | R/W-1                                                                                     | R/W-0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | R/W-0           | U-0               | R/W-1           | R/W-0           | R/W-0 |  |  |  |  |  |

| —             |                                                                                           | OC5IP<2:0>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                 | —                 |                 | IC6IP<2:0>      |       |  |  |  |  |  |

| bit 7         |                                                                                           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                 |                   |                 |                 | bit ( |  |  |  |  |  |

|               |                                                                                           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                 |                   |                 |                 |       |  |  |  |  |  |

| Legend:       |                                                                                           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                 |                   |                 |                 |       |  |  |  |  |  |

| R = Readable  |                                                                                           | W = Writable                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                 | -                 | mented bit, rea |                 |       |  |  |  |  |  |

| -n = Value at | POR                                                                                       | '1' = Bit is set                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                 | '0' = Bit is cle  | eared           | x = Bit is unkn | own   |  |  |  |  |  |

| bit 15        | Unimpleme                                                                                 | ented: Read as '                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | י.              |                   |                 |                 |       |  |  |  |  |  |

| bit 14-12     | -                                                                                         | Soutput Comparison |                 | Interrunt Prior   | ity hits        |                 |       |  |  |  |  |  |

| UIL 14-12     |                                                                                           | • •                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                 | •                 | ity bits        |                 |       |  |  |  |  |  |

|               | <ul> <li>111 = Interrupt is priority 7 (highest priority interrupt)</li> <li>•</li> </ul> |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                 |                   |                 |                 |       |  |  |  |  |  |

|               | •                                                                                         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                 |                   |                 |                 |       |  |  |  |  |  |

|               | •<br>001 - Interr                                                                         | upt is priority 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                 |                   |                 |                 |       |  |  |  |  |  |

|               |                                                                                           | upt is priority i<br>upt source is dis                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | abled           |                   |                 |                 |       |  |  |  |  |  |

| bit 11        |                                                                                           | ented: Read as '                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                 |                   |                 |                 |       |  |  |  |  |  |

| bit 10-8      | -                                                                                         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                 | Interrupt Prior   | ity bits        |                 |       |  |  |  |  |  |

|               |                                                                                           | <b>OC6IP&lt;2:0&gt;:</b> Output Compare Channel 6 Interrupt Priority bits<br>111 = Interrupt is priority 7 (highest priority interrupt)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                 |                   |                 |                 |       |  |  |  |  |  |

|               | •                                                                                         | •                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                 |                   |                 |                 |       |  |  |  |  |  |

|               | •                                                                                         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                 |                   |                 |                 |       |  |  |  |  |  |

|               | •<br>001 = Interr                                                                         | upt is priority 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                 |                   |                 |                 |       |  |  |  |  |  |

|               |                                                                                           | upt source is dis                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | abled           |                   |                 |                 |       |  |  |  |  |  |