Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

### Details

E·XFl

| Betano                     |                                                                                 |

|----------------------------|---------------------------------------------------------------------------------|

| Product Status             | Obsolete                                                                        |

| Core Processor             | PIC                                                                             |

| Core Size                  | 16-Bit                                                                          |

| Speed                      | 20 MIPS                                                                         |

| Connectivity               | CANbus, I <sup>2</sup> C, IrDA, LINbus, SPI, UART/USART                         |

| Peripherals                | Brown-out Detect/Reset, DMA, POR, PWM, WDT                                      |

| Number of I/O              | 85                                                                              |

| Program Memory Size        | 256KB (85.5K x 24)                                                              |

| Program Memory Type        | FLASH                                                                           |

| EEPROM Size                | ·                                                                               |

| RAM Size                   | 16K x 8                                                                         |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 3.6V                                                                       |

| Data Converters            | A/D 32x10b/12b                                                                  |

| Oscillator Type            | Internal                                                                        |

| Operating Temperature      | -40°C ~ 150°C (TA)                                                              |

| Mounting Type              | Surface Mount                                                                   |

| Package / Case             | 100-TQFP                                                                        |

| Supplier Device Package    | 100-TQFP (14x14)                                                                |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic24hj256gp610a-h-pf |

|                            |                                                                                 |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

| SFR Name | SFR<br>Addr | Bit 15 | Bit 14 | Bit 13 | Bit 12 | Bit 11 | Bit 10 | Bit 9   | Bit 8         | Bit 7        | Bit 6     | Bit 5     | Bit 4        | Bit 3        | Bit 2        | Bit 1   | Bit 0  | All<br>Resets |

|----------|-------------|--------|--------|--------|--------|--------|--------|---------|---------------|--------------|-----------|-----------|--------------|--------------|--------------|---------|--------|---------------|

| WREG0    | 0000        |        |        | •      |        |        | •      |         | Working Re    | gister 0     | •         |           |              |              | •            |         | •      | xxxx          |

| WREG1    | 0002        |        |        |        |        |        |        |         | Working Re    | gister 1     |           |           |              |              |              |         |        | xxxx          |

| WREG2    | 0004        |        |        |        |        |        |        |         | Working Re    | gister 2     |           |           |              |              |              |         |        | xxxx          |

| WREG3    | 0006        |        |        |        |        |        |        |         | Working Re    | gister 3     |           |           |              |              |              |         |        | xxxx          |

| WREG4    | 8000        |        |        |        |        |        |        |         | Working Re    | gister 4     |           |           |              |              |              |         |        | xxxx          |

| WREG5    | 000A        |        |        |        |        |        |        |         | Working Re    | gister 5     |           |           |              |              |              |         |        | XXXX          |

| WREG6    | 000C        |        |        |        |        |        |        |         | Working Re    | gister 6     |           |           |              |              |              |         |        | xxxx          |

| WREG7    | 000E        |        |        |        |        |        |        |         | Working Re    | gister 7     |           |           |              |              |              |         |        | XXXX          |

| WREG8    | 0010        |        |        |        |        |        |        |         | Working Re    | gister 8     |           |           |              |              |              |         |        | xxxx          |

| WREG9    | 0012        |        |        |        |        |        |        |         | Working Re    | gister 9     |           |           |              |              |              |         |        | xxxx          |

| WREG10   | 0014        |        |        |        |        |        |        |         | Working Reg   | gister 10    |           |           |              |              |              |         |        | xxxx          |

| WREG11   | 0016        |        |        |        |        |        |        |         | Working Reg   | gister 11    |           |           |              |              |              |         |        | xxxx          |

| WREG12   | 0018        |        |        |        |        |        |        |         | Working Ree   | gister 12    |           |           |              |              |              |         |        | xxxx          |

| WREG13   | 001A        |        |        |        |        |        |        |         | Working Ree   | gister 13    |           |           |              |              |              |         |        | xxxx          |

| WREG14   | 001C        |        |        |        |        |        |        |         | Working Ree   | gister 14    |           |           |              |              |              |         |        | xxxx          |

| WREG15   | 001E        |        |        |        |        |        |        |         | Working Ree   | gister 15    |           |           |              |              |              |         |        | 0800          |

| SPLIM    | 0020        |        |        |        |        |        |        | Sta     | ck Pointer Li | mit Register | •         |           |              |              |              |         |        | xxxx          |

| PCL      | 002E        |        |        |        |        |        |        | Program | n Counter Lo  | w Word Reg   | gister    |           |              |              |              |         |        | 0000          |

| PCH      | 0030        | —      | _      | —      | —      | —      | —      | —       | —             |              |           | Progra    | m Counter    | High Byte F  | Register     |         |        | 0000          |

| TBLPAG   | 0032        | —      | _      | —      | —      | —      | —      | —       | —             |              |           |           | · ·          | ss Pointer F | <b>.</b>     |         |        | 0000          |

| PSVPAG   | 0034        |        | —      | —      | —      | —      | —      |         | —             |              | •         | am Memory | Visibility P | age Addres   | s Pointer Re | egister |        | 0000          |

| RCOUNT   | 0036        |        |        |        |        |        |        | Repe    | eat Loop Cou  | inter Regist |           |           | 1            | 1            | I.           |         |        | xxxx          |

| SR       | 0042        | —      | _      |        | _      | _      | —      | —       | DC            |              | IPL<2:0>  |           | RA           | N            | OV           | Z       | С      | 0000          |

| CORCON   | 0044        | —      | _      | —      | —      | —      | —      | —       | —             | —            | —         | —         | —            | IPL3         | PSV          | —       | —      | 0000          |

| DISICNT  | 0052        | _      | _      |        |        |        |        |         | Disable       | e Interrupts | Counter R | egister   |              |              |              |         | 1      | xxxx          |

| BSRAM    | 0750        |        | —      | —      | —      | —      | —      | —       | —             | —            | —         | _         | —            |              | IW_BSR       | IR_BSR  | RL_BSR | 0000          |

| SSRAM    | 0752        |        | —      | —      | —      | —      | —      | —       | -             | —            | -         | —         | —            | —            | IW_SSR       | IR_SSR  | RL_SSR | 0000          |

PIC24HJXXXGPX06A/X08A/X10A

### TABLE 4-1: CPU CORE REGISTERS MAP

Legend: x = unknown value on Reset, — = unimplemented, read as '0'. Reset values are shown in hexadecimal for PinHigh devices.

| File Name  | Addr                    | Bit 15 | Bit 14 | Bit 13 | Bit 12 | Bit 11                        | Bit 10 | Bit 9  | Bit 8       | Bit 7              | Bit 6    | Bit 5  | Bit 4 | Bit 3              | Bit 2 | Bit 1               | Bit 0  | All<br>Resets |

|------------|-------------------------|--------|--------|--------|--------|-------------------------------|--------|--------|-------------|--------------------|----------|--------|-------|--------------------|-------|---------------------|--------|---------------|

|            | 0500-<br>051E           |        |        |        |        |                               |        | :      | See definit | on when W          | /IN = x  |        |       |                    |       |                     |        |               |

| C2BUFPNT1  | 0520                    |        | F3BF   | ><3:0> |        |                               | F2BF   | D<3:0> |             |                    | F1BF     | <3:0>  |       |                    | F0BF  | <b>^&lt;3:0&gt;</b> |        | 0000          |

| C2BUFPNT2  | 0522                    |        | F7BF   | P<3:0> |        |                               | F6BF   | P<3:0> |             |                    | F5BF     | <3:0>  |       |                    | F4BF  | <b>^&lt;3:0&gt;</b> |        | 0000          |

| C2BUFPNT3  | 0524                    |        | F12B   | P<3:0> |        |                               | F10B   | P<3:0> |             |                    | F9BF     | <3:0>  |       |                    | F8BF  | °<3:0>              |        | 0000          |

| C2BUFPNT4  | 0526                    |        | F15B   | P<3:0> |        |                               | F14B   | P<3:0> |             |                    | F13BI    | P<3:0> |       |                    | F12B  | P<3:0>              |        | 0000          |

| C2RXM0SID  | 0530                    |        |        |        | SID<   | 10:3>                         |        |        |             |                    | SID<2:0> |        | _     | MIDE               | _     | EID<                | 17:16> | xxxx          |

| C2RXM0EID  | 0532                    |        |        |        | EID<   | 15:8>                         |        |        |             |                    |          |        | EID<7 | /:0>               |       |                     |        | xxxx          |

| C2RXM1SID  | 0534                    |        |        |        | SID<   | 10:3>                         |        |        |             |                    | SID<2:0> |        | _     | MIDE               | _     | EID<                | 17:16> | xxxx          |

| C2RXM1EID  | 0536                    |        |        |        | EID<   | 15:8>                         |        |        |             |                    |          |        | EID<7 | /:0>               |       |                     |        | xxxx          |

| C2RXM2SID  | 0538                    |        |        |        | SID<   | 10:3>                         |        |        |             |                    | SID<2:0> |        | _     | MIDE               | _     | EID<                | 17:16> | xxxx          |

| C2RXM2EID  | 053A                    |        |        |        | EID<   | 15:8>                         |        |        |             |                    |          |        | EID<7 | /:0>               |       |                     |        | xxxx          |

| C2RXF0SID  | 0540                    |        |        |        | SID<   | 10:3>                         |        |        |             |                    | SID<2:0> |        | _     | EXIDE              | _     | EID<                | 17:16> | xxxx          |

| C2RXF0EID  | 0542                    |        |        |        | EID<   | 15:8>                         |        |        |             |                    |          |        | EID<7 | /:0>               | _     | _                   |        | xxxx          |

| C2RXF1SID  | 0544                    |        |        |        | SID<   | 10:3>                         |        |        |             |                    | SID<2:0> |        | —     | EXIDE              | _     | EID<                | 17:16> | xxxx          |

| C2RXF1EID  | 0546                    |        |        |        | EID<   | 15:8>                         |        |        |             |                    |          |        | EID<7 | /:0>               | •     | •                   |        | xxxx          |

| C2RXF2SID  | 0548                    |        |        |        | SID<   | 10:3>                         |        |        |             |                    | SID<2:0> |        | _     | EXIDE              | _     | EID<                | 17:16> | xxxx          |

| C2RXF2EID  | 054A                    |        |        |        | EID<   | 15:8>                         |        |        |             |                    |          |        | EID<7 | /:0>               | •     | •                   |        | xxxx          |

| C2RXF3SID  | 054C                    |        |        |        | SID<   | 10:3>                         |        |        |             |                    | SID<2:0> |        | _     | EXIDE              | _     | EID<                | 17:16> | xxxx          |

| C2RXF3EID  | 054E                    |        |        |        | EID<   | 15:8>                         |        |        |             | EID<               |          |        |       | 7:0>               |       |                     |        | xxxx          |

| C2RXF4SID  | 0550                    |        |        |        | SID<   | 10:3>                         |        |        |             | SID<2:0> —         |          |        |       | EXIDE — EID<17:16> |       |                     |        | xxxx          |

| C2RXF4EID  | 0552                    |        |        |        | EID<   | 15:8>                         |        |        |             |                    |          |        | /:0>  |                    |       |                     | xxxx   |               |

| C2RXF5SID  | 0554                    |        |        |        | SID<   | 10:3>                         |        |        |             | SID<2:0> — EXIDE — |          |        |       |                    | _     | EID<                | 17:16> | xxxx          |

| C2RXF5EID  | 0556                    |        |        |        | EID<   | 15:8>                         |        |        |             |                    |          |        | EID<7 | /:0>               |       |                     |        | xxxx          |

| C2RXF6SID  | 0558                    |        |        |        | SID<   | 10:3>                         |        |        |             |                    | SID<2:0> |        | _     | EXIDE              | _     | EID<                | 17:16> | xxxx          |

| C2RXF6EID  | 055A                    |        |        |        | EID<   | 15:8>                         |        |        |             |                    |          |        | EID<7 | /:0>               |       |                     |        | xxxx          |

| C2RXF7SID  | 055C                    |        |        |        | SID<   | 10:3>                         |        |        |             |                    | SID<2:0> |        | _     | EXIDE              | _     | EID<                | 17:16> | xxxx          |

| C2RXF7EID  | 055E                    |        |        |        | EID<   | 15:8>                         |        |        |             |                    |          |        | EID<7 | /:0>               |       |                     |        | xxxx          |

| C2RXF8SID  | 0560                    |        |        |        | SID<   | 10:3>                         |        |        |             |                    | SID<2:0> |        | _     | EXIDE              | _     | EID<                | 17:16> | xxxx          |

| C2RXF8EID  | 0562                    |        |        |        | EID<   | 15:8>                         |        |        |             |                    |          |        | EID<7 | /:0>               |       |                     |        | xxxx          |

| C2RXF9SID  | 0564                    |        |        |        | SID<   | 10:3>                         |        |        |             |                    | SID<2:0> |        |       | EXIDE              |       | EID<                | 17:16> | xxxx          |

| C2RXF9EID  | (F9EID 0566 EID<15:8>   |        |        |        |        |                               |        |        | EID<7       | /:0>               |          |        |       | xxxx               |       |                     |        |               |

| C2RXF10SID | 2XF10SID 0568 SID<10:3> |        |        |        |        | SID<2:0> — EXIDE — EID<17:16> |        |        |             |                    | 17:16>   | xxxx   |       |                    |       |                     |        |               |

| C2RXF10EID | 056A                    |        |        |        | EID<   | 15:8>                         |        |        |             |                    |          |        | EID<7 | /:0>               |       | -                   |        | xxxx          |

| C2RXF11SID | 056C                    | 1      |        |        | SID<   | 10:3>                         |        |        |             |                    | SID<2:0> |        | _     | EXIDE              | _     | EID<                | 17:16> | xxxx          |

### TABLE 4-23: ECAN2 REGISTER MAP WHEN C2CTRL1.WIN = 1 FOR PIC24HJ256GP610A DEVICES ONLY

Legend: x = unknown value on Reset, — = unimplemented, read as '0'. Reset values are shown in hexadecimal for PinHigh devices.

### TABLE 4-31: SYSTEM CONTROL REGISTER MAP

| File Name | Addr | Bit 15 | Bit 14 | Bit 13    | Bit 12 | Bit 11 | Bit 10 | Bit 9     | Bit 8 | Bit 7   | Bit 6  | Bit 5  | Bit 4      | Bit 3 | Bit 2     | Bit 1   | Bit 0 | All<br>Resets       |

|-----------|------|--------|--------|-----------|--------|--------|--------|-----------|-------|---------|--------|--------|------------|-------|-----------|---------|-------|---------------------|

| RCON      | 0740 | TRAPR  | IOPUWR | —         | —      | —      | _      | _         | VREGS | EXTR    | SWR    | SWDTEN | WDTO       | SLEEP | IDLE      | BOR     | POR   | xxxxx(1)            |

| OSCCON    | 0742 | _      | (      | COSC<2:0> | >      | _      | ١      | NOSC<2:0  | >     | CLKLOCK | _      | LOCK   |            | CF    | _         | LPOSCEN | OSWEN | <sub>0300</sub> (2) |

| CLKDIV    | 0744 | ROI    | [      | DOZE<2:0> | >      | DOZEN  | FI     | RCDIV<2:0 | )>    | PLLPOS  | T<1:0> | —      |            | F     | PLLPRE<4: | :0>     |       | 3040                |

| PLLFBD    | 0746 |        | —      |           | —      | —      | _      |           |       |         |        | F      | PLLDIV<8:0 | >     |           |         |       | 0030                |

| OSCTUN    | 0748 |        | —      |           | _      | —      | _      | _         | _     | _       | —      |        |            | TUN   | l<5:0>    |         |       | 0000                |

Legend: x = unknown value on Reset, - = unimplemented, read as '0'. Reset values are shown in hexadecimal for PinHigh devices.

Note 1: RCON register Reset values dependent on type of Reset.

2: OSCCON register Reset values dependent on the FOSC Configuration bits and by type of Reset.

### TABLE 4-32: NVM REGISTER MAP

| File Name | Addr | Bit 15 | Bit 14 | Bit 13 | Bit 12 | Bit 11 | Bit 10 | Bit 9 | Bit 8 | Bit 7 | Bit 6 | Bit 5 | Bit 4 | Bit 3  | Bit 2 | Bit 1  | Bit 0 | All<br>Resets       |

|-----------|------|--------|--------|--------|--------|--------|--------|-------|-------|-------|-------|-------|-------|--------|-------|--------|-------|---------------------|

| NVMCON    | 0760 | WR     | WREN   | WRERR  | _      | _      | _      | —     | _     | _     | ERASE |       |       |        | NVMO  | P<3:0> |       | <sub>0000</sub> (1) |

| NVMKEY    | 0766 | —      |        | —      |        |        |        | —     |       |       |       |       | NVMKE | Y<7:0> |       |        |       | 0000                |

Legend: x = unknown value on Reset, - = unimplemented, read as '0'. Reset values are shown in hexadecimal for PinHigh devices.

Note 1: Reset value shown is for POR only. Value on other Reset states is dependent on the state of memory write or erase operations at the time of Reset.

### TABLE 4-33: PMD REGISTER MAP

| File Name | Addr | Bit 15 | Bit 14 | Bit 13 | Bit 12 | Bit 11 | Bit 10 | Bit 9 | Bit 8 | Bit 7  | Bit 6 | Bit 5 | Bit 4  | Bit 3  | Bit 2 | Bit 1  | Bit 0 | All<br>Resets |

|-----------|------|--------|--------|--------|--------|--------|--------|-------|-------|--------|-------|-------|--------|--------|-------|--------|-------|---------------|

| PMD1      | 0770 | T5MD   | T4MD   | T3MD   | T2MD   | T1MD   | —      | _     | —     | I2C1MD | U2MD  | U1MD  | SPI2MD | SPI1MD | C2MD  | C1MD   | AD1MD | 0000          |

| PMD2      | 0772 | IC8MD  | IC7MD  | IC6MD  | IC5MD  | IC4MD  | IC3MD  | IC2MD | IC1MD | OC8MD  | OC7MD | OC6MD | OC5MD  | OC4MD  | OC3MD | OC2MD  | OC1MD | 0000          |

| PMD3      | 0774 | T9MD   | T8MD   | T7MD   | T6MD   | -      | _      | _     | —     | —      | -     | —     |        | _      | _     | I2C2MD | AD2MD | 0000          |

Legend: x = unknown value on Reset, - = unimplemented, read as '0'. Reset values are shown in hexadecimal for PinHigh devices.

### REGISTER 7-6: IFS1: INTERRUPT FLAG STATUS REGISTER 1 (CONTINUED)

| bit 3 | CNIF: Input Change Notification Interrupt Flag Status bit |

|-------|-----------------------------------------------------------|

|       | 1 = Interrupt request has occurred                        |

|       | 0 = Interrupt request has not occurred                    |

- bit 2 Unimplemented: Read as '0'

- bit 1 MI2C1IF: I2C1 Master Events Interrupt Flag Status bit

- 1 = Interrupt request has occurred

- 0 = Interrupt request has not occurred

- bit 0 SI2C1IF: I2C1 Slave Events Interrupt Flag Status bit

- 1 = Interrupt request has occurred

- 0 = Interrupt request has not occurred

### REGISTER 7-17: IPC2: INTERRUPT PRIORITY CONTROL REGISTER 2

| U-0              | R/W-1            | R/W-0                                      | R/W-0          | U-0              | R/W-1           | R/W-0           | R/W-0 |

|------------------|------------------|--------------------------------------------|----------------|------------------|-----------------|-----------------|-------|

| —                |                  | U1RXIP<2:0>                                |                | —                |                 | SPI1IP<2:0>     |       |

| bit 15           |                  |                                            |                |                  |                 |                 | bit   |

| 11.0             |                  | R/W-0                                      |                | 11.0             |                 | R/W-0           |       |

| U-0              | R/W-1            | SPI1EIP<2:0>                               | R/W-0          | U-0              | R/W-1           | T3IP<2:0>       | R/W-0 |

| bit 7            |                  | 0111211 \2.02                              |                |                  |                 | 1011 \2.02      | bit   |

| 510 1            |                  |                                            |                |                  |                 |                 | bit   |

| Legend:          |                  |                                            |                |                  |                 |                 |       |

| R = Readabl      | e bit            | W = Writable                               | bit            | U = Unimple      | mented bit, rea | d as '0'        |       |

| -n = Value at    | POR              | '1' = Bit is set                           |                | '0' = Bit is cle | eared           | x = Bit is unkr | nown  |

| bit 15           | Unimpleme        | ented: Read as '                           | 0'             |                  |                 |                 |       |

| bit 14-12        | -                | :0>: UART1 Rece                            |                | Prioritv bits    |                 |                 |       |

|                  |                  | rupt is priority 7 (                       | -              | -                |                 |                 |       |

|                  | •                |                                            |                |                  |                 |                 |       |

|                  | •                |                                            |                |                  |                 |                 |       |

|                  | 001 = Inter      | rupt is priority 1                         |                |                  |                 |                 |       |

|                  |                  | rupt source is dis                         | abled          |                  |                 |                 |       |

| bit 11           | Unimpleme        | ented: Read as '                           | 0'             |                  |                 |                 |       |

| bit 10-8         |                  | >: SPI1 Event In                           | =              | -                |                 |                 |       |

|                  | 111 = Inter      | rupt is priority 7 (                       | highest priori | ty interrupt)    |                 |                 |       |

|                  | •                |                                            |                |                  |                 |                 |       |

|                  | •                |                                            |                |                  |                 |                 |       |

|                  |                  | rupt is priority 1<br>rupt source is dis   | abled          |                  |                 |                 |       |

| bit 7            |                  | ented: Read as '                           |                |                  |                 |                 |       |

| bit 6-4          | -                | :0>: SPI1 Error II                         |                | ty bits          |                 |                 |       |

|                  |                  | rupt is priority 7 (                       | -              | -                |                 |                 |       |

|                  | •                |                                            |                |                  |                 |                 |       |

|                  | •                |                                            |                |                  |                 |                 |       |

|                  |                  | rupt is priority 1                         |                |                  |                 |                 |       |

| <b>h</b> :+ 0    |                  | rupt source is dis                         |                |                  |                 |                 |       |

| bit 3<br>bit 2-0 | -                | ented: Read as '                           |                |                  |                 |                 |       |

| DIL 2-0          |                  | : Timer3 Interrupt<br>rupt is priority 7 ( | -              | v interrunt)     |                 |                 |       |

|                  | •                |                                            | riighest phon  | ly interrupt)    |                 |                 |       |

|                  | •                |                                            |                |                  |                 |                 |       |

|                  | •<br>001 = Inter | muchic criteriter d                        |                |                  |                 |                 |       |

|                  |                  |                                            |                |                  |                 |                 |       |

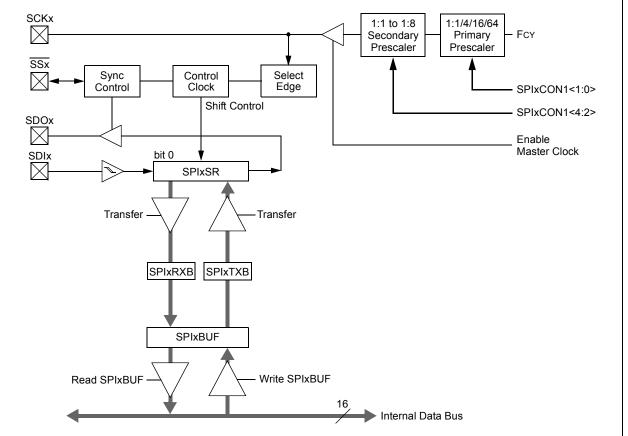

# 16.0 SERIAL PERIPHERAL INTERFACE (SPI)

- Note 1: This data sheet summarizes the features of the PIC24HJXXXGPX06A/X08A/X10A family of devices. However, it is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to the "dsPIC33F/PIC24H Family Reference Manual", Section 18. "Serial Peripheral Interface (SPI)" (DS70206), which is available from the Microchip web site (www.microchip.com).

- 2: Some registers and associated bits described in this section may not be available on all devices. Refer to **Section 4.0 "Memory Organization"** in this data sheet for device-specific register and bit information.

The Serial Peripheral Interface (SPI) module is a synchronous serial interface useful for communicating with other peripheral or microcontroller devices. These peripheral devices may be serial EEPROMs, shift registers, display drivers, Analog-to-Digital converters, etc. The SPI module is compatible with SPI and SIOP from Motorola<sup>®</sup>.

Note: In this section, the SPI modules are referred to together as SPIx, or separately as SPI1 and SPI2. Special Function Registers will follow a similar notation. For example, SPIxCON refers to the control register for the SPI1 or SPI2 module.

Each SPI module consists of a 16-bit shift register, SPIxSR (where x = 1 or 2), used for shifting data in and out, and a buffer register, SPIxBUF. A control register, SPIxCON, configures the module. Additionally, a status register, SPIxSTAT, indicates various status conditions.

The serial interface consists of 4 pins: SDIx (serial data input), SDOx (serial data output), SCKx (shift clock input or output), and SSx (active-low slave select).

In Master mode operation, SCK is a clock output but in Slave mode, it is a clock input.

# FIGURE 16-1: SPI MODULE BLOCK DIAGRAM

# PIC24HJXXXGPX06A/X08A/X10A

| R-0 HSC         | R-0 HSC                                               | U-0                                                                                                    | U-0                              | U-0                      | R/C-0 HS                                         | R-0 HSC          | R-0 HSC    |

|-----------------|-------------------------------------------------------|--------------------------------------------------------------------------------------------------------|----------------------------------|--------------------------|--------------------------------------------------|------------------|------------|

| ACKSTAT         | TRSTAT                                                |                                                                                                        | —                                |                          | BCL                                              | GCSTAT           | ADD10      |

| bit 15          |                                                       |                                                                                                        |                                  |                          |                                                  | 1                | bit 8      |

|                 |                                                       |                                                                                                        |                                  |                          |                                                  |                  |            |

| R/C-0 HS        | R/C-0 HS                                              | R-0 HSC                                                                                                | R/C-0 HSC                        | R/C-0 HSC                | R-0 HSC                                          | R-0 HSC          | R-0 HSC    |

| IWCOL           | I2COV                                                 | D_A                                                                                                    | Р                                | S                        | R_W                                              | RBF              | TBF        |

| bit 7           |                                                       |                                                                                                        |                                  |                          |                                                  |                  | bit C      |

| Legend:         |                                                       | U = Unimpler                                                                                           | nented bit rea                   | ad as '0'                |                                                  | C = Clear on     | lv hit     |

| R = Readable    | hit                                                   | W = Writable                                                                                           |                                  | HS = Set in h            | ardware                                          | HSC = Hardwa     | -          |

| -n = Value at F |                                                       | '1' = Bit is set                                                                                       |                                  | '0' = Bit is cle         |                                                  | x = Bit is unkn  |            |

|                 | OK                                                    | 1 - Dit 13 3et                                                                                         |                                  |                          |                                                  |                  | IOWIT      |

| bit 15          | (when operati<br>1 = NACK rec<br>0 = ACK rece         | cknowledge Sta<br>ing as I <sup>2</sup> C mas<br>ceived from sla<br>ived from slave<br>or clear at end | ter, applicable<br>ve<br>e       |                          | nsmit operation                                  | )                |            |

| bit 14          | 1 = Master tra<br>0 = Master tra                      | ansmit is in pro<br>ansmit is not in                                                                   | gress (8 bits -<br>progress      | + ACK)                   |                                                  | to master trans  |            |

| bit 13-11       | Unimplemen                                            | ted: Read as '                                                                                         | 0'                               |                          |                                                  |                  |            |

| bit 10          | BCL: Master                                           | Bus Collision [                                                                                        | Detect bit                       |                          |                                                  |                  |            |

|                 | 0 = No collisio                                       | lision has beer<br>on<br>at detection of                                                               |                                  | -                        | peration                                         |                  |            |

| bit 9           | GCSTAT: Ger                                           | neral Call Statu                                                                                       | ıs bit                           |                          |                                                  |                  |            |

|                 | 0 = General c                                         | all address wa<br>all address wa<br>when address                                                       | s not received                   |                          | ess. Hardware o                                  | lear at Stop det | ection.    |

| bit 8           | ADD10: 10-B                                           | it Address Stat                                                                                        | us bit                           |                          |                                                  |                  |            |

|                 | 0 = 10-bit add                                        | lress was mate<br>lress was not r<br>at match of 2r                                                    | natched                          | ched 10-bit ad           | dress. Hardwa                                    | re clear at Stop | detection. |

| bit 7           | IWCOL: Write                                          | e Collision Dete                                                                                       | ect bit                          |                          |                                                  |                  |            |

|                 | 0 = No collisio                                       | on                                                                                                     | -                                |                          | ause the I <sup>2</sup> C mo<br>ousy (cleared by | -                |            |

| bit 6           | I2COV: Recei                                          | ive Overflow F                                                                                         | lag bit                          |                          |                                                  |                  |            |

|                 | 0 = No overflo                                        | ow                                                                                                     |                                  | -                        | still holding the                                | -                |            |

| bit 5           |                                                       | dress bit (whe                                                                                         |                                  |                          |                                                  | Solutio).        |            |

| ~               | 1 = Indicates<br>0 = Indicates                        | that the last by<br>that the last by                                                                   | rte received w<br>rte received w | as data<br>as device add | ress<br>by reception of                          | slave byte.      |            |

| bit 4           | <b>P:</b> Stop bit<br>1 = Indicates<br>0 = Stop bit w | that a Stop bit<br>/as not detecte<br>or clear when                                                    | has been dete<br>d last          | ected last               |                                                  | -                |            |

# REGISTER 17-2: I2CxSTAT: I2Cx STATUS REGISTER (CONTINUED)

| bit 3 | <ul> <li>Start bit</li> <li>1 = Indicates that a Start (or Repeated Start) bit has been detected last</li> <li>0 = Start bit was not detected last</li> </ul>                                                               |

|-------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| bit 2 | Hardware set or clear when Start, Repeated Start or Stop detected.<br><b>R_W:</b> Read/Write Information bit (when operating as I <sup>2</sup> C slave)<br>1 = Read – indicates data transfer is output from slave          |

|       | 0 = Write - indicates data transfer is input to slaveHardware set or clear after reception of I2C device address byte.                                                                                                      |

| bit 1 | RBF: Receive Buffer Full Status bit                                                                                                                                                                                         |

|       | <ul> <li>1 = Receive complete, I2CxRCV is full</li> <li>0 = Receive not complete, I2CxRCV is empty</li> <li>Hardware set when I2CxRCV is written with received byte. Hardware clear when software reads I2CxRCV.</li> </ul> |

| bit 0 | TBF: Transmit Buffer Full Status bit                                                                                                                                                                                        |

|       | <ul> <li>1 = Transmit in progress, I2CxTRN is full</li> <li>0 = Transmit complete, I2CxTRN is empty</li> <li>Hardware set when software writes I2CxTRN. Hardware clear at completion of data transmission.</li> </ul>       |

### 18.1 UART Helpful Tips

- 1. In multi-node direct-connect UART networks, receive inputs UART react to the complementary logic level defined by the URXINV bit (UxMODE<4>), which defines the idle state, the default of which is logic high, (i.e., URXINV = 0). Because remote devices do not initialize at the same time, it is likely that one of the devices, because the RX line is floating, will trigger a start bit detection and will cause the first byte received after the device has been initialized to be invalid. To avoid this situation, the user should use a pull-up or pull-down resistor on the RX pin depending on the value of the URXINV bit.

- a) If URXINV = 0, use a pull-up resistor on the RX pin.

- b) If URXINV = 1, use a pull-down resistor on the RX pin.

- 2. The first character received on a wake-up from Sleep mode caused by activity on the UxRX pin of the UART module will be invalid. In Sleep mode, peripheral clocks are disabled. By the time the oscillator system has restarted and stabilized from Sleep mode, the baud rate bit sampling clock relative to the incoming UxRX bit timing is no longer synchronized, resulting in the first character being invalid. This is to be expected.

### 18.2 UART Resources

Many useful resources related to UART are provided on the main product page of the Microchip web site for the devices listed in this data sheet. This product page, which can be accessed using this link, contains the latest updates and additional information.

| Note: | In the event you are not able to access the product page using the link above, enter this URL in your browser: |

|-------|----------------------------------------------------------------------------------------------------------------|

|       | http://www.microchip.com/wwwproducts/<br>Devices.aspx?dDocName=en546061                                        |

### 18.2.1 KEY RESOURCES

- Section 17. "UART" (DS70188)

- Code Samples

- Application Notes

- Software Libraries

- Webinars

- All related dsPIC33F/PIC24H Family Reference Manuals Sections

- Development Tools

| U-0                     | U-0                                                                                           | U-0                                                                                                                               | U-0                                      | U-0              | U-0              | U-0             | U-0   |

|-------------------------|-----------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------|------------------------------------------|------------------|------------------|-----------------|-------|

| —                       | —                                                                                             | —                                                                                                                                 | -                                        | —                | _                |                 |       |

| bit 15                  |                                                                                               |                                                                                                                                   |                                          |                  |                  |                 | bit   |

| R/W-0                   | R/W-0                                                                                         | R/W-0                                                                                                                             | U-0                                      | R/W-0            | R/W-0            | R/W-0           | R/W-0 |

| IVRIE                   | WAKIE                                                                                         | ERRIE                                                                                                                             | _                                        | FIFOIE           | RBOVIE           | RBIE            | TBIE  |

| bit 7                   |                                                                                               |                                                                                                                                   |                                          |                  |                  |                 | bit   |

| Legend:                 |                                                                                               |                                                                                                                                   |                                          |                  |                  |                 |       |

| R = Readab              | le bit                                                                                        | W = Writable I                                                                                                                    | bit                                      | U = Unimpler     | nented bit, read | as '0'          |       |

| -n = Value a            | t POR                                                                                         | '1' = Bit is set                                                                                                                  |                                          | '0' = Bit is cle | ared             | x = Bit is unkr | iown  |

| bit 7<br>bit 6<br>bit 5 | 1 = Interrupt n<br>0 = Interrupt n<br><b>WAKIE:</b> Bus<br>1 = Interrupt n<br>0 = Interrupt n | I Message Inter<br>request enabled<br>request not ena<br>Wake-up Activit<br>request enabled<br>request not ena<br>Interrupt Enabl | d<br>bled<br>ty Interrupt E<br>d<br>bled |                  |                  |                 |       |

|                         | 0 = Interrupt i                                                                               | request enabled<br>request not ena                                                                                                | bled                                     |                  |                  |                 |       |

| bit 4<br>bit 3          | FIFOIE: FIFC                                                                                  | ted: Read as 'd<br>Almost Full Inf<br>request enabled                                                                             | errupt Enabl                             | e bit            |                  |                 |       |

|                         | 0 = Interrupt i                                                                               | request not ena                                                                                                                   | bled                                     |                  |                  |                 |       |

| bit 2                   | 1 = Interrupt i                                                                               | Buffer Overflov<br>request enabled<br>request not ena                                                                             | , t                                      | nable bit        |                  |                 |       |

| bit 1                   | 1 = Interrupt i                                                                               | ffer Interrupt Er<br>request enableo<br>request not ena                                                                           | t                                        |                  |                  |                 |       |

| bit 0                   | 1 = Interrupt i                                                                               | fer Interrupt En<br>request enableo<br>request not ena                                                                            | ł                                        |                  |                  |                 |       |

### **REGISTER 19-7:** CIINTE: ECAN™ MODULE INTERRUPT ENABLE REGISTER

### REGISTER 19-12: CiBUFPNT1: ECAN™ MODULE FILTER 0-3 BUFFER POINTER REGISTER

| R/W-0         | R/W-0                                                                                                                                                             | R/W-0                                                   | R/W-0        | R/W-0             | R/W-0          | R/W-0           | R/W-0 |

|---------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------|--------------|-------------------|----------------|-----------------|-------|

| F3BP<3:0>     |                                                                                                                                                                   |                                                         |              | F2B               | ><3:0>         |                 |       |

| bit 15        |                                                                                                                                                                   |                                                         |              | ·                 |                |                 | bit 8 |

|               |                                                                                                                                                                   |                                                         |              |                   |                |                 |       |

| R/W-0         | R/W-0                                                                                                                                                             | R/W-0                                                   | R/W-0        | R/W-0             | R/W-0          | R/W-0           | R/W-0 |

|               | F1BP                                                                                                                                                              | <3:0>                                                   |              |                   | F0BF           | ><3:0>          |       |

| bit 7         |                                                                                                                                                                   |                                                         |              |                   |                |                 | bit   |

| Legend:       |                                                                                                                                                                   |                                                         |              |                   |                |                 |       |

| R = Readable  | e bit                                                                                                                                                             | W = Writable                                            | bit          | U = Unimpleme     | ented bit, rea | d as '0'        |       |

| -n = Value at | POR                                                                                                                                                               | '1' = Bit is set                                        |              | '0' = Bit is clea | red            | x = Bit is unki | nown  |

| bit 15-12     | 1111 = Filter<br>1110 = Filter                                                                                                                                    | RX Buffer Writt<br>hits received ir<br>hits received ir | n RX FIFO bu | uffer             |                |                 |       |

|               | •                                                                                                                                                                 |                                                         |              |                   |                |                 |       |

|               | •                                                                                                                                                                 |                                                         |              |                   |                |                 |       |

|               |                                                                                                                                                                   | hits received ir hits received ir                       |              |                   |                |                 |       |

| bit 11-8      | <b>F2BP&lt;3:0&gt;:</b> RX Buffer Written when Filter 2 Hits bits<br>1111 = Filter hits received in RX FIFO buffer<br>1110 = Filter hits received in RX Buffer 14 |                                                         |              |                   |                |                 |       |

|               | •                                                                                                                                                                 |                                                         |              |                   |                |                 |       |

|               | •                                                                                                                                                                 |                                                         |              |                   |                |                 |       |

|               |                                                                                                                                                                   | hits received ir hits received ir                       |              |                   |                |                 |       |

| bit 7-4       | 1111 = Filter                                                                                                                                                     | RX Buffer Writt<br>hits received ir<br>hits received ir | n RX FIFO bu | uffer             |                |                 |       |

|               | •                                                                                                                                                                 |                                                         |              |                   |                |                 |       |

|               | •                                                                                                                                                                 |                                                         |              |                   |                |                 |       |

|               |                                                                                                                                                                   | hits received ir hits received ir                       |              |                   |                |                 |       |

| bit 3-0       | 1111 = Filter                                                                                                                                                     | RX Buffer Writ<br>hits received ir<br>hits received ir  | n RX FIFO bu | uffer             |                |                 |       |

|               | •                                                                                                                                                                 |                                                         |              |                   |                |                 |       |

|               | •<br>0001 = Filter<br>0000 = Filter                                                                                                                               | hits received ir                                        |              |                   |                |                 |       |

# PIC24HJXXXGPX06A/X08A/X10A

### REGISTER 20-4: ADxCON4: ADCx CONTROL REGISTER 4

| U-0             | U-0 | U-0              | U-0 | U-0                                     | U-0              | U-0        | U-0   |

|-----------------|-----|------------------|-----|-----------------------------------------|------------------|------------|-------|

| —               | —   | —                | _   | —                                       | —                | —          | —     |

| bit 15          |     |                  |     |                                         |                  |            | bit 8 |

|                 |     |                  |     |                                         |                  |            |       |

| U-0             | U-0 | U-0              | U-0 | U-0                                     | R/W-0            | R/W-0      | R/W-0 |

| —               | _   | —                | _   | —                                       |                  | DMABL<2:0> |       |

| bit 7           |     |                  |     |                                         |                  |            | bit 0 |

|                 |     |                  |     |                                         |                  |            |       |

| Legend:         |     |                  |     |                                         |                  |            |       |

| R = Readable    | bit | W = Writable b   | bit | U = Unimplei                            | mented bit, read | d as '0'   |       |

| -n = Value at P | POR | '1' = Bit is set |     | '0' = Bit is cleared x = Bit is unknown |                  |            | nown  |

### bit 15-3 Unimplemented: Read as '0'

bit 2-0

DMABL<2:0>: Selects Number of DMA Buffer Locations per Analog Input bits

111 = Allocates 128 words of buffer to each analog input

110 = Allocates 64 words of buffer to each analog input

101 = Allocates 32 words of buffer to each analog input

100 = Allocates 16 words of buffer to each analog input

011 = Allocates 8 words of buffer to each analog input

010 = Allocates 4 words of buffer to each analog input

001 = Allocates 2 words of buffer to each analog input

000 = Allocates 1 word of buffer to each analog input

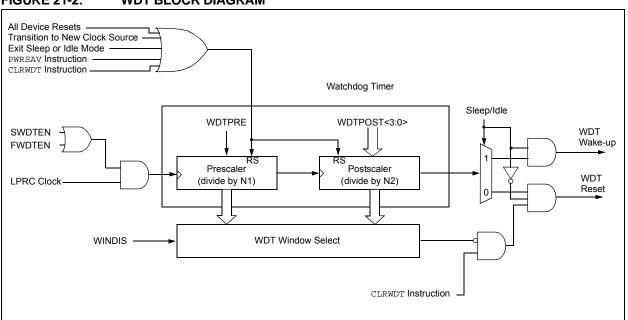

## 21.4 Watchdog Timer (WDT)

For PIC24HJXXXGPX06A/X08A/X10A devices, the WDT is driven by the LPRC oscillator. When the WDT is enabled, the clock source is also enabled.

The nominal WDT clock source from LPRC is 32 kHz. This feeds a prescaler than can be configured for either 5-bit (divide-by-32) or 7-bit (divide-by-128) operation. The prescaler is set by the WDTPRE Configuration bit. With a 32 kHz input, the prescaler yields a nominal WDT time-out period (TwDT) of 1 ms in 5-bit mode, or 4 ms in 7-bit mode.

A variable postscaler divides down the WDT prescaler output and allows for a wide range of time-out periods. The postscaler is controlled by the WDTPOST<3:0> Configuration bits (FWDT<3:0>) which allow the selection of a total of 16 settings, from 1:1 to 1:32,768. Using the prescaler and postscaler, time-out periods ranging from 1 ms to 131 seconds can be achieved.

The WDT, prescaler and postscaler are reset:

- On any device Reset

- On the completion of a clock switch, whether invoked by software (i.e., setting the OSWEN bit after changing the NOSC bits) or by hardware (i.e., Fail-Safe Clock Monitor)

- When a PWRSAV instruction is executed (i.e., Sleep or Idle mode is entered)

- When the device exits Sleep or Idle mode to resume normal operation

- By a CLRWDT instruction during normal execution

If the WDT is enabled, it will continue to run during Sleep or Idle modes. When the WDT time-out occurs, the device will wake the device and code execution will continue from where the PWRSAV instruction was executed. The corresponding SLEEP or IDLE bits (RCON<3,2>) will need to be cleared in software after the device wakes up.

The WDT flag bit, WDTO (RCON<4>), is not automatically cleared following a WDT time-out. To detect subsequent WDT events, the flag must be cleared in software.

Note: The CLRWDT and PWRSAV instructions clear the prescaler and postscaler counts when executed.

The WDT is enabled or disabled by the FWDTEN Configuration bit in the FWDT Configuration register. When the FWDTEN Configuration bit is set, the WDT is always enabled.

The WDT can be optionally controlled in software when the FWDTEN Configuration bit has been programmed to '0'. The WDT is enabled in software by setting the SWDTEN control bit (RCON<5>). The SWDTEN control bit is cleared on any device Reset. The software WDT option allows the user to enable the WDT for critical code segments and disable the WDT during non-critical segments for maximum power savings.

Note: If the WINDIS bit (FWDT<6>) is cleared, the CLRWDT instruction should be executed by the application software only during the last 1/4 of the WDT period. This CLRWDT window can be determined by using a timer. If a CLRWDT instruction is executed before this window, a WDT Reset occurs.

### FIGURE 21-2: WDT BLOCK DIAGRAM

| DC CHARACTERISTICS |                | $\begin{tabular}{lllllllllllllllllllllllllllllllllll$               |      |                    |     |       |                         |

|--------------------|----------------|---------------------------------------------------------------------|------|--------------------|-----|-------|-------------------------|

| Param<br>No.       | Symbol         | Characteristic                                                      | Min  | Тур <sup>(1)</sup> | Max | Units | Conditions              |

| Operating Voltage  |                |                                                                     |      |                    |     |       |                         |

| DC10               | Supply Voltage |                                                                     |      |                    |     |       |                         |

|                    | Vdd            |                                                                     | 3.0  |                    | 3.6 | V     | Industrial and Extended |

| DC12               | Vdr            | RAM Data Retention Voltage <sup>(2)</sup>                           | 1.8  | _                  |     | V     | _                       |

| DC16               | VPOR           | VDD Start Voltage<br>to ensure internal<br>Power-on Reset signal    | _    | _                  | Vss | V     | _                       |

| DC17               | SVDD           | <b>VDD Rise Rate</b><br>to ensure internal<br>Power-on Reset signal | 0.03 | _                  | —   | V/ms  | 0-3.0V in 0.1s          |

**Note 1:** Data in "Typ" column is at 3.3V, 25°C unless otherwise stated.

2: This is the limit to which VDD can be lowered without losing RAM data.

# TABLE 24-35:SPIX SLAVE MODE (FULL-DUPLEX, CKE = 0, CKP = 0, SMP = 0) TIMING<br/>REQUIREMENTS

| АС СНА       | AC CHARACTERISTICS    |                                                              |              | $\begin{array}{l} \mbox{Standard Operating Conditions: 2.4V to 3.6V} \\ \mbox{(unless otherwise stated)} \\ \mbox{Operating temperature} & -40^{\circ}C \leq TA \leq +85^{\circ}C \mbox{ for Industrial} \\ -40^{\circ}C \leq TA \leq +125^{\circ}C \mbox{ for Extended} \end{array}$ |     |       |                                      |  |

|--------------|-----------------------|--------------------------------------------------------------|--------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|-------|--------------------------------------|--|

| Param<br>No. | Symbol                | Characteristic <sup>(1)</sup>                                | Min          | Тур <sup>(2)</sup>                                                                                                                                                                                                                                                                    | Max | Units | Conditions                           |  |

| SP70         | TscP                  | Maximum SCK Input Frequency                                  | _            | _                                                                                                                                                                                                                                                                                     | 11  | MHz   | See Note 3                           |  |

| SP72         | TscF                  | SCKx Input Fall Time                                         | —            | _                                                                                                                                                                                                                                                                                     |     | ns    | See parameter DO32 and <b>Note 4</b> |  |

| SP73         | TscR                  | SCKx Input Rise Time                                         | —            | _                                                                                                                                                                                                                                                                                     |     | ns    | See parameter DO31 and <b>Note 4</b> |  |

| SP30         | TdoF                  | SDOx Data Output Fall Time                                   | —            | _                                                                                                                                                                                                                                                                                     |     | ns    | See parameter DO32 and <b>Note 4</b> |  |

| SP31         | TdoR                  | SDOx Data Output Rise Time                                   | —            | _                                                                                                                                                                                                                                                                                     | _   | ns    | See parameter DO31 and <b>Note 4</b> |  |

| SP35         | TscH2doV,<br>TscL2doV | SDOx Data Output Valid after<br>SCKx Edge                    | —            | 6                                                                                                                                                                                                                                                                                     | 20  | ns    | —                                    |  |

| SP36         | TdoV2scH,<br>TdoV2scL | SDOx Data Output Setup to<br>First SCKx Edge                 | 30           | _                                                                                                                                                                                                                                                                                     |     | ns    | —                                    |  |

| SP40         | TdiV2scH,<br>TdiV2scL | Setup Time of SDIx Data Input to SCKx Edge                   | 30           | _                                                                                                                                                                                                                                                                                     | _   | ns    | —                                    |  |

| SP41         | TscH2diL,<br>TscL2diL | Hold Time of SDIx Data Input to SCKx Edge                    | 30           | _                                                                                                                                                                                                                                                                                     | _   | ns    | —                                    |  |

| SP50         | TssL2scH,<br>TssL2scL | $\overline{SSx} \downarrow$ to SCKx $\uparrow$ or SCKx Input | 120          | _                                                                                                                                                                                                                                                                                     | _   | ns    | _                                    |  |

| SP51         | TssH2doZ              | SSx ↑ to SDOx Output<br>High-Impedance <sup>(4)</sup>        | 10           | —                                                                                                                                                                                                                                                                                     | 50  | ns    | -                                    |  |

| SP52         | TscH2ssH<br>TscL2ssH  | SSx after SCKx Edge                                          | 1.5 TCY + 40 | —                                                                                                                                                                                                                                                                                     | _   | ns    | See Note 4                           |  |

Note 1: These parameters are characterized, but are not tested in manufacturing.

2: Data in "Typ" column is at 3.3V, 25°C unless otherwise stated.

**3:** The minimum clock period for SCKx is 91 ns. Therefore, the SCK clock generated by the Master must not violate this specificiation.

**4:** Assumes 50 pF load on all SPIx pins.

| AC CH            | ARACTE          | RISTICS                                                                   | (unless  |                    | <b>e stated)</b><br>ature -4 | 0°C≤ TA | <b>DV to 3.6V</b><br>$\leq$ +85°C for Industrial<br>$\leq$ +125°C for Extended |

|------------------|-----------------|---------------------------------------------------------------------------|----------|--------------------|------------------------------|---------|--------------------------------------------------------------------------------|

| Param<br>No.     | Symbol          | Characteristic                                                            | Min.     | Typ <sup>(1)</sup> | Max.                         | Units   | Conditions                                                                     |

| Clock Parameters |                 |                                                                           |          |                    |                              |         |                                                                                |

| AD50             | TAD             | ADC Clock Period                                                          | 76       |                    |                              | ns      | —                                                                              |

| AD51             | tRC             | ADC Internal RC Oscillator Period                                         | —        | 250                | _                            | ns      | —                                                                              |

|                  | Conversion Rate |                                                                           |          |                    |                              |         |                                                                                |

| AD55             | tCONV           | Conversion Time                                                           | —        | 12 Tad             | —                            | _       | —                                                                              |

| AD56             | FCNV            | Throughput Rate                                                           | —        | _                  | 1.1                          | Msps    | —                                                                              |

| AD57             | TSAMP           | Sample Time                                                               | 2 Tad    | _                  | _                            | _       | —                                                                              |

|                  |                 | Timin                                                                     | ng Param | eters              |                              |         |                                                                                |

| AD60             | tPCS            | Conversion Start from Sample<br>Trigger <sup>(2)</sup>                    | 2.0 Tad  | —                  | 3.0 Tad                      |         | Auto-Convert Trigger<br>not selected                                           |

| AD61             | tPSS            | Sample Start from Setting<br>Sample (SAMP) bit <sup>(2)</sup>             | 2.0 Tad  | —                  | 3.0 Tad                      | _       | _                                                                              |

| AD62             | tcss            | Conversion Completion to<br>Sample Start (ASAM = 1) <sup>(2)</sup>        | —        | 0.5 Tad            | —                            | —       | _                                                                              |