#### Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFI

| Product Status             | Active                                                                          |

|----------------------------|---------------------------------------------------------------------------------|

| Core Processor             | PIC                                                                             |

| Core Size                  | 16-Bit                                                                          |

| Speed                      | 40 MIPs                                                                         |

| Connectivity               | CANbus, I <sup>2</sup> C, IrDA, LINbus, SPI, UART/USART                         |

| Peripherals                | Brown-out Detect/Reset, DMA, POR, PWM, WDT                                      |

| Number of I/O              | 85                                                                              |

| Program Memory Size        | 256КВ (85.5К х 24)                                                              |

| Program Memory Type        | FLASH                                                                           |

| EEPROM Size                | -                                                                               |

| RAM Size                   | 16K x 8                                                                         |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 3.6V                                                                       |

| Data Converters            | A/D 32x10b/12b                                                                  |

| Oscillator Type            | Internal                                                                        |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                               |

| Mounting Type              | Surface Mount                                                                   |

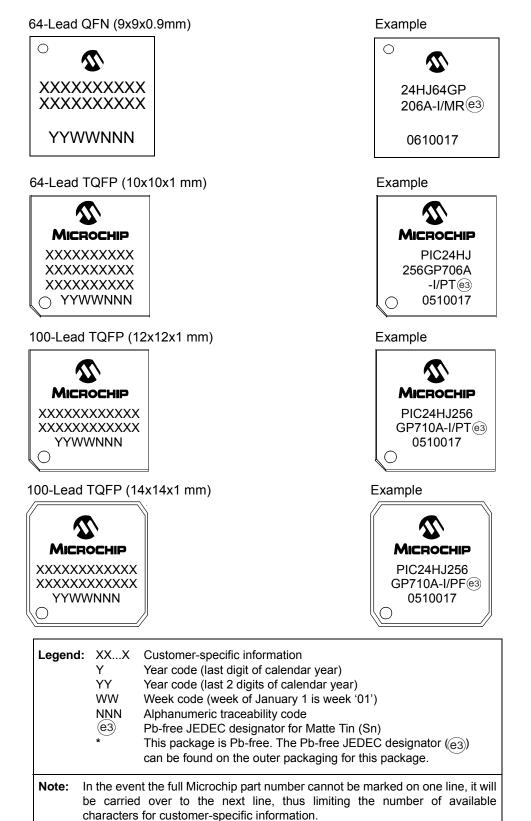

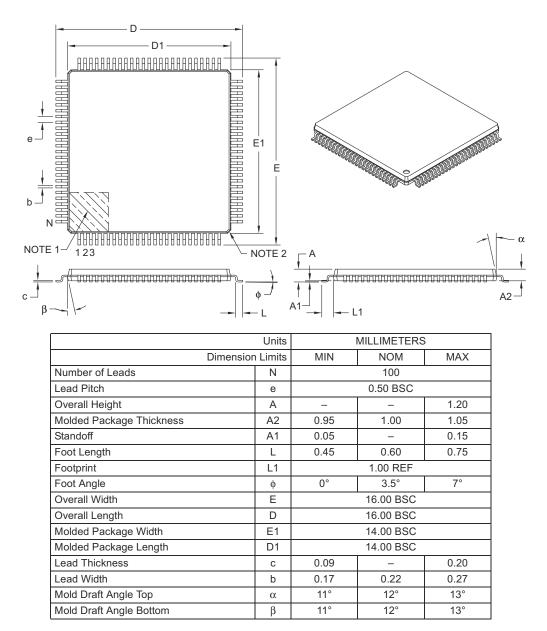

| Package / Case             | 100-TQFP                                                                        |

| Supplier Device Package    | 100-TQFP (14x14)                                                                |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic24hj256gp610a-i-pf |

|                            |                                                                                 |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | D15 D0                                |               |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------|---------------|

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | W0/WREG                               | PUSH.S Shadow |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | W1                                    |               |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | W2                                    | oo Shadow     |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | W3 Le                                 | egend         |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | W4                                    | 0             |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | W5                                    |               |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | W6                                    |               |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | W7                                    |               |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | W8 Working Register                   | S             |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | W9                                    |               |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | W10                                   |               |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | W11                                   |               |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | W12                                   |               |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | W13                                   |               |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | W14/Frame Pointer                     |               |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | W15/Stack Pointer                     |               |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | SPLIM Stack Pointer Limit Reg         | ister         |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                                       |               |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 0 Program Counter                     |               |

| 7 0<br>PSVPAG Pro                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | gram Space Visibility Page Address    |               |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | RCOUNT REPEAT Loop Counter            |               |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 15 0<br>CORCON Core Configuration Reg | gister        |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | DC IPL2 IPL1 IPL0 RA N OV Z C STATUS  | Register      |

| —   —   —   —   —   —   — ✓ SRH —                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | SRL SRL                               |               |

| —   —   —   —   —   —   — ▲ SRH — SRH |                                       |               |

| —   —   —   —   —   — ▲ SRH — S |                                       |               |

#### REGISTER 7-6: IFS1: INTERRUPT FLAG STATUS REGISTER 1 (CONTINUED)

| bit 3 | CNIF: Input Change Notification Interrupt Flag Status bit |

|-------|-----------------------------------------------------------|

|       | 1 = Interrupt request has occurred                        |

|       | 0 = Interrupt request has not occurred                    |

- bit 2 Unimplemented: Read as '0'

- bit 1 MI2C1IF: I2C1 Master Events Interrupt Flag Status bit

- 1 = Interrupt request has occurred

- 0 = Interrupt request has not occurred

- bit 0 SI2C1IF: I2C1 Slave Events Interrupt Flag Status bit

- 1 = Interrupt request has occurred

- 0 = Interrupt request has not occurred

### REGISTER 7-10: IEC0: INTERRUPT ENABLE CONTROL REGISTER 0 (CONTINUED)

| bit 2 | <b>OC1IE:</b> Output Compare Channel 1 Interrupt Enable bit<br>1 = Interrupt request enabled<br>0 = Interrupt request not enabled |

|-------|-----------------------------------------------------------------------------------------------------------------------------------|

| bit 1 | <b>IC1IE:</b> Input Capture Channel 1 Interrupt Enable bit<br>1 = Interrupt request enabled<br>0 = Interrupt request not enabled  |

| bit 0 | INTOIE: External Interrupt 0 Enable bit<br>1 = Interrupt request enabled<br>0 = Interrupt request not enabled                     |

#### REGISTER 7-17: IPC2: INTERRUPT PRIORITY CONTROL REGISTER 2

| U-0              | R/W-1                              | R/W-0                                      | R/W-0          | U-0              | R/W-1           | R/W-0           | R/W-0 |  |  |  |  |

|------------------|------------------------------------|--------------------------------------------|----------------|------------------|-----------------|-----------------|-------|--|--|--|--|

| —                |                                    | U1RXIP<2:0>                                |                | —                |                 | SPI1IP<2:0>     |       |  |  |  |  |

| bit 15           |                                    |                                            |                |                  |                 |                 | bit   |  |  |  |  |

| 11.0             |                                    | R/W-0                                      |                | 11.0             |                 | R/W-0           |       |  |  |  |  |

| U-0              | R/W-1                              | SPI1EIP<2:0>                               | R/W-0          | U-0              | R/W-1           | T3IP<2:0>       | R/W-0 |  |  |  |  |

| bit 7            |                                    | 0111211 \2.02                              |                |                  |                 | 1011 \2.02      | bit   |  |  |  |  |

| 510 1            |                                    |                                            |                |                  |                 |                 | bit   |  |  |  |  |

| Legend:          |                                    |                                            |                |                  |                 |                 |       |  |  |  |  |

| R = Readabl      | e bit                              | W = Writable                               | bit            | U = Unimple      | mented bit, rea | d as '0'        |       |  |  |  |  |

| -n = Value at    | POR                                | '1' = Bit is set                           |                | '0' = Bit is cle | eared           | x = Bit is unkr | nown  |  |  |  |  |

| bit 15           | Unimpleme                          | ented: Read as '                           | 0'             |                  |                 |                 |       |  |  |  |  |

| bit 14-12        | -                                  | :0>: UART1 Rece                            |                | Prioritv bits    |                 |                 |       |  |  |  |  |

|                  |                                    | rupt is priority 7 (                       | -              | -                |                 |                 |       |  |  |  |  |

|                  | •                                  |                                            |                |                  |                 |                 |       |  |  |  |  |

|                  | •                                  |                                            |                |                  |                 |                 |       |  |  |  |  |

|                  | 001 = Inter                        | 001 = Interrupt is priority 1              |                |                  |                 |                 |       |  |  |  |  |

|                  | 000 = Interrupt source is disabled |                                            |                |                  |                 |                 |       |  |  |  |  |

| bit 11           | Unimpleme                          | ented: Read as '                           | 0'             |                  |                 |                 |       |  |  |  |  |

| bit 10-8         |                                    | >: SPI1 Event In                           | =              | -                |                 |                 |       |  |  |  |  |

|                  | 111 = Inter                        | rupt is priority 7 (                       | highest priori | ty interrupt)    |                 |                 |       |  |  |  |  |

|                  | •                                  |                                            |                |                  |                 |                 |       |  |  |  |  |

|                  | •                                  |                                            |                |                  |                 |                 |       |  |  |  |  |

|                  |                                    | rupt is priority 1<br>rupt source is dis   | abled          |                  |                 |                 |       |  |  |  |  |

| bit 7            |                                    | ented: Read as '                           |                |                  |                 |                 |       |  |  |  |  |

| bit 6-4          | -                                  | :0>: SPI1 Error II                         |                | ty bits          |                 |                 |       |  |  |  |  |

|                  |                                    | rupt is priority 7 (                       | -              | -                |                 |                 |       |  |  |  |  |

|                  | •                                  |                                            |                |                  |                 |                 |       |  |  |  |  |

|                  | •                                  |                                            |                |                  |                 |                 |       |  |  |  |  |

|                  |                                    | rupt is priority 1                         |                |                  |                 |                 |       |  |  |  |  |

| <b>h</b> :+ 0    |                                    | rupt source is dis                         |                |                  |                 |                 |       |  |  |  |  |

| bit 3<br>bit 2-0 | -                                  | ented: Read as '                           |                |                  |                 |                 |       |  |  |  |  |

| DIL 2-0          |                                    | : Timer3 Interrupt<br>rupt is priority 7 ( | -              | v interrunt)     |                 |                 |       |  |  |  |  |

|                  | •                                  |                                            | nightest phon  | ly interrupt)    |                 |                 |       |  |  |  |  |

|                  | •                                  |                                            |                |                  |                 |                 |       |  |  |  |  |

|                  | •<br>001 = Inter                   | muchic criteriter d                        |                |                  |                 |                 |       |  |  |  |  |

|                  |                                    |                                            |                |                  |                 |                 |       |  |  |  |  |

| U-0                          | U-0                                                                        | U-0                                                                                                                    | U-0                           | U-0              | R/W-1           | R/W-0           | R/W-0 |

|------------------------------|----------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------|-------------------------------|------------------|-----------------|-----------------|-------|

| _                            | _                                                                          | _                                                                                                                      | _                             | —                |                 | DMA1IP<2:0>     |       |

| bit 15                       | ·                                                                          | ·                                                                                                                      |                               |                  |                 |                 | bit   |

| U-0                          | R/W-1                                                                      | R/W-0                                                                                                                  | R/W-0                         | U-0              | R/W-1           | R/W-0           | R/W-0 |

| —                            |                                                                            | AD1IP<2:0>                                                                                                             |                               |                  |                 | U1TXIP<2:0>     |       |

| bit 7                        |                                                                            |                                                                                                                        |                               |                  | ·               |                 | bit   |

| Legend:                      |                                                                            |                                                                                                                        |                               |                  |                 |                 |       |

| R = Readab                   | ole bit                                                                    | W = Writable                                                                                                           | bit                           | U = Unimplei     | mented bit, rea | ad as '0'       |       |

| -n = Value a                 | it POR                                                                     | '1' = Bit is set                                                                                                       |                               | '0' = Bit is cle | eared           | x = Bit is unkn | own   |

| bit 10-8<br>bit 7<br>bit 6-4 | 111 = Interrup<br>•<br>•<br>001 = Interrup<br>000 = Interrup<br>Unimplemen | >: DMA Channe<br>pt is priority 7 (I<br>pt is priority 1<br>pt source is dis<br><b>ted:</b> Read as '(<br>ADC1 Convers | nighest priori<br>abled<br>)' | ty interrupt)    |                 |                 |       |

|                              | •<br>•<br>001 = Interru                                                    | pt is priority 7 (I<br>pt is priority 1<br>pt source is dis                                                            |                               | ty interrupt)    |                 |                 |       |

| bit 3                        | Unimplemen                                                                 | ted: Read as 'd                                                                                                        | )'                            |                  |                 |                 |       |

| bit 2-0                      |                                                                            | •: UART1 Trans<br>pt is priority 7 (I                                                                                  |                               |                  |                 |                 |       |

|                              | 001 = Interru<br>000 = Interru                                             | ot is priority 1<br>pt source is dis                                                                                   | abled                         |                  |                 |                 |       |

#### REGISTER 7-18: IPC3: INTERRUPT PRIORITY CONTROL REGISTER 3

#### REGISTER 7-21: IPC6: INTERRUPT PRIORITY CONTROL REGISTER 6

| U-0           | R/W-1                                                                                                                                   | R/W-0                                                                                  | R/W-0           | U-0               | R/W-1          | R/W-0           | R/W-0  |  |  |  |

|---------------|-----------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------|-----------------|-------------------|----------------|-----------------|--------|--|--|--|

| _             |                                                                                                                                         | T4IP<2:0>                                                                              |                 | <u> </u>          |                | OC4IP<2:0>      |        |  |  |  |

| bit 15        |                                                                                                                                         |                                                                                        |                 |                   |                |                 | bit 8  |  |  |  |

| U-0           | R/W-1                                                                                                                                   | R/W-0                                                                                  | R/W-0           | U-0               | R/W-1          | R/W-0           | R/W-0  |  |  |  |

| _             |                                                                                                                                         | OC3IP<2:0>                                                                             | 1011 0          | _                 |                | DMA2IP<2:0>     | 1011 0 |  |  |  |

| bit 7         |                                                                                                                                         |                                                                                        |                 |                   |                |                 | bit    |  |  |  |

| Legend:       |                                                                                                                                         |                                                                                        |                 |                   |                |                 |        |  |  |  |

| R = Readable  | e bit                                                                                                                                   | W = Writable                                                                           | bit             | U = Unimplei      | mented bit, re | ad as '0'       |        |  |  |  |

| -n = Value at | POR                                                                                                                                     | '1' = Bit is set                                                                       |                 | '0' = Bit is cle  | ared           | x = Bit is unkn | own    |  |  |  |

| bit 15        | Unimpleme                                                                                                                               | ented: Read as '                                                                       | 0'              |                   |                |                 |        |  |  |  |

| bit 14-12     | -                                                                                                                                       | Timer4 Interrupt                                                                       |                 |                   |                |                 |        |  |  |  |

|               | 111 = Interr                                                                                                                            | upt is priority 7 (                                                                    | highest priorit | ty interrupt)     |                |                 |        |  |  |  |

|               | •                                                                                                                                       |                                                                                        |                 |                   |                |                 |        |  |  |  |

|               |                                                                                                                                         |                                                                                        |                 |                   |                |                 |        |  |  |  |

|               | 001 = Interrupt is priority 1                                                                                                           |                                                                                        |                 |                   |                |                 |        |  |  |  |

|               | 000 = Interrupt source is disabled                                                                                                      |                                                                                        |                 |                   |                |                 |        |  |  |  |

| bit 11        | -                                                                                                                                       | ented: Read as '                                                                       |                 |                   |                |                 |        |  |  |  |

| bit 10-8      | OC4IP<2:0>: Output Compare Channel 4 Interrupt Priority bits                                                                            |                                                                                        |                 |                   |                |                 |        |  |  |  |

|               | 111 = Interrupt is priority 7 (highest priority interrupt)                                                                              |                                                                                        |                 |                   |                |                 |        |  |  |  |

|               | •                                                                                                                                       |                                                                                        |                 |                   |                |                 |        |  |  |  |

|               | •                                                                                                                                       |                                                                                        |                 |                   |                |                 |        |  |  |  |