Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFI

| 2 0 0 0 0 0                |                                                                                 |

|----------------------------|---------------------------------------------------------------------------------|

| Product Status             | Active                                                                          |

| Core Processor             | PIC                                                                             |

| Core Size                  | 16-Bit                                                                          |

| Speed                      | 40 MIPs                                                                         |

| Connectivity               | CANbus, I <sup>2</sup> C, IrDA, LINbus, SPI, UART/USART                         |

| Peripherals                | Brown-out Detect/Reset, DMA, POR, PWM, WDT                                      |

| Number of I/O              | 85                                                                              |

| Program Memory Size        | 256KB (85.5K x 24)                                                              |

| Program Memory Type        | FLASH                                                                           |

| EEPROM Size                | -                                                                               |

| RAM Size                   | 16K x 8                                                                         |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 3.6V                                                                       |

| Data Converters            | A/D 32x10b/12b                                                                  |

| Oscillator Type            | Internal                                                                        |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                               |

| Mounting Type              | Surface Mount                                                                   |

| Package / Case             | 100-TQFP                                                                        |

| Supplier Device Package    | 100-TQFP (12x12)                                                                |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic24hj256gp610a-i-pt |

|                            |                                                                                 |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

For remapping operations, the 8-bit Program Space Visibility register (PSVPAG) is used to define a 16K word page in the program space. When the Most Significant bit of the EA is '1', PSVPAG is concatenated with the lower 15 bits of the EA to form a 23-bit program space address. Unlike table operations, this limits remapping operations strictly to the user memory area. Table 4-35 and Figure 4-6 show how the program EA is created for table operations and remapping accesses from the data EA. Here, P<23:0> refers to a program space word, whereas D<15:0> refers to a data space word.

# TABLE 4-35: PROGRAM SPACE ADDRESS CONSTRUCTION

| Access Type              | Access        | Program Space Address         |             |                                   |                    |       |  |

|--------------------------|---------------|-------------------------------|-------------|-----------------------------------|--------------------|-------|--|

| Access Type              | Space         | <23>                          | <22:16>     | <15>                              | <14:1>             | <0>   |  |

| Instruction Access       | User          | 0 PC<22:1>                    |             |                                   |                    | 0     |  |

| (Code Execution)         |               |                               | 0xxx xxxx x | xxx xx                            | xx xxxx xxx0       |       |  |

| TBLRD/TBLWT              | User          | TBLPAG<7:0>                   |             | Data EA<15:0>                     |                    |       |  |

| (Byte/Word Read/Write)   |               | 0                             | xxx xxxx    | XXXX XX                           | xx xxxx xxxx       |       |  |

|                          | Configuration | TBLPAG<7:0>                   |             | Data EA<15:0>                     |                    |       |  |

|                          |               | 1xxx xxxx xxxx xxxx xxxx xxxx |             |                                   |                    |       |  |

| Program Space Visibility | User          | 0                             | PSVPAG<7    | 7:0> Data EA<14:0> <sup>(1)</sup> |                    | 0>(1) |  |

| (Block Remap/Read)       |               | 0                             | XXXX XXXX   |                                   | xxx xxxx xxxx xxxx |       |  |

**Note 1:** Data EA<15> is always '1' in this case, but is not used in calculating the program space address. Bit 15 of the address is PSVPAG<0>.

| ABLE 7-1         | 1 1                                  | T VECTORS   | 1            |                                      |

|------------------|--------------------------------------|-------------|--------------|--------------------------------------|

| Vector<br>Number | Interrupt<br>Request (IRQ)<br>Number | IVT Address | AIVT Address | Interrupt Source                     |

| 8                | 0                                    | 0x000014    | 0x000114     | INT0 – External Interrupt 0          |

| 9                | 1                                    | 0x000016    | 0x000116     | IC1 – Input Capture 1                |

| 10               | 2                                    | 0x000018    | 0x000118     | OC1 – Output Compare 1               |

| 11               | 3                                    | 0x00001A    | 0x00011A     | T1 – Timer1                          |

| 12               | 4                                    | 0x00001C    | 0x00011C     | DMA0 – DMA Channel 0                 |

| 13               | 5                                    | 0x00001E    | 0x00011E     | IC2 – Input Capture 2                |

| 14               | 6                                    | 0x000020    | 0x000120     | OC2 – Output Compare 2               |

| 15               | 7                                    | 0x000022    | 0x000122     | T2 – Timer2                          |

| 16               | 8                                    | 0x000024    | 0x000124     | T3 – Timer3                          |

| 17               | 9                                    | 0x000026    | 0x000126     | SPI1E – SPI1 Error                   |

| 18               | 10                                   | 0x000028    | 0x000128     | SPI1 – SPI1 Transfer Done            |

| 19               | 11                                   | 0x00002A    | 0x00012A     | U1RX – UART1 Receiver                |

| 20               | 12                                   | 0x00002C    | 0x00012C     | U1TX – UART1 Transmitter             |

| 21               | 13                                   | 0x00002E    | 0x00012E     | ADC1 – Analog-to-Digital Converter 1 |

| 22               | 14                                   | 0x000030    | 0x000130     | DMA1 – DMA Channel 1                 |

| 23               | 15                                   | 0x000032    | 0x000132     | Reserved                             |

| 24               | 16                                   | 0x000034    | 0x000134     | SI2C1 – I2C1 Slave Events            |

| 25               | 17                                   | 0x000036    | 0x000136     | MI2C1 – I2C1 Master Events           |

| 26               | 18                                   | 0x000038    | 0x000138     | Reserved                             |

| 27               | 19                                   | 0x00003A    | 0x00013A     | CN - Change Notification Interrupt   |

| 28               | 20                                   | 0x00003C    | 0x00013C     | INT1 – External Interrupt 1          |

| 29               | 21                                   | 0x00003E    | 0x00013E     | ADC2 – Analog-to-Digital Converter 2 |

| 30               | 22                                   | 0x000040    | 0x000140     | IC7 – Input Capture 7                |

| 31               | 23                                   | 0x000042    | 0x000142     | IC8 – Input Capture 8                |

| 32               | 24                                   | 0x000044    | 0x000144     | DMA2 – DMA Channel 2                 |

| 33               | 25                                   | 0x000046    | 0x000146     | OC3 – Output Compare 3               |

| 34               | 26                                   | 0x000048    | 0x000148     | OC4 – Output Compare 4               |

| 35               | 27                                   | 0x00004A    | 0x00014A     | T4 – Timer4                          |

| 36               | 28                                   | 0x00004C    | 0x00014C     | T5 – Timer5                          |

| 37               | 29                                   | 0x00004E    | 0x00014E     | INT2 – External Interrupt 2          |

| 38               | 30                                   | 0x000050    | 0x000150     | U2RX – UART2 Receiver                |

| 39               | 31                                   | 0x000052    | 0x000152     | U2TX – UART2 Transmitter             |

| 40               | 32                                   | 0x000054    | 0x000154     | SPI2E – SPI2 Error                   |

| 41               | 33                                   | 0x000056    | 0x000156     | SPI1 – SPI1 Transfer Done            |

| 42               | 34                                   | 0x000058    | 0x000158     | C1RX – ECAN1 Receive Data Ready      |

| 43               | 35                                   | 0x00005A    | 0x00015A     | C1 – ECAN1 Event                     |

| 44               | 36                                   | 0x00005C    | 0x00015C     | DMA3 – DMA Channel 3                 |

| 45               | 37                                   | 0x00005E    | 0x00015E     | IC3 – Input Capture 3                |

| 46               | 38                                   | 0x000060    | 0x000160     | IC4 – Input Capture 4                |

| 47               | 39                                   | 0x000062    | 0x000162     | IC5 – Input Capture 5                |

| 48               | 40                                   | 0x000064    | 0x000164     | IC6 – Input Capture 6                |

| 49               | 41                                   | 0x000066    | 0x000166     | OC5 – Output Compare 5               |

| 50               | 42                                   | 0x000068    | 0x000168     | OC6 – Output Compare 6               |

| 51               | 43                                   | 0x00006A    | 0x00016A     | OC7 – Output Compare 7               |

| 52               | 44                                   | 0x00006C    | 0x00016C     | OC8 – Output Compare 8               |

| 53               | 45                                   | 0x00006E    | 0x00016E     | Reserved                             |

TABLE 7-1: INTERRUPT VECTORS

| R/W-0            | R-0                                                                                                                                                                                                                                           | U-0                                                   | U-0                                        | U-0              | U-0    | U-0             | U-0           |  |  |

|------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------|--------------------------------------------|------------------|--------|-----------------|---------------|--|--|

| ALTIVT           | DISI                                                                                                                                                                                                                                          | _                                                     | _                                          | _                | _      | _               | _             |  |  |

| bit 15           |                                                                                                                                                                                                                                               |                                                       |                                            |                  |        |                 | bit 8         |  |  |

|                  |                                                                                                                                                                                                                                               |                                                       |                                            |                  |        |                 |               |  |  |

| U-0              | U-0                                                                                                                                                                                                                                           | U-0                                                   | R/W-0                                      | R/W-0            | R/W-0  | R/W-0           | R/W-0         |  |  |

| <br>bit 7        | _                                                                                                                                                                                                                                             | —                                                     | INT4EP                                     | INT3EP           | INT2EP | INT1EP          | INT0EP<br>bit |  |  |

|                  |                                                                                                                                                                                                                                               |                                                       |                                            |                  |        |                 | DI            |  |  |

| Legend:          |                                                                                                                                                                                                                                               |                                                       |                                            |                  |        |                 |               |  |  |

| R = Readable     | e bit                                                                                                                                                                                                                                         | W = Writable                                          | ble bit U = Unimplemented bit, read as '0' |                  |        |                 |               |  |  |

| -n = Value at    | POR                                                                                                                                                                                                                                           | '1' = Bit is set                                      |                                            | '0' = Bit is cle | ared   | x = Bit is unkr | nown          |  |  |

| bit 15<br>bit 14 | ALTIVT: Enable Alternate Interrupt Vector Table bit<br>1 = Use alternate vector table<br>0 = Use standard (default) vector table<br>DISI: DISI Instruction Status bit<br>1 = DISI instruction is active<br>0 = DISI instruction is not active |                                                       |                                            |                  |        |                 |               |  |  |

| bit 13-5         | Unimplement                                                                                                                                                                                                                                   | ted: Read as '                                        | 0'                                         |                  |        |                 |               |  |  |

| bit 4            | <b>INT4EP:</b> External Interrupt 4 Edge Detect Polarity Select bit<br>1 = Interrupt on negative edge<br>0 = Interrupt on positive edge                                                                                                       |                                                       |                                            |                  |        |                 |               |  |  |

| bit 3            | 1 = Interrupt o                                                                                                                                                                                                                               | rnal Interrupt 3<br>on negative ed<br>on positive edg | ge                                         | Polarity Select  | t bit  |                 |               |  |  |

| bit 2            | <ul> <li>INT2EP: External Interrupt 2 Edge Detect Polarity Select bit</li> <li>1 = Interrupt on negative edge</li> <li>0 = Interrupt on positive edge</li> </ul>                                                                              |                                                       |                                            |                  |        |                 |               |  |  |

| bit 1            | 1 = Interrupt o                                                                                                                                                                                                                               | rnal Interrupt ´<br>on negative ed<br>on positive edg | ge                                         | Polarity Select  | t bit  |                 |               |  |  |

| bit 0            | 1 = Interrupt c                                                                                                                                                                                                                               | rnal Interrupt (<br>on negative ed<br>on positive edg | ge                                         | Polarity Select  | t bit  |                 |               |  |  |

# REGISTER 7-4: INTCON2: INTERRUPT CONTROL REGISTER 2

|                         | U-0                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | U-0                                                                                                                                   | U-0                                                                                                                     | U-0              | U-0             | U-0             | U-0 |

|-------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------|------------------|-----------------|-----------------|-----|

| —                       | _                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                                                                                                                                       |                                                                                                                         | _                | _               |                 |     |

| bit 15                  | -                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                                                                                                                                       |                                                                                                                         |                  |                 |                 | bit |

| R/W-0                   | R/W-0                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | R/W-0                                                                                                                                 | R/W-0                                                                                                                   | U-0              | R/W-0           | R/W-0           | U-0 |

| C2TXIF                  | C1TXIF                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | DMA7IF                                                                                                                                | DMA6IF                                                                                                                  | _                | U2EIF           | U1EIF           | _   |

| bit 7                   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                                                                                                                                       |                                                                                                                         |                  |                 |                 | bit |

| Legend:                 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                                                                                                                                       |                                                                                                                         |                  |                 |                 |     |

| R = Readable            | bit                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | W = Writable                                                                                                                          | bit                                                                                                                     | U = Unimplen     | nented bit, rea | id as '0'       |     |

| -n = Value at F         | POR                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | '1' = Bit is set                                                                                                                      |                                                                                                                         | '0' = Bit is cle | ared            | x = Bit is unkn | own |

| bit 7<br>bit 6<br>bit 5 | <ul> <li>C2TXIF: ECAN2 Transmit Data Request Interrupt Flag Status bit</li> <li>1 = Interrupt request has occurred</li> <li>0 = Interrupt request has not occurred</li> <li>C1TXIF: ECAN1 Transmit Data Request Interrupt Flag Status bit</li> <li>1 = Interrupt request has occurred</li> <li>0 = Interrupt request has not occurred</li> <li>DMA7IF: DMA Channel 7 Data Transfer Complete Interrupt Flag Status bit</li> <li>1 = Interrupt request has occurred</li> </ul> |                                                                                                                                       |                                                                                                                         |                  |                 |                 |     |

|                         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                                                                                                                                       |                                                                                                                         |                  |                 |                 |     |

|                         | 0 = Interrupt r<br>DMA6IF: DM.<br>1 = Interrupt r                                                                                                                                                                                                                                                                                                                                                                                                                            | request has not                                                                                                                       | : occurred<br>ata Transfer C<br>curred                                                                                  | Complete Interr  | upt Flag Statu  | s bit           |     |

| bit 4                   | 0 = Interrupt r<br>DMA6IF: DM<br>1 = Interrupt r<br>0 = Interrupt r                                                                                                                                                                                                                                                                                                                                                                                                          | equest has not<br>A Channel 6 Da<br>equest has occ                                                                                    | coccurred<br>ata Transfer C<br>curred<br>coccurred                                                                      | Complete Interr  | upt Flag Statu  | s bit           |     |

|                         | 0 = Interrupt r<br>DMA6IF: DM.<br>1 = Interrupt r<br>0 = Interrupt r<br>Unimplemen<br>U2EIF: UART<br>1 = Interrupt r                                                                                                                                                                                                                                                                                                                                                         | request has not<br>A Channel 6 Da<br>request has occ<br>request has not                                                               | coccurred<br>ata Transfer C<br>curred<br>coccurred<br>o'<br>ot Flag Status<br>curred                                    |                  | upt Flag Statu  | s bit           |     |

| bit 4<br>bit 3          | 0 = Interrupt r<br>DMA6IF: DM.<br>1 = Interrupt r<br>0 = Interrupt r<br>Unimplemen<br>U2EIF: UART<br>1 = Interrupt r<br>0 = Interrupt r<br>U1EIF: UART<br>1 = Interrupt r                                                                                                                                                                                                                                                                                                    | equest has not<br>A Channel 6 Da<br>equest has occ<br>equest has not<br><b>ted:</b> Read as '0<br>'2 Error Interrup<br>equest has occ | coccurred<br>ata Transfer C<br>curred<br>coccurred<br>of Flag Status<br>curred<br>coccurred<br>of Flag Status<br>curred | bit              | upt Flag Statu  | s bit           |     |

### REGISTER 7-9: IFS4: INTERRUPT FLAG STATUS REGISTER 4

# 7.4 Interrupt Setup Procedures

### 7.4.1 INITIALIZATION

To configure an interrupt source:

- 1. Set the NSTDIS bit (INTCON1<15>) if nested interrupts are not desired.

- Select the user-assigned priority level for the interrupt source by writing the control bits in the appropriate IPCx register. The priority level will depend on the specific application and type of interrupt source. If multiple priority levels are not desired, the IPCx register control bits for all enabled interrupt sources may be programmed to the same non-zero value.

| Note: | At a device Reset, the IPCx registers are |  |  |  |

|-------|-------------------------------------------|--|--|--|

|       | initialized, such that all user interrupt |  |  |  |

|       | sources are assigned to priority level 4. |  |  |  |

- 3. Clear the interrupt flag status bit associated with the peripheral in the associated IFSx register.

- 4. Enable the interrupt source by setting the interrupt enable control bit associated with the source in the appropriate IECx register.

# 7.4.2 INTERRUPT SERVICE ROUTINE

The method that is used to declare an ISR and initialize the IVT with the correct vector address will depend on the programming language (i.e., C or assembler) and the language development toolsuite that is used to develop the application. In general, the user must clear the interrupt flag in the appropriate IFSx register for the source of interrupt that the ISR handles. Otherwise, the ISR will be re-entered immediately after exiting the routine. If the ISR is coded in assembly language, it must be terminated using a RETFIE instruction to unstack the saved PC value, SRL value and old CPU priority level.

#### 7.4.3 TRAP SERVICE ROUTINE

A Trap Service Routine (TSR) is coded like an ISR, except that the appropriate trap status flag in the INTCON1 register must be cleared to avoid re-entry into the TSR.

#### 7.4.4 INTERRUPT DISABLE

All user interrupts can be disabled using the following procedure:

- 1. Push the current SR value onto the software stack using the PUSH instruction.

- 2. Force the CPU to priority level 7 by inclusive ORing the value 0x0E with SRL.

To enable user interrupts, the POP instruction may be used to restore the previous SR value.

Note that only user interrupts with a priority level of 7 or less can be disabled. Trap sources (level 8-level 15) cannot be disabled.

The DISI instruction provides a convenient way to disable interrupts of priority levels 1-6 for a fixed period of time. Level 7 interrupt sources are not disabled by the DISI instruction.

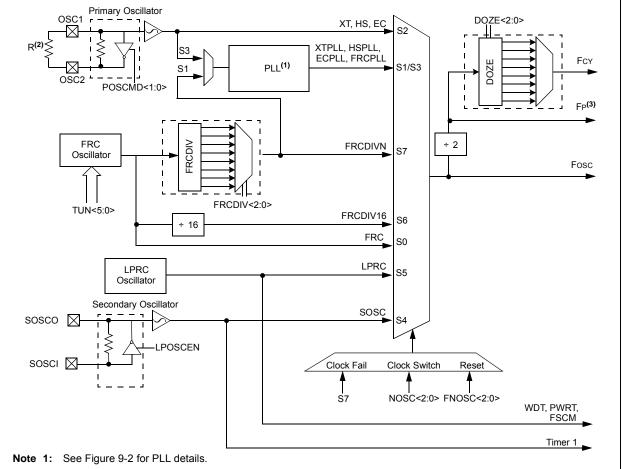

# 9.0 OSCILLATOR CONFIGURATION

- Note 1: This data sheet summarizes the features of the PIC24HJXXXGPX06A/X08A/X10A family of devices. However, it is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to Section 7. "Oscillator" (DS70186) of the "dsPIC33F/dsPIC33F/PIC24H Family Reference Manual", which is available from the Microchip web site (www.microchip.com).

- 2: Some registers and associated bits described in this section may not be available on all devices. Refer to Section 4.0 "Memory Organization" in this data sheet for device-specific register and bit information.

The PIC24HJXXXGPX06A/X08A/X10A oscillator system provides:

- Various external and internal oscillator options as clock sources

- An on-chip PLL to scale the internal operating frequency to the required system clock frequency

- The internal FRC oscillator can also be used with the PLL, thereby allowing full-speed operation without any external clock generation hardware

- Clock switching between various clock sources

- Programmable clock postscaler for system power savings

- A Fail-Safe Clock Monitor (FSCM) that detects clock failure and takes fail-safe measures

- An Oscillator Control register (OSCCON)

- Nonvolatile Configuration bits for main oscillator selection.

A simplified diagram of the oscillator system is shown in Figure 9-1.

# FIGURE 9-1: PIC24HJXXXGPX06A/X08A/X10A OSCILLATOR SYSTEM DIAGRAM

- 2: If the Oscillator is used with XT or HS modes, an extended parallel resistor with the value of 1 MΩ must be connected.

- **3:** The term, FP refers to the clock source for all the peripherals, while FCY refers to the clock source for the CPU. Throughout this document FP and FCY are used interchangeably, except in the case of Doze mode. FP and FCY will be different when Doze mode is used in any ratio other than 1:1, which is the default.

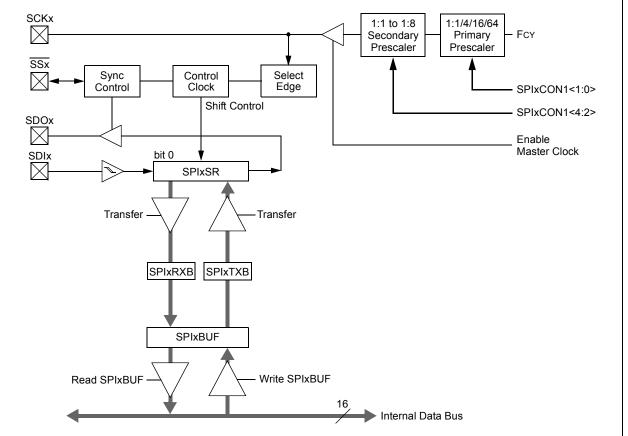

# 16.0 SERIAL PERIPHERAL INTERFACE (SPI)

- Note 1: This data sheet summarizes the features of the PIC24HJXXXGPX06A/X08A/X10A family of devices. However, it is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to the "dsPIC33F/PIC24H Family Reference Manual", Section 18. "Serial Peripheral Interface (SPI)" (DS70206), which is available from the Microchip web site (www.microchip.com).

- 2: Some registers and associated bits described in this section may not be available on all devices. Refer to **Section 4.0 "Memory Organization"** in this data sheet for device-specific register and bit information.

The Serial Peripheral Interface (SPI) module is a synchronous serial interface useful for communicating with other peripheral or microcontroller devices. These peripheral devices may be serial EEPROMs, shift registers, display drivers, Analog-to-Digital converters, etc. The SPI module is compatible with SPI and SIOP from Motorola<sup>®</sup>.

Note: In this section, the SPI modules are referred to together as SPIx, or separately as SPI1 and SPI2. Special Function Registers will follow a similar notation. For example, SPIxCON refers to the control register for the SPI1 or SPI2 module.

Each SPI module consists of a 16-bit shift register, SPIxSR (where x = 1 or 2), used for shifting data in and out, and a buffer register, SPIxBUF. A control register, SPIxCON, configures the module. Additionally, a status register, SPIxSTAT, indicates various status conditions.

The serial interface consists of 4 pins: SDIx (serial data input), SDOx (serial data output), SCKx (shift clock input or output), and SSx (active-low slave select).

In Master mode operation, SCK is a clock output but in Slave mode, it is a clock input.

# FIGURE 16-1: SPI MODULE BLOCK DIAGRAM

# REGISTER 17-2: I2CxSTAT: I2Cx STATUS REGISTER (CONTINUED)

| bit 3 | <ul> <li>Start bit</li> <li>1 = Indicates that a Start (or Repeated Start) bit has been detected last</li> <li>0 = Start bit was not detected last</li> </ul>                                                               |

|-------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| bit 2 | Hardware set or clear when Start, Repeated Start or Stop detected.<br><b>R_W:</b> Read/Write Information bit (when operating as I <sup>2</sup> C slave)<br>1 = Read – indicates data transfer is output from slave          |

|       | 0 = Write - indicates data transfer is input to slaveHardware set or clear after reception of I2C device address byte.                                                                                                      |

| bit 1 | RBF: Receive Buffer Full Status bit                                                                                                                                                                                         |

|       | <ul> <li>1 = Receive complete, I2CxRCV is full</li> <li>0 = Receive not complete, I2CxRCV is empty</li> <li>Hardware set when I2CxRCV is written with received byte. Hardware clear when software reads I2CxRCV.</li> </ul> |

| bit 0 | TBF: Transmit Buffer Full Status bit                                                                                                                                                                                        |

|       | <ul> <li>1 = Transmit in progress, I2CxTRN is full</li> <li>0 = Transmit complete, I2CxTRN is empty</li> <li>Hardware set when software writes I2CxTRN. Hardware clear at completion of data transmission.</li> </ul>       |

| R/W-x             | R/W-x                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | R/W-x                     | R/W-x            | R/W-x                              | R/W-x | R/W-x              | R/W-x |  |  |  |

|-------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------|------------------|------------------------------------|-------|--------------------|-------|--|--|--|

|                   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                           |                  | :10:3>                             |       |                    |       |  |  |  |

| bit 15            |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                           |                  |                                    |       |                    | bit   |  |  |  |

| R/W-x             | R/W-x                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | R/W-x                     | U-0              | R/W-x                              | U-0   | R/W-x              | R/W-x |  |  |  |

|                   | SID<2:0>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                           | _                | EXIDE                              | _     | EID<1              | 7:16> |  |  |  |

| bit 7             |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                           |                  |                                    |       |                    | bit ( |  |  |  |

|                   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                           |                  |                                    |       |                    |       |  |  |  |

| Legend:           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                           |                  |                                    |       |                    |       |  |  |  |

| R = Readable bit  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | W = Writable bit          |                  | U = Unimplemented bit, read as '0' |       | l as '0'           |       |  |  |  |

| -n = Value at POR |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | '1' = Bit is set          |                  | '0' = Bit is cleared               |       | x = Bit is unknown |       |  |  |  |

| bit 15-5          | SID<10:0>: Standard Identifier bits<br>1 = Message address bit SIDx must be '1<br>0 = Message address bit SIDx must be '0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                           |                  |                                    |       |                    |       |  |  |  |

| bit 4             | Unimplemer                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | ted: Read as '            | 0'               |                                    |       |                    |       |  |  |  |

| bit 3             |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | nded Identifier           | Enable bit       |                                    |       |                    |       |  |  |  |

|                   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | If MIDE = 1:              |                  |                                    |       |                    |       |  |  |  |

|                   | <ol> <li>1 = Match only messages with extended identifier addresses</li> <li>0 = Match only messages with standard identifier addresses</li> </ol>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                           |                  |                                    |       |                    |       |  |  |  |

|                   | O – Match on     O     O     O     O     O     O     O     O     O     O     O     O     O     O     O     O     O     O     O     O     O     O     O     O     O     O     O     O     O     O     O     O     O     O     O     O     O     O     O     O     O     O     O     O     O     O     O     O     O     O     O     O     O     O     O     O     O     O     O     O     O     O     O     O     O     O     O     O     O     O     O     O     O     O     O     O     O     O     O     O     O     O     O     O     O     O     O     O     O     O     O     O     O     O     O     O     O     O     O     O     O     O     O     O     O     O     O     O     O     O     O     O     O     O     O     O     O     O     O     O     O     O     O     O     O     O     O     O     O     O     O     O     O     O     O     O     O     O     O     O     O     O     O     O     O     O     O     O     O     O     O     O     O     O     O     O     O     O     O     O     O     O     O     O     O     O     O     O     O     O     O     O     O     O     O     O     O     O     O     O     O     O     O     O     O     O     O     O     O     O     O     O     O     O     O     O     O     O     O     O     O     O     O     O     O     O     O     O     O     O     O     O     O     O     O     O     O     O     O     O     O     O     O     O     O     O     O     O     O     O     O     O     O     O     O     O     O     O     O     O     O     O     O     O     O     O     O     O     O     O     O     O     O     O     O     O     O     O     O     O     O     O     O     O     O     O     O     O     O     O     O     O     O     O     O     O     O     O     O     O     O     O     O     O     O     O     O     O     O     O     O     O     O     O     O     O     O     O     O     O     O     O     O     O     O     O     O     O     O     O     O     O     O     O     O     O     O     O     O     O     O     O     O     O     O     O     O     O     O     O     O     O     O     O     O     O     O | iy messayes w             | illi Slanuaru il |                                    | 000   |                    |       |  |  |  |