Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFl

| Product Status             | Active                                                                           |

|----------------------------|----------------------------------------------------------------------------------|

| Core Processor             | PIC                                                                              |

| Core Size                  | 16-Bit                                                                           |

| Speed                      | 40 MIPs                                                                          |

| Connectivity               | CANbus, I <sup>2</sup> C, IrDA, LINbus, SPI, UART/USART                          |

| Peripherals                | Brown-out Detect/Reset, DMA, POR, PWM, WDT                                       |

| Number of I/O              | 85                                                                               |

| Program Memory Size        | 256KB (85.5K x 24)                                                               |

| Program Memory Type        | FLASH                                                                            |

| EEPROM Size                | -                                                                                |

| RAM Size                   | 16K x 8                                                                          |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 3.6V                                                                        |

| Data Converters            | A/D 32x10b/12b                                                                   |

| Oscillator Type            | Internal                                                                         |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                                |

| Mounting Type              | Surface Mount                                                                    |

| Package / Case             | 100-TQFP                                                                         |

| Supplier Device Package    | 100-TQFP (14x14)                                                                 |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic24hj256gp610at-i-pf |

|                            |                                                                                  |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

#### 2.5 ICSP Pins

The PGECx and PGEDx pins are used for In-Circuit Serial Programming<sup>TM</sup> (ICSP<sup>TM</sup>) and debugging purposes. It is recommended to keep the trace length between the ICSP connector and the ICSP pins on the device as short as possible. If the ICSP connector is expected to experience an ESD event, a series resistor is recommended, with the value in the range of a few tens of Ohms, not to exceed 100 Ohms.

Pull-up resistors, series diodes, and capacitors on the PGECx and PGEDx pins are not recommended as they will interfere with the programmer/debugger communications to the device. If such discrete components are an application requirement, they should be removed from the circuit during programming and debugging. Alternatively, refer to the AC/DC characteristics and requirements timing information in the "dsPIC33F/PIC24H Flash Programming Specification" (DS70152) for information on capacitive loading limits and pin input voltage high (VIH) and input low (VIL) requirements.

Ensure that the "Communication Channel Select" (i.e., PGECx/PGEDx pins) programmed into the device matches the physical connections for the ICSP to MPLAB<sup>®</sup> ICD 3 or MPLAB REAL ICE<sup>™</sup>.

For more information on ICD 3 and REAL ICE connection requirements, refer to the following documents that are available on the Microchip web site.

- "Using MPLAB<sup>®</sup> ICD 3 In-Circuit Debugger" (poster) DS51765

- "MPLAB<sup>®</sup> ICD 3 Design Advisory" DS51764

- "MPLAB<sup>®</sup> REAL ICE<sup>™</sup> In-Circuit Emulator User's Guide" DS51616

- *"Using MPLAB<sup>®</sup> REAL ICE™"* (poster) DS51749

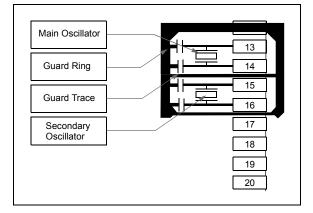

#### 2.6 External Oscillator Pins

Many MCUs have options for at least two oscillators: a high-frequency primary oscillator and a low-frequency secondary oscillator (refer to **Section 9.0 "Oscillator Configuration"** for details).

The oscillator circuit should be placed on the same side of the board as the device. Also, place the oscillator circuit close to the respective oscillator pins, not exceeding one-half inch (12 mm) distance between them. The load capacitors should be placed next to the oscillator itself, on the same side of the board. Use a grounded copper pour around the oscillator circuit to isolate them from surrounding circuits. The grounded copper pour should be routed directly to the MCU ground. Do not run any signal traces or power traces inside the ground pour. Also, if using a two-sided board, avoid any traces on the other side of the board where the crystal is placed. A suggested layout is shown in Figure 2-3.

#### FIGURE 2-3: SUGGESTED PLACEMENT OF THE OSCILLATOR CIRCUIT

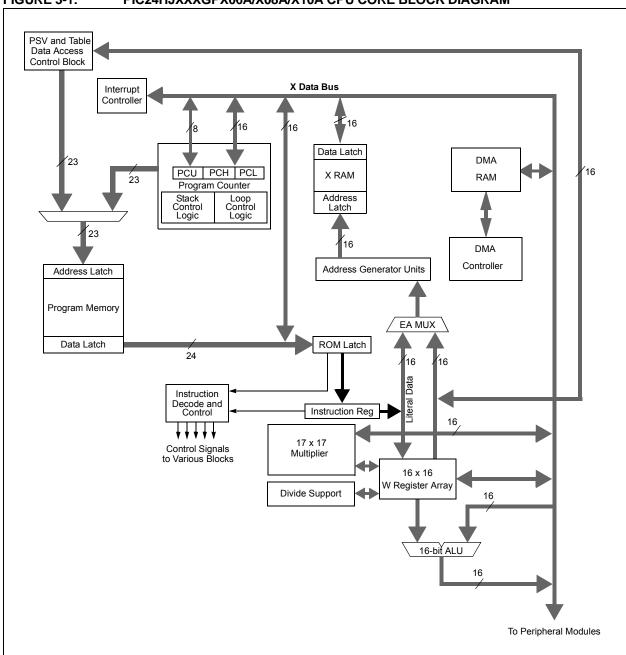

#### FIGURE 3-1: PIC24HJXXXGPX06A/X08A/X10A CPU CORE BLOCK DIAGRAM

#### 4.2 Data Address Space

The PIC24HJXXXGPX06A/X08A/X10A CPU has a separate 16-bit wide data memory space. The data space is accessed using separate Address Generation Units (AGUs) for read and write operations. Data memory maps of devices with different RAM sizes are shown in Figure 4-3 and Figure 4-4.

All Effective Addresses (EAs) in the data memory space are 16 bits wide and point to bytes within the data space. This arrangement gives a data space address range of 64 Kbytes or 32K words. The lower half of the data memory space (that is, when EA<15> = 0) is used for implemented memory addresses, while the upper half (EA<15> = 1) is reserved for the Program Space Visibility area (see Section 4.4.3 "Reading Data from Program Memory Using Program Space Visibility").

PIC24HJXXXGPX06A/X08A/X10A devices implement up to 16 Kbytes of data memory. Should an EA point to a location outside of this area, an all-zero word or byte will be returned.

#### 4.2.1 DATA SPACE WIDTH

The data memory space is organized in byte addressable, 16-bit wide blocks. Data is aligned in data memory and registers as 16-bit words, but all data space EAs resolve to bytes. The Least Significant Bytes of each word have even addresses, while the Most Significant Bytes have odd addresses.

#### 4.2.2 DATA MEMORY ORGANIZATION AND ALIGNMENT

To maintain backward compatibility with PIC<sup>®</sup> MCU devices and improve data space memory usage efficiency, the PIC24HJXXXGPX06A/X08A/X10A instruction set supports both word and byte operations. As a consequence of byte accessibility, all effective address calculations are internally scaled to step through word-aligned memory. For example, the core recognizes that Post-Modified Register Indirect Addressing mode [Ws++] will result in a value of Ws + 1 for byte operations and Ws + 2 for word operations.

Data byte reads will read the complete word that contains the byte, using the Least Significant bit (LSb) of any EA to determine which byte to select. The selected byte is placed onto the Least Significant Byte (LSB) of the data path. That is, data memory and registers are organized as two parallel byte-wide entities with shared (word) address decode but separate write lines. Data byte writes only write to the corresponding side of the array or register which matches the byte address. All word accesses must be aligned to an even address. Misaligned word data fetches are not supported, so care must be taken when mixing byte and word operations, or translating from 8-bit MCU code. If a misaligned read or write is attempted, an address error trap is generated. If the error occurred on a read, the instruction underway is completed; if it occurred on a write, the instruction will be executed but the write does not occur. In either case, a trap is then executed, allowing the system and/or user to examine the machine state prior to execution of the address Fault.

All byte loads into any W register are loaded into the Least Significant Byte. The Most Significant Byte (MSB) is not modified.

A sign-extend instruction (SE) is provided to allow users to translate 8-bit signed data to 16-bit signed values. Alternatively, for 16-bit unsigned data, users can clear the Most Significant Byte of any W register by executing a zero-extend (ZE) instruction on the appropriate address.

#### 4.2.3 SFR SPACE

The first 2 Kbytes of the Near Data Space, from 0x0000 to 0x07FF, is primarily occupied by Special Function Registers (SFRs). These are used by the PIC24HJXXXGPX06A/X08A/X10A core and peripheral modules for controlling the operation of the device.

SFRs are distributed among the modules that they control, and are generally grouped together by module. Much of the SFR space contains unused addresses; these are read as '0'. A complete listing of implemented SFRs, including their addresses, is shown in Table 4-1 through Table 4-33.

| Note: | The actual set of peripheral features and<br>interrupts varies by the device. Please<br>refer to the corresponding device tables<br>and pinout diagrams for device-specific |

|-------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|       | information.                                                                                                                                                                |

#### 4.2.4 NEAR DATA SPACE

The 8-Kbyte area between 0x0000 and 0x1FFF is referred to as the Near Data Space. Locations in this space are directly addressable via a 13-bit absolute address field within all memory direct instructions. Additionally, the whole data space is addressable using MOV instructions, which support Memory Direct Addressing mode with a 16-bit address field, or by using Indirect Addressing mode using a working register as an Address Pointer.

| IABLE 4-23 | S: EC | AN2 RI    | GISTE  | R MAF     | WHEN   |        | RL1.W   | IN = 1 | FOR PIC | 24HJ2    | 6GP610   |          | CES OF   | NLY (CO              |       | JED)  |        |               |

|------------|-------|-----------|--------|-----------|--------|--------|---------|--------|---------|----------|----------|----------|----------|----------------------|-------|-------|--------|---------------|

| File Name  | Addr  | Bit 15    | Bit 14 | Bit 13    | Bit 12 | Bit 11 | Bit 10  | Bit 9  | Bit 8   | Bit 7    | Bit 6    | Bit 5    | Bit 4    | Bit 3                | Bit 2 | Bit 1 | Bit 0  | All<br>Resets |

| C2RXF11EID | 056E  |           |        |           | EID<   | 15:8>  |         |        |         |          |          |          | EID<7    | /:0>                 |       |       |        | xxxx          |

| C2RXF12SID | 0570  |           |        |           | SID<   | 10:3>  |         |        |         |          | SID<2:0> |          | —        | EXIDE                | —     | EID<1 | 17:16> | xxxx          |

| C2RXF12EID | 0572  |           |        |           | EID<   | 15:8>  |         |        |         |          |          |          | EID<7:0> |                      |       |       | xxxx   |               |

| C2RXF13SID | 0574  |           |        |           | SID<   | 10:3>  |         |        |         |          | SID<2:0> |          | _        | — EXIDE — EID<17:16> |       |       |        | xxxx          |

| C2RXF13EID | 0576  |           |        | EID<15:8> |        |        |         |        |         |          | EID<7    | EID<7:0> |          |                      |       | xxxx  |        |               |

| C2RXF14SID | 0578  |           |        |           | SID<   | 10:3>  |         |        |         |          | SID<2:0> |          | _        | EXIDE                | —     | EID<1 | xxxx   |               |

| C2RXF14EID | 057A  | EID<15:8> |        |           |        |        | D<15:8> |        |         | EID<7:0> |          |          |          |                      | xxxx  |       |        |               |

| C2RXF15SID | 057C  |           |        |           | SID<   | 10:3>  |         |        |         |          | SID<2:0> |          | —        | EXIDE                | _     | EID<1 | 17:16> | xxxx          |

| C2RXF15EID | 057E  |           |        |           | EID<   | 15:8>  |         |        |         |          |          |          | EID<7    | /:0>                 |       |       |        | xxxx          |

#### TABLE 4-23: ECAN2 REGISTER MAP WHEN C2CTRL1.WIN = 1 FOR PIC24HJ256GP610A DEVICES ONLY (CONTINUED)

Legend: x = unknown value on Reset, — = unimplemented, read as '0'. Reset values are shown in hexadecimal for PinHigh devices.

DS70592D-page 49

#### TABLE 4-24: PORTA REGISTER MAP<sup>(1)</sup>

|           |      |         |         |         |         |        | -       | -      |       |        | -      |        |        |        |        |        |        |               |

|-----------|------|---------|---------|---------|---------|--------|---------|--------|-------|--------|--------|--------|--------|--------|--------|--------|--------|---------------|

| File Name | Addr | Bit 15  | Bit 14  | Bit 13  | Bit 12  | Bit 11 | Bit 10  | Bit 9  | Bit 8 | Bit 7  | Bit 6  | Bit 5  | Bit 4  | Bit 3  | Bit 2  | Bit 1  | Bit 0  | All<br>Resets |

| TRISA     | 02C0 | TRISA15 | TRISA14 | TRISA13 | TRISA12 | —      | TRISA10 | TRISA9 | -     | TRISA7 | TRISA6 | TRISA5 | TRISA4 | TRISA3 | TRISA2 | TRISA1 | TRISA0 | F6FF          |

| PORTA     | 02C2 | RA15    | RA14    | RA13    | RA12    | _      | RA10    | RA9    | _     | RA7    | RA6    | RA5    | RA4    | RA3    | RA2    | RA1    | RA0    | xxxx          |

| LATA      | 02C4 | LATA15  | LATA14  | LATA13  | LATA12  | _      | LATA10  | LATA9  | _     | LATA7  | LATA6  | LATA5  | LATA4  | LATA3  | LATA2  | LATA1  | LATA0  | xxxx          |

| ODCA      | 06C0 | ODCA15  | ODCA14  | _       | _       |        | _       | _      | -     |        |        | ODCA5  | ODCA4  | ODCA3  | ODCA2  | ODCA1  | ODCA0  | 0000          |

Legend: x = unknown value on Reset, — = unimplemented, read as '0'. Reset values are shown in hexadecimal for PinHigh devices.

Note 1: The actual set of I/O port pins varies from one device to another. Please refer to the corresponding pinout diagrams.

#### TABLE 4-25: PORTB REGISTER MAP<sup>(1)</sup>

| File Name | Addr | Bit 15  | Bit 14  | Bit 13  | Bit 12  | Bit 11  | Bit 10  | Bit 9  | Bit 8  | Bit 7  | Bit 6  | Bit 5  | Bit 4  | Bit 3  | Bit 2  | Bit 1  | Bit 0  | All<br>Resets |

|-----------|------|---------|---------|---------|---------|---------|---------|--------|--------|--------|--------|--------|--------|--------|--------|--------|--------|---------------|

| TRISB     | 02C6 | TRISB15 | TRISB14 | TRISB13 | TRISB12 | TRISB11 | TRISB10 | TRISB9 | TRISB8 | TRISB7 | TRISB6 | TRISB5 | TRISB4 | TRISB3 | TRISB2 | TRISB1 | TRISB0 | FFFF          |

| PORTB     | 02C8 | RB15    | RB14    | RB13    | RB12    | RB11    | RB10    | RB9    | RB8    | RB7    | RB6    | RB5    | RB4    | RB3    | RB2    | RB1    | RB0    | xxxx          |

| LATB      | 02CA | LATB15  | LATB14  | LATB13  | LATB12  | LATB11  | LATB10  | LATB9  | LATB8  | LATB7  | LATB6  | LATB5  | LATB4  | LATB3  | LATB2  | LATB1  | LATB0  | xxxx          |

Legend: x = unknown value on Reset, — = unimplemented, read as '0'. Reset values are shown in hexadecimal for PinHigh devices.

Note 1: The actual set of I/O port pins varies from one device to another. Please refer to the corresponding pinout diagrams.

#### TABLE 4-26: PORTC REGISTER MAP<sup>(1)</sup>

| File Name | Addr | Bit 15  | Bit 14  | Bit 13  | Bit 12  | Bit 11 | Bit 10 | Bit 9 | Bit 8 | Bit 7 | Bit 6 | Bit 5 | Bit 4  | Bit 3  | Bit 2  | Bit 1  | Bit 0 | All<br>Resets |

|-----------|------|---------|---------|---------|---------|--------|--------|-------|-------|-------|-------|-------|--------|--------|--------|--------|-------|---------------|

| TRISC     | 02CC | TRISC15 | TRISC14 | TRISC13 | TRISC12 | _      | _      | —     | _     | _     | _     |       | TRISC4 | TRISC3 | TRISC2 | TRISC1 | —     | F01E          |

| PORTC     | 02CE | RC15    | RC14    | RC13    | RC12    | _      | —      | _     | _     | _     | _     | —     | RC4    | RC3    | RC2    | RC1    | —     | xxxx          |

| LATC      | 02D0 | LATC15  | LATC14  | LATC13  | LATC12  | _      | _      | _     | _     | _     | _     | -     | LATC4  | LATC3  | LATC2  | LATC1  | —     | xxxx          |

Legend: x = unknown value on Reset, — = unimplemented, read as '0'. Reset values are shown in hexadecimal for PinHigh devices.

Note 1: The actual set of I/O port pins varies from one device to another. Please refer to the corresponding pinout diagrams.

#### TABLE 4-27: PORTD REGISTER MAP<sup>(1)</sup>

| File Name | Addr | Bit 15  | Bit 14  | Bit 13  | Bit 12  | Bit 11  | Bit 10  | Bit 9  | Bit 8  | Bit 7  | Bit 6  | Bit 5  | Bit 4  | Bit 3  | Bit 2  | Bit 1  | Bit 0  | All<br>Resets |

|-----------|------|---------|---------|---------|---------|---------|---------|--------|--------|--------|--------|--------|--------|--------|--------|--------|--------|---------------|

| TRISD     | 02D2 | TRISD15 | TRISD14 | TRISD13 | TRISD12 | TRISD11 | TRISD10 | TRISD9 | TRISD8 | TRISD7 | TRISD6 | TRISD5 | TRISD4 | TRISD3 | TRISD2 | TRISD1 | TRISD0 | FFFF          |

| PORTD     | 02D4 | RD15    | RD14    | RD13    | RD12    | RD11    | RD10    | RD9    | RD8    | RD7    | RD6    | RD5    | RD4    | RD3    | RD2    | RD1    | RD0    | xxxx          |

| LATD      | 02D6 | LATD15  | LATD14  | LATD13  | LATD12  | LATD11  | LATD10  | LATD9  | LATD8  | LATD7  | LATD6  | LATD5  | LATD4  | LATD3  | LATD2  | LATD1  | LATD0  | xxxx          |

| ODCD      | 06D2 | ODCD15  | ODCD14  | ODCD13  | ODCD12  | ODCD11  | ODCD10  | ODCD9  | ODCD8  | ODCD7  | ODCD6  | ODCD5  | ODCD4  | ODCD3  | ODCD2  | ODCD1  | ODCD0  | 0000          |

Legend: x = unknown value on Reset, - = unimplemented, read as '0'. Reset values are shown in hexadecimal for PinHigh devices.

Note 1: The actual set of I/O port pins varies from one device to another. Please refer to the corresponding pinout diagrams.

#### REGISTER 7-12: IEC2: INTERRUPT ENABLE CONTROL REGISTER 2

| R/W-0         | R/W-0           | U-0                             | R/W-0          | R/W-0            | R/W-0            | R/W-0           | R/W-0   |

|---------------|-----------------|---------------------------------|----------------|------------------|------------------|-----------------|---------|

| T6IE          | DMA4IE          | —                               | OC8IE          | OC7IE            | OC6IE            | OC5IE           | IC6IE   |

| bit 15        |                 |                                 |                |                  | •                |                 | bit 8   |

| R/W-0         | R/W-0           | R/W-0                           | R/W-0          | R/W-0            | R/W-0            | R/W-0           | R/W-0   |

| IC5IE         | IC4IE           | IC3IE                           | DMA3IE         | C1IE             | C1RXIE           | SPI2IE          | SPI2EIE |

| bit 7         |                 |                                 |                | 0                |                  |                 | bit (   |

| Legend:       |                 |                                 |                |                  |                  |                 |         |

| R = Readable  | e bit           | W = Writable                    | bit            | U = Unimpler     | mented bit, read | l as '0'        |         |

| -n = Value at | POR             | '1' = Bit is set                |                | '0' = Bit is cle | eared            | x = Bit is unki | nown    |

| bit 15        | T6IE: Timer6    | Interrupt Enabl                 | e bit          |                  |                  |                 |         |

|               |                 | request enable                  |                |                  |                  |                 |         |

|               | 0 = Interrupt r | equest not ena                  | bled           |                  |                  |                 |         |

| bit 14        |                 | A Channel 4 D                   |                | Complete Interi  | rupt Enable bit  |                 |         |

|               |                 | equest enable<br>equest not ena |                |                  |                  |                 |         |

| bit 13        | •               | ted: Read as '                  |                |                  |                  |                 |         |

| bit 12        | •               | ut Compare Ch                   |                | unt Enable bit   |                  |                 |         |

| 511 12        | •               | request enable                  |                |                  |                  |                 |         |

|               |                 | equest not ena                  |                |                  |                  |                 |         |

| bit 11        | OC7IE: Outpu    | ut Compare Ch                   | annel 7 Interr | upt Enable bit   |                  |                 |         |

|               |                 | equest enable<br>equest not ena |                |                  |                  |                 |         |

| bit 10        | OC6IE: Outpu    | ut Compare Ch                   | annel 6 Interr | upt Enable bit   |                  |                 |         |

|               |                 | equest enable<br>equest not ena |                |                  |                  |                 |         |

| bit 9         | OC5IE: Outpu    | ut Compare Ch                   | annel 5 Interr | upt Enable bit   |                  |                 |         |

|               |                 | equest enable<br>equest not ena |                |                  |                  |                 |         |

| bit 8         |                 | Capture Channe                  |                | Enable bit       |                  |                 |         |

|               |                 | equest enable<br>equest not ena |                |                  |                  |                 |         |

| bit 7         |                 | Capture Channe                  |                | Enable bit       |                  |                 |         |

|               | -               | equest enable                   |                |                  |                  |                 |         |

|               | •               | request not ena                 |                |                  |                  |                 |         |

| bit 6         | -               | Capture Channe                  |                | Enable bit       |                  |                 |         |

|               |                 | equest enable<br>equest not ena |                |                  |                  |                 |         |

| bit 5         | •               | Capture Channe                  |                | -nable bit       |                  |                 |         |

|               | -               | equest enable                   | -              |                  |                  |                 |         |

|               | 0 = Interrupt r | equest not ena                  | bled           |                  |                  |                 |         |

| bit 4         | DMA3IE: DM      | A Channel 3 D                   | ata Transfer C | Complete Interi  | rupt Enable bit  |                 |         |

|               |                 | equest enable<br>equest not ena |                |                  |                  |                 |         |

| bit 3         | -               | Event Interrup                  |                |                  |                  |                 |         |

| bit J         |                 | equest enable                   |                |                  |                  |                 |         |

|               |                 | equest not ena                  |                |                  |                  |                 |         |

| <b>REGISTER 8-1: DMAxCON: DMA CHANNEL x CONTROL REGISTER</b> |

|--------------------------------------------------------------|

|--------------------------------------------------------------|

| R/W-0                         | R/W-0                       | R/W-0                                 | R/W-0              | R/W-0                                    | U-0            | U-0              | U-0     |

|-------------------------------|-----------------------------|---------------------------------------|--------------------|------------------------------------------|----------------|------------------|---------|

| CHEN                          | SIZE                        | DIR                                   | HALF               | NULLW                                    | —              |                  | —       |

| pit 15                        |                             |                                       |                    |                                          |                |                  | bit     |

| U-0                           | U-0                         | R/W-0                                 | R/W-0              | U-0                                      | U-0            | R/W-0            | R/W-0   |

| _                             |                             | -                                     | E<1:0>             |                                          | _              | MODE             |         |

| bit 7                         |                             |                                       |                    |                                          |                |                  | bit     |

| Logondu                       |                             |                                       |                    |                                          |                |                  |         |

| <b>Legend:</b><br>R = Readabl | e hit                       | W = Writable                          | bit                | U = Unimplem                             | onted hit rea  | d as '0'         |         |

| -n = Value at                 |                             | '1' = Bit is set                      |                    | '0' = Bit is clea                        |                | x = Bit is unkr  |         |

|                               | FUR                         |                                       |                    |                                          | areu           |                  | IOWII   |

| bit 15                        | CHEN: Chan                  | nel Enable bit                        |                    |                                          |                |                  |         |

|                               | 1 = Channel                 | enabled                               |                    |                                          |                |                  |         |

|                               | 0 = Channel                 | disabled                              |                    |                                          |                |                  |         |

| bit 14                        | SIZE: Data T                | ransfer Size bi                       | t                  |                                          |                |                  |         |

|                               | 1 = Byte<br>0 = Word        |                                       |                    |                                          |                |                  |         |

| bit 13                        | DIR: Transfe                | r Direction bit (                     | source/destination | ation bus select)                        | 1              |                  |         |

|                               |                             |                                       |                    | to peripheral ado<br>o DMA RAM ado       |                |                  |         |

| bit 12                        | HALF: Early                 | Block Transfer                        | Complete Int       | errupt Select bit                        |                |                  |         |

|                               |                             |                                       |                    | ipt when half of t<br>ipt when all of th |                |                  |         |

| bit 11                        |                             | l Data Peripher                       | -                  | -                                        |                |                  |         |

|                               |                             | write to periph                       |                    | n to DMA RAM v                           | write (DIR bit | must also be cle | ar)     |

| bit 10-6                      | Unimplemer                  | ted: Read as                          | 0'                 |                                          |                |                  |         |

| bit 5-4                       | AMODE<1:0                   | >: DMA Chann                          | el Operating I     | Mode Select bits                         | 5              |                  |         |

|                               | 11 = Reserve                |                                       |                    |                                          |                |                  |         |

|                               |                             | ral Indirect Add                      |                    |                                          |                |                  |         |

|                               |                             | r Indirect witho<br>r Indirect with F |                    |                                          |                |                  |         |

| bit 3-2                       | Unimplemer                  | nted: Read as '                       | 0'                 |                                          |                |                  |         |

| oit 1-0                       | MODE<1:0>                   | : DMA Channe                          | I Operating M      | ode Select bits                          |                |                  |         |

|                               | 11 = One-Sh<br>10 = Continu |                                       |                    | ed (one block tra                        | nsfer from/to  | each DMA RAM     | buffer) |

|                               |                             | ot, Ping-Pong                         |                    |                                          |                |                  |         |

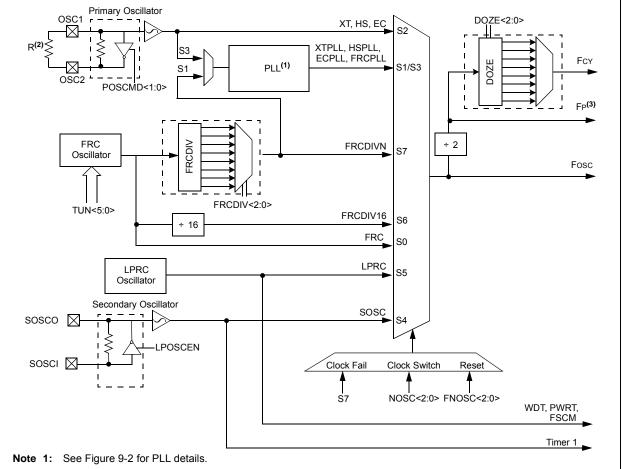

### 9.0 OSCILLATOR CONFIGURATION

- Note 1: This data sheet summarizes the features of the PIC24HJXXXGPX06A/X08A/X10A family of devices. However, it is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to Section 7. "Oscillator" (DS70186) of the "dsPIC33F/dsPIC33F/PIC24H Family Reference Manual", which is available from the Microchip web site (www.microchip.com).

- 2: Some registers and associated bits described in this section may not be available on all devices. Refer to Section 4.0 "Memory Organization" in this data sheet for device-specific register and bit information.

The PIC24HJXXXGPX06A/X08A/X10A oscillator system provides:

- Various external and internal oscillator options as clock sources

- An on-chip PLL to scale the internal operating frequency to the required system clock frequency

- The internal FRC oscillator can also be used with the PLL, thereby allowing full-speed operation without any external clock generation hardware

- Clock switching between various clock sources

- Programmable clock postscaler for system power savings

- A Fail-Safe Clock Monitor (FSCM) that detects clock failure and takes fail-safe measures

- An Oscillator Control register (OSCCON)

- Nonvolatile Configuration bits for main oscillator selection.

A simplified diagram of the oscillator system is shown in Figure 9-1.

#### FIGURE 9-1: PIC24HJXXXGPX06A/X08A/X10A OSCILLATOR SYSTEM DIAGRAM

- 2: If the Oscillator is used with XT or HS modes, an extended parallel resistor with the value of 1 MΩ must be connected.

- **3:** The term, FP refers to the clock source for all the peripherals, while FCY refers to the clock source for the CPU. Throughout this document FP and FCY are used interchangeably, except in the case of Doze mode. FP and FCY will be different when Doze mode is used in any ratio other than 1:1, which is the default.

#### 9.1 CPU Clocking System

There are seven system clock options provided by the PIC24HJXXXGPX06A/X08A/X10A:

- FRC Oscillator

- FRC Oscillator with PLL

- Primary (XT, HS or EC) Oscillator

- Primary Oscillator with PLL

- Secondary (LP) Oscillator

- LPRC Oscillator

- FRC Oscillator with postscaler

#### 9.1.1 SYSTEM CLOCK SOURCES

The FRC (Fast RC) internal oscillator runs at a nominal frequency of 7.37 MHz. The user software can tune the FRC frequency. User software can optionally specify a factor (ranging from 1:2 to 1:256) by which the FRC clock frequency is divided. This factor is selected using the FRCDIV<2:0> (CLKDIV<10:8>) bits.

The primary oscillator can use one of the following as its clock source:

- XT (Crystal): Crystals and ceramic resonators in the range of 3 MHz to 10 MHz. The crystal is connected to the OSC1 and OSC2 pins.

- HS (High-Speed Crystal): Crystals in the range of 10 MHz to 40 MHz. The crystal is connected to the OSC1 and OSC2 pins.

- EC (External Clock): External clock signal is directly applied to the OSC1 pin.

The secondary (LP) oscillator is designed for low power and uses a 32.768 kHz crystal or ceramic resonator. The LP oscillator uses the SOSCI and SOSCO pins.

The LPRC (Low-Power RC) internal oscillator runs at a nominal frequency of 32.768 kHz. It is also used as a reference clock by the Watchdog Timer (WDT) and Fail-Safe Clock Monitor (FSCM).

The clock signals generated by the FRC and primary oscillators can be optionally applied to an on-chip Phase-Locked Loop (PLL) to provide a wide range of output frequencies for device operation. PLL configuration is described in **Section 9.1.3 "PLL Configuration**".

The FRC frequency depends on the FRC accuracy (see Table 24-19) and the value of the FRC Oscillator Tuning register (see Register 9-4).

#### 9.1.2 SYSTEM CLOCK SELECTION

The oscillator source that is used at a device Power-on Reset event is selected using Configuration bit settings. The oscillator Configuration bit settings are located in the Configuration registers in the program memory. (Refer to **Section 21.1 "Configuration Bits"** for further details.) The Initial Oscillator Selection Configuration bits, FNOSC<2:0> (FOSCSEL<2:0>), and the Primary Oscillator Mode Select Configuration bits, POSCMD<1:0> (FOSC<1:0>), select the oscillator source that is used at a Power-on Reset. The FRC primary oscillator is the default (unprogrammed) selection.

The Configuration bits allow users to choose between twelve different clock modes, shown in Table 9-1.

The output of the oscillator (or the output of the PLL if a PLL mode has been selected) FOSC is divided by 2 to generate the device instruction clock (FCY) and the peripheral clock time base (FP). FCY defines the operating speed of the device, and speeds up to 40 MHz are supported by the PIC24HJXXXGPX06A/ X08A/X10A architecture.

Instruction execution speed or device operating frequency, FCY, is calculated, as shown in Equation 9-1:

#### EQUATION 9-1: DEVICE OPERATING FREQUENCY

$$FCY = \frac{FOSC}{2}$$

#### 9.1.3 PLL CONFIGURATION

The primary oscillator and internal FRC oscillator can optionally use an on-chip PLL to obtain higher speeds of operation. The PLL provides a significant amount of flexibility in selecting the device operating speed. A block diagram of the PLL is shown in Figure 9-2.

The output of the primary oscillator or FRC, denoted as 'FIN', is divided down by a prescale factor (N1) of 2, 3, ... or 33 before being provided to the PLL's Voltage Controlled Oscillator (VCO). The input to the VCO must be selected to be in the range of 0.8 MHz to 8 MHz. Since the minimum prescale factor is 2, this implies that FIN must be chosen to be in the range of 1.6 MHz to 16 MHz. The prescale factor 'N1' is selected using the PLLPRE<4:0> bits (CLKDIV<4:0>).

The PLL Feedback Divisor, selected using the PLLDIV<8:0> bits (PLLFBD<8:0>), provides a factor 'M', by which the input to the VCO is multiplied. This factor must be selected such that the resulting VCO output frequency is in the range of 100 MHz to 200 MHz.

The VCO output is further divided by a postscale factor 'N2'. This factor is selected using the PLLPOST<1:0> bits (CLKDIV<7:6>). 'N2' can be either 2, 4 or 8, and must be selected such that the PLL output frequency (Fosc) is in the range of 12.5 MHz to 80 MHz, which generates device operating speeds of 6.25-40 MIPS.

For a primary oscillator or FRC oscillator, output 'FIN', the PLL output 'FOSC' is given by:

#### EQUATION 9-2: Fosc CALCULATION

$FOSC = FIN \cdot \left(\frac{M}{N1 \cdot N2}\right)$

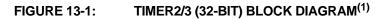

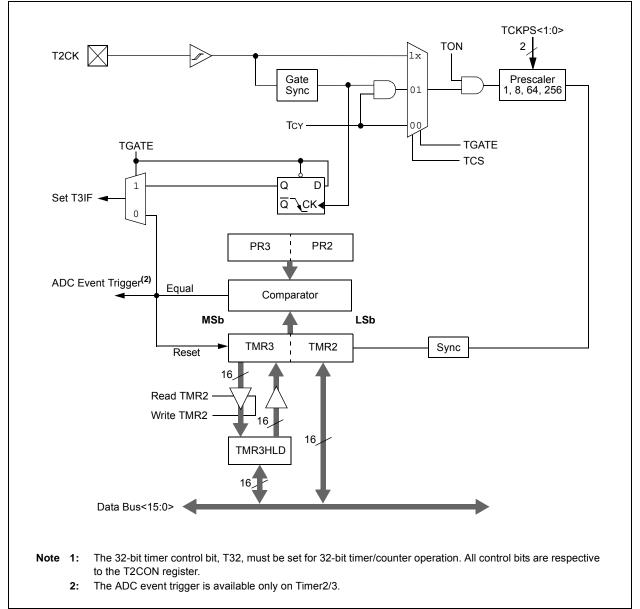

A block diagram for a 32-bit timer pair (Timer4/5) example is shown in Figure 13-1 and a timer (Timer4) operating in 16-bit mode example is shown in Figure 13-2.

**Note:** Only Timer2 and Timer3 can trigger a DMA data transfer.

NOTES:

| U-0                | U-0                        | U-0                               | R/W-0          | R/W-0                                  | R/W-0                                    | R/W-0              | R/W-0                |

|--------------------|----------------------------|-----------------------------------|----------------|----------------------------------------|------------------------------------------|--------------------|----------------------|

| _                  | —                          | _                                 | DISSCK         | DISSDO                                 | MODE16                                   | SMP                | CKE <sup>(1)</sup>   |

| bit 15             |                            |                                   |                |                                        |                                          |                    | bit                  |

| <b>D</b> 444 0     |                            |                                   | 5444.0         | 5444.0                                 | <b>D</b> # <b>M</b> / <b>O</b>           | 5444.0             |                      |

| R/W-0              |                            | R/W-0                             | R/W-0          | R/W-0                                  | R/W-0                                    | R/W-0              | R/W-0                |

| SSEN <sup>(3</sup> | <sup>3)</sup> CKP          | MSTEN                             |                | SPRE<2:0>(2                            | -)                                       | PPRE               | <1:0> <sup>(2)</sup> |

| bit 7              |                            |                                   |                |                                        |                                          |                    | bit                  |

| Legend:            |                            |                                   |                |                                        |                                          |                    |                      |

| R = Reada          | able bit                   | W = Writable                      | bit            | U = Unimpler                           | mented bit, read                         | as '0'             |                      |

| -n = Value         | at POR                     | '1' = Bit is set                  |                | '0' = Bit is cle                       | ared                                     | x = Bit is unkr    | nown                 |

|                    |                            | ind. Deed as i                    | 01             |                                        |                                          |                    |                      |

| bit 15-13          | -                          | ted: Read as '                    |                |                                        |                                          |                    |                      |

| bit 12             |                            | able SCKx pin<br>PI clock is disa |                | • •                                    |                                          |                    |                      |

|                    |                            | SPI clock is ena                  |                |                                        |                                          |                    |                      |

| bit 11             | DISSDO: Dis                | able SDOx pin                     | bit            |                                        |                                          |                    |                      |

|                    |                            |                                   |                | functions as I/C                       | )                                        |                    |                      |

|                    |                            | is controlled b                   | 5              |                                        |                                          |                    |                      |

| bit 10             |                            | ord/Byte Comm<br>ication is word- |                |                                        |                                          |                    |                      |

|                    |                            | ication is byte-                  |                |                                        |                                          |                    |                      |

| bit 9              | SMP: SPIx D                | ata Input Samp                    | ole Phase bit  |                                        |                                          |                    |                      |

|                    | Master mode                |                                   |                |                                        |                                          |                    |                      |

|                    |                            | a sampled at er<br>a sampled at m |                |                                        |                                          |                    |                      |

|                    | Slave mode:                | -                                 |                |                                        |                                          |                    |                      |

|                    |                            |                                   |                | in Slave mode.                         |                                          |                    |                      |

| bit 8              |                            | lock Edge Sele                    |                |                                        |                                          |                    |                      |

|                    |                            |                                   |                |                                        | clock state to Idl<br>ock state to activ |                    |                      |

| bit 7              |                            | Select Enable                     |                |                                        |                                          |                    | ,                    |

|                    | $1 = \overline{SSx}$ pin u | ised for Slave r                  | node           |                                        |                                          |                    |                      |

|                    | 0 = SSx pin n              | not used by mo                    | dule. Pin cont | rolled by port fu                      | unction                                  |                    |                      |

| bit 6              |                            | Polarity Select I                 |                |                                        |                                          |                    |                      |

|                    |                            |                                   |                | ve state is a lov<br>e state is a higl |                                          |                    |                      |

| bit 5              |                            | ter Mode Enab                     |                |                                        |                                          |                    |                      |

| bito               | 1 = Master m               |                                   |                |                                        |                                          |                    |                      |

|                    | 0 = Slave mo               | de                                |                |                                        |                                          |                    |                      |

| Note 1:            | The CKE bit is not         | used in the Fra                   | amed SPI mo    | des. The user s                        | should program                           | this bit to '0' fo | or the Frame         |

|                    | SPI modes (FRME            | EN = 1).                          |                |                                        |                                          |                    |                      |

| 2:                 | Do not set both Pr         | imary and Sec                     | ondary presca  | alers to a value                       | of 1:1.                                  |                    |                      |

- 2: Do not set both Primary and Secondary prescalers to a value of 1:1.

- 3: This bit must be cleared when FRMEN = 1.

### 17.0 INTER-INTEGRATED CIRCUIT™ (I<sup>2</sup>C™)

- Note 1: This data sheet summarizes the features of the PIC24HJXXXGPX06A/X08A/X10A family of devices. However, it is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to Section 19. "Inter-Integrated Circuit™ (I<sup>2</sup>C™)" (DS70195) of the "dsPIC33F/ PIC24H Family Reference Manual", which is available from the Microchip web site (www.microchip.com).

- Some registers and associated bits described in this section may not be available on all devices. Refer to Section 4.0 "Memory Organization" in this data sheet for device-specific register and bit information.

The Inter-Integrated Circuit ( $I^2C$ ) module provides complete hardware support for both Slave and Multi-Master modes of the  $I^2C$  serial communication standard, with a 16-bit interface.

The PIC24HJXXXGPX06A/X08A/X10A devices have up to two I<sup>2</sup>C interface modules, denoted as I2C1 and I2C2. Each I<sup>2</sup>C module has a 2-pin interface: the SCLx pin is clock and the SDAx pin is data.

Each  $I^2C$  module 'x' (x = 1 or 2) offers the following key features:

- I<sup>2</sup>C interface supporting both master and slave operation

- I<sup>2</sup>C Slave mode supports 7-bit and 10-bit addressing

- I<sup>2</sup>C Master mode supports 7-bit and 10-bit addressing

- I<sup>2</sup>C Port allows bidirectional transfers between master and slaves

- Serial clock synchronization for I<sup>2</sup>C port can be used as a handshake mechanism to suspend and resume serial transfer (SCLREL control)

- I<sup>2</sup>C supports multi-master operation; detects bus collision and will arbitrate accordingly

#### 17.1 Operating Modes

The hardware fully implements all the master and slave functions of the  $l^2C$  Standard and Fast mode specifications, as well as 7 and 10-bit addressing.

The  $I^2C$  module can operate either as a slave or a master on an  $I^2C$  bus.

The following types of I<sup>2</sup>C operation are supported:

- I<sup>2</sup>C slave operation with 7-bit addressing

- I<sup>2</sup>C slave operation with 10-bit addressing

- I<sup>2</sup>C master operation with 7-bit or 10-bit addressing

For details about the communication sequence in each of these modes, please refer to the *"dsPIC33F/PIC24H Family Reference Manual"*.

#### 19.0 ENHANCED CAN (ECAN™) MODULE

- Note 1: This data sheet summarizes the features of the PIC24HJXXXGPX06A/X08A/X10A family of devices. However, it is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to the *"dsPIC33F/PIC24H Family Reference Manual"*, Section 21. "Enhanced Controller Area Network (ECAN™)" (DS70185), which is available from the Microchip web site (www.microchip.com).

- 2: Some registers and associated bits described in this section may not be available on all devices. Refer to Section 4.0 "Memory Organization" in this data sheet for device-specific register and bit information.

#### 19.1 Overview

The Enhanced Controller Area Network (ECAN<sup>™</sup>) module is a serial interface, useful for communicating with other CAN modules or microcontroller devices. This interface/protocol was designed to allow communications within noisy environments. The PIC24HJXXXGPX06A/X08A/X10A devices contain up to two ECAN modules.

The CAN module is a communication controller implementing the CAN 2.0 A/B protocol, as defined in the BOSCH specification. The module will support CAN 1.2, CAN 2.0A, CAN 2.0B Passive and CAN 2.0B Active versions of the protocol. The module implementation is a full CAN system. The CAN specification is not covered within this data sheet. The reader may refer to the BOSCH CAN specification for further details.

The module features are as follows:

- Implementation of the CAN protocol, CAN 1.2, CAN 2.0A and CAN 2.0B

- · Standard and extended data frames

- 0-8 bytes data length

- Programmable bit rate up to 1 Mbit/sec

- Automatic response to remote transmission requests

- Up to 8 transmit buffers with application specified prioritization and abort capability (each buffer may contain up to 8 bytes of data)

- Up to 32 receive buffers (each buffer may contain up to 8 bytes of data)

- Up to 16 full (standard/extended identifier)

acceptance filters

- 3 full acceptance filter masks

- DeviceNet<sup>™</sup> addressing support

- Programmable wake-up functionality with integrated low-pass filter

- Programmable Loopback mode supports self-test operation

- Signaling via interrupt capabilities for all CAN receiver and transmitter error states

- Programmable clock source

- Programmable link to input capture module (IC2 for both CAN1 and CAN2) for time-stamping and network synchronization

- · Low-power Sleep and Idle mode

The CAN bus module consists of a protocol engine and message buffering/control. The CAN protocol engine handles all functions for receiving and transmitting messages on the CAN bus. Messages are transmitted by first loading the appropriate data registers. Status and errors can be checked by reading the appropriate registers. Any message detected on the CAN bus is checked for errors and then matched against filters to see if it should be received and stored in one of the receive registers.

#### 19.2 Frame Types

The CAN module transmits various types of frames which include data messages, remote transmission requests and as other frames that are automatically generated for control purposes. The following frame types are supported:

Standard Data Frame:

A standard data frame is generated by a node when the node wishes to transmit data. It includes an 11-bit standard identifier (SID) but not an 18-bit extended identifier (EID).

- Extended Data Frame: An extended data frame is similar to a standard data frame but includes an extended identifier as well.

- Remote Frame:

It is possible for a destination node to request the data from the source. For this purpose, the destination node sends a remote frame with an identifier that matches the identifier of the required data frame. The appropriate data source node will then send a data frame as a response to this remote request.

• Error Frame:

An error frame is generated by any node that detects a bus error. An error frame consists of two fields: an error flag field and an error delimiter field.

Overload Frame:

An overload frame can be generated by a node as a result of two conditions. First, the node detects a dominant bit during interframe space which is an illegal condition. Second, due to internal conditions, the node is not yet able to start reception of the next message. A node may generate a maximum of 2 sequential overload frames to delay the start of the next message.

· Interframe Space:

Interframe space separates a proceeding frame (of whatever type) from a following data or remote frame.

| U-0          | U-0                                                      | U-0                                  | U-0         | U-0              | U-0              | U-0             | U-0   |

|--------------|----------------------------------------------------------|--------------------------------------|-------------|------------------|------------------|-----------------|-------|

| _            | —                                                        | —                                    | _           | —                | —                | —               | _     |

| bit 15       |                                                          |                                      |             |                  |                  |                 | bit   |

| R/W-0        | R/W-0                                                    | R/W-0                                | R/W-0       | R/W-0            | R/W-0            | R/W-0           | R/W-0 |

|              | W<1:0>                                                   |                                      |             |                  | P<5:0>           |                 |       |

| bit 7        |                                                          |                                      |             |                  |                  |                 | bit   |

|              |                                                          |                                      |             |                  |                  |                 |       |

| Legend:      |                                                          |                                      |             |                  |                  |                 |       |

| R = Readab   |                                                          | W = Writable                         |             | •                | nented bit, read |                 |       |

| -n = Value a | t POR                                                    | '1' = Bit is set                     |             | '0' = Bit is cle | ared             | x = Bit is unki | nown  |

| bit 15-8     | Unimpleme                                                | nted: Read as '                      | o'          |                  |                  |                 |       |

| bit 7-6      | -                                                        | Synchronization                      |             | hite             |                  |                 |       |

|              | 11 = Length<br>10 = Length<br>01 = Length<br>00 = Length | is 4 x TQ<br>is 3 x TQ<br>is 2 x TQ  |             |                  |                  |                 |       |

| bit 5-0      | 0                                                        | Baud Rate Pres                       | scaler bits |                  |                  |                 |       |

|              | 11 1111 =                                                | Tq = 2 x 64 x 1/                     | FCAN        |                  |                  |                 |       |

|              | •                                                        |                                      |             |                  |                  |                 |       |

|              | •                                                        |                                      |             |                  |                  |                 |       |

|              | •                                                        |                                      |             |                  |                  |                 |       |

|              |                                                          | Tq = 2 x 3 x 1/F<br>Tq = 2 x 2 x 1/F |             |                  |                  |                 |       |

#### **REGISTER 19-9:** CiCFG1: ECAN™ MODULE BAUD RATE CONFIGURATION REGISTER 1

## 22.0 INSTRUCTION SET SUMMARY

**Note:** This data sheet summarizes the features of the PIC24HJXXXGPX06A/X08A/X10A families of devices. However, it is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to the related section in the "dsPIC33F/PIC24H Family Reference Manual", which is available from the Microchip web site (www.microchip.com).

The PIC24H instruction set is identical to that of the PIC24F, and is a subset of the dsPIC30F/33F instruction set.

Most instructions are a single program memory word (24 bits). Only three instructions require two program memory locations.

Each single-word instruction is a 24-bit word, divided into an 8-bit opcode, which specifies the instruction type and one or more operands, which further specify the operation of the instruction.

The instruction set is highly orthogonal and is grouped into five basic categories:

- · Word or byte-oriented operations

- · Bit-oriented operations

- · Literal operations

- DSP operations

- · Control operations

Table 22-1 shows the general symbols used in describing the instructions.

The PIC24H instruction set summary in Table 22-2 lists all the instructions, along with the status flags affected by each instruction.

Most word or byte-oriented W register instructions (including barrel shift instructions) have three operands:

- The first source operand which is typically a register 'Wb' without any address modifier

- The second source operand which is typically a register 'Ws' with or without an address modifier

- The destination of the result which is typically a register 'Wd' with or without an address modifier

However, word or byte-oriented file register instructions have two operands:

- · The file register specified by the value 'f'

- The destination, which could either be the file register 'f' or the W0 register, which is denoted as 'WREG'

Most bit-oriented instructions (including simple rotate/shift instructions) have two operands:

- The W register (with or without an address modifier) or file register (specified by the value of 'Ws' or 'f')

- The bit in the W register or file register (specified by a literal value or indirectly by the contents of register 'Wb')

The literal instructions that involve data movement may use some of the following operands:

- A literal value to be loaded into a W register or file register (specified by the value of 'k')

- The W register or file register where the literal value is to be loaded (specified by 'Wb' or 'f')

However, literal instructions that involve arithmetic or logical operations use some of the following operands:

- The first source operand which is a register 'Wb' without any address modifier

- The second source operand which is a literal value

- The destination of the result (only if not the same as the first source operand) which is typically a register 'Wd' with or without an address modifier

The control instructions may use some of the following operands:

- A program memory address

- The mode of the table read and table write instructions

All instructions are a single word, except for certain double word instructions, which were made double word instructions so that all the required information is available in these 48 bits. In the second word, the 8 MSbs are '0's. If this second word is executed as an instruction (by itself), it will execute as a NOP.

Most single-word instructions are executed in a single instruction cycle, unless a conditional test is true, or the program counter is changed as a result of the instruction. In these cases, the execution takes two instruction cycles with the additional instruction cycle(s) executed as a NOP. Notable exceptions are the BRA (unconditional/computed branch), indirect CALL/GOTO, all table reads and writes and RETURN/RETFIE instructions, which are single-word instructions but take two or three cycles. Certain instructions that involve skipping over the subsequent instruction require either two or three cycles if the skip is performed, depending on whether the instruction being skipped is a single-word or double word instruction. Moreover, double word moves require two cycles. The double word instructions execute in two instruction cycles.

Note: For more details on the instruction set, refer to the *"16-bit MCU and DSC Programmer's Reference Manual"* (DS70157).

#### Base Assembly # of # of Status Flags Instr Assembly Syntax Description Mnemonic Words Cycles Affected # 47 Relative Call RCALL RCALL 1 2 None Expr RCALL Computed Call 1 2 None Wn 48 REPEAT REPEAT #lit14 Repeat Next Instruction lit14 + 1 times 1 1 None REPEAT Repeat Next Instruction (Wn) + 1 times 1 1 None Wn 1 1 49 RESET RESET Software device Reset None 50 RETFIE RETFIE Return from interrupt 1 3 (2) None 51 RETLW #lit10,Wn Return with literal in Wn 1 3 (2) None RETLW 52 1 RETURN RETURN Return from Subroutine 3 (2) None 53 RLC RLC f = Rotate Left through Carry f 1 1 C,N,Z f RLC f,WREG WREG = Rotate Left through Carry f 1 1 C,N,Z RLC Ws,Wd Wd = Rotate Left through Carry Ws 1 1 C,N,Z 54 f = Rotate Left (No Carry) f 1 1 N,Z RLNC RUNC f 1 RLNC f,WREG WREG = Rotate Left (No Carry) f 1 N,Z RLNC Ws,Wd Wd = Rotate Left (No Carry) Ws 1 1 N,Z 55 RRC RRC f = Rotate Right through Carry f 1 1 C,N,Z f WREG = Rotate Right through Carry f 1 1 C,N,Z RRC f,WREG RRC Wd = Rotate Right through Carry Ws 1 1 C,N,Z Ws,Wd 56 RRNC RRNC f = Rotate Right (No Carry) f 1 1 N,Z f WREG = Rotate Right (No Carry) f 1 1 N,Z RRNC f,WREG Wd = Rotate Right (No Carry) Ws 1 1 N,Z RRNC Ws,Wd 1 C,N,Z 57 SE SE Ws,Wnd Wnd = sign-extended Ws 1 58 SETM SETM f f = 0xFFFF1 1 None WREG = 0xFFFF 1 1 SETM WREG None Ws = 0xFFFF 1 SETM Ws 1 None 59 SL SL f f = Left Shift f 1 1 C,N,OV,Z SL f,WREG WREG = Left Shift f 1 1 C,N,OV,Z Wd = Left Shift Ws 1 1 C,N,OV,Z SL Ws,Wd Wnd = Left Shift Wb by Wns 1 1 SL N.Z Wb, Wns, Wnd SL Wb,#lit5,Wnd Wnd = Left Shift Wb by lit5 1 1 N,Z 60 SUB SUB f = f – WREG 1 1 C,DC,N,OV,Z f WREG = f - WREG 1 1 C,DC,N,OV,Z SUB f,WREG Wn = Wn - lit10SUB #lit10,Wn 1 1 C,DC,N,OV,Z SUB Wb,Ws,Wd Wd = Wb - Ws1 1 C,DC,N,OV,Z Wd = Wb - lit5 1 1 C,DC,N,OV,Z SUB Wb,#lit5,Wd 61 SUBB $f = f - WREG - (\overline{C})$ C,DC,N,OV,Z 1 1 SUBB f WREG = $f - WREG - (\overline{C})$ 1 SUBB f,WREG 1 C,DC,N,OV,Z $Wn = Wn - lit10 - (\overline{C})$ 1 C,DC,N,OV,Z 1 SUBB #lit10,Wn SUBB $Wd = Wb - Ws - (\overline{C})$ 1 1 C,DC,N,OV,Z Wb,Ws,Wd SUBB Wb,#lit5,Wd $Wd = Wb - lit5 - (\overline{C})$ 1 1 C,DC,N,OV,Z 62 SUBR f = WREG - f 1 1 C,DC,N,OV,Z SUBR f WREG = WREG - f 1 1 C,DC,N,OV,Z SUBR f,WREG SUBR Wb,Ws,Wd Wd = Ws - Wb 1 1 C,DC,N,OV,Z Wd = lit5 - Wb1 1 C,DC,N,OV,Z SUBR Wb, #lit5, Wd 63 SUBBR $f = WREG - f - (\overline{C})$ 1 1 C,DC,N,OV,Z SUBBR f WREG = WREG - f - $(\overline{C})$ 1 SUBBR f,WREG 1 C,DC,N,OV,Z $Wd = Ws - Wb - (\overline{C})$ 1 1 C,DC,N,OV,Z SUBBR Wb.Ws.Wd $Wd = lit5 - Wb - (\overline{C})$ 1 C,DC,N,OV,Z SUBBR Wb,#lit5,Wd 1 64 1 SWAP SWAP.b Wn Wn = nibble swap Wn 1 None SWAP Wn = byte swap Wn 1 1 None Wn 1 2 65 Read Prog<23:16> to Wd<7:0> TBLRDH TBLRDH Ws,Wd None

#### TABLE 22-2: INSTRUCTION SET OVERVIEW (CONTINUED)

#### 23.7 MPLAB SIM Software Simulator

The MPLAB SIM Software Simulator allows code development in a PC-hosted environment by simulating the PIC MCUs and dsPIC<sup>®</sup> DSCs on an instruction level. On any given instruction, the data areas can be examined or modified and stimuli can be applied from a comprehensive stimulus controller. Registers can be logged to files for further run-time analysis. The trace buffer and logic analyzer display extend the power of the simulator to record and track program execution, actions on I/O, most peripherals and internal registers.

The MPLAB SIM Software Simulator fully supports symbolic debugging using the MPLAB C Compilers, and the MPASM and MPLAB Assemblers. The software simulator offers the flexibility to develop and debug code outside of the hardware laboratory environment, making it an excellent, economical software development tool.

#### 23.8 MPLAB REAL ICE In-Circuit Emulator System

MPLAB REAL ICE In-Circuit Emulator System is Microchip's next generation high-speed emulator for Microchip Flash DSC and MCU devices. It debugs and programs PIC<sup>®</sup> Flash MCUs and dsPIC<sup>®</sup> Flash DSCs with the easy-to-use, powerful graphical user interface of the MPLAB Integrated Development Environment (IDE), included with each kit.

The emulator is connected to the design engineer's PC using a high-speed USB 2.0 interface and is connected to the target with either a connector compatible with incircuit debugger systems (RJ11) or with the new high-speed, noise tolerant, Low-Voltage Differential Signal (LVDS) interconnection (CAT5).

The emulator is field upgradable through future firmware downloads in MPLAB IDE. In upcoming releases of MPLAB IDE, new devices will be supported, and new features will be added. MPLAB REAL ICE offers significant advantages over competitive emulators including low-cost, full-speed emulation, run-time variable watches, trace analysis, complex breakpoints, a ruggedized probe interface and long (up to three meters) interconnection cables.

#### 23.9 MPLAB ICD 3 In-Circuit Debugger System

MPLAB ICD 3 In-Circuit Debugger System is Microchip's most cost effective high-speed hardware debugger/programmer for Microchip Flash Digital Signal Controller (DSC) and microcontroller (MCU) devices. It debugs and programs PIC<sup>®</sup> Flash microcontrollers and dsPIC<sup>®</sup> DSCs with the powerful, yet easyto-use graphical user interface of MPLAB Integrated Development Environment (IDE).

The MPLAB ICD 3 In-Circuit Debugger probe is connected to the design engineer's PC using a high-speed USB 2.0 interface and is connected to the target with a connector compatible with the MPLAB ICD 2 or MPLAB REAL ICE systems (RJ-11). MPLAB ICD 3 supports all MPLAB ICD 2 headers.

#### 23.10 PICkit 3 In-Circuit Debugger/ Programmer and PICkit 3 Debug Express

The MPLAB PICkit 3 allows debugging and programming of PIC<sup>®</sup> and dsPIC<sup>®</sup> Flash microcontrollers at a most affordable price point using the powerful graphical user interface of the MPLAB Integrated Development Environment (IDE). The MPLAB PICkit 3 is connected to the design engineer's PC using a full speed USB interface and can be connected to the target via an Microchip debug (RJ-11) connector (compatible with MPLAB ICD 3 and MPLAB REAL ICE). The connector uses two device I/O pins and the reset line to implement in-circuit debugging and In-Circuit Serial Programming<sup>™</sup>.

The PICkit 3 Debug Express include the PICkit 3, demo board and microcontroller, hookup cables and CDROM with user's guide, lessons, tutorial, compiler and MPLAB IDE software.

NOTES:

#### F

| •                                                  |

|----------------------------------------------------|

| Flash Program Memory59                             |

| Control Registers60                                |

| Operations60                                       |

| Programming Algorithm62                            |

| RTSP Operation60                                   |

| Table Instructions59                               |

| Flexible Configuration                             |

| FSCM                                               |

| Delay for Crystal and PLL Clock Sources            |

| Device Resets                                      |

| н                                                  |

| High Temperature Electrical Characteristics        |

|                                                    |

|                                                    |

| I/O Ports                                          |

| Parallel I/O (PIO)141                              |

| Write/Read Timing                                  |

| l <sup>2</sup> C                                   |

| Operating Modes                                    |

| Registers                                          |

| I <sup>2</sup> C Module                            |

| I2C1 Register Map                                  |

| I2C2 Register Map                                  |

| In-Circuit Debugger                                |

| In-Circuit Emulation                               |

| In-Circuit Serial Programming (ICSP)               |

| Input Capture                                      |

| Registers                                          |

| Input Change Notification Module                   |

| Instruction Addressing Modes                       |

| File Register Instructions                         |

| Fundamental Modes Supported                        |

| MCU Instructions                                   |

| Move and Accumulator Instructions                  |

| Other Instructions                                 |

| Instruction Set                                    |

| Overview                                           |

| Summary                                            |

| Instruction-Based Power-Saving Modes               |

| Idle                                               |

| Sleep                                              |

| Internal RC Oscillator                             |

| Use with WDT                                       |

| Internet Address                                   |

| Interrupt Control and Status Registers             |

| IECx                                               |

| IFSx                                               |

| INTCON1                                            |

| INTCON2                                            |

| INTTREG                                            |

| IPCx                                               |

| Interrupt Setup Procedures                         |

| Initialization                                     |

| Interrupt Disable                                  |

| Interrupt Disable                                  |

| Trap Service Routine                               |

| Interrupt Vector Table (IVT)                       |

| Interrupts Coincident with Power Save Instructions |

| interrupto confedent with rower dave instructions  |

| J                                                  |

| JTAG Boundary Scan Interface                       |

| · · · · · · · · · · · · · · · · · · ·              |

#### Μ

| Memory Organization                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| Modes of Operation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| Disable                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |