Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFI

| Details                    |                                                                                |

|----------------------------|--------------------------------------------------------------------------------|

| Product Status             | Active                                                                         |

| Core Processor             | PIC                                                                            |

| Core Size                  | 16-Bit                                                                         |

| Speed                      | 40 MIPs                                                                        |

| Connectivity               | I²C, IrDA, LINbus, SPI, UART/USART                                             |

| Peripherals                | Brown-out Detect/Reset, DMA, POR, PWM, WDT                                     |

| Number of I/O              | 53                                                                             |

| Program Memory Size        | 64KB (22K x 24)                                                                |

| Program Memory Type        | FLASH                                                                          |

| EEPROM Size                | -                                                                              |

| RAM Size                   | 8K x 8                                                                         |

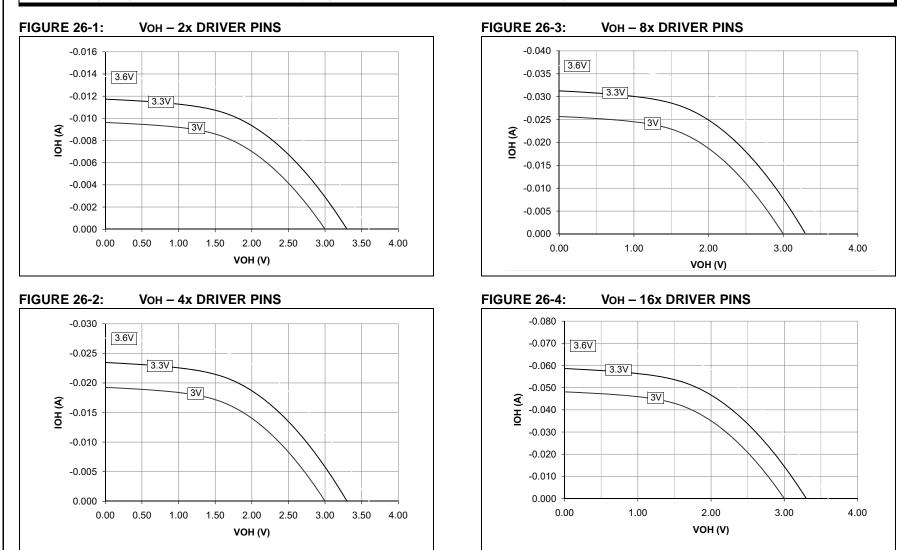

| Voltage - Supply (Vcc/Vdd) | 3V ~ 3.6V                                                                      |

| Data Converters            | A/D 18x10b/12b                                                                 |

| Oscillator Type            | Internal                                                                       |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                              |

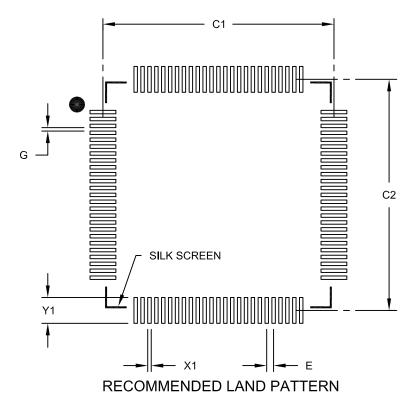

| Mounting Type              | Surface Mount                                                                  |

| Package / Case             | 64-VFQFN Exposed Pad                                                           |

| Supplier Device Package    | 64-VQFN (9x9)                                                                  |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic24hj64gp206a-i-mr |

|                            |                                                                                |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

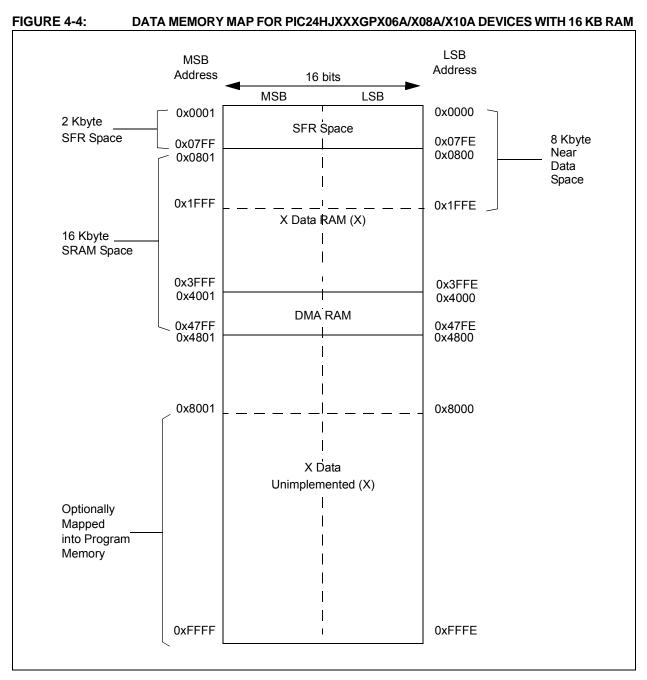

### 4.2.5 DMA RAM

Every PIC24HJXXXGPX06A/X08A/X10A device contains 2 Kbytes of dual ported DMA RAM located at the end of data space. Memory locations in the DMA RAM space are accessible simultaneously by the CPU and the DMA controller module. DMA RAM is utilized by the DMA controller to store data to be transferred to various peripherals using DMA, as well as data transferred from various peripherals using DMA. The DMA RAM can be accessed by the DMA controller without having to steal cycles from the CPU.

When the CPU and the DMA controller attempt to concurrently write to the same DMA RAM location, the hardware ensures that the CPU is given precedence in accessing the DMA RAM location. Therefore, the DMA RAM provides a reliable means of transferring DMA data without ever having to stall the CPU.

Note: DMA RAM can be used for general purpose data storage if the DMA function is not required in an application.

| SFR Name | SFR<br>Addr | Bit 15 | Bit 14                 | Bit 13 | Bit 12 | Bit 11 | Bit 10 | Bit 9   | Bit 8         | Bit 7        | Bit 6     | Bit 5     | Bit 4        | Bit 3        | Bit 2        | Bit 1   | Bit 0  | All<br>Resets |

|----------|-------------|--------|------------------------|--------|--------|--------|--------|---------|---------------|--------------|-----------|-----------|--------------|--------------|--------------|---------|--------|---------------|

| WREG0    | 0000        |        |                        | •      |        |        | •      |         | Working Re    | gister 0     | •         |           | •            |              | •            |         | •      | xxxx          |

| WREG1    | 0002        |        |                        |        |        |        |        |         | Working Re    | gister 1     |           |           |              |              |              |         |        | xxxx          |

| WREG2    | 0004        |        |                        |        |        |        |        |         | Working Re    | gister 2     |           |           |              |              |              |         |        | xxxx          |

| WREG3    | 0006        |        |                        |        |        |        |        |         | Working Re    | gister 3     |           |           |              |              |              |         |        | xxxx          |

| WREG4    | 8000        |        | Working Register 4     |        |        |        |        |         |               |              |           | xxxx      |              |              |              |         |        |               |

| WREG5    | 000A        |        | Working Register 5     |        |        |        |        |         |               |              |           | XXXX      |              |              |              |         |        |               |

| WREG6    | 000C        |        | Working Register 6     |        |        |        |        |         |               |              |           | xxxx      |              |              |              |         |        |               |

| WREG7    | 000E        |        | Working Register 7     |        |        |        |        |         |               |              |           | XXXX      |              |              |              |         |        |               |

| WREG8    | 0010        |        | Working Register 8     |        |        |        |        |         |               |              |           | xxxx      |              |              |              |         |        |               |

| WREG9    | 0012        |        | Working Register 9     |        |        |        |        |         |               |              |           | xxxx      |              |              |              |         |        |               |

| WREG10   | 0014        |        | Working Register 10 2  |        |        |        |        |         |               |              |           | xxxx      |              |              |              |         |        |               |

| WREG11   | 0016        |        | Working Register 11 xx |        |        |        |        |         |               |              |           | xxxx      |              |              |              |         |        |               |

| WREG12   | 0018        |        | Working Register 12    |        |        |        |        |         |               |              |           | xxxx      |              |              |              |         |        |               |

| WREG13   | 001A        |        |                        |        |        |        |        |         | Working Ree   | gister 13    |           |           |              |              |              |         |        | xxxx          |

| WREG14   | 001C        |        |                        |        |        |        |        |         | Working Ree   | gister 14    |           |           |              |              |              |         |        | xxxx          |

| WREG15   | 001E        |        |                        |        |        |        |        |         | Working Ree   | gister 15    |           |           |              |              |              |         |        | 0800          |

| SPLIM    | 0020        |        |                        |        |        |        |        | Sta     | ck Pointer Li | mit Register | •         |           |              |              |              |         |        | xxxx          |

| PCL      | 002E        |        |                        |        |        |        |        | Program | n Counter Lo  | w Word Reg   | gister    |           |              |              |              |         |        | 0000          |

| PCH      | 0030        | —      | _                      | —      | —      | —      | —      | —       | —             |              |           | Progra    | m Counter    | High Byte F  | Register     |         |        | 0000          |

| TBLPAG   | 0032        | —      | _                      | —      | —      | —      | —      | —       | —             |              |           |           | · ·          | ss Pointer F | <b>.</b>     |         |        | 0000          |

| PSVPAG   | 0034        |        | —                      | —      | —      | —      | —      |         | —             |              | •         | am Memory | Visibility P | age Addres   | s Pointer Re | egister |        | 0000          |

| RCOUNT   | 0036        |        |                        |        |        |        |        | Repe    | eat Loop Cou  | inter Regist |           |           | 1            | 1            | I.           |         | •      | xxxx          |

| SR       | 0042        | _      | _                      |        | _      | _      | —      | —       | DC            |              | IPL<2:0>  |           | RA           | N            | OV           | Z       | С      | 0000          |

| CORCON   | 0044        | —      | _                      | —      | —      | —      | —      | —       | —             | —            | —         | —         | —            | IPL3         | PSV          | —       | —      | 0000          |

| DISICNT  | 0052        | _      | _                      |        |        |        |        |         | Disable       | e Interrupts | Counter R | egister   |              |              |              |         | 1      | xxxx          |

| BSRAM    | 0750        |        | —                      | —      | —      | —      | —      | —       | —             | —            | —         | _         | —            |              | IW_BSR       | IR_BSR  | RL_BSR | 0000          |

| SSRAM    | 0752        |        | —                      | —      | —      | —      | —      | —       | -             | —            | -         | —         | —            | —            | IW_SSR       | IR_SSR  | RL_SSR | 0000          |

### TABLE 4-1: CPU CORE REGISTERS MAP

Legend: x = unknown value on Reset, — = unimplemented, read as '0'. Reset values are shown in hexadecimal for PinHigh devices.

| R/W-0         | R/W-0                                            | R/W-1              | R/W-1         | R/W-0                | R/W-0           | R/W-0              | R/W-0      |  |  |  |  |

|---------------|--------------------------------------------------|--------------------|---------------|----------------------|-----------------|--------------------|------------|--|--|--|--|

| ROI           |                                                  | DOZE<2:0>          |               | DOZEN <sup>(1)</sup> |                 | FRCDIV<2:0>        |            |  |  |  |  |

| bit 15        |                                                  |                    |               | <u> </u>             |                 |                    | bit 8      |  |  |  |  |

|               |                                                  |                    |               |                      |                 |                    |            |  |  |  |  |

| R/W-0         | R/W-1                                            | U-0                | R/W-0         | R/W-0                | R/W-0           | R/W-0              | R/W-0      |  |  |  |  |

| PLLPC         | ST<1:0>                                          | —                  |               |                      | PLLPRE<4:0>     | >                  |            |  |  |  |  |

| bit 7         |                                                  |                    |               |                      |                 |                    | bit (      |  |  |  |  |

|               |                                                  |                    |               |                      |                 |                    |            |  |  |  |  |

| Legend:       |                                                  | y = Value set      | from Configu  | ration bits on PC    | R               |                    |            |  |  |  |  |

| R = Readable  | e bit                                            | W = Writable       | bit           | U = Unimplem         | ented bit, read | 1 as '0'           |            |  |  |  |  |

| -n = Value at | POR                                              | '1' = Bit is set   |               | '0' = Bit is clea    | ired            | x = Bit is unkr    | iown       |  |  |  |  |

|               |                                                  |                    |               |                      |                 |                    |            |  |  |  |  |

| bit 15        |                                                  | er on Interrupt bi |               |                      |                 |                    |            |  |  |  |  |

|               |                                                  |                    |               | nd the processor     | clock/periphe   | ral clock ratio is | set to 1:1 |  |  |  |  |

|               | •                                                | ts have no effec   |               |                      |                 |                    |            |  |  |  |  |

| bit 14-12     |                                                  | Processor Clo      | ck Reduction  | Select bits          |                 |                    |            |  |  |  |  |

|               | 111 = FCY/12                                     | -                  |               |                      |                 |                    |            |  |  |  |  |

|               | 110 = FCY/64<br>101 = FCY/32                     |                    |               |                      |                 |                    |            |  |  |  |  |

|               | 100 = FCY/10                                     |                    |               |                      |                 |                    |            |  |  |  |  |

|               | 011 = FCY/8                                      |                    |               |                      |                 |                    |            |  |  |  |  |

|               | 010 = Fcy/4                                      | . ,                |               |                      |                 |                    |            |  |  |  |  |

|               | 001 = FCY/2                                      |                    |               |                      |                 |                    |            |  |  |  |  |

|               | 000 = Fcy/1                                      |                    | (4)           |                      |                 |                    |            |  |  |  |  |

| bit 11        |                                                  | ZE Mode Enabl      |               |                      |                 |                    |            |  |  |  |  |

|               |                                                  |                    |               | etween the perip     | oheral clocks a | and the process    | or clocks  |  |  |  |  |

|               |                                                  | or clock/periphe   |               |                      |                 |                    |            |  |  |  |  |

| bit 10-8      |                                                  |                    | RC Oscillato  | r Postscaler bits    |                 |                    |            |  |  |  |  |

|               | 111 = FRC c                                      |                    |               |                      |                 |                    |            |  |  |  |  |

|               | 110 = FRC divide by 64<br>101 = FRC divide by 32 |                    |               |                      |                 |                    |            |  |  |  |  |

|               | 100 = FRC c                                      |                    |               |                      |                 |                    |            |  |  |  |  |

|               | 011 <b>= FRC c</b>                               |                    |               |                      |                 |                    |            |  |  |  |  |

|               | 010 <b>= FRC c</b>                               |                    |               |                      |                 |                    |            |  |  |  |  |

|               | 001 = FRC c                                      |                    |               |                      |                 |                    |            |  |  |  |  |

|               |                                                  | livide by 1 (defa  |               |                      |                 |                    |            |  |  |  |  |

| bit 7-6       |                                                  |                    | Output Divide | er Select bits (als  | o denoted as    | 'N2', PLL posts    | caler)     |  |  |  |  |

|               | 11 = Output/<br>10 = Reserve                     |                    |               |                      |                 |                    |            |  |  |  |  |

|               | 01 = Output/                                     |                    |               |                      |                 |                    |            |  |  |  |  |

|               | 00 = Output/                                     | . ,                |               |                      |                 |                    |            |  |  |  |  |

| bit 5         | •                                                | nted: Read as '    | 0'            |                      |                 |                    |            |  |  |  |  |

| bit 4-0       | =                                                |                    |               | t Divider bits (als  | so denoted as   | 'N1'. PLL preso    | aler)      |  |  |  |  |

|               | 11111 <b>= Inp</b>                               |                    |               |                      |                 | , 1                | ,          |  |  |  |  |

|               | •                                                |                    |               |                      |                 |                    |            |  |  |  |  |

|               |                                                  |                    |               |                      |                 |                    |            |  |  |  |  |

|               | •                                                |                    |               |                      |                 |                    |            |  |  |  |  |

|               | •<br>00001 = Inp                                 | ut/3               |               |                      |                 |                    |            |  |  |  |  |

### REGISTER 9-2: CLKDIV: CLOCK DIVISOR REGISTER<sup>(2)</sup>

- Note 1: This bit is cleared when the ROI bit is set and an interrupt occurs.

- **2:** This register is reset only on a Power-on Reset (POR).

### **REGISTER 15-1:** OCxCON: OUTPUT COMPARE x CONTROL REGISTER (x = 1, 2)

| U-0    | U-0 | R/W-0  | U-0     | U-0    | U-0   | U-0      | U-0   |

|--------|-----|--------|---------|--------|-------|----------|-------|

| _      | —   | OCSIDL |         | —      | —     | —        | —     |

| bit 15 |     |        | •       |        |       |          | bit 8 |

|        |     |        |         |        |       |          |       |

| U-0    | U-0 | U-0    | R-0, HC | R/W-0  | R/W-0 | R/W-0    | R/W-0 |

|        | —   | —      | OCFLT   | OCTSEL |       | OCM<2:0> |       |

| bit 7  |     |        | •       |        |       |          | bit 0 |

|        |     |        |         |        |       |          |       |

| Legend:           | HC = Hardware Clearable bit |                                    |                    |  |  |

|-------------------|-----------------------------|------------------------------------|--------------------|--|--|

| R = Readable bit  | W = Writable bit            | U = Unimplemented bit, read as '0' |                    |  |  |

| -n = Value at POR | '1' = Bit is set            | '0' = Bit is cleared               | x = Bit is unknown |  |  |

| bit 15-14 | Unimplemented: Read as '0'                                                          |

|-----------|-------------------------------------------------------------------------------------|

| bit 13    | OCSIDL: Stop Output Compare in Idle Mode Control bit                                |

|           | 1 = Output Compare x halts in CPU Idle mode                                         |

|           | 0 = Output Compare x continues to operate in CPU Idle mode                          |

| bit 12-5  | Unimplemented: Read as '0'                                                          |

| bit 4     | OCFLT: PWM Fault Condition Status bit                                               |

|           | 1 = PWM Fault condition has occurred (cleared in hardware only)                     |

|           | 0 = No PWM Fault condition has occurred (this bit is only used when OCM<2:0> = 111) |

| bit 3     | OCTSEL: Output Compare Timer Select bit                                             |

|           | 1 = Timer3 is the clock source for Compare x                                        |

|           | 0 = Timer2 is the clock source for Compare x                                        |

| bit 2-0   | OCM<2:0>: Output Compare Mode Select bits                                           |

|           | 111 = PWM mode on OCx, Fault pin enabled                                            |

|           | 110 = PWM mode on OCx, Fault pin disabled                                           |

|           | 101 = Initialize OCx pin low, generate continuous output pulses on OCx pin          |

|           | 100 = Initialize OCx pin low, generate single output pulse on OCx pin               |

|           | 011 = Compare event toggles OCx pin                                                 |

|           | 010 = Initialize OCx pin high, compare event forces OCx pin low                     |

|           | 001 = Initialize OCx pin low, compare event forces OCx pin high                     |

|           | 000 = Output compare channel is disabled                                            |

### REGISTER 18-2: UxSTA: UARTx STATUS AND CONTROL REGISTER (CONTINUED)

| bit 5 | ADDEN: Address Character Detect bit (bit 8 of received data = 1)                                                                                                            |

|-------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|       | <ul> <li>1 = Address Detect mode enabled. If 9-bit mode is not selected, this does not take effect</li> <li>0 = Address Detect mode disabled</li> </ul>                     |

| bit 4 | RIDLE: Receiver Idle bit (read-only)                                                                                                                                        |

|       | <ul><li>1 = Receiver is Idle</li><li>0 = Receiver is active</li></ul>                                                                                                       |

| bit 3 | PERR: Parity Error Status bit (read-only)                                                                                                                                   |

|       | <ul> <li>1 = Parity error has been detected for the current character (character at the top of the receive FIFO)</li> <li>0 = Parity error has not been detected</li> </ul> |

| bit 2 | FERR: Framing Error Status bit (read-only)                                                                                                                                  |

|       | 1 = Framing error has been detected for the current character (character at the top of the receive FIFO)                                                                    |

|       | 0 = Framing error has not been detected                                                                                                                                     |

| bit 1 | OERR: Receive Buffer Overrun Error Status bit (read/clear only)                                                                                                             |

|       | 1 = Receive buffer has overflowed                                                                                                                                           |

|       | 0 = Receive buffer has not overflowed. Clearing a previously set OERR bit (1 $\rightarrow$ 0 transition) will reset<br>the receiver buffer and the UxRSR to the empty state |

| bit 0 | URXDA: Receive Buffer Data Available bit (read-only)                                                                                                                        |

|       | <ul> <li>1 = Receive buffer has data, at least one more character can be read</li> <li>0 = Receive buffer is empty</li> </ul>                                               |

|       |                                                                                                                                                                             |

**Note 1:** Refer to **Section 17. "UART**" (DS70188) in the *"dsPIC33F/PIC24H Family Reference Manual"* for information on enabling the UART module for transmit operation.

| U-0           | U-0                                                                                         | R-0                                                                                        | R-0         | R-0              | R-0             | R-0             | R-0   |  |  |  |  |  |  |

|---------------|---------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------|-------------|------------------|-----------------|-----------------|-------|--|--|--|--|--|--|

|               |                                                                                             | ТХВО                                                                                       | TXBP        | RXBP             | TXWAR           | RXWAR           | EWARN |  |  |  |  |  |  |

| bit 15        |                                                                                             |                                                                                            |             |                  |                 |                 | bit 8 |  |  |  |  |  |  |

|               |                                                                                             |                                                                                            |             |                  |                 |                 |       |  |  |  |  |  |  |

| R/C-0         | R/C-0                                                                                       | R/C-0                                                                                      | U-0         | R/C-0            | R/C-0           | R/C-0           | R/C-0 |  |  |  |  |  |  |

| IVRIF         | WAKIF                                                                                       | ERRIF                                                                                      |             | FIFOIF           | RBOVIF          | RBIF            | TBIF  |  |  |  |  |  |  |

| bit 7         |                                                                                             |                                                                                            |             |                  |                 |                 | bit ( |  |  |  |  |  |  |

|               |                                                                                             |                                                                                            |             |                  |                 |                 |       |  |  |  |  |  |  |

| Legend:       |                                                                                             | C = Clear on                                                                               | y bit       |                  |                 |                 |       |  |  |  |  |  |  |

| R = Readable  | e bit                                                                                       | W = Writable                                                                               | bit         | U = Unimplei     | mented bit, rea | d as '0'        |       |  |  |  |  |  |  |

| -n = Value at | POR                                                                                         | '1' = Bit is set                                                                           | t           | '0' = Bit is cle | eared           | x = Bit is unkr | nown  |  |  |  |  |  |  |

| bit 15-14     | Unimplomon                                                                                  | ted. Dood oo '                                                                             | 0'          |                  |                 |                 |       |  |  |  |  |  |  |

| bit 13        | -                                                                                           | i <b>ted:</b> Read as '<br>mitter in Error                                                 |             | hit              |                 |                 |       |  |  |  |  |  |  |

| bit 15        |                                                                                             | er is in Bus Of                                                                            |             | bit              |                 |                 |       |  |  |  |  |  |  |

|               | 0 = Transmitt                                                                               | er is not in Bus                                                                           | s Off state |                  |                 |                 |       |  |  |  |  |  |  |

| bit 12        |                                                                                             | mitter in Error                                                                            |             | sive bit         |                 |                 |       |  |  |  |  |  |  |

|               |                                                                                             | er is in Bus Pa                                                                            |             | _                |                 |                 |       |  |  |  |  |  |  |

| bit 11        |                                                                                             | er is not in Bus<br>ver in Error Sta                                                       |             |                  |                 |                 |       |  |  |  |  |  |  |

|               |                                                                                             | is in Bus Pass                                                                             |             | vebil            |                 |                 |       |  |  |  |  |  |  |

|               | 0 = Receiver is not in Bus Passive state                                                    |                                                                                            |             |                  |                 |                 |       |  |  |  |  |  |  |

| bit 10        |                                                                                             | XWAR: Transmitter in Error State Warning bit                                               |             |                  |                 |                 |       |  |  |  |  |  |  |

|               |                                                                                             | 1 = Transmitter is in Error Warning state<br>0 = Transmitter is not in Error Warning state |             |                  |                 |                 |       |  |  |  |  |  |  |

| bit 9         |                                                                                             |                                                                                            | -           |                  |                 |                 |       |  |  |  |  |  |  |

| DIL 9         | <b>RXWAR:</b> Receiver in Error State Warning bit<br>1 = Receiver is in Error Warning state |                                                                                            |             |                  |                 |                 |       |  |  |  |  |  |  |

|               | 0 = Receiver is not in Error Warning state                                                  |                                                                                            |             |                  |                 |                 |       |  |  |  |  |  |  |

| bit 8         | EWARN: Transmitter or Receiver in Error State Warning bit                                   |                                                                                            |             |                  |                 |                 |       |  |  |  |  |  |  |

|               |                                                                                             | er or receiver i                                                                           |             | 0                |                 |                 |       |  |  |  |  |  |  |

| <b>b</b> # 7  |                                                                                             | er or receiver i                                                                           |             | •                |                 |                 |       |  |  |  |  |  |  |

| bit 7         | IVRIF: Invalid Message Received Interrupt Flag bit<br>1 = Interrupt request has occurred    |                                                                                            |             |                  |                 |                 |       |  |  |  |  |  |  |

|               | 0 = Interrupt request has not occurred                                                      |                                                                                            |             |                  |                 |                 |       |  |  |  |  |  |  |

| bit 6         | WAKIF: Bus Wake-up Activity Interrupt Flag bit                                              |                                                                                            |             |                  |                 |                 |       |  |  |  |  |  |  |

|               |                                                                                             | 1 = Interrupt request has occurred                                                         |             |                  |                 |                 |       |  |  |  |  |  |  |

| 64 F          | •                                                                                           | request has no                                                                             |             |                  |                 | h =)            |       |  |  |  |  |  |  |

| bit 5         |                                                                                             |                                                                                            |             | ources in Clin   | F<13:8> regist  | (er)            |       |  |  |  |  |  |  |

|               |                                                                                             | request has oc<br>request has no                                                           |             |                  |                 |                 |       |  |  |  |  |  |  |

| bit 4         | •                                                                                           | ted: Read as '                                                                             |             |                  |                 |                 |       |  |  |  |  |  |  |

| bit 3         | •                                                                                           | Almost Full In                                                                             |             | it               |                 |                 |       |  |  |  |  |  |  |

|               | 1 = Interrupt i                                                                             | request has oc                                                                             | curred      |                  |                 |                 |       |  |  |  |  |  |  |

|               |                                                                                             | request has no                                                                             |             |                  |                 |                 |       |  |  |  |  |  |  |

| bit 2         |                                                                                             | Buffer Overflo                                                                             | •           | ag bit           |                 |                 |       |  |  |  |  |  |  |

|               |                                                                                             | request has oc<br>request has no                                                           |             |                  |                 |                 |       |  |  |  |  |  |  |

| bit 1         |                                                                                             | ffer Interrupt F                                                                           |             |                  |                 |                 |       |  |  |  |  |  |  |

|               |                                                                                             | request has oc                                                                             |             |                  |                 |                 |       |  |  |  |  |  |  |

|               |                                                                                             | request has no                                                                             |             |                  |                 |                 |       |  |  |  |  |  |  |

| 1.1.0         | TDIE. TV Duf                                                                                |                                                                                            |             |                  |                 |                 |       |  |  |  |  |  |  |

| bit 0         |                                                                                             | fer Interrupt Fla                                                                          |             |                  |                 |                 |       |  |  |  |  |  |  |

| DIT U         | 1 = Interrupt i                                                                             | request has oc<br>request has no                                                           | curred      |                  |                 |                 |       |  |  |  |  |  |  |

| R/W-x                             | R/W-x                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | R/W-x                                                  | R/W-x            | R/W-x             | R/W-x           | R/W-x           | R/W-x |  |  |  |  |

|-----------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------|------------------|-------------------|-----------------|-----------------|-------|--|--|--|--|

|                                   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                                                        |                  | :10:3>            |                 |                 |       |  |  |  |  |

| bit 15                            |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                                                        |                  |                   |                 |                 | bit   |  |  |  |  |

| R/W-x                             | R/W-x                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | R/W-x                                                  | U-0              | R/W-x             | U-0             | R/W-x           | R/W-x |  |  |  |  |

|                                   | SID<2:0>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                                                        | _                | EXIDE             | _               | EID<1           | 7:16> |  |  |  |  |

| bit 7                             |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                                                        |                  |                   |                 |                 | bit ( |  |  |  |  |

|                                   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                                                        |                  |                   |                 |                 |       |  |  |  |  |

| Legend:                           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                                                        |                  |                   |                 |                 |       |  |  |  |  |

| R = Readable bit W = Writable bit |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                                                        |                  | U = Unimplem      | ented bit, read | l as '0'        |       |  |  |  |  |

| -n = Value at POR '1' = Bit is s  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                                                        |                  | '0' = Bit is clea | ared            | x = Bit is unkn | iown  |  |  |  |  |

| bit 15-5                          | 1 = Message                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | Standard Identif<br>address bit SII<br>address bit SII | Dx must be '1    |                   |                 |                 |       |  |  |  |  |

| bit 4                             | Unimplemer                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | ted: Read as '                                         | 0'               |                   |                 |                 |       |  |  |  |  |

| bit 3                             |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | nded Identifier                                        | Enable bit       |                   |                 |                 |       |  |  |  |  |

|                                   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | <u>If MIDE = 1:</u>                                    |                  |                   |                 |                 |       |  |  |  |  |

|                                   | <ul> <li>1 = Match only messages with extended identifier addresses</li> <li>0 = Match only messages with standard identifier addresses</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                                                        |                  |                   |                 |                 |       |  |  |  |  |