Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFI

| Details                    |                                                                                 |

|----------------------------|---------------------------------------------------------------------------------|

| Product Status             | Active                                                                          |

| Core Processor             | PIC                                                                             |

| Core Size                  | 16-Bit                                                                          |

| Speed                      | 40 MIPs                                                                         |

| Connectivity               | I <sup>2</sup> C, IrDA, LINbus, SPI, UART/USART                                 |

| Peripherals                | Brown-out Detect/Reset, DMA, POR, PWM, WDT                                      |

| Number of I/O              | 53                                                                              |

| Program Memory Size        | 64KB (22K x 24)                                                                 |

| Program Memory Type        | FLASH                                                                           |

| EEPROM Size                | · ·                                                                             |

| RAM Size                   | 8K x 8                                                                          |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 3.6V                                                                       |

| Data Converters            | A/D 18x10b/12b                                                                  |

| Oscillator Type            | Internal                                                                        |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                               |

| Mounting Type              | Surface Mount                                                                   |

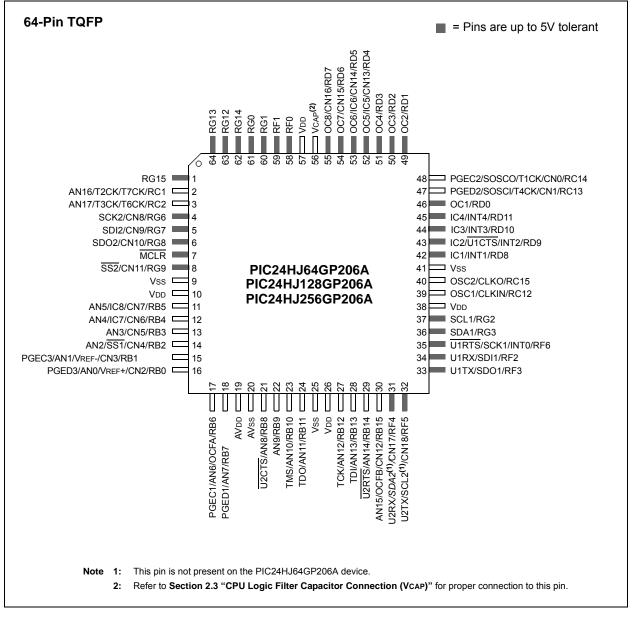

| Package / Case             | 64-TQFP                                                                         |

| Supplier Device Package    | 64-TQFP (10x10)                                                                 |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic24hj64gp206at-i-pt |

|                            |                                                                                 |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

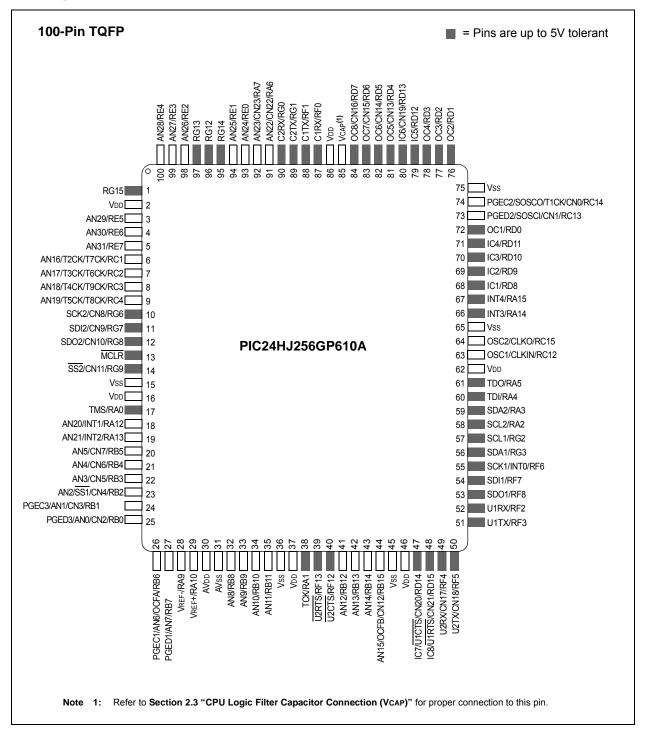

### Pin Diagrams (Continued)

#### Pin Diagrams (Continued)

© 2009-2012 Microchip Technology Inc.

### 3.4 Arithmetic Logic Unit (ALU)

The PIC24HJXXXGPX06A/X08A/X10A ALU is 16 bits wide and is capable of addition, subtraction, bit shifts and logic operations. Unless otherwise mentioned, arithmetic operations are 2's complement in nature. Depending on the operation, the ALU may affect the values of the Carry (C), Zero (Z), Negative (N), Overflow (OV) and Digit Carry (DC) Status bits in the <u>SR register</u>. The <u>C and DC</u> Status bits operate as Borrow and Digit Borrow bits, respectively, for subtraction operations.

The ALU can perform 8-bit or 16-bit operations, depending on the mode of the instruction that is used. Data for the ALU operation can come from the W register array, or data memory, depending on the addressing mode of the instruction. Likewise, output data from the ALU can be written to the W register array or a data memory location.

Refer to the "16-bit MCU and DSC Programmer's Reference Manual" (DS70157) for information on the SR bits affected by each instruction.

The PIC24HJXXXGPX06A/X08A/X10A CPU incorporates hardware support for both multiplication and division. This includes a dedicated hardware multiplier and support hardware for 16-bit divisor division.

#### 3.4.1 MULTIPLIER

Using the high-speed 17-bit x 17-bit multiplier, the ALU supports unsigned, signed or mixed-sign operation in several multiplication modes:

- 16-bit x 16-bit signed

- 16-bit x 16-bit unsigned

- 16-bit signed x 5-bit (literal) unsigned

- 16-bit unsigned x 16-bit unsigned

- 16-bit unsigned x 5-bit (literal) unsigned

- 16-bit unsigned x 16-bit signed

- 8-bit unsigned x 8-bit unsigned

### 3.4.2 DIVIDER

The divide block supports 32-bit/16-bit and 16-bit/16-bit signed and unsigned integer divide operations with the following data sizes:

- 32-bit signed/16-bit signed divide

- 32-bit unsigned/16-bit unsigned divide

- 16-bit signed/16-bit signed divide

- 16-bit unsigned/16-bit unsigned divide

The quotient for all divide instructions ends up in W0 and the remainder in W1. Sixteen-bit signed and unsigned DIV instructions can specify any W register for both the 16-bit divisor (Wn) and any W register (aligned) pair (W(m + 1):Wm) for the 32-bit dividend. The divide algorithm takes one cycle per bit of divisor, so both 32-bit/16-bit and 16-bit/16-bit instructions take the same number of cycles to execute.

#### 3.4.3 MULTI-BIT DATA SHIFTER

The multi-bit data shifter is capable of performing up to 16-bit arithmetic or logic right shifts, or up to 16-bit left shifts in a single cycle. The source can be either a working register or a memory location.

The shifter requires a signed binary value to determine both the magnitude (number of bits) and direction of the shift operation. A positive value shifts the operand right. A negative value shifts the operand left. A value of '0' does not modify the operand.

| TABLE       | 4-6:        | TIME                                                 | R REG           | ISTER N | IAP    |        |        |              |              |                |                      |       |        |       |       |       |       |               |

|-------------|-------------|------------------------------------------------------|-----------------|---------|--------|--------|--------|--------------|--------------|----------------|----------------------|-------|--------|-------|-------|-------|-------|---------------|

| SFR<br>Name | SFR<br>Addr | Bit 15                                               | Bit 14          | Bit 13  | Bit 12 | Bit 11 | Bit 10 | Bit 9        | Bit 8        | Bit 7          | Bit 6                | Bit 5 | Bit 4  | Bit 3 | Bit 2 | Bit 1 | Bit 0 | All<br>Resets |

| TMR1        | 0100        |                                                      | Timer1 Register |         |        |        |        |              |              |                |                      | 0000  |        |       |       |       |       |               |

| PR1         | 0102        |                                                      |                 |         |        |        |        |              | Period F     | Register 1     |                      |       |        |       |       |       |       | FFFF          |

| T1CON       | 0104        | TON                                                  |                 | TSIDL   |        | _      | _      | _            | _            | _              | TGATE                | TCKP  | S<1:0> | _     | TSYNC | TCS   | _     | 0000          |

| TMR2        | 0106        |                                                      |                 |         |        |        |        |              | Timer2       | Register       |                      |       |        |       |       |       |       | 0000          |

| TMR3HLD     | 0108        |                                                      |                 |         |        |        | Tim    | ner3 Holding | Register (fo | r 32-bit time  | operations c         | only) |        |       |       |       |       | xxxx          |

| TMR3        | 010A        |                                                      |                 |         |        |        |        |              | Timer3       | Register       |                      |       |        |       |       |       |       | 0000          |

| PR2         | 010C        |                                                      |                 |         |        |        |        |              | Period F     | Register 2     |                      |       |        |       |       |       |       | FFFF          |

| PR3         | 010E        |                                                      |                 |         |        |        |        |              | Period F     | Register 3     |                      |       |        |       |       |       |       | FFFF          |

| T2CON       | 0110        | TON                                                  |                 | TSIDL   | _      | _      | _      | _            | _            | _              | TGATE                | TCKP  | S<1:0> | T32   | —     | TCS   | _     | 0000          |

| T3CON       | 0112        | TON                                                  |                 | TSIDL   | _      | _      | _      | _            | _            | _              | TGATE                | TCKP  | S<1:0> | _     | _     | TCS   | _     | 0000          |

| TMR4        | 0114        |                                                      |                 |         |        |        |        |              | Timer4       | Register       |                      |       |        |       |       |       |       | 0000          |

| TMR5HLD     | 0116        | Timer5 Holding Register (for 32-bit operations only) |                 |         |        |        |        |              |              |                | xxxx                 |       |        |       |       |       |       |               |

| TMR5        | 0118        | Timer5 Register                                      |                 |         |        |        |        |              |              | 0000           |                      |       |        |       |       |       |       |               |

| PR4         | 011A        | Period Register 4                                    |                 |         |        |        |        |              |              | FFFF           |                      |       |        |       |       |       |       |               |

| PR5         | 011C        | Period Register 5                                    |                 |         |        |        |        |              |              | FFFF           |                      |       |        |       |       |       |       |               |

| T4CON       | 011E        | TON                                                  | _               | TSIDL   | _      | _      | _      | _            | _            | _              | TGATE                | TCKP  | S<1:0> | T32   | _     | TCS   | _     | 0000          |

| T5CON       | 0120        | TON                                                  | _               | TSIDL   | _      | _      | _      | _            | _            | _              | TGATE                | TCKP  | S<1:0> | _     | _     | TCS   | —     | 0000          |

| TMR6        | 0122        |                                                      |                 |         |        |        |        |              | Timer6       | Register       |                      |       |        |       |       |       |       | 0000          |

| TMR7HLD     | 0124        |                                                      |                 |         |        |        | -      | Timer7 Hold  | ing Register | (for 32-bit op | perations only       | /)    |        |       |       |       |       | xxxx          |

| TMR7        | 0126        |                                                      |                 |         |        |        |        |              | Timer7       | Register       |                      |       |        |       |       |       |       | 0000          |

| PR6         | 0128        |                                                      |                 |         |        |        |        |              | Period F     | Register 6     |                      |       |        |       |       |       |       | FFFF          |

| PR7         | 012A        |                                                      |                 |         |        |        |        |              | Period F     | Register 7     |                      |       |        |       |       |       |       | FFFF          |

| T6CON       | 012C        | TON                                                  |                 | TSIDL   | _      | _      | _      | _            | _            | _              | TGATE                | TCKP  | S<1:0> | T32   | _     | TCS   | _     | 0000          |

| T7CON       | 012E        | TON                                                  |                 | TSIDL   | _      | _      | _      | _            | _            | _              | TGATE                | TCKP  | S<1:0> | _     | _     | TCS   | _     | 0000          |

| TMR8        | 0130        | Timer8 Register                                      |                 |         |        |        |        |              | 0000         |                |                      |       |        |       |       |       |       |               |

| TMR9HLD     | 0132        | Timer9 Holding Register (for 32-bit operations only) |                 |         |        |        |        |              |              | xxxx           |                      |       |        |       |       |       |       |               |

| TMR9        | 0134        |                                                      |                 |         |        |        |        |              | Timer9       | Register       |                      |       |        |       |       |       |       | 0000          |

| PR8         | 0136        |                                                      |                 |         |        |        |        |              | Period F     | Register 8     |                      |       |        |       |       |       |       | FFFF          |

| PR9         | 0138        |                                                      |                 |         |        |        |        |              | Period F     | Register 9     |                      |       |        |       |       |       |       | FFFF          |

| T8CON       | 013A        | TON                                                  | _               | TSIDL   | —      | —      | —      | —            | —            | —              | TGATE                | TCKP  | S<1:0> | T32   | _     | TCS   | —     | 0000          |

| T9CON       | 013C        | TON                                                  | _               | TSIDL   | _      | _      | _      | _            | _            | _              | TGATE                | TCKP  | S<1:0> | _     | _     | TCS   | _     | 0000          |

| L           |             |                                                      | har an Daa      |         |        |        |        |              |              |                | Dire Liberte ad av d |       |        |       |       |       |       |               |

#### . . TIMED DEGIGTED MAD

Legend: x = unknown value on Reset, — = unimplemented, read as '0'. Reset values are shown in hexadecimal for PinHigh devices.

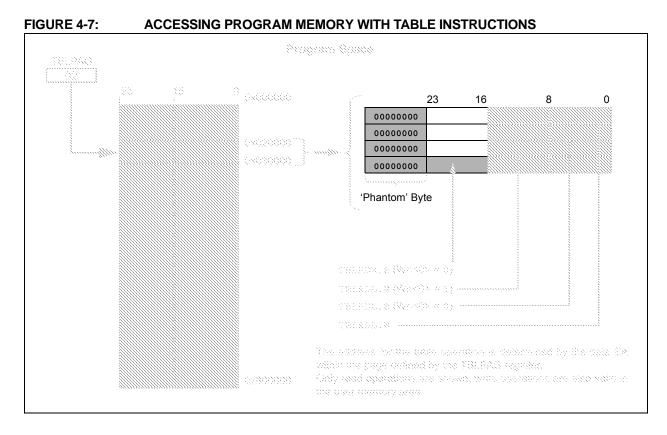

#### 4.4.2 DATA ACCESS FROM PROGRAM MEMORY USING TABLE INSTRUCTIONS

The TBLRDL and TBLWTL instructions offer a direct method of reading or writing the lower word of any address within the program space without going through data space. The TBLRDH and TBLWTH instructions are the only method to read or write the upper 8 bits of a program space word as data.

The PC is incremented by two for each successive 24-bit program word. This allows program memory addresses to directly map to data space addresses. Program memory can thus be regarded as two 16-bit, word wide address spaces, residing side by side, each with the same address range. TBLRDL and TBLWTL access the space which contains the least significant data word and TBLRDH and TBLWTH access the space which contains the upper data byte.

Two table instructions are provided to move byte or word sized (16-bit) data to and from program space. Both function as either byte or word operations.

TBLRDL (Table Read Low): In Word mode, it maps the lower word of the program space location (P<15:0>) to a data address (D<15:0>).

In Byte mode, either the upper or lower byte of the lower program word is mapped to the lower byte of a data address. The upper byte is selected when Byte Select is '1'; the lower byte is selected when it is '0'.  TBLRDH (Table Read High): In Word mode, it maps the entire upper word of a program address (P<23:16>) to a data address. Note that D<15:8>, the 'phantom byte', will always be '0'.

In Byte mode, it maps the upper or lower byte of the program word to D<7:0> of the data address, as above. Note that the data will always be '0' when the upper 'phantom' byte is selected (Byte Select = 1).

In a similar fashion, two table instructions, TBLWTH and TBLWTL, are used to write individual bytes or words to a program space address. The details of their operation are explained in **Section 5.0 "Flash Program Memory"**.

For all table operations, the area of program memory space to be accessed is determined by the Table Page register (TBLPAG). TBLPAG covers the entire program memory space of the device, including user and configuration spaces. When TBLPAG<7> = 0, the table page is located in the user memory space. When TBLPAG<7> = 1, the page is located in configuration space.

| R/W-      | 0 R/W-0                                                                                                                                                                           | U-0                                                    | U-0                       | U-0                                                 | U-0                | U-0              | R/W-0                |

|-----------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------|---------------------------|-----------------------------------------------------|--------------------|------------------|----------------------|

| TRAP      | R IOPUWR                                                                                                                                                                          | —                                                      | —                         | —                                                   | —                  | —                | VREGS <sup>(3)</sup> |

| bit 15    | ·                                                                                                                                                                                 |                                                        |                           |                                                     |                    |                  | bit                  |

| R/W-      | 0 R/W-0                                                                                                                                                                           | R/W-0                                                  | R/W-0                     | R/W-0                                               | R/W-0              | R/W-1            | R/W-1                |

| EXTR      |                                                                                                                                                                                   | SWDTEN <sup>(2)</sup>                                  | WDTO                      | SLEEP                                               | IDLE               | BOR              | POR                  |

| bit 7     |                                                                                                                                                                                   |                                                        |                           |                                                     |                    |                  | bit                  |

| Legend:   |                                                                                                                                                                                   |                                                        |                           |                                                     |                    |                  |                      |

| R = Read  | able bit                                                                                                                                                                          | W = Writable                                           | bit                       | U = Unimpler                                        | nented bit, read   | as '0'           |                      |

| -n = Valu | e at POR                                                                                                                                                                          | '1' = Bit is set                                       |                           | '0' = Bit is cle                                    | ared               | x = Bit is unk   | nown                 |

| bit 15    | 1 = A Trap Co                                                                                                                                                                     | Reset Flag bit<br>onflict Reset ha<br>onflict Reset ha | s occurred                | d                                                   |                    |                  |                      |

| bit 14    | 1 = An illega<br>Address                                                                                                                                                          | l opcode deter<br>Pointer caused                       | ction, an ille<br>a Reset | W Access Rese<br>gal address mo<br>Reset has not oo | ode or uninitiali  | zed W regist     | er used as a         |

| bit 13-9  | Unimplemen                                                                                                                                                                        | ted: Read as 'o                                        | )'                        |                                                     |                    |                  |                      |

| bit 8     | 1 = Voltage R                                                                                                                                                                     | age Regulator S<br>egulator is acti<br>egulator goes i | ve during Sle             |                                                     | еер                |                  |                      |

| bit 7     | 1 = A Master                                                                                                                                                                      | al Reset (MCL<br>Clear (pin) Res<br>Clear (pin) Res    | et has occur              |                                                     |                    |                  |                      |

| bit 6     | 1 <b>= A</b> reset                                                                                                                                                                | re Reset (Instru<br>instruction has<br>instruction has | been execut               | ed                                                  |                    |                  |                      |

| bit 5     | <b>SWDTEN:</b> So<br>1 = WDT is en<br>0 = WDT is di                                                                                                                               |                                                        | Disable of W              | DT bit <sup>(2)</sup>                               |                    |                  |                      |

| bit 4     | 1 = WDT time                                                                                                                                                                      | hdog Timer Tim<br>e-out has occur<br>e-out has not oc  | red                       | it                                                  |                    |                  |                      |

| bit 3     | SLEEP: Wake<br>1 = Device ha                                                                                                                                                      | e-up from Sleer<br>as been in Slee                     | o Flag bit<br>p mode      |                                                     |                    |                  |                      |

| bit 2     | <ul> <li>0 = Device has not been in Sleep mode</li> <li>IDLE: Wake-up from Idle Flag bit</li> <li>1 = Device was in Idle mode</li> <li>0 = Device was not in Idle mode</li> </ul> |                                                        |                           |                                                     |                    |                  |                      |

| bit 1     | <b>BOR:</b> Brown-out Reset Flag bit<br>1 = A Brown-out Reset has occurred<br>0 = A Brown-out Reset has not occurred                                                              |                                                        |                           |                                                     |                    |                  |                      |

| bit 0     | <b>POR:</b> Power-<br>1 = A Power-                                                                                                                                                | on Reset Flag I<br>on Reset has o<br>on Reset has n    | bit<br>ccurred            |                                                     |                    |                  |                      |

| Note 1:   | All of the Reset sta<br>cause a device Re                                                                                                                                         | -                                                      | set or cleare             | ed in software. S                                   | Setting one of the | ese bits in soff | tware does no        |

| 2:        | If the FWDTEN Co<br>SWDTEN bit settin                                                                                                                                             | ig.                                                    |                           | -                                                   | -                  | -                |                      |

| 3:        | For PIC24HJ256G                                                                                                                                                                   | PX06A/X08A/X                                           | (10A devices              | , this bit is unim                                  | plemented and      | reads back p     | rogrammed            |

**3:** For PIC24HJ256GPX06A/X08A/X10A devices, this bit is unimplemented and reads back programmed value.

| ABLE 7-1         | 1 1                                  | T VECTORS   | 1            |                                      |

|------------------|--------------------------------------|-------------|--------------|--------------------------------------|

| Vector<br>Number | Interrupt<br>Request (IRQ)<br>Number | IVT Address | AIVT Address | Interrupt Source                     |

| 8                | 0                                    | 0x000014    | 0x000114     | INT0 – External Interrupt 0          |

| 9                | 1                                    | 0x000016    | 0x000116     | IC1 – Input Capture 1                |

| 10               | 2                                    | 0x000018    | 0x000118     | OC1 – Output Compare 1               |

| 11               | 3                                    | 0x00001A    | 0x00011A     | T1 – Timer1                          |

| 12               | 4                                    | 0x00001C    | 0x00011C     | DMA0 – DMA Channel 0                 |

| 13               | 5                                    | 0x00001E    | 0x00011E     | IC2 – Input Capture 2                |

| 14               | 6                                    | 0x000020    | 0x000120     | OC2 – Output Compare 2               |

| 15               | 7                                    | 0x000022    | 0x000122     | T2 – Timer2                          |

| 16               | 8                                    | 0x000024    | 0x000124     | T3 – Timer3                          |

| 17               | 9                                    | 0x000026    | 0x000126     | SPI1E – SPI1 Error                   |

| 18               | 10                                   | 0x000028    | 0x000128     | SPI1 – SPI1 Transfer Done            |

| 19               | 11                                   | 0x00002A    | 0x00012A     | U1RX – UART1 Receiver                |

| 20               | 12                                   | 0x00002C    | 0x00012C     | U1TX – UART1 Transmitter             |

| 21               | 13                                   | 0x00002E    | 0x00012E     | ADC1 – Analog-to-Digital Converter 1 |

| 22               | 14                                   | 0x000030    | 0x000130     | DMA1 – DMA Channel 1                 |

| 23               | 15                                   | 0x000032    | 0x000132     | Reserved                             |

| 24               | 16                                   | 0x000034    | 0x000134     | SI2C1 – I2C1 Slave Events            |

| 25               | 17                                   | 0x000036    | 0x000136     | MI2C1 – I2C1 Master Events           |

| 26               | 18                                   | 0x000038    | 0x000138     | Reserved                             |

| 27               | 19                                   | 0x00003A    | 0x00013A     | CN - Change Notification Interrupt   |

| 28               | 20                                   | 0x00003C    | 0x00013C     | INT1 – External Interrupt 1          |

| 29               | 21                                   | 0x00003E    | 0x00013E     | ADC2 – Analog-to-Digital Converter 2 |

| 30               | 22                                   | 0x000040    | 0x000140     | IC7 – Input Capture 7                |

| 31               | 23                                   | 0x000042    | 0x000142     | IC8 – Input Capture 8                |

| 32               | 24                                   | 0x000044    | 0x000144     | DMA2 – DMA Channel 2                 |

| 33               | 25                                   | 0x000046    | 0x000146     | OC3 – Output Compare 3               |

| 34               | 26                                   | 0x000048    | 0x000148     | OC4 – Output Compare 4               |

| 35               | 27                                   | 0x00004A    | 0x00014A     | T4 – Timer4                          |

| 36               | 28                                   | 0x00004C    | 0x00014C     | T5 – Timer5                          |

| 37               | 29                                   | 0x00004E    | 0x00014E     | INT2 – External Interrupt 2          |

| 38               | 30                                   | 0x000050    | 0x000150     | U2RX – UART2 Receiver                |

| 39               | 31                                   | 0x000052    | 0x000152     | U2TX – UART2 Transmitter             |

| 40               | 32                                   | 0x000054    | 0x000154     | SPI2E – SPI2 Error                   |

| 41               | 33                                   | 0x000056    | 0x000156     | SPI1 – SPI1 Transfer Done            |

| 42               | 34                                   | 0x000058    | 0x000158     | C1RX – ECAN1 Receive Data Ready      |

| 43               | 35                                   | 0x00005A    | 0x00015A     | C1 – ECAN1 Event                     |

| 44               | 36                                   | 0x00005C    | 0x00015C     | DMA3 – DMA Channel 3                 |

| 45               | 37                                   | 0x00005E    | 0x00015E     | IC3 – Input Capture 3                |

| 46               | 38                                   | 0x000060    | 0x000160     | IC4 – Input Capture 4                |

| 47               | 39                                   | 0x000062    | 0x000162     | IC5 – Input Capture 5                |

| 48               | 40                                   | 0x000064    | 0x000164     | IC6 – Input Capture 6                |

| 49               | 41                                   | 0x000066    | 0x000166     | OC5 – Output Compare 5               |

| 50               | 42                                   | 0x000068    | 0x000168     | OC6 – Output Compare 6               |

| 51               | 43                                   | 0x00006A    | 0x00016A     | OC7 – Output Compare 7               |

| 52               | 44                                   | 0x00006C    | 0x00016C     | OC8 – Output Compare 8               |

| 53               | 45                                   | 0x00006E    | 0x00016E     | Reserved                             |

TABLE 7-1: INTERRUPT VECTORS

#### REGISTER 7-17: IPC2: INTERRUPT PRIORITY CONTROL REGISTER 2

| U-0              | R/W-1                                                                   | R/W-0                                    | R/W-0          | U-0              | R/W-1           | R/W-0           | R/W-0 |  |  |  |

|------------------|-------------------------------------------------------------------------|------------------------------------------|----------------|------------------|-----------------|-----------------|-------|--|--|--|

| —                |                                                                         | U1RXIP<2:0>                              |                | —                |                 | SPI1IP<2:0>     |       |  |  |  |

| bit 15           |                                                                         |                                          |                |                  |                 |                 | bit   |  |  |  |

| 11.0             |                                                                         | R/W-0                                    |                | 11.0             |                 | R/W-0           |       |  |  |  |

| U-0              | R/W-1                                                                   | SPI1EIP<2:0>                             | R/W-0          | U-0              | R/W-1           | T3IP<2:0>       | R/W-0 |  |  |  |

| bit 7            |                                                                         | 0111211 \2.02                            |                |                  |                 | 1011 \2.02      | bit   |  |  |  |

| 510 1            |                                                                         |                                          |                |                  |                 |                 | bit   |  |  |  |

| Legend:          |                                                                         |                                          |                |                  |                 |                 |       |  |  |  |

| R = Readabl      | e bit                                                                   | W = Writable                             | bit            | U = Unimple      | mented bit, rea | d as '0'        |       |  |  |  |

| -n = Value at    | POR                                                                     | '1' = Bit is set                         |                | '0' = Bit is cle | eared           | x = Bit is unkr | nown  |  |  |  |

| bit 15           | Unimpleme                                                               | ented: Read as '                         | 0'             |                  |                 |                 |       |  |  |  |

| bit 14-12        | -                                                                       | :0>: UART1 Rece                          |                | Prioritv bits    |                 |                 |       |  |  |  |

|                  |                                                                         | rupt is priority 7 (                     | -              | -                |                 |                 |       |  |  |  |

|                  | •                                                                       |                                          |                |                  |                 |                 |       |  |  |  |

|                  | •                                                                       |                                          |                |                  |                 |                 |       |  |  |  |

|                  | 001 = Inter                                                             | rupt is priority 1                       |                |                  |                 |                 |       |  |  |  |

|                  |                                                                         | rupt source is dis                       | abled          |                  |                 |                 |       |  |  |  |

| bit 11           | Unimpleme                                                               | ented: Read as '                         | 0'             |                  |                 |                 |       |  |  |  |

| bit 10-8         | SPI1IP<2:0>: SPI1 Event Interrupt Priority bits                         |                                          |                |                  |                 |                 |       |  |  |  |

|                  | 111 = Inter                                                             | rupt is priority 7 (                     | highest priori | ty interrupt)    |                 |                 |       |  |  |  |

|                  | •                                                                       |                                          |                |                  |                 |                 |       |  |  |  |

|                  | •                                                                       |                                          |                |                  |                 |                 |       |  |  |  |

|                  |                                                                         | rupt is priority 1<br>rupt source is dis | abled          |                  |                 |                 |       |  |  |  |

| bit 7            |                                                                         | ented: Read as '                         |                |                  |                 |                 |       |  |  |  |

| bit 6-4          | -                                                                       | :0>: SPI1 Error II                       |                | ty bits          |                 |                 |       |  |  |  |

|                  |                                                                         | rupt is priority 7 (                     | -              | -                |                 |                 |       |  |  |  |

|                  | •                                                                       |                                          |                |                  |                 |                 |       |  |  |  |

|                  | •                                                                       |                                          |                |                  |                 |                 |       |  |  |  |

|                  |                                                                         | rupt is priority 1                       |                |                  |                 |                 |       |  |  |  |

| <b>h</b> :+ 0    |                                                                         | rupt source is dis                       |                |                  |                 |                 |       |  |  |  |

| bit 3<br>bit 2-0 | Unimplemented: Read as '0'<br>T3IP<2:0>: Timer3 Interrupt Priority bits |                                          |                |                  |                 |                 |       |  |  |  |

| DIL 2-0          |                                                                         | rupt is priority 7 (                     | -              | v interrunt)     |                 |                 |       |  |  |  |

|                  | •                                                                       |                                          | riighest phon  | ly interrupt)    |                 |                 |       |  |  |  |

|                  | •                                                                       |                                          |                |                  |                 |                 |       |  |  |  |

|                  | •<br>001 = Inter                                                        | muchic criteriter d                      |                |                  |                 |                 |       |  |  |  |

|                  |                                                                         |                                          |                |                  |                 |                 |       |  |  |  |

| U-0          | R/W-1                                                      | R/W-0                                              | R/W-0           | U-0                                | R/W-1 | R/W-0           | R/W-0 |  |  |  |

|--------------|------------------------------------------------------------|----------------------------------------------------|-----------------|------------------------------------|-------|-----------------|-------|--|--|--|

| _            |                                                            | U2TXIP<2:0>                                        |                 |                                    |       | U2RXIP<2:0>     |       |  |  |  |

| bit 15       |                                                            |                                                    |                 |                                    |       |                 | bit   |  |  |  |

| U-0          | R/W-1                                                      | R/W-0                                              | R/W-0           | U-0                                | R/W-1 | R/W-0           | R/W-0 |  |  |  |

|              |                                                            | INT2IP<2:0>                                        |                 | _                                  |       | T5IP<2:0>       |       |  |  |  |

| bit 7        |                                                            |                                                    |                 |                                    | 1     |                 | bit   |  |  |  |

| Legend:      |                                                            |                                                    |                 |                                    |       |                 |       |  |  |  |

| R = Readab   | le bit                                                     | W = Writable                                       | bit             | U = Unimplemented bit, read as '0' |       |                 |       |  |  |  |

| -n = Value a | n = Value at POR '1' = Bit is set                          |                                                    |                 |                                    | eared | x = Bit is unkr | iown  |  |  |  |

| bit 15       | Unimpleme                                                  | ented: Read as '                                   | כי              |                                    |       |                 |       |  |  |  |

| bit 14-12    |                                                            | <b>0&gt;:</b> UART2 Trans<br>rupt is priority 7 (I |                 |                                    |       |                 |       |  |  |  |

|              | •                                                          |                                                    |                 |                                    |       |                 |       |  |  |  |

|              | •<br>001 = Interr                                          | upt is priority 1                                  |                 |                                    |       |                 |       |  |  |  |

|              |                                                            | upt source is dis                                  | abled           |                                    |       |                 |       |  |  |  |

| bit 11       | Unimpleme                                                  | ented: Read as '                                   | o'              |                                    |       |                 |       |  |  |  |

| bit 10-8     | U2RXIP<2:0>: UART2 Receiver Interrupt Priority bits        |                                                    |                 |                                    |       |                 |       |  |  |  |

|              | 111 = Interrupt is priority 7 (highest priority interrupt) |                                                    |                 |                                    |       |                 |       |  |  |  |

|              | •                                                          |                                                    |                 |                                    |       |                 |       |  |  |  |

|              | •                                                          |                                                    |                 |                                    |       |                 |       |  |  |  |

|              | 001 = Interrupt is priority 1                              |                                                    |                 |                                    |       |                 |       |  |  |  |

|              |                                                            | upt source is dis                                  |                 |                                    |       |                 |       |  |  |  |

| bit 7        | -                                                          | ented: Read as '                                   |                 |                                    |       |                 |       |  |  |  |

| bit 6-4      |                                                            | >: External Interr                                 |                 |                                    |       |                 |       |  |  |  |

|              | 111 = Interr                                               | rupt is priority 7 (I                              | nighest priori  | ty interrupt)                      |       |                 |       |  |  |  |

|              | •                                                          |                                                    |                 |                                    |       |                 |       |  |  |  |

|              | •                                                          |                                                    |                 |                                    |       |                 |       |  |  |  |

|              |                                                            | upt is priority 1                                  | ablad           |                                    |       |                 |       |  |  |  |

| bit 3        |                                                            | upt source is dis<br>ented: Read as 'o             |                 |                                    |       |                 |       |  |  |  |

| bit 2-0      | -                                                          | Timer5 Interrupt                                   |                 |                                    |       |                 |       |  |  |  |

| DIL 2-0      |                                                            | upt is priority 7 (I                               | -               | tv interrupt)                      |       |                 |       |  |  |  |

|              | •                                                          | арт ю р. ю. т. у т. (.                             | ingineer priori | ()                                 |       |                 |       |  |  |  |

|              | •                                                          |                                                    |                 |                                    |       |                 |       |  |  |  |

|              | •                                                          |                                                    |                 |                                    |       |                 |       |  |  |  |

|              | ()()   = Interr                                            | upt is priority 1                                  |                 |                                    |       |                 |       |  |  |  |

#### 10.2.2 IDLE MODE

Idle mode has these features:

- · The CPU stops executing instructions.

- The WDT is automatically cleared.

- The system clock source remains active. By default, all peripheral modules continue to operate normally from the system clock source, but can also be selectively disabled (see Section 10.4 "Peripheral Module Disable").

- If the WDT or FSCM is enabled, the LPRC also remains active.

The device will wake from Idle mode on any of these events:

- Any interrupt that is individually enabled.

- · Any device Reset.

- A WDT time-out.

On wake-up from Idle, the clock is reapplied to the CPU and instruction execution will begin (2-4 clock cycles later), starting with the instruction following the PWRSAV instruction, or the first instruction in the ISR.

#### 10.2.3 INTERRUPTS COINCIDENT WITH POWER SAVE INSTRUCTIONS

Any interrupt that coincides with the execution of a PWRSAV instruction is held off until entry into Sleep or Idle mode has completed. The device then wakes up from Sleep or Idle mode.

#### 10.3 Doze Mode

Generally, changing clock speed and invoking one of the power-saving modes are the preferred strategies for reducing power consumption. There may be circumstances, however, where this is not practical. For example, it may be necessary for an application to maintain uninterrupted synchronous communication, even while it is doing nothing else. Reducing system clock speed may introduce communication errors, while using a power-saving mode may stop communications completely.

Doze mode is a simple and effective alternative method to reduce power consumption while the device is still executing code. In this mode, the system clock continues to operate from the same source and at the same speed. Peripheral modules continue to be clocked at the same speed, while the CPU clock speed is reduced. Synchronization between the two clock domains is maintained, allowing the peripherals to access the SFRs while the CPU executes code at a slower rate. Doze mode is enabled by setting the DOZEN bit (CLKDIV<11>). The ratio between peripheral and core clock speed is determined by the DOZE<2:0> bits (CLKDIV<14:12>). There are eight possible configurations, from 1:1 to 1:128, with 1:1 being the default setting.

It is also possible to use Doze mode to selectively reduce power consumption in event-driven applications. This allows clock-sensitive functions, such as synchronous communications, to continue without interruption while the CPU idles, waiting for something to invoke an interrupt routine. Enabling the automatic return to full-speed CPU operation on interrupts is enabled by setting the ROI bit (CLKDIV<15>). By default, interrupt events have no effect on Doze mode operation.

For example, suppose the device is operating at 20 MIPS and the CAN module has been configured for 500 kbps based on this device operating speed. If the device is now placed in Doze mode with a clock frequency ratio of 1:4, the CAN module continues to communicate at the required bit rate of 500 kbps, but the CPU now starts executing instructions at a frequency of 5 MIPS.

### 10.4 Peripheral Module Disable

The Peripheral Module Disable (PMD) registers provide a method to disable a peripheral module by stopping all clock sources supplied to that module. When a peripheral is disabled via the appropriate PMD control bit, the peripheral is in a minimum power consumption state. The control and status registers associated with the peripheral are also disabled, so writes to those registers will have no effect and read values will be invalid.

A peripheral module is only enabled if both the associated bit in the PMD register is cleared and the peripheral is supported by the specific dsPIC<sup>®</sup> DSC variant. If the peripheral is present in the device, it is enabled in the PMD register by default.

Note: If a PMD bit is set, the corresponding module is disabled after a delay of 1 instruction cycle. Similarly, if a PMD bit is cleared, the corresponding module is enabled after a delay of 1 instruction cycle (assuming the module control registers are already configured to enable module operation).

### 11.6 I/O Helpful Tips

- 1. In some cases, certain pins as defined in TABLE 24-9: "DC Characteristics: I/O Pin Input Specifications" under "Injection Current", have internal protection diodes to VDD and Vss. The term "Injection Current" is also referred to as "Clamp Current". On designated pins, with sufficient external current limiting precautions by the user, I/O pin input voltages are allowed to be greater or less than the data sheet absolute maximum ratings with nominal VDD with respect to the VSS and VDD supplies. Note that when the user application forward biases either of the high or low side internal input clamp diodes, that the resulting current being injected into the device that is clamped internally by the VDD and VSS power rails, may affect the ADC accuracy by four to six counts.

- I/O pins that are shared with any analog input pin, 2. (i.e., ANx), are always analog pins by default after any reset. Consequently, any pin(s) configured as an analog input pin, automatically disables the digital input pin buffer. As such, any attempt to read a digital input pin will always return a '0' regardless of the digital logic level on the pin if the analog pin is configured. To use a pin as a digital I/O pin on a shared ANx pin, the user application needs to configure the analog pin configuration registers in the ADC module, (i.e., ADxPCFGL, AD1PCFGH), by setting the appropriate bit that corresponds to that I/O port pin to a '1'. On devices with more than one ADC, both analog pin configurations for both ADC modules must be configured as a digital I/O pin for that pin to function as a digital I/O pin.

- **Note:** Although it is not possible to use a digital input pin when its analog function is enabled, it is possible to use the digital I/O output function, TRISx = 0x0, while the analog function is also enabled. However, this is not recommended, particularly if the analog input is connected to an external analog voltage source, which would create signal contention between the analog signal and the output pin driver.

- 3. Most I/O pins have multiple functions. Referring to the device pin diagrams in the data sheet, the priorities of the functions allocated to any pins are indicated by reading the pin name from left-to-right. The left most function name takes precedence over any function to its right in the naming convention. For example: AN16/T2CK/T7CK/RC1. This indicates that AN16 is the highest priority in this example and will supersede all other functions to its right in the list. Those other functions to its right, even if enabled, would not work as long as any other function to its left was enabled. This rule applies to all of the functions listed for a given pin.

- 4. Each CN pin has a configurable internal weak pull-up resistor. The pull-ups act as a current source connected to the pin, and eliminates the need for external resistors in certain applications. The internal pull-up is to ~(VDD-0.8) not VDD. This is still above the minimum VIH of CMOS and TTL devices.

- 5. When driving LEDs directly, the I/O pin can source or sink more current than what is specified in the VOH/IOH and VOL/IOL DC characteristic specification. The respective IOH and IOL current rating only applies to maintaining the corresponding output at or above the VOH and at or below the VOL levels. However, for LEDs unlike digital inputs of an externally connected device, they are not governed by the same minimum VIH/VIL levels. An I/O pin output can safely sink or source any current less than that listed in the absolute maximum rating section of the data sheet. For example:

VOH = 2.4v @ IOH = -8 mA and VDD = 3.3V

The maximum output current sourced by any 8 mA I/O pin = 12 mA.

LED source current < 12 mA is technically permitted. Refer to the VOH/IOH graphs in Section 24.0 "Electrical Characteristics" for additional information.

### 11.7 I/O Resources

Many useful resources related to I/O are provided on the main product page of the Microchip web site for the devices listed in this data sheet. This product page, which can be accessed using this link, contains the latest updates and additional information.

Note: In the event you are not able to access the product page using the link above, enter this URL in your browser: http://www.microchip.com/wwwproducts/ Devices.aspx?dDocName=en546061

#### 11.7.1 KEY RESOURCES

- Section 10. "I/O Ports" (DS70193)

- Code Samples

- Application Notes

- Software Libraries

- Webinars

- All related dsPIC33F/PIC24H Family Reference Manuals Sections

- Development Tools

REGISTER 16-3: SPIxCON2: SPIx CONTROL REGISTER 2

| R/W-0                        | R/W-0                                                                                                                                                                           | R/W-0                                                                                                                                                                                                             | U-0                                                                                                                                                               | U-0                             | U-0             | U-0                | U-0 |  |

|------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------|-----------------|--------------------|-----|--|

| FRMEN                        | SPIFSD                                                                                                                                                                          | FRMPOL                                                                                                                                                                                                            | _                                                                                                                                                                 | —                               | _               | _                  | _   |  |

| pit 15                       |                                                                                                                                                                                 |                                                                                                                                                                                                                   |                                                                                                                                                                   |                                 |                 |                    | bit |  |

|                              |                                                                                                                                                                                 |                                                                                                                                                                                                                   |                                                                                                                                                                   |                                 |                 |                    |     |  |

| U-0                          | U-0                                                                                                                                                                             | U-0                                                                                                                                                                                                               | U-0                                                                                                                                                               | U-0                             | U-0             | R/W-0              | U-0 |  |

| —                            | —                                                                                                                                                                               | _                                                                                                                                                                                                                 | —                                                                                                                                                                 | —                               | —               | FRMDLY             | —   |  |

| bit 7                        |                                                                                                                                                                                 |                                                                                                                                                                                                                   |                                                                                                                                                                   |                                 |                 |                    | bit |  |

| Legend:                      |                                                                                                                                                                                 |                                                                                                                                                                                                                   |                                                                                                                                                                   |                                 |                 |                    |     |  |

| R = Readable                 | e bit                                                                                                                                                                           | W = Writable                                                                                                                                                                                                      | bit                                                                                                                                                               | U = Unimplem                    | nented bit, rea | ad as '0'          |     |  |

| -n = Value at                | POR                                                                                                                                                                             | '1' = Bit is set                                                                                                                                                                                                  |                                                                                                                                                                   | '0' = Bit is clea               | ared            | x = Bit is unknown |     |  |

| bit 15                       | 1 = Framed S                                                                                                                                                                    |                                                                                                                                                                                                                   | abled ( <del>SSx</del> p                                                                                                                                          | oin used as fram                |                 | input/output)      |     |  |

| bit 15                       | 1 = Framed S                                                                                                                                                                    | SPIx support en                                                                                                                                                                                                   | abled ( <del>SSx</del> p                                                                                                                                          | oin used as fram                |                 | input/output)      |     |  |

| bit 15<br>bit 14             | 1 = Framed S<br>0 = Framed S<br><b>SPIFSD:</b> Fran                                                                                                                             | SPIx support en<br>SPIx support dis<br>me Sync Pulse                                                                                                                                                              | abled ( <mark>SSx</mark> p<br>abled<br>Direction Co                                                                                                               |                                 |                 | input/output)      |     |  |

| bit 14                       | 1 = Framed S<br>0 = Framed S<br><b>SPIFSD:</b> Fran<br>1 = Frame sy<br>0 = Frame sy                                                                                             | SPIx support en<br>SPIx support dis<br>me Sync Pulse<br>nc pulse input (<br>nc pulse output                                                                                                                       | abled ( <del>SSx</del> p<br>sabled<br>Direction Co<br>(slave)<br>t (master)                                                                                       | ntrol bit                       |                 | input/output)      |     |  |

|                              | 1 = Framed S<br>0 = Framed S<br><b>SPIFSD:</b> Fran<br>1 = Frame sy<br>0 = Frame sy<br><b>FRMPOL:</b> Fran                                                                      | SPIx support en<br>SPIx support dis<br>me Sync Pulse<br>nc pulse input (                                                                                                                                          | abled (SSx p<br>sabled<br>Direction Co<br>(slave)<br>t (master)<br>e Polarity bit                                                                                 | ntrol bit                       |                 | input/output)      |     |  |

| bit 14                       | 1 = Framed S<br>0 = Framed S<br><b>SPIFSD:</b> Fran<br>1 = Frame sy<br>0 = Frame sy<br><b>FRMPOL:</b> Fran<br>1 = Frame sy                                                      | SPIx support en<br>SPIx support dis<br>me Sync Pulse<br>nc pulse input (<br>nc pulse output<br>ame Sync Pulse                                                                                                     | abled (SSx p<br>sabled<br>Direction Co<br>(slave)<br>t (master)<br>e Polarity bit<br>ve-high                                                                      | ntrol bit                       |                 | input/output)      |     |  |

| bit 14                       | 1 = Framed S<br>0 = Framed S<br>SPIFSD: France<br>1 = Frame sy<br>0 = Frame sy<br>FRMPOL: France sy<br>0 = Frame sy                                                             | SPIx support en<br>SPIx support dis<br>me Sync Pulse<br>nc pulse input (<br>nc pulse output<br>ame Sync Pulse<br>nc pulse is activ                                                                                | abled (SSx p<br>sabled<br>Direction Co<br>(slave)<br>t (master)<br>e Polarity bit<br>ve-high<br>ve-low                                                            | ntrol bit                       |                 | input/output)      |     |  |

| bit 14<br>bit 13             | 1 = Framed S<br>0 = Framed S<br>SPIFSD: Fran<br>1 = Frame sy<br>0 = Frame sy<br>FRMPOL: Fran<br>1 = Frame sy<br>0 = Frame sy<br>Unimplemen                                      | Plx support en<br>Plx support dis<br>me Sync Pulse<br>nc pulse input (<br>nc pulse output<br>ame Sync Pulse<br>nc pulse is acti<br>nc pulse is acti                                                               | abled (SSx p<br>sabled<br>Direction Co<br>(slave)<br>t (master)<br>e Polarity bit<br>ve-high<br>ve-low<br>o'                                                      | ntrol bit                       |                 | input/output)      |     |  |

| bit 14<br>bit 13<br>bit 12-2 | 1 = Framed S<br>0 = Framed S<br>SPIFSD: France<br>1 = Frame sy<br>0 = Frame sy<br>0 = Frame sy<br>0 = Frame sy<br>Unimplement<br>FRMDLY: France<br>1 = Frame sy                 | SPIx support en<br>SPIx support dis<br>me Sync Pulse<br>nc pulse input (<br>nc pulse output<br>ame Sync Pulse<br>nc pulse is actir<br>nc pulse is actir<br>ated: Read as '(<br>ame Sync Pulse<br>nc pulse coincir | abled (SSx p<br>sabled<br>Direction Co<br>(slave)<br>t (master)<br>e Polarity bit<br>ve-high<br>ve-low<br>o'<br>e Edge Selec<br>des with first                    | ntrol bit<br>t bit<br>bit clock |                 | input/output)      |     |  |

| bit 14<br>bit 13<br>bit 12-2 | 1 = Framed S<br>0 = Framed S<br>SPIFSD: France<br>1 = Frame sy<br>0 = Frame sy<br>0 = Frame sy<br>0 = Frame sy<br>Unimplement<br>FRMDLY: France<br>1 = Frame sy<br>0 = Frame sy | SPIx support en<br>SPIx support dis<br>me Sync Pulse<br>nc pulse input (<br>nc pulse output<br>ame Sync Pulse<br>nc pulse is actir<br>nc pulse is actir<br>ted: Read as '(<br>ame Sync Pulse                      | abled (SSx p<br>sabled<br>Direction Co<br>(slave)<br>t (master)<br>e Polarity bit<br>ve-high<br>ve-low<br>p'<br>e Edge Selec<br>des with first<br>des first bit c | ntrol bit<br>t bit<br>bit clock |                 | input/output)      |     |  |

| R-0 HSC         | R-0 HSC                                                                                                                             | U-0                                                                                                                       | U-0                                                                                                    | U-0                      | R/C-0 HS                                         | R-0 HSC          | R-0 HSC         |  |  |  |

|-----------------|-------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------|--------------------------|--------------------------------------------------|------------------|-----------------|--|--|--|

| ACKSTAT         | TRSTAT                                                                                                                              |                                                                                                                           | —                                                                                                      |                          | BCL                                              | GCSTAT           | ADD10           |  |  |  |

| bit 15          |                                                                                                                                     |                                                                                                                           |                                                                                                        |                          |                                                  | 1                | bit 8           |  |  |  |

| R/C-0 HS        | R/C-0 HS                                                                                                                            | R-0 HSC                                                                                                                   | R/C-0 HSC                                                                                              | R/C-0 HSC                | R-0 HSC                                          | R-0 HSC          | R-0 HSC         |  |  |  |

| IWCOL           | I2COV                                                                                                                               | 1                                                                                                                         | Р                                                                                                      | S                        | R W                                              | RBF              | TBF             |  |  |  |

| bit 7           | 12000                                                                                                                               | D_A                                                                                                                       |                                                                                                        | 3                        | R_VV                                             | KDF              | bit C           |  |  |  |

|                 |                                                                                                                                     |                                                                                                                           |                                                                                                        |                          |                                                  |                  |                 |  |  |  |