Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFI

| 2 010.00                   |                                                                                |

|----------------------------|--------------------------------------------------------------------------------|

| Product Status             | Active                                                                         |

| Core Processor             | PIC                                                                            |

| Core Size                  | 16-Bit                                                                         |

| Speed                      | 40 MIPs                                                                        |

| Connectivity               | I <sup>2</sup> C, IrDA, LINbus, SPI, UART/USART                                |

| Peripherals                | Brown-out Detect/Reset, DMA, POR, PWM, WDT                                     |

| Number of I/O              | 85                                                                             |

| Program Memory Size        | 64KB (22K x 24)                                                                |

| Program Memory Type        | FLASH                                                                          |

| EEPROM Size                | -                                                                              |

| RAM Size                   | 8K x 8                                                                         |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 3.6V                                                                      |

| Data Converters            | A/D 32x10b/12b                                                                 |

| Oscillator Type            | Internal                                                                       |

| Operating Temperature      | -40°C ~ 125°C (TA)                                                             |

| Mounting Type              | Surface Mount                                                                  |

| Package / Case             | 100-TQFP                                                                       |

| Supplier Device Package    | 100-TQFP (14x14)                                                               |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic24hj64gp210a-e-pf |

|                            |                                                                                |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# 2.7 Oscillator Value Conditions on Device Start-up

If the PLL of the target device is enabled and configured for the device start-up oscillator, the maximum oscillator source frequency must be limited to  $\leq$  8 MHz for start-up with PLL enabled to comply with device PLL start-up conditions. This means that if the external oscillator frequency is outside this range, the application must start-up in the FRC mode first. The default PLL settings after a POR with an oscillator frequency outside this range will violate the device operating speed.

Once the device powers up, the application firmware can initialize the PLL SFRs, CLKDIV and PLLDBF to a suitable value, and then perform a clock switch to the Oscillator + PLL clock source. Note that clock switching must be enabled in the device Configuration word.

# 2.8 Configuration of Analog and Digital Pins During ICSP Operations

If MPLAB ICD 3 or REAL ICE is selected as a debugger, it automatically initializes all of the A/D input pins (ANx) as "digital" pins, by setting all bits in the AD1PCFGL register.

The bits in this register that correspond to the A/D pins that are initialized by MPLAB ICD 3 or REAL ICE, must not be cleared by the user application firmware; otherwise, communication errors will result between the debugger and the device.

If your application needs to use certain A/D pins as analog input pins during the debug session, the user application must clear the corresponding bits in the AD1PCFGL register during initialization of the ADC module.

When MPLAB ICD 3 or REAL ICE is used as a programmer, the user application firmware must correctly configure the AD1PCFGL register. Automatic initialization of this register is only done during debugger operation. Failure to correctly configure the register(s) will result in all A/D pins being recognized as analog input pins, resulting in the port value being read as a logic '0', which may affect user application functionality.

# 2.9 Unused I/Os

Unused I/O pins should be configured as outputs and driven to a logic-low state.

Alternatively, connect a 1k to 10k resistor between Vss and the unused pins.

| IABLE 4       | -19:          | ECAN    | 1 REGIS                 |             | AP WHE     | :N C1C     | RL1.W   | IN = 0F | OR PIC       | 24HJXX    | XGP50       | 5A/510A     | V610A L    | EVICE      | SONLY   |         |         |               |

|---------------|---------------|---------|-------------------------|-------------|------------|------------|---------|---------|--------------|-----------|-------------|-------------|------------|------------|---------|---------|---------|---------------|

| File Name     | Addr          | Bit 15  | Bit 14                  | Bit 13      | Bit 12     | Bit 11     | Bit 10  | Bit 9   | Bit 8        | Bit 7     | Bit 6       | Bit 5       | Bit 4      | Bit 3      | Bit 2   | Bit 1   | Bit 0   | All<br>Resets |

|               | 0400-<br>041E |         |                         |             |            |            |         | See     | e definition | when WIN  | = x         |             |            |            |         |         |         |               |

| C1RXFUL1      | 0420          | RXFUL15 | RXFUL14                 | RXFUL13     | RXFUL12    | RXFUL11    | RXFUL10 | RXFUL9  | RXFUL8       | RXFUL7    | RXFUL6      | RXFUL5      | RXFUL4     | RXFUL3     | RXFUL2  | RXFUL1  | RXFUL0  | 0000          |

| C1RXFUL2      | 0422          | RXFUL31 | RXFUL30                 | RXFUL29     | RXFUL28    | RXFUL27    | RXFUL26 | RXFUL25 | RXFUL24      | RXFUL23   | RXFUL22     | RXFUL21     | RXFUL20    | RXFUL19    | RXFUL18 | RXFUL17 | RXFUL16 | 0000          |

| C1RXOVF1      | 0428          | RXOVF15 | RXOVF14                 | RXOVF13     | RXOVF12    | RXOVF11    | RXOVF10 | RXOVF9  | RXOVF8       | RXOVF7    | RXOVF6      | RXOVF5      | RXOVF4     | RXOVF3     | RXOVF2  | RXOVF1  | RXOVF0  | 0000          |

| C1RXOVF2      | 042A          | RXOVF31 | RXOVF30                 | RXOVF29     | RXOVF28    | RXOVF27    | RXOVF26 | RXOVF25 | RXOVF24      | RXOVF23   | RXOVF22     | RXOVF21     | RXOVF20    | RXOVF19    | RXOVF18 | RXOVF17 | RXOVF16 | 0000          |

| C1TR01CO<br>N | 0430          | TXEN1   | TX<br>ABT1              | TX<br>LARB1 | TX<br>ERR1 | TX<br>REQ1 | RTREN1  | TX1PF   | RI<1:0>      | TXEN0     | TX<br>ABAT0 | TX<br>LARB0 | TX<br>ERR0 | TX<br>REQ0 | RTREN0  | TX0PF   | RI<1:0> | 0000          |

| C1TR23CO<br>N | 0432          | TXEN3   | TX<br>ABT3              | TX<br>LARB3 | TX<br>ERR3 | TX<br>REQ3 | RTREN3  | TX3PF   | RI<1:0>      | TXEN2     | TX<br>ABAT2 | TX<br>LARB2 | TX<br>ERR2 | TX<br>REQ2 | RTREN2  | TX2PF   | RI<1:0> | 0000          |

| C1TR45CO<br>N | 0434          | TXEN5   | TX<br>ABT5              | TX<br>LARB5 | TX<br>ERR5 | TX<br>REQ5 | RTREN5  | TX5PF   | RI<1:0>      | TXEN4     | TX<br>ABAT4 | TX<br>LARB4 | TX<br>ERR4 | TX<br>REQ4 | RTREN4  | TX4PF   | RI<1:0> | 0000          |

| C1TR67CO<br>N | 0436          | TXEN7   | TX<br>ABT7              | TX<br>LARB7 | TX<br>ERR7 | TX<br>REQ7 | RTREN7  | TX7PF   | RI<1:0>      | TXEN6     | TX<br>ABAT6 | TX<br>LARB6 | TX<br>ERR6 | TX<br>REQ6 | RTREN6  | TX6PF   | RI<1:0> | xxxx          |

| C1RXD         | 0440          |         |                         |             |            |            |         |         | Recieved I   | Data Word |             |             |            |            |         |         |         | xxxx          |

| C1TXD         | 0442          |         | Transmit Data Word xxxx |             |            |            |         |         |              |           |             |             |            |            |         |         |         |               |

### TABLE 4-19: ECAN1 REGISTER MAP WHEN C1CTRL1.WIN = 0 FOR PIC24HJXXXGP506A/510A/610A DEVICES ONLY

Legend: x = unknown value on Reset, — = unimplemented, read as '0'. Reset values are shown in hexadecimal for PinHigh devices.

### TABLE 4-20: ECAN1 REGISTER MAP WHEN C1CTRL1.WIN = 1 FOR PIC24HJXXXGP506A/510A/610A DEVICES ONLY

| File Name | Addr          | Bit 15     | Bit 14    | Bit 13 | Bit 12 | Bit 11                        | Bit 10 | Bit 9  | Bit 8       | Bit 7               | Bit 6    | Bit 5      | Bit 4 | Bit 3 | Bit 2 | Bit 1 | Bit 0 | All<br>Resets |

|-----------|---------------|------------|-----------|--------|--------|-------------------------------|--------|--------|-------------|---------------------|----------|------------|-------|-------|-------|-------|-------|---------------|

|           | 0400-<br>041E |            |           |        |        |                               |        |        | See definit | ion when W          | /IN = x  |            |       |       |       |       |       |               |

| C1BUFPNT1 | 0420          |            | F3BP      | <3:0>  |        | F2BP<3:0> F1BP<3:0> F0BP<3:0> |        |        |             |                     |          |            | 0000  |       |       |       |       |               |

| C1BUFPNT2 | 0422          |            | F7BP      | <3:0>  |        |                               | F6BF   | ><3:0> |             |                     | F5BP     | <3:0>      |       |       | F4BP  | <3:0> |       | 0000          |

| C1BUFPNT3 | 0424          |            | F11BF     | P<3:0> |        |                               | F10B   | P<3:0> |             | F9BP<3:0> F8BP<3:0> |          |            |       |       | 0000  |       |       |               |

| C1BUFPNT4 | 0426          | F15BP<3:0> |           |        |        | F14BP<3:0>                    |        |        |             | F13BP<3:0>          |          | F12BP<3:0> |       |       |       | 0000  |       |               |

| C1RXM0SID | 0430          |            |           |        | SID<   | 10:3>                         | 1:3>   |        |             |                     | SID<2:0> |            | —     | MIDE  | —     | EID<1 | 7:16> | xxxx          |

| C1RXM0EID | 0432          |            |           |        | EID<   | 15:8>                         |        |        |             |                     |          |            | EID<  | 7:0>  |       |       |       | xxxx          |

| C1RXM1SID | 0434          |            |           |        | SID<   | 10:3>                         | ):3>   |        |             | SID<2:0> —          |          |            | MIDE  | _     | EID<1 | 7:16> | xxxx  |               |

| C1RXM1EID | 0436          |            | EID<15:8> |        |        |                               |        |        |             | EID<                | 7:0>     |            |       |       | xxxx  |       |       |               |

| C1RXM2SID | 0438          | SID<       |           |        | 10:3>  |                               |        |        |             | SID<2:0>            |          | _          | MIDE  | _     | EID<1 | 7:16> | xxxx  |               |

| C1RXM2EID | 043A          |            |           |        | EID<   | :15:8>                        |        |        |             |                     |          |            | EID<  | 7:0>  |       |       |       | xxxx          |

| C1RXF0SID | 0440          |            |           |        | SID<   | 10:3>                         |        |        |             |                     | SID<2:0> |            | —     | EXIDE | —     | EID<1 | 7:16> | xxxx          |

| C1RXF0EID | 0442          |            |           |        | EID<   | 15:8>                         |        |        |             |                     |          |            | EID<  | 7:0>  |       |       |       | xxxx          |

| C1RXF1SID | 0444          |            | SID<      |        |        | 10:3>                         | 0:3>   |        |             |                     | SID<2:0> |            | —     | EXIDE |       | EID<1 | 7:16> | xxxx          |

© 2009-2012 Microchip Technology Inc.

Legend: x = unknown value on Reset, — = unimplemented, read as '0'. Reset values are shown in hexadecimal for PinHigh devices.

# REGISTER 7-5: IFS0: INTERRUPT FLAG STATUS REGISTER 0 (CONTINUED)

| bit 2 | OC1IF: Output Compare Channel 1 Interrupt Flag Status bit |

|-------|-----------------------------------------------------------|

|       | <ol> <li>Interrupt request has occurred</li> </ol>        |

|       | 0 = Interrupt request has not occurred                    |

| bit 1 | IC1IF: Input Capture Channel 1 Interrupt Flag Status bit  |

|       | 1 = Interrupt request has occurred                        |

|       | 0 = Interrupt request has not occurred                    |

| bit 0 | INTOIF: External Interrupt 0 Flag Status bit              |

|       | 1 = Interrupt request has occurred                        |

|       | 0 = Interrupt request has not occurred                    |

## REGISTER 7-19: IPC4: INTERRUPT PRIORITY CONTROL REGISTER 4

| U-0              | R/W-1                                                                                    | R/W-0                                                    | R/W-0                                              | U-0                | U-0             | U-0             | U-0   |

|------------------|------------------------------------------------------------------------------------------|----------------------------------------------------------|----------------------------------------------------|--------------------|-----------------|-----------------|-------|

| —                |                                                                                          | CNIP<2:0>                                                |                                                    | —                  |                 | —               | —     |

| bit 15           |                                                                                          |                                                          |                                                    |                    |                 |                 | bit 8 |

|                  |                                                                                          | 5444                                                     |                                                    |                    | <b>-</b>        |                 |       |

| U-0              | R/W-1                                                                                    | R/W-0                                                    | R/W-0                                              | U-0                | R/W-1           | R/W-0           | R/W-0 |

|                  |                                                                                          | MI2C1IP<2:0>                                             |                                                    | —                  |                 | SI2C1IP<2:0>    |       |

| bit 7            |                                                                                          |                                                          |                                                    |                    |                 |                 | bit ( |

| Legend:          |                                                                                          |                                                          |                                                    |                    |                 |                 |       |

| R = Readab       | le bit                                                                                   | W = Writable                                             | bit                                                | U = Unimpler       | nented bit, rea | ad as '0'       |       |

| -n = Value a     | t POR                                                                                    | '1' = Bit is set                                         |                                                    | '0' = Bit is cle   |                 | x = Bit is unkr | nown  |

|                  |                                                                                          |                                                          |                                                    |                    |                 |                 |       |

| bit 15           | Unimpleme                                                                                | nted: Read as '                                          | כי                                                 |                    |                 |                 |       |

| bit 14-12        | CNIP<2:0>:                                                                               | Change Notifica                                          | tion Interrupt                                     | t Priority bits    |                 |                 |       |

|                  | 111 = Interru                                                                            | upt is priority 7 (                                      | nighest priori                                     | ty interrupt)      |                 |                 |       |

|                  | •                                                                                        |                                                          |                                                    |                    |                 |                 |       |

|                  | •                                                                                        |                                                          |                                                    |                    |                 |                 |       |

|                  | 001 = Interru                                                                            | upt is priority 1                                        |                                                    |                    |                 |                 |       |

|                  |                                                                                          | upt source is dis                                        | abled                                              |                    |                 |                 |       |

| bit 11-7         | Unimpleme                                                                                | nted: Read as '                                          | o'                                                 |                    |                 |                 |       |

| bit 6-4          | MI2C1IP<2:                                                                               | 0>: I2C1 Master                                          | Events Inter                                       | rupt Priority bits | ;               |                 |       |

|                  | 111 = Interru                                                                            | upt is priority 7 (                                      | highest priori                                     | ty interrupt)      |                 |                 |       |

|                  | •                                                                                        |                                                          |                                                    |                    |                 |                 |       |

|                  | •                                                                                        |                                                          |                                                    |                    |                 |                 |       |

|                  | •                                                                                        |                                                          |                                                    |                    |                 |                 |       |

|                  | •<br>001 = Interru                                                                       | upt is priority 1                                        |                                                    |                    |                 |                 |       |

|                  |                                                                                          | upt is priority 1<br>upt source is dis                   | abled                                              |                    |                 |                 |       |

| bit 3            | 000 = Interru                                                                            |                                                          |                                                    |                    |                 |                 |       |

|                  | 000 = Interru<br>Unimpleme                                                               | upt source is dis                                        | כ'                                                 | pt Priority bits   |                 |                 |       |

|                  | 000 = Interru<br>Unimpleme<br>SI2C1IP<2:0                                                | upt source is dis<br>nted: Read as '                     | o'<br>Events Interru                               |                    |                 |                 |       |

|                  | 000 = Interru<br>Unimpleme<br>SI2C1IP<2:0                                                | upt source is dis<br>nted: Read as '<br>I>: I2C1 Slave E | o'<br>Events Interru                               |                    |                 |                 |       |

|                  | 000 = Interru<br>Unimpleme<br>SI2C1IP<2:0                                                | upt source is dis<br>nted: Read as '<br>I>: I2C1 Slave E | o'<br>Events Interru                               |                    |                 |                 |       |

| bit 3<br>bit 2-0 | 000 = Intern<br>Unimplemen<br>SI2C1IP<2:0<br>111 = Intern<br>•<br>•<br>•<br>001 = Intern | upt source is dis<br>nted: Read as '<br>I>: I2C1 Slave E | <sub>D</sub> '<br>Events Interru<br>nighest priori |                    |                 |                 |       |

## REGISTER 7-32: IPC17: INTERRUPT PRIORITY CONTROL REGISTER 17

|                 | R/W-1              | R/W-0                | R/W-0           | U-0              | R/W-1            | R/W-0           | R/W-0 |

|-----------------|--------------------|----------------------|-----------------|------------------|------------------|-----------------|-------|

| —               |                    | C2TXIP<2:0>          |                 | —                |                  | C1TXIP<2:0>     |       |

| bit 15          |                    |                      |                 |                  |                  |                 | bit 8 |

|                 |                    |                      |                 |                  |                  |                 |       |

| U-0             | R/W-1              | R/W-0                | R/W-0           | U-0              | R/W-1            | R/W-0           | R/W-0 |

|                 |                    | DMA7IP<2:0>          |                 | —                |                  | DMA6IP<2:0>     |       |

| bit 7           |                    |                      |                 |                  |                  |                 | bit   |

| Legend:         |                    |                      |                 |                  |                  |                 |       |

| R = Readable    | bit                | W = Writable I       | bit             | U = Unimple      | mented bit, re   | ad as '0'       |       |

| -n = Value at F | POR                | '1' = Bit is set     |                 | '0' = Bit is cle | eared            | x = Bit is unkn | own   |

| bit 15          | Unimplemer         | nted: Read as 'd     | )'              |                  |                  |                 |       |

| bit 14-12       | -                  | >: ECAN2 Trans       |                 | quest Interrupt  | Priority bits    |                 |       |

|                 |                    | ipt is priority 7 (ł |                 |                  |                  |                 |       |

|                 | •                  |                      |                 |                  |                  |                 |       |

|                 | •                  |                      |                 |                  |                  |                 |       |

|                 | 001 = Interru      | pt is priority 1     |                 |                  |                  |                 |       |

|                 |                    | pt source is disa    | abled           |                  |                  |                 |       |

| bit 11          | Unimplemer         | nted: Read as 'd     | )'              |                  |                  |                 |       |

| bit 10-8        | C1TXIP<2:0         | >: ECAN1 Trans       | smit Data Rec   | quest Interrupt  | Priority bits    |                 |       |

|                 | 111 = Interru      | ipt is priority 7 (ł | nighest priorit | y interrupt)     |                  |                 |       |

|                 | •                  |                      |                 |                  |                  |                 |       |

|                 | •                  |                      |                 |                  |                  |                 |       |

|                 | •<br>001 = Interru | pt is priority 1     |                 |                  |                  |                 |       |

|                 |                    | ipt source is disa   | abled           |                  |                  |                 |       |

| bit 7           | Unimplemer         | nted: Read as 'o     | )'              |                  |                  |                 |       |

| bit 6-4         | DMA7IP<2:0         | >: DMA Channe        | el 7 Data Trar  | nsfer Complete   | e Interrupt Pric | ority bits      |       |

|                 | 111 = Interru      | ıpt is priority 7 (ł | nighest priorit | y interrupt)     |                  |                 |       |

|                 | •                  |                      |                 |                  |                  |                 |       |

|                 | •                  |                      |                 |                  |                  |                 |       |

|                 | •<br>001 = Interru | pt is priority 1     |                 |                  |                  |                 |       |

|                 |                    | ipt source is disa   | abled           |                  |                  |                 |       |

| bit 3           |                    | nted: Read as '0     |                 |                  |                  |                 |       |

| bit 2-0         | DMA6IP<2:0         | >: DMA Channe        | el 6 Data Trar  | nsfer Complete   | e Interrupt Pric | ority bits      |       |

|                 |                    | ipt is priority 7 (h |                 | •                |                  | 5               |       |

|                 | •                  |                      |                 |                  |                  |                 |       |

|                 | •                  |                      |                 |                  |                  |                 |       |

|                 | •<br>001 = Interru | unt in priority 1    |                 |                  |                  |                 |       |

|                 |                    |                      |                 |                  |                  |                 |       |

### REGISTER 8-3: DMAXSTA: DMA CHANNEL x RAM START ADDRESS OFFSET REGISTER A

| R/W-0                                                                | R/W-0 | R/W-0            | R/W-0 | R/W-0            | R/W-0 | R/W-0           | R/W-0 |

|----------------------------------------------------------------------|-------|------------------|-------|------------------|-------|-----------------|-------|

|                                                                      |       |                  | STA   | <15:8>           |       |                 |       |

| bit 15                                                               |       |                  |       |                  |       |                 | bit 8 |

|                                                                      |       |                  |       |                  |       |                 |       |

| R/W-0                                                                | R/W-0 | R/W-0            | R/W-0 | R/W-0            | R/W-0 | R/W-0           | R/W-0 |

|                                                                      |       |                  | STA   | <7:0>            |       |                 |       |

| bit 7                                                                |       |                  |       |                  |       |                 | bit 0 |

|                                                                      |       |                  |       |                  |       |                 |       |

| Legend:                                                              |       |                  |       |                  |       |                 |       |

| R = Readable bit W = Writable bit U = Unimplemented bit, read as '0' |       |                  |       |                  |       |                 |       |

| -n = Value at P                                                      | OR    | '1' = Bit is set |       | '0' = Bit is cle | ared  | x = Bit is unkr | nown  |

bit 15-0 STA<15:0>: Primary DMA RAM Start Address bits (source or destination)

### REGISTER 8-4: DMAxSTB: DMA CHANNEL x RAM START ADDRESS OFFSET REGISTER B

| R/W-0           | R/W-0 | R/W-0            | R/W-0 | R/W-0            | R/W-0           | R/W-0           | R/W-0 |

|-----------------|-------|------------------|-------|------------------|-----------------|-----------------|-------|

|                 |       |                  | STB   | <15:8>           |                 |                 |       |

| bit 15          |       |                  |       |                  |                 |                 | bit 8 |

|                 |       |                  |       |                  |                 |                 |       |

| R/W-0           | R/W-0 | R/W-0            | R/W-0 | R/W-0            | R/W-0           | R/W-0           | R/W-0 |

|                 |       |                  | STE   | 3<7:0>           |                 |                 |       |

| bit 7           |       |                  |       |                  |                 |                 | bit 0 |

| Legend:         |       |                  |       |                  |                 |                 |       |

| R = Readable    | bit   | W = Writable b   | it    | U = Unimpler     | mented bit, rea | ad as '0'       |       |

| -n = Value at P | POR   | '1' = Bit is set |       | '0' = Bit is cle | ared            | x = Bit is unkı | nown  |

bit 15-0 STB<15:0>: Secondary DMA RAM Start Address bits (source or destination)

NOTES:

# 10.2.2 IDLE MODE

Idle mode has these features:

- · The CPU stops executing instructions.

- The WDT is automatically cleared.

- The system clock source remains active. By default, all peripheral modules continue to operate normally from the system clock source, but can also be selectively disabled (see Section 10.4 "Peripheral Module Disable").

- If the WDT or FSCM is enabled, the LPRC also remains active.

The device will wake from Idle mode on any of these events:

- Any interrupt that is individually enabled.

- · Any device Reset.

- A WDT time-out.

On wake-up from Idle, the clock is reapplied to the CPU and instruction execution will begin (2-4 clock cycles later), starting with the instruction following the PWRSAV instruction, or the first instruction in the ISR.

### 10.2.3 INTERRUPTS COINCIDENT WITH POWER SAVE INSTRUCTIONS

Any interrupt that coincides with the execution of a PWRSAV instruction is held off until entry into Sleep or Idle mode has completed. The device then wakes up from Sleep or Idle mode.

# 10.3 Doze Mode

Generally, changing clock speed and invoking one of the power-saving modes are the preferred strategies for reducing power consumption. There may be circumstances, however, where this is not practical. For example, it may be necessary for an application to maintain uninterrupted synchronous communication, even while it is doing nothing else. Reducing system clock speed may introduce communication errors, while using a power-saving mode may stop communications completely.

Doze mode is a simple and effective alternative method to reduce power consumption while the device is still executing code. In this mode, the system clock continues to operate from the same source and at the same speed. Peripheral modules continue to be clocked at the same speed, while the CPU clock speed is reduced. Synchronization between the two clock domains is maintained, allowing the peripherals to access the SFRs while the CPU executes code at a slower rate. Doze mode is enabled by setting the DOZEN bit (CLKDIV<11>). The ratio between peripheral and core clock speed is determined by the DOZE<2:0> bits (CLKDIV<14:12>). There are eight possible configurations, from 1:1 to 1:128, with 1:1 being the default setting.

It is also possible to use Doze mode to selectively reduce power consumption in event-driven applications. This allows clock-sensitive functions, such as synchronous communications, to continue without interruption while the CPU idles, waiting for something to invoke an interrupt routine. Enabling the automatic return to full-speed CPU operation on interrupts is enabled by setting the ROI bit (CLKDIV<15>). By default, interrupt events have no effect on Doze mode operation.

For example, suppose the device is operating at 20 MIPS and the CAN module has been configured for 500 kbps based on this device operating speed. If the device is now placed in Doze mode with a clock frequency ratio of 1:4, the CAN module continues to communicate at the required bit rate of 500 kbps, but the CPU now starts executing instructions at a frequency of 5 MIPS.

# 10.4 Peripheral Module Disable

The Peripheral Module Disable (PMD) registers provide a method to disable a peripheral module by stopping all clock sources supplied to that module. When a peripheral is disabled via the appropriate PMD control bit, the peripheral is in a minimum power consumption state. The control and status registers associated with the peripheral are also disabled, so writes to those registers will have no effect and read values will be invalid.

A peripheral module is only enabled if both the associated bit in the PMD register is cleared and the peripheral is supported by the specific dsPIC<sup>®</sup> DSC variant. If the peripheral is present in the device, it is enabled in the PMD register by default.

Note: If a PMD bit is set, the corresponding module is disabled after a delay of 1 instruction cycle. Similarly, if a PMD bit is cleared, the corresponding module is enabled after a delay of 1 instruction cycle (assuming the module control registers are already configured to enable module operation).

### REGISTER 17-3: I2CxMSK: I2Cx SLAVE MODE ADDRESS MASK REGISTER

| U-0          | U-0   | U-0          | U-0   | U-0          | U-0              | R/W-0  | R/W-0 |

|--------------|-------|--------------|-------|--------------|------------------|--------|-------|

| _            | —     | —            | _     | _            | —                | AMSK9  | AMSK8 |

| bit 15       |       |              |       |              |                  |        | bit 8 |

|              |       |              |       |              |                  |        |       |

| R/W-0        | R/W-0 | R/W-0        | R/W-0 | R/W-0        | R/W-0            | R/W-0  | R/W-0 |

| AMSK7        | AMSK6 | AMSK5        | AMSK4 | AMSK3        | AMSK2            | AMSK1  | AMSK0 |

| bit 7        |       |              |       |              |                  |        | bit 0 |

|              |       |              |       |              |                  |        |       |

| Legend:      |       |              |       |              |                  |        |       |

| R = Readable | bit   | W = Writable | bit   | U = Unimplei | mented bit, read | as '0' |       |

-n = Value at POR (1' = Bit is set (0' = Bit is cleared x = Bit is unknown)

bit 15-10 Unimplemented: Read as '0'

bit 9-0

AMSKx: Mask for Address Bit x Select bit

1 = Enable masking for bit x of incoming message address; bit match not required in this position

0 = Disable masking for bit x; bit match required in this position

## REGISTER 19-2: CiCTRL2: ECAN™ MODULE CONTROL REGISTER 2

| U-0           | U-0                | U-0                               | U-0             | U-0              | U-0              | U-0             | U-0   |  |  |  |  |

|---------------|--------------------|-----------------------------------|-----------------|------------------|------------------|-----------------|-------|--|--|--|--|

| _             | _                  | _                                 |                 | _                | —                |                 | —     |  |  |  |  |

| bit 15        |                    | ·                                 |                 |                  | •                |                 | bit 8 |  |  |  |  |

|               |                    |                                   |                 |                  |                  |                 |       |  |  |  |  |

| U-0           | U-0                | U-0                               | R-0             | R-0              | R-0              | R-0             | R-0   |  |  |  |  |

| _             | —                  | _                                 |                 |                  | DNCNT<4:0>       | :0>             |       |  |  |  |  |

| bit 7         |                    |                                   |                 |                  |                  |                 | bit 0 |  |  |  |  |

|               |                    |                                   |                 |                  |                  |                 |       |  |  |  |  |

| Legend:       |                    |                                   |                 |                  |                  |                 |       |  |  |  |  |

| R = Readable  | e bit              | W = Writable                      | bit             | U = Unimpler     | mented bit, read | as '0'          |       |  |  |  |  |

| -n = Value at | POR                | '1' = Bit is set                  | :               | '0' = Bit is cle | ared             | x = Bit is unkr | nown  |  |  |  |  |

|               |                    |                                   |                 |                  |                  |                 |       |  |  |  |  |

| bit 15-5      | Unimplemen         | ted: Read as '                    | 0'              |                  |                  |                 |       |  |  |  |  |

| bit 4-0       | DNCNT<4:0>         | •: DeviceNet™                     | Filter Bit Num  | ber bits         |                  |                 |       |  |  |  |  |

|               | 10010-1111         | 1 = Invalid sel                   | ection          |                  |                  |                 |       |  |  |  |  |

|               | 10001 <b>= Con</b> | npare up to dat                   | a byte 3, bit 6 | with EID<17>     |                  |                 |       |  |  |  |  |

|               | •                  |                                   |                 |                  |                  |                 |       |  |  |  |  |

|               | •                  |                                   |                 |                  |                  |                 |       |  |  |  |  |

|               | •                  |                                   |                 |                  |                  |                 |       |  |  |  |  |

|               |                    | npare up to dat<br>not compare da |                 | with EID<0>      |                  |                 |       |  |  |  |  |

|               |                    |                                   |                 |                  |                  |                 |       |  |  |  |  |

| U-0           | U-0             | R-0                                        | R-0             | R-0              | R-0             | R-0             | R-0   |

|---------------|-----------------|--------------------------------------------|-----------------|------------------|-----------------|-----------------|-------|

|               |                 | ТХВО                                       | TXBP            | RXBP             | TXWAR           | RXWAR           | EWARN |

| bit 15        |                 |                                            |                 |                  |                 |                 | bit 8 |

|               |                 |                                            |                 |                  |                 |                 |       |

| R/C-0         | R/C-0           | R/C-0                                      | U-0             | R/C-0            | R/C-0           | R/C-0           | R/C-0 |

| IVRIF         | WAKIF           | ERRIF                                      |                 | FIFOIF           | RBOVIF          | RBIF            | TBIF  |

| bit 7         |                 |                                            |                 |                  |                 |                 | bit ( |

|               |                 |                                            |                 |                  |                 |                 |       |

| Legend:       |                 | C = Clear on                               | y bit           |                  |                 |                 |       |

| R = Readable  | e bit           | W = Writable                               | bit             | U = Unimplei     | mented bit, rea | d as '0'        |       |

| -n = Value at | POR             | '1' = Bit is set                           | t               | '0' = Bit is cle | eared           | x = Bit is unkr | nown  |

| bit 15-14     | Unimplomon      | ted. Dood oo '                             | 0'              |                  |                 |                 |       |

| bit 13        | -               | i <b>ted:</b> Read as '<br>mitter in Error |                 | hit              |                 |                 |       |

| bit 15        |                 | er is in Bus Of                            |                 | bit              |                 |                 |       |

|               | 0 = Transmitt   | er is not in Bus                           | s Off state     |                  |                 |                 |       |

| bit 12        |                 | mitter in Error                            |                 | sive bit         |                 |                 |       |

|               |                 | er is in Bus Pa                            |                 | _                |                 |                 |       |

| bit 11        |                 | er is not in Bus<br>ver in Error Sta       |                 |                  |                 |                 |       |

|               |                 | is in Bus Pass                             |                 | vebil            |                 |                 |       |

|               | 0 = Receiver    | is not in Bus P                            | assive state    |                  |                 |                 |       |

| bit 10        |                 | nsmitter in Erro                           |                 | ng bit           |                 |                 |       |

|               |                 | er is in Error W                           |                 |                  |                 |                 |       |

| bit 9         |                 | er is not in Error                         | -               |                  |                 |                 |       |

| DIL 9         |                 | ceiver in Error<br>is in Error War         | -               | DIL              |                 |                 |       |

|               |                 | is not in Error                            |                 |                  |                 |                 |       |

| bit 8         | EWARN: Trai     | nsmitter or Red                            | ceiver in Error | State Warning    | bit             |                 |       |

|               |                 | er or receiver i                           |                 | 0                |                 |                 |       |

| <b>b</b> # 7  |                 | er or receiver i                           |                 | •                |                 |                 |       |

| bit 7         |                 | I Message Rec<br>request has oc            |                 | of Flag bit      |                 |                 |       |

|               | •               | request has no                             |                 |                  |                 |                 |       |

| bit 6         | WAKIF: Bus      | Wake-up Activ                              | ity Interrupt F | ag bit           |                 |                 |       |

|               |                 | request has oc                             |                 |                  |                 |                 |       |

| 64 F          | •               | request has no                             |                 |                  |                 | h =)            |       |

| bit 5         |                 |                                            |                 | ources in Clin   | F<13:8> regist  | (er)            |       |

|               |                 | request has oc<br>request has no           |                 |                  |                 |                 |       |

| bit 4         | -               | ted: Read as '                             |                 |                  |                 |                 |       |

| bit 3         | •               | Almost Full In                             |                 | it               |                 |                 |       |

|               | 1 = Interrupt i | request has oc                             | curred          |                  |                 |                 |       |

|               | •               | request has no                             |                 |                  |                 |                 |       |

| bit 2         |                 | Buffer Overflo                             | •               | ag bit           |                 |                 |       |

|               |                 | request has oc<br>request has no           |                 |                  |                 |                 |       |

| bit 1         |                 | ffer Interrupt F                           |                 |                  |                 |                 |       |

|               |                 | request has oc                             |                 |                  |                 |                 |       |

|               |                 | request has no                             |                 |                  |                 |                 |       |

| 1.1.0         | TDIE. TV Duf    |                                            |                 |                  |                 |                 |       |

| bit 0         |                 | fer Interrupt Fla                          |                 |                  |                 |                 |       |

| DIT U         | 1 = Interrupt i | request has oc<br>request has no           | curred          |                  |                 |                 |       |

### REGISTER 20-4: ADxCON4: ADCx CONTROL REGISTER 4

| U-0                                                                  | U-0 | U-0              | U-0 | U-0              | U-0   | U-0             | U-0   |

|----------------------------------------------------------------------|-----|------------------|-----|------------------|-------|-----------------|-------|

| —                                                                    | —   | —                | _   | —                | —     | —               | —     |

| bit 15                                                               |     |                  |     |                  |       |                 | bit 8 |

|                                                                      |     |                  |     |                  |       |                 |       |

| U-0                                                                  | U-0 | U-0              | U-0 | U-0              | R/W-0 | R/W-0           | R/W-0 |

| —                                                                    | _   | —                | _   | —                |       | DMABL<2:0>      |       |

| bit 7                                                                |     |                  |     |                  |       |                 | bit 0 |

|                                                                      |     |                  |     |                  |       |                 |       |

| Legend:                                                              |     |                  |     |                  |       |                 |       |

| R = Readable bit W = Writable bit U = Unimplemented bit, read as '0' |     |                  |     |                  |       |                 |       |

| -n = Value at P                                                      | POR | '1' = Bit is set |     | '0' = Bit is cle | eared | x = Bit is unkr | nown  |

### bit 15-3 Unimplemented: Read as '0'

bit 2-0

DMABL<2:0>: Selects Number of DMA Buffer Locations per Analog Input bits

111 = Allocates 128 words of buffer to each analog input

110 = Allocates 64 words of buffer to each analog input

101 = Allocates 32 words of buffer to each analog input

100 = Allocates 16 words of buffer to each analog input

011 = Allocates 8 words of buffer to each analog input

010 = Allocates 4 words of buffer to each analog input

001 = Allocates 2 words of buffer to each analog input

000 = Allocates 1 word of buffer to each analog input

# **REGISTER 20-9:** AD1PCFGH: ADC1 PORT CONFIGURATION REGISTER HIGH<sup>(1,2,3,4)</sup>

| R/W-0  |

|--------|--------|--------|--------|--------|--------|--------|--------|

| PCFG31 | PCFG30 | PCFG29 | PCFG28 | PCFG27 | PCFG26 | PCFG25 | PCFG24 |

| bit 15 | -      |        |        |        |        |        | bit 8  |

|        |        |        |        |        |        |        |        |

| R/W-0  |

| R/W-0  |

|--------|--------|--------|--------|--------|--------|--------|--------|

| PCFG23 | PCFG22 | PCFG21 | PCFG20 | PCFG19 | PCFG18 | PCFG17 | PCFG16 |

| bit 7  |        |        |        |        |        |        | bit 0  |

| Legend:           |                  |                             |                    |

|-------------------|------------------|-----------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, read | d as 'O'           |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared        | x = Bit is unknown |

bit 15-0 **PCFG<31:16>:** ADC Port Configuration Control bits

1 = Port pin in Digital mode, port read input enabled, ADC input multiplexer connected to AVss

0 = Port pin in Analog mode, port read input disabled, ADC samples pin voltage

- **Note 1:** On devices without 32 analog inputs, all PCFG bits are R/W by user. However, PCFG bits are ignored on ports without a corresponding input on device.

- 2: ADC2 only supports analog inputs AN0-AN15; therefore, no ADC2 high port Configuration register exists.

- **3:** PCFGx = ANx, where x = 16 through 31.

- **4:** PCFGx bits will have no effect if ADC module is disabled by setting ADxMD bit in the PMDx register. In this case all port pins multiplexed with ANx will be in Digital mode.

| TABLE 21-2: | CONFIGURATION BITS DESCRIPTION |                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |  |

|-------------|--------------------------------|----------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| Bit Field   | Register                       | RTSP<br>Effect | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |  |

| BWRP        | FBS                            | Immediate      | Boot Segment Program Flash Write Protection<br>1 = Boot segment may be written<br>0 = Boot segment is write-protected                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |  |

| BSS<2:0>    | FBS                            | Immediate      | <ul> <li>Boot Segment Program Flash Code Protection Size</li> <li>X11 = No Boot program Flash segment</li> <li>Boot space is 1K IW less VS</li> <li>110 = Standard security; boot program Flash segment starts at End of VS, ends at 0x0007FE</li> <li>010 = High security; boot program Flash segment starts at End of VS, ends at 0x0007FE</li> <li>Boot space is 4K IW less VS</li> <li>101 = Standard security; boot program Flash segment starts at End of VS, ends at 0x001FFE</li> <li>001 = High security; boot program Flash segment starts at End of VS, ends at 0x001FFE</li> <li>001 = High security; boot program Flash segment starts at End of VS, ends at 0x001FFE</li> <li>Boot space is 8K IW less VS</li> </ul> |  |

|             |                                |                | <ul> <li>100 = Standard security; boot program Flash segment starts at End of VS, ends at 0x003FFE</li> <li>000 = High security; boot program Flash segment starts at End of VS, ends at 0x003FFE</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |  |

| RBS<1:0>    | FBS                            | Immediate      | Boot Segment RAM Code Protection<br>11 = No Boot RAM defined<br>10 = Boot RAM is 128 Bytes<br>01 = Boot RAM is 256 Bytes<br>00 = Boot RAM is 1024 Bytes                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |  |

| SWRP        | FSS                            | Immediate      | Secure Segment Program Flash Write Protection<br>1 = Secure segment may be written<br>0 = Secure segment is write-protected                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |  |

### TABLE 21-2: CONFIGURATION BITS DESCRIPTION

NOTES:

| CHARAG          | AC<br>CTERISTICS | Standard Operating Conditions: 3.0V to 3.6V (unless otherwise stated)Operating temperature $-40^{\circ}C \le TA \le +150^{\circ}C$ for High Temperature |     |     |     |       |            |  |

|-----------------|------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------|-----|-----|-----|-------|------------|--|

| Param<br>No.    | Symbol           | Characteristic                                                                                                                                          | Min | Тур | Max | Units | Conditions |  |

|                 | Clock Parameters |                                                                                                                                                         |     |     |     |       |            |  |

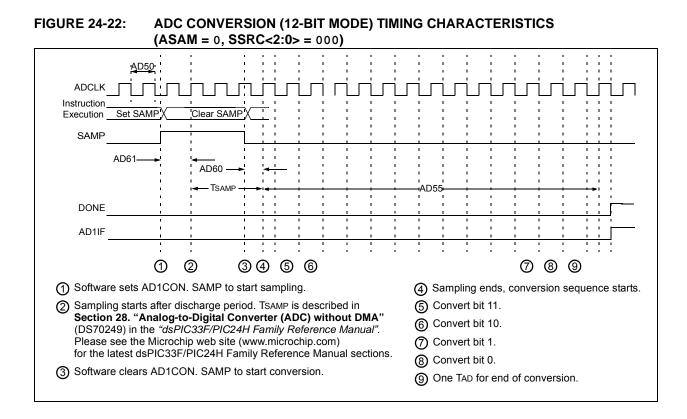

| HAD50           | TAD              | ADC Clock Period <sup>(1)</sup>                                                                                                                         | 147 |     |     | ns    | —          |  |

| Conversion Rate |                  |                                                                                                                                                         |     |     |     |       |            |  |

|                 |                  | 001                                                                                                                                                     |     |     |     |       |            |  |

### TABLE 25-17: ADC CONVERSION (12-BIT MODE) TIMING REQUIREMENTS

Note 1: These parameters are characterized but not tested in manufacturing.

# TABLE 25-18: ADC CONVERSION (10-BIT MODE) TIMING REQUIREMENTS

| AC<br>CHARACTERISTICS |                                                                    | Standard Operating Conditions: 3.0V to 3.6V (unless otherwise stated)Operating temperature $-40^{\circ}C \le TA \le +150^{\circ}C$ for High Temperature |     |     |     |       |            |  |

|-----------------------|--------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------|-----|-----|-----|-------|------------|--|

| Param<br>No.          | Symbol                                                             | Characteristic                                                                                                                                          | Min | Тур | Max | Units | Conditions |  |

| Clock Parameters      |                                                                    |                                                                                                                                                         |     |     |     |       |            |  |

| HAD50                 | Tad                                                                | ADC Clock Period <sup>(1)</sup>                                                                                                                         | 104 | _   |     | ns    | _          |  |

| Conversion Rate       |                                                                    |                                                                                                                                                         |     |     |     |       |            |  |

| HAD56                 | FCNV                                                               | Throughput Rate <sup>(1)</sup>                                                                                                                          |     |     | 800 | Ksps  | _          |  |

|                       | These permeters are characterized but not tested in mean feet wing |                                                                                                                                                         |     |     |     |       |            |  |

**Note 1:** These parameters are characterized but not tested in manufacturing.

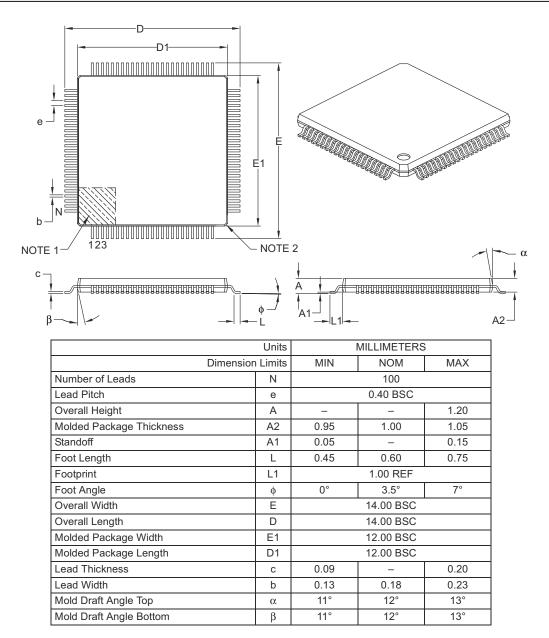

# 100-Lead Plastic Thin Quad Flatpack (PT) – 12x12x1 mm Body, 2.00 mm Footprint [TQFP]

**Note:** For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

#### Notes:

1. Pin 1 visual index feature may vary, but must be located within the hatched area.

2. Chamfers at corners are optional; size may vary.

3. Dimensions D1 and E1 do not include mold flash or protrusions. Mold flash or protrusions shall not exceed 0.25 mm per side.

- 4. Dimensioning and tolerancing per ASME Y14.5M.

- BSC: Basic Dimension. Theoretically exact value shown without tolerances.

REF: Reference Dimension, usually without tolerance, for information purposes only.

Microchip Technology Drawing C04-100B

# APPENDIX B: REVISION HISTORY

# Revision A (April 2009)

This is the initial released version of the document.

# **Revision B (October 2009)**

The revision includes the following global update:

Added Note 2 to the shaded table that appears at the beginning of each chapter. This new note provides information regarding the availability of registers and their associated bits

This revision also includes minor typographical and formatting changes throughout the data sheet text.

All other major changes are referenced by their respective section in the following table.

### TABLE B-1:MAJOR SECTION UPDATES

| Section Name                                                         | Update Description                                                                                                                                          |

|----------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------|

| "High-Performance, 16-bit<br>Microcontrollers"                       | Added information on high temperature operation (see <b>"Operating Range:</b> ").                                                                           |

| Section 10.0 "Power-Saving Features"                                 | Updated the last paragraph to clarify the number of cycles that occur prior to the start of instruction execution (see <b>Section 10.2.2 "Idle Mode"</b> ). |

| Section 11.0 "I/O Ports"                                             | Changed the reference to digital-only pins to 5V tolerant pins in the second paragraph of <b>Section 11.2</b> " <b>Open-Drain Configuration</b> ".          |

| Section 18.0 "Universal Asynchronous<br>Receiver Transmitter (UART)" | Updated the two baud rate range features to: 10 Mbps to 38 bps at 40 MIPS.                                                                                  |

| Section 20.0 "10-bit/12-bit Analog-to-Digital Converter (ADC)"       | Updated the ADCx block diagram (see Figure 20-1).                                                                                                           |

| Section 21.0 "Special Features"                                      | Updated the second paragraph and removed the fourth paragraph in <b>Section 21.1 "Configuration Bits"</b> .                                                 |

|                                                                      | Updated the Device Configuration Register Map (see Table 21-1).                                                                                             |

| Section 24.0 "Electrical Characteristics"                            | Updated the Absolute Maximum Ratings for high temperature and added Note 4.                                                                                 |

|                                                                      | Updated Power-Down Current parameters DC60d, DC60a, DC60b, and DC60d (see Table 24-7).                                                                      |

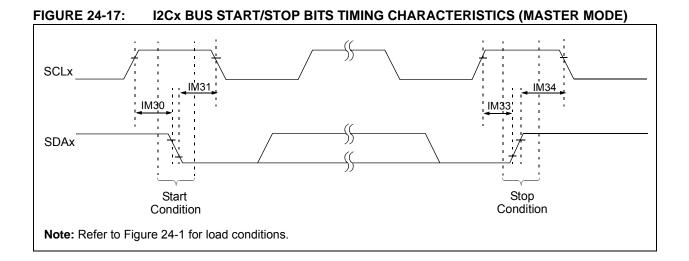

|                                                                      | Added I2Cx Bus Data Timing Requirements (Master Mode) parameter IM51 (see Table 24-36).                                                                     |

|                                                                      | Updated the SPIx Module Slave Mode (CKE = 1) Timing<br>Characteristics (see Figure 24-12).                                                                  |

|                                                                      | Updated the Internal LPRC Accuracy parameters (see Table 24-18 and Table 24-19).                                                                            |

|                                                                      | Updated the ADC Module Specifications (12-bit Mode) parameters AD23a and AD24a (see Table 24-40).                                                           |

|                                                                      | Updated the ADC Module Specifications (10-bit Mode) parameters AD23b and AD24b (see Table 24-41).                                                           |

| Section 25.0 "High Temperature Electrical Characteristics"           | Added new chapter with high temperature specifications.                                                                                                     |

| "Product Identification System"                                      | Added the "H" definition for high temperature.                                                                                                              |