Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFI

| Details                    |                                                                                 |

|----------------------------|---------------------------------------------------------------------------------|

| Product Status             | Obsolete                                                                        |

| Core Processor             | PIC                                                                             |

| Core Size                  | 16-Bit                                                                          |

| Speed                      | 40 MIPs                                                                         |

| Connectivity               | I²C, IrDA, LINbus, SPI, UART/USART                                              |

| Peripherals                | Brown-out Detect/Reset, DMA, POR, PWM, WDT                                      |

| Number of I/O              | 85                                                                              |

| Program Memory Size        | 64KB (22K x 24)                                                                 |

| Program Memory Type        | FLASH                                                                           |

| EEPROM Size                | -                                                                               |

| RAM Size                   | 8K x 8                                                                          |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 3.6V                                                                       |

| Data Converters            | A/D 32x10b/12b                                                                  |

| Oscillator Type            | Internal                                                                        |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                               |

| Mounting Type              | Surface Mount                                                                   |

| Package / Case             | 100-TQFP                                                                        |

| Supplier Device Package    | 100-TQFP (14x14)                                                                |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic24hj64gp210at-i-pf |

|                            |                                                                                 |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

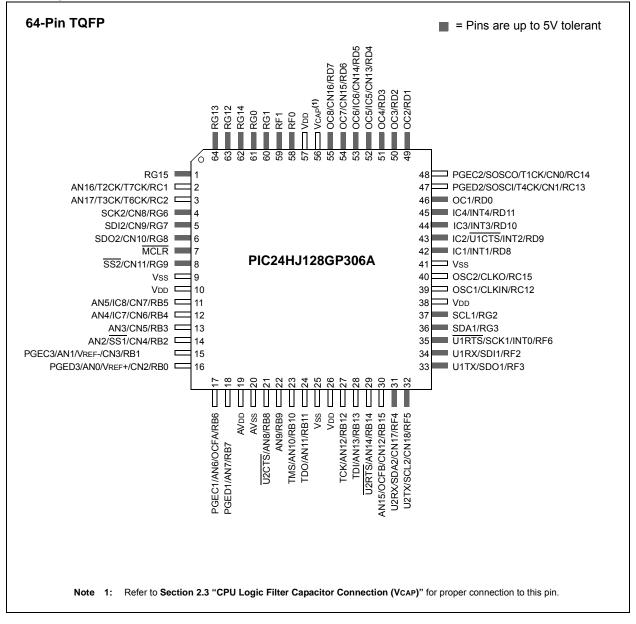

# Pin Diagrams (Continued)

| IADLE 4-2  | I. E |         | EGISTE   |         |                   | ZUIKL   |           |          |        |          | 230GF    |        | EVICE                        | 3 UNLI    |          |         |        |               |

|------------|------|---------|----------|---------|-------------------|---------|-----------|----------|--------|----------|----------|--------|------------------------------|-----------|----------|---------|--------|---------------|

| File Name  | Addr | Bit 15  | Bit 14   | Bit 13  | Bit 12            | Bit 11  | Bit 10    | Bit 9    | Bit 8  | Bit 7    | Bit 6    | Bit 5  | Bit 4                        | Bit 3     | Bit 2    | Bit 1   | Bit 0  | All<br>Resets |

| C2CTRL1    | 0500 | _       | _        | CSIDL   | ABAT              | —       | RE        | EQOP<2:0 | >      | OPN      | /ODE<2:0 | >      | —                            | CANCAP    | _        | —       | WIN    | 0480          |

| C2CTRL2    | 0502 | _       | _        | _       | _                 | _       | _         | _        | _      | _        | _        | _      |                              | C         | NCNT<4:  | )>      |        | 0000          |

| C2VEC      | 0504 | _       | _        | _       |                   | FI      | LHIT<4:0> |          |        | _        |          |        |                              | ICODE<6:0 | 0>       |         |        | 0000          |

| C2FCTRL    | 0506 | C       | MABS<2:0 | >       | —                 | _       | _         | _        | —      | —        | _        | —      |                              |           | FSA<4:0> |         |        | 0000          |

| C2FIFO     | 0508 | _       | _        |         |                   | FBP<5   | :0>       |          |        | _        | _        |        |                              | FNRE      | 3<5:0>   |         |        | 0000          |

| C2INTF     | 050A | _       | _        | TXBO    | TXBP              | RXBP    | TXWAR     | RXWAR    | EWARN  | IVRIF    | WAKIF    | ERRIF  | _                            | FIFOIF    | RBOVIF   | RBIF    | TBIF   | 0000          |

| C2INTE     | 050C | _       | _        | _       | _                 | _       | _         | _        | _      | IVRIE    | WAKIE    | ERRIE  | _                            | FIFOIE    | RBOVIE   | RBIE    | TBIE   | 0000          |

| C2EC       | 050E |         |          |         | TERRCN            | Γ<7:0>  |           |          |        |          |          |        | RERRC                        | NT<7:0>   |          |         |        | 0000          |

| C2CFG1     | 0510 | _       | _        | _       | _                 | _       | _         | _        | _      | SJW<1    | 1:0>     |        |                              | BRP       | <5:0>    |         |        | 0000          |

| C2CFG2     | 0512 | _       | WAKFIL   | _       | _                 | _       | SE        | G2PH<2:0 | )>     | SEG2PHTS | SAM      | SI     | EG1PH<2                      | :0>       | F        | RSEG<2: | 0>     | 0000          |

| C2FEN1     | 0514 | FLTEN15 | FLTEN14  | FLTEN13 | FLTEN12           | FLTEN11 | FLTEN10   | FLTEN9   | FLTEN8 | FLTEN7   | FLTEN6   | FLTEN5 | FLTEN4                       | FLTEN3    | FLTEN2   | FLTEN1  | FLTEN0 | FFFF          |

| C2FMSKSEL1 | 0518 | F7MS    | <<1:0>   | F6MSI   | <b>&lt;</b> <1:0> | F5MSł   | <<1:0>    | F4MS     | <<1:0> | F3MSK<   | <1:0>    | F2MSH  | <1:0> F1MSK<1:0> F0MSK<1:0>  |           |          |         | 0000   |               |

| C2FMSKSEL2 | 051A | F15MS   | K<1:0>   | F14MS   | K<1:0>            | F13MS   | K<1:0>    | F12MS    | K<1:0> | F11MSK   | <1:0>    | F10MS  | K<1:0> F9MSK<1:0> F8MSK<1:0> |           |          |         | 0000   |               |

#### TABLE 4-21: ECAN2 REGISTER MAP WHEN C2CTRL1.WIN = 0 OR 1 FOR PIC24HJ256GP610A DEVICES ONLY

Legend: - = unimplemented, read as '0'. Reset values are shown in hexadecimal for PinHigh devices.

#### TABLE 4-22: ECAN2 REGISTER MAP WHEN C2CTRL1.WIN = 0 FOR PIC24HJ256GP610A DEVICES ONLY

| File Name | Addr          | Bit 15  | Bit 14      | Bit 13      | Bit 12     | Bit 11     | Bit 10  | Bit 9   | Bit 8       | Bit 7     | Bit 6       | Bit 5       | Bit 4      | Bit 3      | Bit 2   | Bit 1   | Bit 0   | All<br>Resets |

|-----------|---------------|---------|-------------|-------------|------------|------------|---------|---------|-------------|-----------|-------------|-------------|------------|------------|---------|---------|---------|---------------|

|           | 0500-<br>051E |         |             |             |            |            |         | See     | edefinition | when WIN  | = x         |             |            |            |         |         |         |               |

| C2RXFUL1  | 0520          | RXFUL15 | RXFUL14     | RXFUL13     | RXFUL12    | RXFUL11    | RXFUL10 | RXFUL9  | RXFUL8      | RXFUL7    | RXFUL6      | RXFUL5      | RXFUL4     | RXFUL3     | RXFUL2  | RXFUL1  | RXFUL0  | 0000          |

| C2RXFUL2  | 0522          | RXFUL31 | RXFUL30     | RXFUL29     | RXFUL28    | RXFUL27    | RXFUL26 | RXFUL25 | RXFUL24     | RXFUL23   | RXFUL22     | RXFUL21     | RXFUL20    | RXFUL19    | RXFUL18 | RXFUL17 | RXFUL16 | 0000          |

| C2RXOVF1  | 0528          | RXOVF15 | RXOVF14     | RXOVF13     | RXOVF12    | RXOVF11    | RXOVF10 | RXOVF09 | RXOVF08     | RXOVF7    | RXOVF6      | RXOVF5      | RXOVF4     | RXOVF3     | RXOVF2  | RXOVF1  | RXOVF0  | 0000          |

| C2RXOVF2  | 052A          | RXOVF31 | RXOVF30     | RXOVF29     | RXOVF28    | RXOVF27    | RXOVF26 | RXOVF25 | RXOVF24     | RXOVF23   | RXOVF22     | RXOVF21     | RXOVF20    | RXOVF19    | RXOVF18 | RXOVF17 | RXOVF16 | 0000          |

| C2TR01CON | 0530          | TXEN1   | TX<br>ABAT1 | TX<br>LARB1 | TX<br>ERR1 | TX<br>REQ1 | RTREN1  | TX1PF   | l<1:0>      | TXEN0     | TX<br>ABAT0 | TX<br>LARB0 | TX<br>ERR0 | TX<br>REQ0 | RTREN0  | TX0PR   | l<1:0>  | 0000          |

| C2TR23CON | 0532          | TXEN3   | TX<br>ABAT3 | TX<br>LARB3 | TX<br>ERR3 | TX<br>REQ3 | RTREN3  | TX3PF   | l<1:0>      | TXEN2     | TX<br>ABAT2 | TX<br>LARB2 | TX<br>ERR2 | TX<br>REQ2 | RTREN2  | TX2PR   | <1:0>   | 0000          |

| C2TR45CON | 0534          | TXEN5   | TX<br>ABAT5 | TX<br>LARB5 | TX<br>ERR5 | TX<br>REQ5 | RTREN5  | TX5PF   | l<1:0>      | TXEN4     | TX<br>ABAT4 | TX<br>LARB4 | TX<br>ERR4 | TX<br>REQ4 | RTREN4  | TX4PR   | l<1:0>  | 0000          |

| C2TR67CON | 0536          | TXEN7   | TX<br>ABAT7 | TX<br>LARB7 | TX<br>ERR7 | TX<br>REQ7 | RTREN7  | TX7PF   | l<1:0>      | TXEN6     | TX<br>ABAT6 | TX<br>LARB6 | TX<br>ERR6 | TX<br>REQ6 | RTREN6  | TX6PR   | l<1:0>  | xxxx          |

| C2RXD     | 0540          |         |             |             |            |            |         |         | Recieved    | Data Word |             |             |            |            |         |         |         | xxxx          |

| C2TXD     | 0542          |         |             |             |            |            |         |         | Transmit [  | Data Word |             |             |            |            |         |         |         | xxxx          |

PIC24HJXXXGPX06A/X08A/X10A

# TABLE 4-28: PORTE REGISTER MAP<sup>(1)</sup>

| File Name | Addr | Bit 15 | Bit 14 | Bit 13 | Bit 12 | Bit 11 | Bit 10 | Bit 9 | Bit 8 | Bit 7  | Bit 6  | Bit 5  | Bit 4  | Bit 3  | Bit 2  | Bit 1  | Bit 0  | All<br>Resets |

|-----------|------|--------|--------|--------|--------|--------|--------|-------|-------|--------|--------|--------|--------|--------|--------|--------|--------|---------------|

| TRISE     | 02D8 | —      | _      |        | _      | _      | _      | _     |       | TRISE7 | TRISE6 | TRISE5 | TRISE4 | TRISE3 | TRISE2 | TRISE1 | TRISE0 | OOFF          |

| PORTE     | 02DA | _      | -      | _      | _      | -      | -      |       | _     | RE7    | RE6    | RE5    | RE4    | RE3    | RE2    | RE1    | RE0    | xxxx          |

| LATE      | 02DC | _      | _      | _      | _      | _      | _      | _     | -     | LATE7  | LATE6  | LATE5  | LATE4  | LATE3  | LATE2  | LATE1  | LATE0  | xxxx          |

Legend: x = unknown value on Reset, - = unimplemented, read as '0'. Reset values are shown in hexadecimal for PinHigh devices.

Note 1: The actual set of I/O port pins varies from one device to another. Please refer to the corresponding pinout diagrams.

# TABLE 4-29: PORTF REGISTER MAP<sup>(1)</sup>

| File Name           | Addr | Bit 15 | Bit 14 | Bit 13  | Bit 12  | Bit 11 | Bit 10 | Bit 9 | Bit 8  | Bit 7  | Bit 6  | Bit 5  | Bit 4  | Bit 3  | Bit 2  | Bit 1  | Bit 0  | All Resets |

|---------------------|------|--------|--------|---------|---------|--------|--------|-------|--------|--------|--------|--------|--------|--------|--------|--------|--------|------------|

| TRISF               | 02DE | _      | _      | TRISF13 | TRISF12 | —      | _      | _     | TRISF8 | TRISF7 | TRISF6 | TRISF5 | TRISF4 | TRISF3 | TRISF2 | TRISF1 | TRISF0 | 31FF       |

| PORTF               | 02E0 | _      | _      | RF13    | RF12    | —      | _      | -     | RF8    | RF7    | RF6    | RF5    | RF4    | RF3    | RF2    | RF1    | RF0    | xxxx       |

| LATF                | 02E2 | _      | _      | LATF13  | LATF12  | _      | _      | _     | LATF8  | LATF7  | LATF6  | LATF5  | LATF4  | LATF3  | LATF2  | LATF1  | LATF0  | xxxx       |

| ODCF <sup>(2)</sup> | 06DE | -      | -      | ODCF13  | ODCF12  |        | -      |       | ODCF8  | ODCF7  | ODCF6  | ODCF5  | ODCF4  | ODCF3  | ODCF2  | ODCF1  | ODCF0  | 0000       |

Legend: x = unknown value on Reset, — = unimplemented, read as '0'. Reset values are shown in hexadecimal for PinHigh devices.

Note 1: The actual set of I/O port pins varies from one device to another. Please refer to the corresponding pinout diagrams.

# TABLE 4-30: PORTG REGISTER MAP<sup>(1)</sup>

| File Name           | Addr | Bit 15  | Bit 14  | Bit 13  | Bit 12  | Bit 11 | Bit 10 | Bit 9  | Bit 8  | Bit 7  | Bit 6  | Bit 5 | Bit 4 | Bit 3  | Bit 2  | Bit 1  | Bit 0  | All<br>Resets |

|---------------------|------|---------|---------|---------|---------|--------|--------|--------|--------|--------|--------|-------|-------|--------|--------|--------|--------|---------------|

| TRISG               | 02E4 | TRISG15 | TRISG14 | TRISG13 | TRISG12 | _      | _      | TRISG9 | TRISG8 | TRISG7 | TRISG6 | _     |       | TRISG3 | TRISG2 | TRISG1 | TRISG0 | F3CF          |

| PORTG               | 02E6 | RG15    | RG14    | RG13    | RG12    | _      | -      | RG9    | RG8    | RG7    | RG6    | _     | _     | RG3    | RG2    | RG1    | RG0    | xxxx          |

| LATG                | 02E8 | LATG15  | LATG14  | LATG13  | LATG12  | _      | -      | LATG9  | LATG8  | LATG7  | LATG6  | _     | _     | LATG3  | LATG2  | LATG1  | LATG0  | xxxx          |

| ODCG <sup>(2)</sup> | 06E4 | ODCG15  | ODCG14  | ODCG13  | ODCG12  | -      | _      | ODCG9  | ODCG8  | ODCG7  | ODCG6  | _     | -     | ODCG3  | ODCG2  | ODCG1  | ODCG0  | 0000          |

Legend: x = unknown value on Reset, - = unimplemented, read as '0'. Reset values are shown in hexadecimal for PinHigh devices.

**Note** 1: The actual set of I/O port pins varies from one device to another. Please refer to the corresponding pinout diagrams.

| Addressing Mode                        | Description                                                                                            |

|----------------------------------------|--------------------------------------------------------------------------------------------------------|

| File Register Direct                   | The address of the file register is specified explicitly.                                              |

| Register Direct                        | The contents of a register are accessed directly.                                                      |

| Register Indirect                      | The contents of Wn forms the EA.                                                                       |

| Register Indirect Post-Modified        | The contents of Wn forms the EA. Wn is post-modified (incremented or decremented) by a constant value. |

| Register Indirect Pre-Modified         | Wn is pre-modified (incremented or decremented) by a signed constant value to form the EA.             |

| Register Indirect with Register Offset | The sum of Wn and Wb forms the EA.                                                                     |

| Register Indirect with Literal Offset  | The sum of Wn and a literal forms the EA.                                                              |

# TABLE 4-34: FUNDAMENTAL ADDRESSING MODES SUPPORTED

#### 4.3.3 MOVE INSTRUCTIONS

Move instructions provide a greater degree of addressing flexibility than other instructions. In addition to the Addressing modes supported by most MCU instructions, move instructions also support Register Indirect with Register Offset Addressing mode, also referred to as Register Indexed mode.

Note: For the MOV instructions, the Addressing mode specified in the instruction can differ for the source and destination EA. However, the 4-bit Wb (Register Offset) field is shared between both source and destination (but typically only used by one).

In summary, the following Addressing modes are supported by move instructions:

- Register Direct

- · Register Indirect

- Register Indirect Post-modified

- Register Indirect Pre-modified

- Register Indirect with Register Offset (Indexed)

- Register Indirect with Literal Offset

- 8-bit Literal

- 16-bit Literal

| Note: | Not all   | instructi | ons   | suppo | ort | all  | the  |

|-------|-----------|-----------|-------|-------|-----|------|------|

|       | Addressi  | ng mo     | des   | give  | n   | ab   | ove. |

|       | Individua | l instru  | ction | s ma  | ay  | sup  | port |

|       | different | subsets   | of    | these | Ado | dres | sing |

|       | modes.    |           |       |       |     |      |      |

#### 4.3.4 OTHER INSTRUCTIONS

Besides the various addressing modes outlined above, some instructions use literal constants of various sizes. For example, BRA (branch) instructions use 16-bit signed literals to specify the branch destination directly, whereas the DISI instruction uses a 14-bit unsigned literal field. In some instructions, the source of an operand or result is implied by the opcode itself. Certain operations, such as NOP, do not have any operands.

# 4.4 Interfacing Program and Data Memory Spaces

The PIC24HJXXXGPX06A/X08A/X10A architecture uses a 24-bit wide program space and a 16-bit wide data space. The architecture is also a modified Harvard scheme, meaning that data can also be present in the program space. To use this data successfully, it must be accessed in a way that preserves the alignment of information in both spaces.

Aside from normal execution, the PIC24HJXXXGPX06A/X08A/X10A architecture provides two methods by which program space can be accessed during operation:

- Using table instructions to access individual bytes or words anywhere in the program space

- Remapping a portion of the program space into the data space (Program Space Visibility)

Table instructions allow an application to read or write to small areas of the program memory. This capability makes the method ideal for accessing data tables that need to be updated from time to time. It also allows access to all bytes of the program word. The remapping method allows an application to access a large block of data on a read-only basis, which is ideal for look ups from a large table of static data. It can only access the least significant word of the program word.

#### 4.4.1 ADDRESSING PROGRAM SPACE

Since the address ranges for the data and program spaces are 16 and 24 bits, respectively, a method is needed to create a 23-bit or 24-bit program address from 16-bit data registers. The solution depends on the interface method to be used.

For table operations, the 8-bit Table Page register (TBLPAG) is used to define a 32K word region within the program space. This is concatenated with a 16-bit EA to arrive at a full 24-bit program space address. In this format, the Most Significant bit of TBLPAG is used to determine if the operation occurs in the user memory (TBLPAG<7> = 0) or the configuration memory (TBLPAG<7> = 1).

#### 5.4.1 PROGRAMMING ALGORITHM FOR FLASH PROGRAM MEMORY

The user can program one row of program Flash memory at a time. To do this, it is necessary to erase the 8-row erase page that contains the desired row. The general process is:

- 1. Read eight rows of program memory (512 instructions) and store in data RAM.

- 2. Update the program data in RAM with the desired new data.

- 3. Erase the page (see Example 5-1):

- a) Set the NVMOP bits (NVMCON<3:0>) to '0010' to configure for block erase. Set the ERASE (NVMCON<6>) and WREN (NVMCON<14>) bits.

- b) Write the starting address of the page to be erased into the TBLPAG and W registers.

- Perform a dummy table write operation (TBLWTL) to any address within the page that needs to be erased.

- d) Write 0x55 to NVMKEY.

- e) Write 0xAA to NVMKEY.

- f) Set the WR bit (NVMCON<15>). The erase cycle begins and the CPU stalls for the duration of the erase cycle. When the erase is done, the WR bit is cleared automatically.

- 4. Write the first 64 instructions from data RAM into the program memory buffers (see Example 5-2).

- 5. Write the program block to Flash memory:

- a) Set the NVMOP bits to '0001' to configure for row programming. Clear the ERASE bit and set the WREN bit.

- b) Write 0x55 to NVMKEY.

- c) Write 0xAA to NVMKEY.

- d) Set the WR bit. The programming cycle begins and the CPU stalls for the duration of the write cycle. When the write to Flash memory is done, the WR bit is cleared automatically.

- Repeat steps 4 and 5, using the next available 64 instructions from the block in data RAM by incrementing the value in TBLPAG, until all 512 instructions are written back to Flash memory.

For protection against accidental operations, the write initiate sequence for NVMKEY must be used to allow any erase or program operation to proceed. After the programming command has been executed, the user must wait for the programming time until programming is complete. The two instructions following the start of the programming sequence should be NOPS, as shown in Example 5-3.

#### EXAMPLE 5-1: ERASING A PROGRAM MEMORY PAGE

| ; Set up NVMCON for block erase operation |                                         |

|-------------------------------------------|-----------------------------------------|

| MOV #0x4042, W0                           | i                                       |

| MOV W0, NVMCON                            | ; Initialize NVMCON                     |

| ; Init pointer to row to be ERASED        |                                         |

| MOV #tblpage(PROG_ADDR), W0               | ;                                       |

| MOV W0, TBLPAG                            | ; Initialize PM Page Boundary SFR       |

| MOV #tbloffset(PROG_ADDR), W0             | ; Initialize in-page EA<15:0> pointer   |

| TBLWTL W0, [W0]                           | ; Set base address of erase block       |

| DISI #5                                   | ; Block all interrupts with priority <7 |

|                                           | ; for next 5 instructions               |

| MOV #0x55, W0                             |                                         |

| MOV W0, NVMKEY                            | ; Write the 55 key                      |

| MOV #0xAA, W1                             | ;                                       |

| MOV W1, NVMKEY                            | ; Write the AA key                      |

| BSET NVMCON, #WR                          | ; Start the erase sequence              |

| NOP                                       | ; Insert two NOPs after the erase       |

| NOP                                       | ; command is asserted                   |

|                                           |                                         |

Note: A program memory page erase operation is set up by performing a dummy table write (TBLWTL) operation to any address within the page. This methodology is different from the page erase operation on dsPIC30F/33F devices in which the erase page was selected using a dedicated pair of registers (NVMADRU and NVMADR).

# PIC24HJXXXGPX06A/X08A/X10A

NOTES:

### REGISTER 7-6: IFS1: INTERRUPT FLAG STATUS REGISTER 1 (CONTINUED)

| bit 3 | CNIF: Input Change Notification Interrupt Flag Status bit |

|-------|-----------------------------------------------------------|

|       | 1 = Interrupt request has occurred                        |

|       | 0 = Interrupt request has not occurred                    |

- bit 2 Unimplemented: Read as '0'

- bit 1 MI2C1IF: I2C1 Master Events Interrupt Flag Status bit

- 1 = Interrupt request has occurred

- 0 = Interrupt request has not occurred

- bit 0 SI2C1IF: I2C1 Slave Events Interrupt Flag Status bit

- 1 = Interrupt request has occurred

- 0 = Interrupt request has not occurred

## REGISTER 7-32: IPC17: INTERRUPT PRIORITY CONTROL REGISTER 17

|                 | R/W-1              | R/W-0                | R/W-0           | U-0              | R/W-1            | R/W-0           | R/W-0 |

|-----------------|--------------------|----------------------|-----------------|------------------|------------------|-----------------|-------|

| —               |                    | C2TXIP<2:0>          |                 | —                |                  | C1TXIP<2:0>     |       |

| bit 15          |                    |                      |                 |                  |                  |                 | bit 8 |

|                 |                    |                      |                 |                  |                  |                 |       |

| U-0             | R/W-1              | R/W-0                | R/W-0           | U-0              | R/W-1            | R/W-0           | R/W-0 |

|                 |                    | DMA7IP<2:0>          |                 | —                |                  | DMA6IP<2:0>     |       |

| bit 7           |                    |                      |                 |                  |                  |                 | bit   |

| Legend:         |                    |                      |                 |                  |                  |                 |       |

| R = Readable    | bit                | W = Writable I       | bit             | U = Unimple      | mented bit, re   | ad as '0'       |       |

| -n = Value at F | POR                | '1' = Bit is set     |                 | '0' = Bit is cle | eared            | x = Bit is unkn | own   |

| bit 15          | Unimplemer         | nted: Read as 'd     | )'              |                  |                  |                 |       |

| bit 14-12       | -                  | >: ECAN2 Trans       |                 | quest Interrupt  | Priority bits    |                 |       |

|                 |                    | ipt is priority 7 (ł |                 |                  |                  |                 |       |

|                 | •                  |                      |                 |                  |                  |                 |       |

|                 | •                  |                      |                 |                  |                  |                 |       |

|                 | 001 = Interru      | pt is priority 1     |                 |                  |                  |                 |       |

|                 |                    | pt source is disa    | abled           |                  |                  |                 |       |

| bit 11          | Unimplemer         | nted: Read as 'd     | )'              |                  |                  |                 |       |

| bit 10-8        | C1TXIP<2:0         | >: ECAN1 Trans       | smit Data Rec   | quest Interrupt  | Priority bits    |                 |       |

|                 | 111 = Interru      | ipt is priority 7 (ł | nighest priorit | y interrupt)     |                  |                 |       |

|                 | •                  |                      |                 |                  |                  |                 |       |

|                 | •                  |                      |                 |                  |                  |                 |       |

|                 | •<br>001 = Interru | pt is priority 1     |                 |                  |                  |                 |       |

|                 |                    | ipt source is disa   | abled           |                  |                  |                 |       |

| bit 7           | Unimplemer         | nted: Read as 'o     | )'              |                  |                  |                 |       |

| bit 6-4         | DMA7IP<2:0         | >: DMA Channe        | el 7 Data Trar  | nsfer Complete   | e Interrupt Pric | ority bits      |       |

|                 | 111 = Interru      | ıpt is priority 7 (ł | nighest priorit | y interrupt)     | ·                |                 |       |

|                 | •                  |                      |                 |                  |                  |                 |       |

|                 | •                  |                      |                 |                  |                  |                 |       |

|                 | •<br>001 = Interru | pt is priority 1     |                 |                  |                  |                 |       |

|                 |                    | ipt source is disa   | abled           |                  |                  |                 |       |

| bit 3           |                    | nted: Read as '0     |                 |                  |                  |                 |       |

| bit 2-0         | DMA6IP<2:0         | >: DMA Channe        | el 6 Data Trar  | nsfer Complete   | e Interrupt Pric | ority bits      |       |

|                 |                    | ipt is priority 7 (h |                 | •                |                  | 5               |       |

|                 | •                  |                      |                 |                  |                  |                 |       |

|                 | •                  |                      |                 |                  |                  |                 |       |

|                 | •<br>001 = Interru | unt in priority 1    |                 |                  |                  |                 |       |

|                 |                    |                      |                 |                  |                  |                 |       |

# **REGISTER 9-1:** OSCCON: OSCILLATOR CONTROL REGISTER<sup>(1,3)</sup>

| U-0           | R-0                | R-0                                          | R-0            | U-0              | R/W-y           | R/W-y             | R/W-y        |

|---------------|--------------------|----------------------------------------------|----------------|------------------|-----------------|-------------------|--------------|

| _             |                    | COSC<2:0>                                    |                |                  | -               | NOSC<2:0>(2)      |              |

| bit 15        |                    |                                              |                |                  |                 |                   | bit 8        |

|               |                    |                                              |                |                  |                 |                   |              |

| R/W-0         | U-0                | R-0                                          | U-0            | R/C-0            | U-0             | R/W-0             | R/W-0        |

| CLKLOCK       | <u> </u>           | LOCK                                         | _              | CF               |                 | LPOSCEN           | OSWEN        |

| bit 7         |                    |                                              |                |                  |                 |                   | bit 0        |

| Legend:       |                    | y = Value set                                | from Configui  | ation bits on P  | OR              | C = Clear only    | y bit        |

| R = Readable  | e bit              | W = Writable                                 | bit            | U = Unimpler     | mented bit, rea | id as '0'         |              |

| -n = Value at | POR                | '1' = Bit is set                             |                | '0' = Bit is cle | ared            | x = Bit is unkn   | own          |

| bit 15        | Unimplemer         | nted: Read as '                              | n'             |                  |                 |                   |              |

| bit 14-12     | -                  | Current Oscilla                              |                | hits (read-only  | 0               |                   |              |

| 511112        |                    | C oscillator (FF                             |                |                  | ,               |                   |              |

|               |                    | RC oscillator (FF                            |                |                  |                 |                   |              |

|               |                    | ower RC oscilla                              |                |                  |                 |                   |              |

|               |                    | dary oscillator (                            | • • •          |                  |                 |                   |              |

|               | 011 <b>= Prima</b> | ry oscillator (XT                            | , HS, EC) with | ו PLL            |                 |                   |              |

|               |                    | ry oscillator (XT                            |                |                  |                 |                   |              |

|               |                    | RC Oscillator (Fl                            | ,              | le-by-N and PL   | L (FRCDIVN ·    | + PLL)            |              |

|               |                    | RC oscillator (FF                            |                |                  |                 |                   |              |

| bit 11        | -                  | nted: Read as '                              |                | (2)              |                 |                   |              |

| bit 10-8      |                    | New Oscillator                               |                |                  |                 |                   |              |

|               |                    | RC oscillator (FF                            | ,              | •                |                 |                   |              |

|               |                    | RC oscillator (FF<br>Power RC oscilla        |                | e-by-16          |                 |                   |              |

|               |                    | idary oscillator (                           |                |                  |                 |                   |              |

|               |                    | ry oscillator (XT                            |                | 1 PLL            |                 |                   |              |

|               |                    | ry oscillator (XT                            |                |                  |                 |                   |              |

|               |                    | RC Oscillator (FI                            |                | le-by-N and PL   | L (FRCDIVN ·    | + PLL)            |              |

| 1             |                    | RC oscillator (FF                            |                |                  |                 |                   |              |

| bit 7         |                    | Clock Lock Ena                               |                |                  | ana la alca d   |                   |              |

|               |                    | SM0 = 1), the closed $SM0 = 0$ ), the closed |                |                  |                 | ad a              |              |

|               |                    | nd PLL selection                             |                |                  |                 |                   |              |

| bit 6         | Unimplemer         | nted: Read as '                              | 0'             |                  | ·               |                   |              |

| bit 5         | LOCK: PLL I        | Lock Status bit (                            | read-only)     |                  |                 |                   |              |

|               |                    | s that PLL is in I<br>s that PLL is ou       |                |                  |                 | l is disabled     |              |

| bit 4         |                    | nted: Read as '                              |                |                  |                 |                   |              |

| bit 3         | -                  | ail Detect bit (rea                          |                | plication)       |                 |                   |              |

|               | 1 = FSCM h         | as detected clo<br>as not detected           | ck failure     | . ,              |                 |                   |              |

| bit 2         |                    | nted: Read as '                              |                |                  |                 |                   |              |

|               | -                  | ster require an i                            | unlock sequer  |                  | ection 7. "Os   | cillator" (DS7018 | 86) in the   |

|               |                    | •                                            |                |                  | h PI L and EP(  | CPLL mode are n   | ot permitted |

|               |                    |                                              |                |                  |                 | lication must swi |              |

|               | ode as a transiti  |                                              |                |                  |                 |                   |              |

- mode as a transition clock source between the two PLL modes.

- 3: This register is reset only on a Power-on Reset (POR).

#### REGISTER 10-1: PMD1: PERIPHERAL MODULE DISABLE CONTROL REGISTER 1 (CONTINUED)

- bit 1 C1MD: ECAN1 Module Disable bit 1 = ECAN1 module is disabled

- 0 = ECAN1 module is enabled

- bit 0 AD1MD: ADC1 Module Disable bit<sup>(1)</sup>

- 1 = ADC1 module is disabled

- 0 = ADC1 module is enabled

- **Note 1:** PCFGx bits have no effect if ADC module is disabled by setting this bit. In this case all port pins multiplexed with ANx will be in Digital mode.

# 18.3 UART Control Registers

# REGISTER 18-1: UxMODE: UARTx MODE REGISTER

| R/W-0                 | U-0                                                                                                                        | R/W-0                            | R/W-0               | R/W-0            | U-0                              | R/W-0             | R/W-0           |  |  |

|-----------------------|----------------------------------------------------------------------------------------------------------------------------|----------------------------------|---------------------|------------------|----------------------------------|-------------------|-----------------|--|--|

| UARTEN <sup>(1)</sup> |                                                                                                                            | USIDL                            | IREN <sup>(2)</sup> | RTSMD            |                                  | UEN               | <1:0>           |  |  |

| bit 15                |                                                                                                                            |                                  |                     |                  |                                  |                   | bit             |  |  |

|                       |                                                                                                                            |                                  |                     |                  |                                  |                   |                 |  |  |

| R/W-0 HC              | R/W-0                                                                                                                      | R/W-0 HC                         | R/W-0               | R/W-0            | R/W-0                            | R/W-0             | R/W-0           |  |  |

| WAKE                  | LPBACK                                                                                                                     | ABAUD                            | URXINV              | BRGH             | PDSE                             | L<1:0>            | STSEL           |  |  |

| bit 7                 |                                                                                                                            |                                  |                     |                  |                                  |                   | bit             |  |  |

| Legend:               |                                                                                                                            | HC = Hardwa                      | re cleared          |                  |                                  |                   |                 |  |  |

| R = Readable          | bit                                                                                                                        | W = Writable                     | bit                 | U = Unimpler     | mented bit, read                 | 1 as '0'          |                 |  |  |

| -n = Value at F       | POR                                                                                                                        | '1' = Bit is set                 |                     | '0' = Bit is cle |                                  | x = Bit is unkr   | iown            |  |  |

|                       |                                                                                                                            |                                  |                     |                  |                                  |                   |                 |  |  |

| bit 15                | UARTEN: UA                                                                                                                 | ARTx Enable bi                   | t(1)                |                  |                                  |                   |                 |  |  |

|                       | 1 = UARTx is                                                                                                               | s enabled; all L                 | ARTx pins are       | e controlled by  | UARTx as defi                    | ned by UEN<1:     | 0>              |  |  |

|                       | 0 = UARTx is                                                                                                               |                                  |                     |                  | port latches; L                  |                   |                 |  |  |

|                       | minimal                                                                                                                    |                                  |                     |                  |                                  |                   |                 |  |  |

| bit 14                | Unimplemen                                                                                                                 | ted: Read as '                   | 0'                  |                  |                                  |                   |                 |  |  |

| bit 13                | USIDL: Stop in Idle Mode bit                                                                                               |                                  |                     |                  |                                  |                   |                 |  |  |

|                       |                                                                                                                            | nue module ope                   |                     |                  | dle mode                         |                   |                 |  |  |

|                       |                                                                                                                            | e module opera                   |                     |                  |                                  |                   |                 |  |  |

| bit 12                | IREN: IrDA <sup>®</sup> Encoder and Decoder Enable bit <sup>(2)</sup><br>1 = IrDA <sup>®</sup> encoder and decoder enabled |                                  |                     |                  |                                  |                   |                 |  |  |

|                       |                                                                                                                            | coder and dec<br>coder and dec   |                     |                  |                                  |                   |                 |  |  |

| bit 11                |                                                                                                                            | te Selection for                 |                     | i+               |                                  |                   |                 |  |  |

|                       |                                                                                                                            | oin in Simplex n                 |                     | it.              |                                  |                   |                 |  |  |

|                       |                                                                                                                            | oin in Flow Con                  |                     |                  |                                  |                   |                 |  |  |

| bit 10                | Unimplemen                                                                                                                 | ted: Read as '                   | 0'                  |                  |                                  |                   |                 |  |  |

| bit 9-8               | UEN<1:0>: U                                                                                                                | JARTx Enable I                   | oits                |                  |                                  |                   |                 |  |  |

|                       |                                                                                                                            |                                  |                     |                  | ; UxCTS pin co                   | ntrolled by port  | latches         |  |  |

|                       |                                                                                                                            | JxRX, UxCTS a                    |                     |                  |                                  |                   |                 |  |  |

|                       |                                                                                                                            |                                  |                     |                  | ed; UxCTS pin c<br>S and UxRTS/E |                   |                 |  |  |

|                       | port latcl                                                                                                                 |                                  | ire enableu an      |                  |                                  |                   | olled by        |  |  |

| bit 7                 | •                                                                                                                          | e-up on Start bi                 | t Detect Durine     | a Sleep Mode     | Enable bit                       |                   |                 |  |  |

|                       |                                                                                                                            | -                                |                     |                  | upt generated o                  | n falling edge; t | oit cleared     |  |  |

|                       |                                                                                                                            | are on following                 |                     | • •              | 1 0                              | 0 0 /             |                 |  |  |

|                       | 0 = No wake                                                                                                                | -up enabled                      |                     |                  |                                  |                   |                 |  |  |

| bit 6                 | LPBACK: UA                                                                                                                 | ARTx Loopback                    | Mode Select         | bit              |                                  |                   |                 |  |  |

|                       |                                                                                                                            | oopback mode                     |                     |                  |                                  |                   |                 |  |  |

|                       | -                                                                                                                          | k mode is disal                  |                     |                  |                                  |                   |                 |  |  |

| bit 5                 |                                                                                                                            | o-Baud Enable                    |                     |                  |                                  |                   | e = =           |  |  |

|                       |                                                                                                                            | aud rate meas<br>ny data; cleare |                     |                  | er – requires re                 | ception of a Syl  | nc field (0x55  |  |  |

|                       |                                                                                                                            | e measuremen                     |                     | • •              |                                  |                   |                 |  |  |

|                       | 2.30100                                                                                                                    |                                  |                     |                  |                                  |                   |                 |  |  |

| Note 1: Ref           | er to Section 1                                                                                                            | I <b>7. "UART</b> " (D           | S70188) in the      | e "dsPIC33F/P    | PIC24H Family F                  | Reference Manu    | <i>ual"</i> for |  |  |

|                       | ormation on ena                                                                                                            |                                  |                     |                  |                                  |                   |                 |  |  |

| о т. ·                | - <b>f t</b>                                                                                                               | , available fart                 |                     |                  | a)                               |                   |                 |  |  |

**2:** This feature is only available for the 16x BRG mode (BRGH = 0).

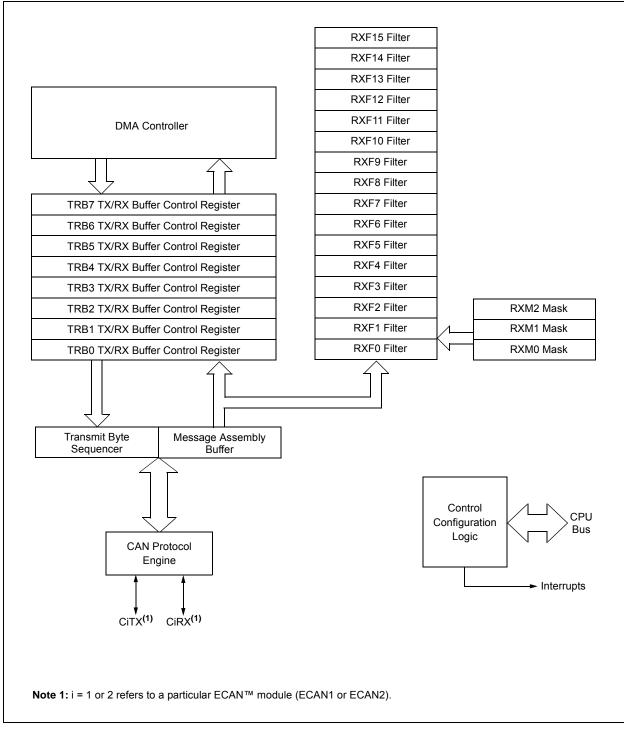

# 19.0 ENHANCED CAN (ECAN™) MODULE

- Note 1: This data sheet summarizes the features of the PIC24HJXXXGPX06A/X08A/X10A family of devices. However, it is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to the *"dsPIC33F/PIC24H Family Reference Manual"*, Section 21. "Enhanced Controller Area Network (ECAN™)" (DS70185), which is available from the Microchip web site (www.microchip.com).

- 2: Some registers and associated bits described in this section may not be available on all devices. Refer to Section 4.0 "Memory Organization" in this data sheet for device-specific register and bit information.

## 19.1 Overview

The Enhanced Controller Area Network (ECAN<sup>™</sup>) module is a serial interface, useful for communicating with other CAN modules or microcontroller devices. This interface/protocol was designed to allow communications within noisy environments. The PIC24HJXXXGPX06A/X08A/X10A devices contain up to two ECAN modules.

The CAN module is a communication controller implementing the CAN 2.0 A/B protocol, as defined in the BOSCH specification. The module will support CAN 1.2, CAN 2.0A, CAN 2.0B Passive and CAN 2.0B Active versions of the protocol. The module implementation is a full CAN system. The CAN specification is not covered within this data sheet. The reader may refer to the BOSCH CAN specification for further details.

The module features are as follows:

- Implementation of the CAN protocol, CAN 1.2, CAN 2.0A and CAN 2.0B

- · Standard and extended data frames

- 0-8 bytes data length

- Programmable bit rate up to 1 Mbit/sec

- Automatic response to remote transmission requests

- Up to 8 transmit buffers with application specified prioritization and abort capability (each buffer may contain up to 8 bytes of data)

- Up to 32 receive buffers (each buffer may contain up to 8 bytes of data)

- Up to 16 full (standard/extended identifier)

acceptance filters

- 3 full acceptance filter masks

- DeviceNet<sup>™</sup> addressing support

- Programmable wake-up functionality with integrated low-pass filter

- Programmable Loopback mode supports self-test operation

- Signaling via interrupt capabilities for all CAN receiver and transmitter error states

- Programmable clock source

- Programmable link to input capture module (IC2 for both CAN1 and CAN2) for time-stamping and network synchronization

- · Low-power Sleep and Idle mode

The CAN bus module consists of a protocol engine and message buffering/control. The CAN protocol engine handles all functions for receiving and transmitting messages on the CAN bus. Messages are transmitted by first loading the appropriate data registers. Status and errors can be checked by reading the appropriate registers. Any message detected on the CAN bus is checked for errors and then matched against filters to see if it should be received and stored in one of the receive registers.

# 19.2 Frame Types

The CAN module transmits various types of frames which include data messages, remote transmission requests and as other frames that are automatically generated for control purposes. The following frame types are supported:

Standard Data Frame:

A standard data frame is generated by a node when the node wishes to transmit data. It includes an 11-bit standard identifier (SID) but not an 18-bit extended identifier (EID).

- Extended Data Frame: An extended data frame is similar to a standard data frame but includes an extended identifier as well.

- Remote Frame:

It is possible for a destination node to request the data from the source. For this purpose, the destination node sends a remote frame with an identifier that matches the identifier of the required data frame. The appropriate data source node will then send a data frame as a response to this remote request.

• Error Frame:

An error frame is generated by any node that detects a bus error. An error frame consists of two fields: an error flag field and an error delimiter field.

Overload Frame:

An overload frame can be generated by a node as a result of two conditions. First, the node detects a dominant bit during interframe space which is an illegal condition. Second, due to internal conditions, the node is not yet able to start reception of the next message. A node may generate a maximum of 2 sequential overload frames to delay the start of the next message.

· Interframe Space:

Interframe space separates a proceeding frame (of whatever type) from a following data or remote frame.

# PIC24HJXXXGPX06A/X08A/X10A

## FIGURE 19-1: ECAN™ MODULE BLOCK DIAGRAM

## REGISTER 19-19: CiFMSKSEL2: ECAN™ FILTER 15-8 MASK SELECTION REGISTER

| R/W-0           | R/W-0        | R/W-0                              | R/W-0           | R/W-0            | R/W-0           | R/W-0           | R/W    | /-0   |

|-----------------|--------------|------------------------------------|-----------------|------------------|-----------------|-----------------|--------|-------|

| F15M            | SK<1:0>      | F14MS                              | K<1:0>          | F13M             | SK<1:0>         | F12MS           | K<1:0> |       |

| bit 15          |              |                                    |                 |                  |                 |                 |        | bit 8 |

|                 |              |                                    |                 |                  |                 |                 |        |       |

| R/W-0           | R/W-0        | R/W-0                              | R/W-0           | R/W-0            | R/W-0           | R/W-0           | R/W    | /-0   |

| F11M            | SK<1:0>      | F10MS                              | K<1:0>          | F9MS             | SK<1:0>         | F8MS            | K<1:0> |       |

| bit 7           |              |                                    |                 |                  |                 |                 |        | bit ( |

| <u> </u>        |              |                                    |                 |                  |                 |                 |        |       |

| Legend:         |              |                                    | ,               |                  |                 |                 |        |       |

| R = Readable    |              | W = Writable                       |                 | •                | nented bit, rea |                 |        |       |

| -n = Value at   | POR          | '1' = Bit is set                   |                 | '0' = Bit is cle | ared            | x = Bit is unkr | lown   |       |

| bit 15-14       | E15MSK-1.0   | >: Mask Sourc                      | e for Filter 15 | bit              |                 |                 |        |       |

| DIL 10-14       |              | ed; do not use                     |                 | bit              |                 |                 |        |       |

|                 |              | ince Mask 2 reg                    | gisters contair | n mask           |                 |                 |        |       |

|                 |              | ince Mask 1 reg                    |                 |                  |                 |                 |        |       |

|                 | 00 = Accepta | ince Mask 0 reg                    | gisters contair | n mask           |                 |                 |        |       |

| bit 13-12       |              | >: Mask Sourc                      | e for Filter 14 | bit              |                 |                 |        |       |

|                 |              | ed; do not use                     | vietere eerteiv | maal             |                 |                 |        |       |

|                 |              | ince Mask 2 reg<br>ince Mask 1 reg |                 |                  |                 |                 |        |       |

|                 |              | ince Mask 0 reg                    |                 |                  |                 |                 |        |       |

| bit 11-10       | -            | >: Mask Sourc                      | -               |                  |                 |                 |        |       |

|                 | 11 = Reserve | ed; do not use                     |                 |                  |                 |                 |        |       |

|                 |              | ince Mask 2 reg                    |                 |                  |                 |                 |        |       |

|                 |              | nce Mask 1 reg                     |                 |                  |                 |                 |        |       |

| <b>h</b> it 0 0 | -            | ince Mask 0 reg                    |                 |                  |                 |                 |        |       |

| bit 9-8         |              | I>: Mask Sourc<br>ed; do not use   | e for Filter 12 | DIL              |                 |                 |        |       |

|                 |              | ince Mask 2 reg                    | isters contair  | n mask           |                 |                 |        |       |

|                 |              | ince Mask 1 reg                    |                 |                  |                 |                 |        |       |

|                 | 00 = Accepta | ince Mask 0 reg                    | jisters contair | n mask           |                 |                 |        |       |

| bit 7-6         |              | >: Mask Sourc                      | e for Filter 11 | bit              |                 |                 |        |       |

|                 |              | ed; do not use                     |                 |                  |                 |                 |        |       |

|                 |              | ince Mask 2 reg                    |                 |                  |                 |                 |        |       |

|                 |              | ince Mask 1 reg<br>ince Mask 0 reg |                 |                  |                 |                 |        |       |

| bit 5-4         | -            | >: Mask Sourc                      |                 |                  |                 |                 |        |       |

|                 |              | ed; do not use                     |                 |                  |                 |                 |        |       |

|                 | 10 = Accepta | nce Mask 2 reg                     | jisters contair | n mask           |                 |                 |        |       |

|                 |              | nce Mask 1 reg                     |                 |                  |                 |                 |        |       |

|                 | -            | ince Mask 0 reg                    | -               |                  |                 |                 |        |       |

| bit 3-2         |              | : Mask Source                      | for Filter 9 bi | t                |                 |                 |        |       |

|                 |              | ed; do not use<br>ince Mask 2 reg  | nisters contair | n mask           |                 |                 |        |       |

|                 |              | ince Mask 1 reg                    |                 |                  |                 |                 |        |       |

|                 |              | ince Mask 0 reg                    |                 |                  |                 |                 |        |       |

| bit 1-0         |              | . Mask Source                      |                 |                  |                 |                 |        |       |

|                 | 11 = Reserve | ed; do not use                     |                 |                  |                 |                 |        |       |

|                 |              | ince Mask 2 reg                    |                 |                  |                 |                 |        |       |

|                 | 01 = Accepta | nce Mask 1 reg                     | gisters contair | n mask           |                 |                 |        |       |

|                 |              | nce Mask 0 reg                     |                 |                  |                 |                 |        |       |

# **REGISTER 20-9:** AD1PCFGH: ADC1 PORT CONFIGURATION REGISTER HIGH<sup>(1,2,3,4)</sup>

| R/W-0  |

|--------|--------|--------|--------|--------|--------|--------|--------|

| PCFG31 | PCFG30 | PCFG29 | PCFG28 | PCFG27 | PCFG26 | PCFG25 | PCFG24 |

| bit 15 | -      |        |        |        |        |        | bit 8  |

|        |        |        |        |        |        |        |        |

| R/W-0  |

| R/W-0  |

|--------|--------|--------|--------|--------|--------|--------|--------|

| PCFG23 | PCFG22 | PCFG21 | PCFG20 | PCFG19 | PCFG18 | PCFG17 | PCFG16 |

| bit 7  |        |        |        |        |        |        | bit 0  |

| Legend:           |                  |                             |                    |

|-------------------|------------------|-----------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, read | d as 'O'           |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared        | x = Bit is unknown |

bit 15-0 **PCFG<31:16>:** ADC Port Configuration Control bits

1 = Port pin in Digital mode, port read input enabled, ADC input multiplexer connected to AVss

0 = Port pin in Analog mode, port read input disabled, ADC samples pin voltage

- **Note 1:** On devices without 32 analog inputs, all PCFG bits are R/W by user. However, PCFG bits are ignored on ports without a corresponding input on device.

- 2: ADC2 only supports analog inputs AN0-AN15; therefore, no ADC2 high port Configuration register exists.

- **3:** PCFGx = ANx, where x = 16 through 31.

- **4:** PCFGx bits will have no effect if ADC module is disabled by setting ADxMD bit in the PMDx register. In this case all port pins multiplexed with ANx will be in Digital mode.

# 23.0 DEVELOPMENT SUPPORT

The PIC<sup>®</sup> microcontrollers and dsPIC<sup>®</sup> digital signal controllers are supported with a full range of software and hardware development tools:

- Integrated Development Environment

- MPLAB<sup>®</sup> IDE Software

- Compilers/Assemblers/Linkers

- MPLAB C Compiler for Various Device Families

- HI-TECH C<sup>®</sup> for Various Device Families

- MPASM<sup>™</sup> Assembler

- MPLINK<sup>™</sup> Object Linker/ MPLIB<sup>™</sup> Object Librarian

- MPLAB Assembler/Linker/Librarian for Various Device Families

- Simulators

- MPLAB SIM Software Simulator

- Emulators

- MPLAB REAL ICE™ In-Circuit Emulator

- In-Circuit Debuggers

- MPLAB ICD 3

- PICkit™ 3 Debug Express

- Device Programmers

- PICkit<sup>™</sup> 2 Programmer

- MPLAB PM3 Device Programmer

- Low-Cost Demonstration/Development Boards, Evaluation Kits, and Starter Kits

# 23.1 MPLAB Integrated Development Environment Software

The MPLAB IDE software brings an ease of software development previously unseen in the 8/16/32-bit microcontroller market. The MPLAB IDE is a Windows<sup>®</sup> operating system-based application that contains:

- A single graphical interface to all debugging tools

- Simulator

- Programmer (sold separately)

- In-Circuit Emulator (sold separately)

- In-Circuit Debugger (sold separately)

- A full-featured editor with color-coded context

- A multiple project manager

- Customizable data windows with direct edit of contents

- High-level source code debugging

- Mouse over variable inspection

- Drag and drop variables from source to watch windows

- · Extensive on-line help

- Integration of select third party tools, such as IAR C Compilers

The MPLAB IDE allows you to:

- Edit your source files (either C or assembly)

- One-touch compile or assemble, and download to emulator and simulator tools (automatically updates all project information)

- Debug using:

- Source files (C or assembly)

- Mixed C and assembly

- Machine code

MPLAB IDE supports multiple debugging tools in a single development paradigm, from the cost-effective simulators, through low-cost in-circuit debuggers, to full-featured emulators. This eliminates the learning curve when upgrading to tools with increased flexibility and power.

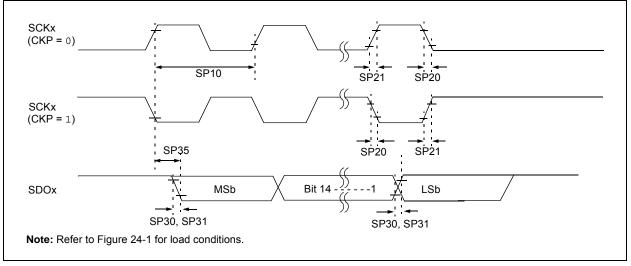

#### TABLE 24-28: SPIx MAXIMUM DATA/CLOCK RATE SUMMARY

| AC CHARACTERISTICS   |                                          |                                             | $\begin{tabular}{lllllllllllllllllllllllllllllllllll$ |     |     |     |  |

|----------------------|------------------------------------------|---------------------------------------------|-------------------------------------------------------|-----|-----|-----|--|

| Maximum<br>Data Rate | Master<br>Transmit Only<br>(Half-Duplex) | Master<br>Transmit/Receive<br>(Full-Duplex) | Slave<br>Transmit/Receive<br>(Full-Duplex)            | CKE | СКР | SMP |  |

| 15 MHz               | Table 24-29                              | —                                           | —                                                     | 0,1 | 0,1 | 0,1 |  |

| 10 MHz               | —                                        | Table 24-30                                 | —                                                     | 1   | 0,1 | 1   |  |

| 10 MHz               | —                                        | Table 24-31                                 | —                                                     | 0   | 0,1 | 1   |  |

| 15 MHz               | —                                        | —                                           | Table 24-32                                           | 1   | 0   | 0   |  |

| 11 MHz               | —                                        | —                                           | Table 24-33                                           | 1   | 1   | 0   |  |

| 15 MHz               | _                                        | _                                           | Table 24-34                                           | 0   | 1   | 0   |  |

| 11 MHz               |                                          |                                             | Table 24-35                                           | 0   | 0   | 0   |  |

#### FIGURE 24-9: SPIX MASTER MODE (HALF-DUPLEX, TRANSMIT ONLY CKE = 0) TIMING CHARACTERISTICS

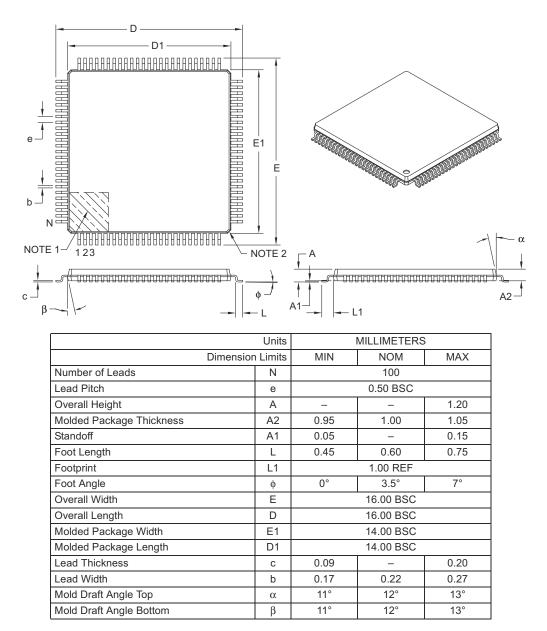

# 100-Lead Plastic Thin Quad Flatpack (PF) – 14x14x1 mm Body, 2.00 mm Footprint [TQFP]

**Note:** For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

Notes:

1. Pin 1 visual index feature may vary, but must be located within the hatched area.

2. Chamfers at corners are optional; size may vary.

3. Dimensions D1 and E1 do not include mold flash or protrusions. Mold flash or protrusions shall not exceed 0.25 mm per side.

4. Dimensioning and tolerancing per ASME Y14.5M.

BSC: Basic Dimension. Theoretically exact value shown without tolerances.

REF: Reference Dimension, usually without tolerance, for information purposes only.

Microchip Technology Drawing C04-110B

# PIC24HJXXXGPX06A/X08A/X10A

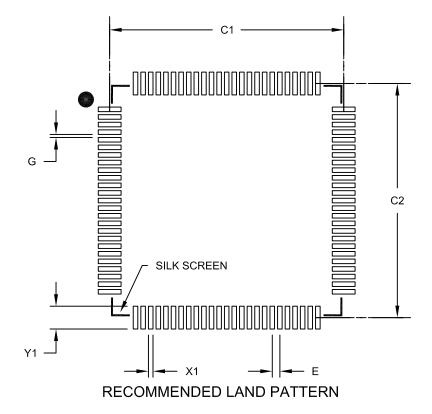

100-Lead Plastic Thin Quad Flatpack (PF) - 14x14x1 mm Body 2.00 mm Footprint [TQFP]

**Note:** For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

|                           | Units  | N    | <b>ILLIMETER</b> | S    |

|---------------------------|--------|------|------------------|------|

| Dimension                 | Limits | MIN  | NOM              | MAX  |

| Contact Pitch             | E      |      | 0.50 BSC         |      |

| Contact Pad Spacing       | C1     |      | 15.40            |      |

| Contact Pad Spacing       | C2     |      | 15.40            |      |

| Contact Pad Width (X100)  | X1     |      |                  | 0.30 |

| Contact Pad Length (X100) | Y1     |      |                  | 1.50 |

| Distance Between Pads     | G      | 0.20 |                  |      |

Notes:

1. Dimensioning and tolerancing per ASME Y14.5M

BSC: Basic Dimension. Theoretically exact value shown without tolerances.

Microchip Technology Drawing No. C04-2110B

# PIC24HJXXXGPX06A/X08A/X10A

#### R

| Reader Response                                                           | 2      |

|---------------------------------------------------------------------------|--------|

| ADxCHS0 (ADCx Input Channel 0 Select                                      | ,      |

| ADxCHS123 (ADCx Input                                                     |        |

| Channel 1, 2, 3 Select)                                                   |        |

|                                                                           |        |

| ADxCON2 (ADCx Control 2)                                                  |        |

| ADxCON3 (ADCx Control 3)214<br>ADxCON4 (ADCx Control 4)215                |        |

| ADxCON4 (ADCx Control 4)215<br>ADxCSSH (ADCx Input Scan Select High)218   |        |

| ADxCSSI (ADCx Input Scan Select Fight)                                    | ,<br>, |

| ADxPCFGH (ADCx Port Configuration High)                                   |        |

| ADxPCFGL (ADCx Port Configuration Low)                                    |        |

| CiBUFPNT1 (ECAN Filter 0-3 Buffer Pointer)                                |        |

| CiBUFPNT2 (ECAN Filter 4-7 Buffer Pointer)                                |        |

| CiBUFPNT3 (ECAN Filter 8-11 Buffer Pointer) 195                           |        |

| CiBUFPNT4 (ECAN Filter 12-15 Buffer Pointer) 196                          |        |

| CiCFG1 (ECAN Baud Rate Configuration 1) 190                               |        |

| CiCFG2 (ECAN Baud Rate Configuration 2) 191                               |        |

| CiCTRL1 (ECAN Control 1) 182                                              |        |

| CiCTRL2 (ECAN Control 2) 183                                              |        |

| CiEC (ECAN Transmit/Receive Error Count)                                  | )      |

| CIFCTRL (ECAN FIFO Control) 185                                           | 5      |

| CiFEN1 (ECAN Acceptance Filter Enable) 192                                |        |

| CiFIFO (ECAN FIFO Status)186                                              | 5      |

| CiFMSKSEL1 (ECAN Filter 7-0 Mask                                          |        |

| Selection)198, 199                                                        | )      |

| CiINTE (ECAN Interrupt Enable) 188                                        |        |

| CiINTF (ECAN Interrupt Flag)187                                           | '      |

| CiRXFnEID (ECAN Acceptance Filter n                                       |        |

| Extended Identifier) 197                                                  | '      |

| CiRXFnSID (ECAN Acceptance Filter n                                       |        |

| Standard Identifier) 197                                                  |        |

| CiRXFUL1 (ECAN Receive Buffer Full 1)201                                  |        |

| CiRXFUL2 (ECAN Receive Buffer Full 2)                                     |        |

| CiRXMnEID (ECAN Acceptance Filter Mask n                                  |        |

| Extended Identifier)                                                      | )      |

|                                                                           | ,      |

| Standard Identifier) 200<br>CiRXOVF1 (ECAN Receive Buffer Overflow 1) 202 |        |

| CiRXOVF2 (ECAN Receive Buffer Overflow 2)                                 |        |

| CiTRBnDLC (ECAN Buffer n Data                                             | •      |

| Length Control)                                                           |        |

| CiTRBnEID (ECAN Buffer n Extended Identifier) 204                         |        |

| CiTRBnSID (ECAN Buffer n Standard Identifier) 204                         |        |

| CiTRBnSTAT (ECAN Receive Buffer n Status)                                 |        |

| CiTRmnCON (ECAN TX/RX Buffer m Control)                                   |        |