Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFI

| Details                    |                                                                                |

|----------------------------|--------------------------------------------------------------------------------|

| Product Status             | Active                                                                         |

| Core Processor             | PIC                                                                            |

| Core Size                  | 16-Bit                                                                         |

| Speed                      | 40 MIPs                                                                        |

| Connectivity               | CANbus, I <sup>2</sup> C, IrDA, LINbus, SPI, UART/USART                        |

| Peripherals                | Brown-out Detect/Reset, DMA, POR, PWM, WDT                                     |

| Number of I/O              | 53                                                                             |

| Program Memory Size        | 64KB (22K x 24)                                                                |

| Program Memory Type        | FLASH                                                                          |

| EEPROM Size                | -                                                                              |

| RAM Size                   | 8K x 8                                                                         |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 3.6V                                                                      |

| Data Converters            | A/D 18x10b/12b                                                                 |

| Oscillator Type            | Internal                                                                       |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                              |

| Mounting Type              | Surface Mount                                                                  |

| Package / Case             | 64-TQFP                                                                        |

| Supplier Device Package    | 64-TQFP (10x10)                                                                |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic24hj64gp506a-i-pt |

|                            |                                                                                |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

### **Table of Contents**

| PIC24H Product Families                                                     |                                                      | 2   |

|-----------------------------------------------------------------------------|------------------------------------------------------|-----|

|                                                                             |                                                      |     |

| 2.0 Guidelines for Getting Started with 16-Bit Mid                          | crocontrollers                                       | 19  |

|                                                                             |                                                      |     |

| 4.0 Memory Organization                                                     |                                                      | 29  |

| 5.0 Flash Program Memory                                                    |                                                      | 59  |

| 6.0 Reset                                                                   |                                                      | 65  |

| 7.0 Interrupt Controller                                                    |                                                      | 69  |

| 8.0 Direct Memory Access (DMA)                                              |                                                      | 113 |

| 9.0 Oscillator Configuration                                                |                                                      | 123 |

| 10.0 Power-Saving Features                                                  |                                                      | 133 |

| 11.0 I/O Ports                                                              |                                                      | 141 |

| 12.0 Timer1                                                                 |                                                      | 145 |

|                                                                             |                                                      |     |

|                                                                             |                                                      |     |

|                                                                             |                                                      |     |

| 16.0 Serial Peripheral Interface (SPI)                                      |                                                      | 159 |

| 17.0 Inter-Integrated Circuit <sup>™</sup> (I <sup>2</sup> C <sup>™</sup> ) |                                                      | 165 |

|                                                                             | er (UART)                                            |     |

| 19.0 Enhanced CAN (ECAN™) Module                                            |                                                      | 179 |

|                                                                             | С)                                                   |     |

| 21.0 Special Features                                                       |                                                      | 221 |

| 22.0 Instruction Set Summary                                                |                                                      | 229 |

| 23.0 Development Support                                                    |                                                      | 237 |

| 24.0 Electrical Characteristics                                             |                                                      | 241 |

| 25.0 High Temperature Electrical Characteristics .                          |                                                      | 287 |

| 26.0 DC and AC Device Characteristics Graphs                                |                                                      | 297 |

|                                                                             |                                                      |     |

| Appendix A: Migrating from PIC24HJXXXGPX06/X                                | 08/X10 Devices to PIC24HJXXXGPX06A/X08A/X10A Devices | 311 |

| Appendix B: Revision History                                                |                                                      | 312 |

| Index                                                                       |                                                      | 317 |

| The Microchip Web Site                                                      |                                                      | 321 |

| Customer Change Notification Service                                        |                                                      | 321 |

| Customer Support                                                            |                                                      | 321 |

| Reader Response                                                             |                                                      | 322 |

| Product Identification System                                               |                                                      | 323 |

# 5.0 FLASH PROGRAM MEMORY

- Note 1: This data sheet summarizes the features of the PIC24HJXXXGPX06A/X08A/X10A family of devices. However, it is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to Section 5. "Flash Programming" (DS70191) of the "dsPIC33F/PIC24H Family Reference Manual", which is available from the Microchip web site (www.microchip.com).

- Some registers and associated bits described in this section may not be available on all devices. Refer to Section 4.0 "Memory Organization" in this data sheet for device-specific register and bit information.

The PIC24HJXXXGPX06A/X08A/X10A devices contain internal Flash program memory for storing and executing application code. The memory is readable, writable and erasable during normal operation over the entire VDD range.

Flash memory can be programmed in two ways:

- In-Circuit Serial Programming<sup>™</sup> (ICSP<sup>™</sup>) programming capability

- 2. Run-Time Self-Programming (RTSP)

ICSP programming capability allows a PIC24HJXXXGPX06A/X08A/X10A device to be serially programmed while in the end application circuit. This is simply done with two lines for programming clock and programming data (one of the alternate programming pin pairs: PGECx/PGEDx, and three other lines for power (VDD), ground (VSS) and Master Clear (MCLR). This allows customers to manufacture boards with unprogrammed devices and then program the digital signal controller just before shipping the product. This also allows the most recent firmware or a custom firmware to be programmed.

RTSP is accomplished using TBLRD (table read) and TBLWT (table write) instructions. With RTSP, the user can write program memory data either in blocks or 'rows' of 64 instructions (192 bytes) at a time, or single instructions and erase program memory in blocks or 'pages' of 512 instructions (1536 bytes) at a time.

### 5.1 Table Instructions and Flash Programming

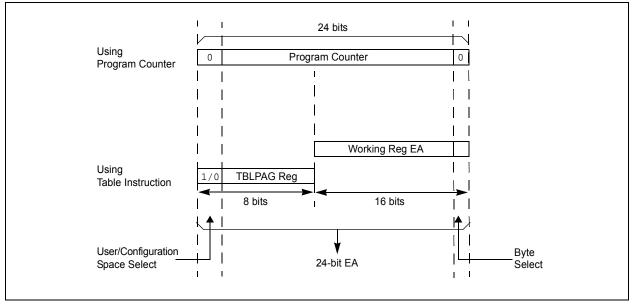

Regardless of the method used, all programming of Flash memory is done with the table read and table write instructions. These allow direct read and write access to the program memory space from the data memory while the device is in normal operating mode. The 24-bit target address in the program memory is formed using bits<7:0> of the TBLPAG register and the Effective Address (EA) from a W register specified in the table instruction, as shown in Figure 5-1.

The TBLRDL and the TBLWTL instructions are used to read or write to bits<15:0> of program memory. TBLRDL and TBLWTL can access program memory in both Word and Byte modes.

The TBLRDH and TBLWTH instructions are used to read or write to bits<23:16> of program memory. TBLRDH and TBLWTH can also access program memory in Word or Byte mode.

#### FIGURE 5-1: ADDRESSING FOR TABLE REGISTERS

### REGISTER 7-5: IFS0: INTERRUPT FLAG STATUS REGISTER 0

| U-0             | R/W-0           | R/W-0                            | R/W-0            | R/W-0            | R/W-0            | R/W-0           | R/W-0  |

|-----------------|-----------------|----------------------------------|------------------|------------------|------------------|-----------------|--------|

|                 | DMA1IF          | AD1IF                            | U1TXIF           | U1RXIF           | SPI1IF           | SPI1EIF         | T3IF   |

| bit 15          |                 |                                  |                  |                  |                  |                 | bit 8  |

|                 |                 |                                  |                  |                  |                  |                 |        |

| R/W-0           | R/W-0           | R/W-0                            | R/W-0            | R/W-0            | R/W-0            | R/W-0           | R/W-0  |

| T2IF            | OC2IF           | IC2IF                            | DMA01IF          | T1IF             | OC1IF            | IC1IF           | INTOIF |

| bit 7           |                 |                                  |                  |                  |                  |                 | bit C  |

| Legend:         |                 |                                  |                  |                  |                  |                 |        |

| R = Readable    | bit             | W = Writable                     | bit              | U = Unimpler     | mented bit, rea  | d as '0'        |        |

| -n = Value at F | OR              | '1' = Bit is se                  |                  | '0' = Bit is cle |                  | x = Bit is unkn | iown   |

|                 |                 |                                  |                  |                  |                  |                 |        |

| bit 15          | Unimplemen      | ted: Read as                     | 0'               |                  |                  |                 |        |

| bit 14          | DMA1IF: DM      | A Channel 1 D                    | ata Transfer C   | Complete Interr  | rupt Flag Status | bit             |        |

|                 |                 | request has oc                   |                  |                  |                  |                 |        |

| bit 13          |                 | request has no<br>I Conversion C |                  | unt Elog Statu   | o hit            |                 |        |

| DIL 13          |                 | request has oc                   | •                | upi riay Sialu   |                  |                 |        |

|                 |                 | request has no                   |                  |                  |                  |                 |        |

| bit 12          | U1TXIF: UAF     | RT1 Transmitte                   | r Interrupt Flag | g Status bit     |                  |                 |        |

|                 |                 | request has oc                   |                  |                  |                  |                 |        |

|                 |                 | request has no                   |                  |                  |                  |                 |        |

| bit 11          |                 | RT1 Receiver I<br>request has oc |                  | Status Dit       |                  |                 |        |

|                 |                 | request has oc                   |                  |                  |                  |                 |        |

| bit 10          | -               | Event Interrup                   |                  | bit              |                  |                 |        |

|                 |                 | request has oc                   |                  |                  |                  |                 |        |

|                 |                 | request has no                   |                  |                  |                  |                 |        |

| bit 9           |                 | 1 Fault Interru                  | •                | bit              |                  |                 |        |

|                 |                 | request has oc<br>request has no |                  |                  |                  |                 |        |

| bit 8           |                 | Interrupt Flag                   |                  |                  |                  |                 |        |

|                 |                 | request has oc                   |                  |                  |                  |                 |        |

|                 | -               | request has no                   |                  |                  |                  |                 |        |

| bit 7           |                 | Interrupt Flag                   |                  |                  |                  |                 |        |

|                 |                 | request has oc<br>request has no |                  |                  |                  |                 |        |

| bit 6           |                 | ut Compare Ch                    |                  | upt Flag Status  | s bit            |                 |        |

|                 |                 | request has oc                   |                  | -p               |                  |                 |        |

|                 | 0 = Interrupt i | request has no                   | t occurred       |                  |                  |                 |        |

| bit 5           | -               | Capture Chann                    | •                | -lag Status bit  |                  |                 |        |

|                 |                 | request has oc<br>request has no |                  |                  |                  |                 |        |

| bit 4           | -               | -                                |                  | Complete Inte    | rrupt Flag Statu | ıs bit          |        |

|                 |                 | request has oc                   |                  |                  |                  |                 |        |

|                 |                 | request has no                   |                  |                  |                  |                 |        |

| bit 3           |                 | Interrupt Flag                   |                  |                  |                  |                 |        |

|                 |                 | request has oc                   |                  |                  |                  |                 |        |

|                 | 0 = interrupt i | request has no                   | coccurred        |                  |                  |                 |        |

### REGISTER 7-7: IFS2: INTERRUPT FLAG STATUS REGISTER 2

| R/W-0         | R/W-0          | U-0                                | R/W-0            | R/W-0            | R/W-0            | R/W-0           | R/W-0   |

|---------------|----------------|------------------------------------|------------------|------------------|------------------|-----------------|---------|

| T6IF          | DMA4IF         | _                                  | OC8IF            | OC7IF            | OC6IF            | OC5IF           | IC6IF   |

| bit 15        |                |                                    |                  |                  |                  |                 | bit 8   |

| R/W-0         | R/W-0          | R/W-0                              | R/W-0            | R/W-0            | R/W-0            | R/W-0           | R/W-0   |

| IC5IF         | IC4IF          | IC3IF                              | DMA3IF           | C1IF             | C1RXIF           | SPI2IF          | SPI2EIF |

| bit 7         |                | 10011                              | Different        | 0.11             | <b>O</b> Hour    |                 | bit (   |

| Legend:       |                |                                    |                  |                  |                  |                 |         |

| R = Readab    | le bit         | W = Writable                       | bit              | U = Unimplei     | mented bit, read | l as '0'        |         |

| -n = Value a  | t POR          | '1' = Bit is set                   |                  | '0' = Bit is cle | ared             | x = Bit is unki | nown    |

| bit 15        | TEIE. Timore   | Interrupt Flag                     | Status bit       |                  |                  |                 |         |

| DIL 15        |                | request has oc                     |                  |                  |                  |                 |         |

|               |                | request has not                    |                  |                  |                  |                 |         |

| bit 14        | DMA4IF: DM     | A Channel 4 D                      | ata Transfer C   | Complete Interr  | rupt Flag Status | bit             |         |

|               |                | request has occ                    |                  |                  |                  |                 |         |

| bit 13        | •              | request has not<br>ited: Read as ' |                  |                  |                  |                 |         |

| bit 12        | •              | ut Compare Ch                      |                  | unt Elan Status  | e hit            |                 |         |

|               | •              | request has oc                     |                  | upi i lag Status | 5 01             |                 |         |

|               |                | request has not                    |                  |                  |                  |                 |         |

| bit 11        | OC7IF: Output  | ut Compare Ch                      | annel 7 Interr   | upt Flag Status  | s bit            |                 |         |

|               |                | request has oco<br>request has not |                  |                  |                  |                 |         |

| bit 10        | OC6IF: Output  | ut Compare Ch                      | annel 6 Interr   | upt Flag Status  | s bit            |                 |         |

|               |                | request has oco<br>request has not |                  |                  |                  |                 |         |

| bit 9         | OC5IF: Output  | ut Compare Ch                      | annel 5 Interr   | upt Flag Status  | s bit            |                 |         |

|               |                | request has oc                     |                  |                  |                  |                 |         |

| <b>h</b> :+ 0 | •              | request has not                    |                  | The Otative hit  |                  |                 |         |

| bit 8         | -              | Capture Channe<br>request has oce  |                  | -lag Status bit  |                  |                 |         |

|               | •              | request has not                    |                  |                  |                  |                 |         |

| bit 7         | IC5IF: Input ( | Capture Channe                     | el 5 Interrupt I | -lag Status bit  |                  |                 |         |

|               |                | request has oc                     |                  |                  |                  |                 |         |

|               | •              | request has not                    |                  |                  |                  |                 |         |

| bit 6         |                | Capture Channe                     |                  | -lag Status bit  |                  |                 |         |

|               |                | request has oco<br>request has not |                  |                  |                  |                 |         |

| bit 5         | IC3IF: Input C | Capture Channe                     | el 3 Interrupt I | -lag Status bit  |                  |                 |         |

|               |                | request has oc                     |                  |                  |                  |                 |         |

| bit 4         | -              | request has not                    |                  | amplata Intorr   | unt Flog Status  | hit             |         |

| bit 4         |                | request has oc                     |                  |                  | rupt Flag Status | UIL             |         |

|               |                | request has not                    |                  |                  |                  |                 |         |

| bit 3         | •              | I Event Interrup                   |                  | bit              |                  |                 |         |

|               |                | request has oc                     |                  |                  |                  |                 |         |

|               | 0 = Interrupt  | request has not                    | occurred         |                  |                  |                 |         |

| U-0            | R/W-1              | R/W-0                                  | R/W-0           | U-0              | R/W-1            | R/W-0           | R/W-0 |

|----------------|--------------------|----------------------------------------|-----------------|------------------|------------------|-----------------|-------|

| —              |                    | T6IP<2:0>                              |                 | —                |                  |                 |       |

| bit 15         |                    |                                        |                 |                  |                  |                 | bit   |

|                |                    |                                        |                 |                  |                  |                 |       |

| U-0            | U-0                | U-0                                    | U-0             | U-0              | R/W-1            | R/W-0           | R/W-0 |

| _              | —                  | —                                      |                 |                  |                  | OC8IP<2:0>      |       |

| bit 7          |                    |                                        |                 |                  |                  |                 | bit   |

| Legend:        |                    |                                        |                 |                  |                  |                 |       |

| R = Readab     | ole bit            | W = Writable                           | bit             | U = Unimple      | mented bit, rea  | d as '0'        |       |

| -n = Value a   | at POR             | '1' = Bit is set                       |                 | '0' = Bit is cle | eared            | x = Bit is unkn | iown  |

| bit 1 <i>5</i> | l inima la vere    | nted. Deed at f                        | <u>`</u>        |                  |                  |                 |       |

| bit 15         | -                  | nted: Read as '                        |                 |                  |                  |                 |       |

| bit 14-12      |                    | Timer6 Interrupt                       | •               |                  |                  |                 |       |

|                | 111 = Intern       | upt is priority 7 (I                   | nignest priorit | y interrupt)     |                  |                 |       |

|                | •                  |                                        |                 |                  |                  |                 |       |

|                | •                  |                                        |                 |                  |                  |                 |       |

|                |                    | upt is priority 1                      | ablad           |                  |                  |                 |       |

| L:1 11         |                    | upt source is dis                      |                 |                  |                  |                 |       |

| bit 11         | -                  | nted: Read as '                        |                 |                  |                  |                 |       |

| bit 10-8       |                    | D>: DMA Channe                         |                 | •                | e interrupt Prio | ity bits        |       |

|                | •                  | upt is priority 7 (I                   | lignest phone   | y interrupt)     |                  |                 |       |

|                | •                  |                                        |                 |                  |                  |                 |       |

|                | •                  |                                        |                 |                  |                  |                 |       |

|                |                    | upt is priority 1                      | ablad           |                  |                  |                 |       |

|                |                    | upt source is dis                      |                 |                  |                  |                 |       |

| bit 7-3        | -                  | nted: Read as '                        |                 |                  |                  |                 |       |

| bit 2-0        |                    | : Output Compa                         |                 | -                | ity bits         |                 |       |

|                | 111 = Interru<br>• | upt is priority 7 (I                   | nignest priorit | y interrupt)     |                  |                 |       |

|                | •                  |                                        |                 |                  |                  |                 |       |

|                |                    |                                        |                 |                  |                  |                 |       |

|                | •                  |                                        |                 |                  |                  |                 |       |

|                |                    | upt is priority 1<br>upt source is dis |                 |                  |                  |                 |       |

#### REGISTER 7-26: IPC11: INTERRUPT PRIORITY CONTROL REGISTER 11

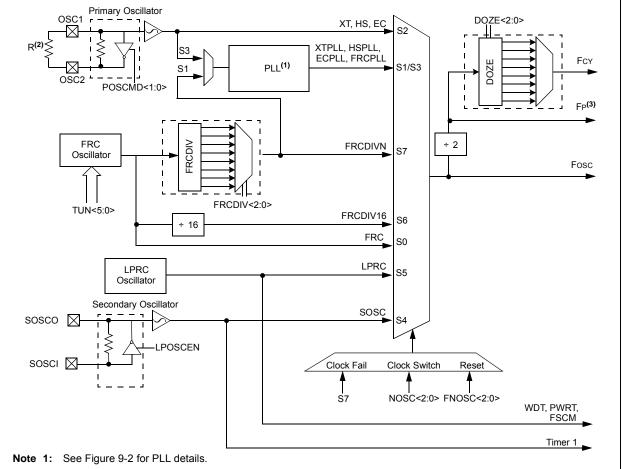

# 9.0 OSCILLATOR CONFIGURATION

- Note 1: This data sheet summarizes the features of the PIC24HJXXXGPX06A/X08A/X10A family of devices. However, it is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to Section 7. "Oscillator" (DS70186) of the "dsPIC33F/dsPIC33F/PIC24H Family Reference Manual", which is available from the Microchip web site (www.microchip.com).

- 2: Some registers and associated bits described in this section may not be available on all devices. Refer to Section 4.0 "Memory Organization" in this data sheet for device-specific register and bit information.

The PIC24HJXXXGPX06A/X08A/X10A oscillator system provides:

- Various external and internal oscillator options as clock sources

- An on-chip PLL to scale the internal operating frequency to the required system clock frequency

- The internal FRC oscillator can also be used with the PLL, thereby allowing full-speed operation without any external clock generation hardware

- Clock switching between various clock sources

- Programmable clock postscaler for system power savings

- A Fail-Safe Clock Monitor (FSCM) that detects clock failure and takes fail-safe measures

- An Oscillator Control register (OSCCON)

- Nonvolatile Configuration bits for main oscillator selection.

A simplified diagram of the oscillator system is shown in Figure 9-1.

### FIGURE 9-1: PIC24HJXXXGPX06A/X08A/X10A OSCILLATOR SYSTEM DIAGRAM

- 2: If the Oscillator is used with XT or HS modes, an extended parallel resistor with the value of 1 MΩ must be connected.

- **3:** The term, FP refers to the clock source for all the peripherals, while FCY refers to the clock source for the CPU. Throughout this document FP and FCY are used interchangeably, except in the case of Doze mode. FP and FCY will be different when Doze mode is used in any ratio other than 1:1, which is the default.

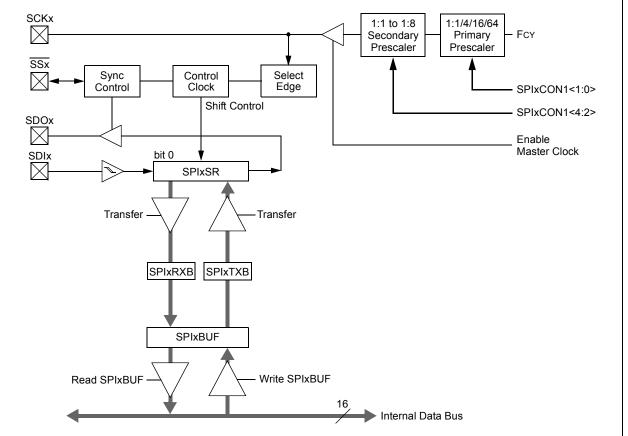

# 16.0 SERIAL PERIPHERAL INTERFACE (SPI)

- Note 1: This data sheet summarizes the features of the PIC24HJXXXGPX06A/X08A/X10A family of devices. However, it is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to the "dsPIC33F/PIC24H Family Reference Manual", Section 18. "Serial Peripheral Interface (SPI)" (DS70206), which is available from the Microchip web site (www.microchip.com).

- 2: Some registers and associated bits described in this section may not be available on all devices. Refer to **Section 4.0 "Memory Organization"** in this data sheet for device-specific register and bit information.

The Serial Peripheral Interface (SPI) module is a synchronous serial interface useful for communicating with other peripheral or microcontroller devices. These peripheral devices may be serial EEPROMs, shift registers, display drivers, Analog-to-Digital converters, etc. The SPI module is compatible with SPI and SIOP from Motorola<sup>®</sup>.

Note: In this section, the SPI modules are referred to together as SPIx, or separately as SPI1 and SPI2. Special Function Registers will follow a similar notation. For example, SPIxCON refers to the control register for the SPI1 or SPI2 module.

Each SPI module consists of a 16-bit shift register, SPIxSR (where x = 1 or 2), used for shifting data in and out, and a buffer register, SPIxBUF. A control register, SPIxCON, configures the module. Additionally, a status register, SPIxSTAT, indicates various status conditions.

The serial interface consists of 4 pins: SDIx (serial data input), SDOx (serial data output), SCKx (shift clock input or output), and SSx (active-low slave select).

In Master mode operation, SCK is a clock output but in Slave mode, it is a clock input.

# FIGURE 16-1: SPI MODULE BLOCK DIAGRAM

### 18.1 UART Helpful Tips

- 1. In multi-node direct-connect UART networks, receive inputs UART react to the complementary logic level defined by the URXINV bit (UxMODE<4>), which defines the idle state, the default of which is logic high, (i.e., URXINV = 0). Because remote devices do not initialize at the same time, it is likely that one of the devices, because the RX line is floating, will trigger a start bit detection and will cause the first byte received after the device has been initialized to be invalid. To avoid this situation, the user should use a pull-up or pull-down resistor on the RX pin depending on the value of the URXINV bit.

- a) If URXINV = 0, use a pull-up resistor on the RX pin.

- b) If URXINV = 1, use a pull-down resistor on the RX pin.

- 2. The first character received on a wake-up from Sleep mode caused by activity on the UxRX pin of the UART module will be invalid. In Sleep mode, peripheral clocks are disabled. By the time the oscillator system has restarted and stabilized from Sleep mode, the baud rate bit sampling clock relative to the incoming UxRX bit timing is no longer synchronized, resulting in the first character being invalid. This is to be expected.

#### 18.2 UART Resources

Many useful resources related to UART are provided on the main product page of the Microchip web site for the devices listed in this data sheet. This product page, which can be accessed using this link, contains the latest updates and additional information.

| Note: | In the event you are not able to access the product page using the link above, enter this URL in your browser: |

|-------|----------------------------------------------------------------------------------------------------------------|

|       | http://www.microchip.com/wwwproducts/<br>Devices.aspx?dDocName=en546061                                        |

#### 18.2.1 KEY RESOURCES

- Section 17. "UART" (DS70188)

- Code Samples

- Application Notes

- Software Libraries

- Webinars

- All related dsPIC33F/PIC24H Family Reference Manuals Sections

- Development Tools

### 19.0 ENHANCED CAN (ECAN™) MODULE

- Note 1: This data sheet summarizes the features of the PIC24HJXXXGPX06A/X08A/X10A family of devices. However, it is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to the *"dsPIC33F/PIC24H Family Reference Manual"*, Section 21. *"Enhanced Controller Area Network (ECAN™)"* (DS70185), which is available from the Microchip web site (www.microchip.com).

- 2: Some registers and associated bits described in this section may not be available on all devices. Refer to Section 4.0 "Memory Organization" in this data sheet for device-specific register and bit information.

### 19.1 Overview

The Enhanced Controller Area Network (ECAN<sup>™</sup>) module is a serial interface, useful for communicating with other CAN modules or microcontroller devices. This interface/protocol was designed to allow communications within noisy environments. The PIC24HJXXXGPX06A/X08A/X10A devices contain up to two ECAN modules.

The CAN module is a communication controller implementing the CAN 2.0 A/B protocol, as defined in the BOSCH specification. The module will support CAN 1.2, CAN 2.0A, CAN 2.0B Passive and CAN 2.0B Active versions of the protocol. The module implementation is a full CAN system. The CAN specification is not covered within this data sheet. The reader may refer to the BOSCH CAN specification for further details.

The module features are as follows:

- Implementation of the CAN protocol, CAN 1.2, CAN 2.0A and CAN 2.0B

- · Standard and extended data frames

- 0-8 bytes data length

- Programmable bit rate up to 1 Mbit/sec

- Automatic response to remote transmission requests

- Up to 8 transmit buffers with application specified prioritization and abort capability (each buffer may contain up to 8 bytes of data)

- Up to 32 receive buffers (each buffer may contain up to 8 bytes of data)

- Up to 16 full (standard/extended identifier)

acceptance filters

- 3 full acceptance filter masks

- DeviceNet<sup>™</sup> addressing support

- Programmable wake-up functionality with integrated low-pass filter

- Programmable Loopback mode supports self-test operation

- Signaling via interrupt capabilities for all CAN receiver and transmitter error states

- Programmable clock source

- Programmable link to input capture module (IC2 for both CAN1 and CAN2) for time-stamping and network synchronization

- · Low-power Sleep and Idle mode

The CAN bus module consists of a protocol engine and message buffering/control. The CAN protocol engine handles all functions for receiving and transmitting messages on the CAN bus. Messages are transmitted by first loading the appropriate data registers. Status and errors can be checked by reading the appropriate registers. Any message detected on the CAN bus is checked for errors and then matched against filters to see if it should be received and stored in one of the receive registers.

### 19.2 Frame Types

The CAN module transmits various types of frames which include data messages, remote transmission requests and as other frames that are automatically generated for control purposes. The following frame types are supported:

Standard Data Frame:

A standard data frame is generated by a node when the node wishes to transmit data. It includes an 11-bit standard identifier (SID) but not an 18-bit extended identifier (EID).

- Extended Data Frame: An extended data frame is similar to a standard data frame but includes an extended identifier as well.

- Remote Frame:

It is possible for a destination node to request the data from the source. For this purpose, the destination node sends a remote frame with an identifier that matches the identifier of the required data frame. The appropriate data source node will then send a data frame as a response to this remote request.

• Error Frame:

An error frame is generated by any node that detects a bus error. An error frame consists of two fields: an error flag field and an error delimiter field.

Overload Frame:

An overload frame can be generated by a node as a result of two conditions. First, the node detects a dominant bit during interframe space which is an illegal condition. Second, due to internal conditions, the node is not yet able to start reception of the next message. A node may generate a maximum of 2 sequential overload frames to delay the start of the next message.

· Interframe Space:

Interframe space separates a proceeding frame (of whatever type) from a following data or remote frame.

#### REGISTER 19-24: CIRXOVF1: ECAN™ MODULE RECEIVE BUFFER OVERFLOW REGISTER 1

| R/C-0   | R/C-0   | R/C-0   | R/C-0   | R/C-0   | R/C-0   | R/C-0  | R/C-0  |

|---------|---------|---------|---------|---------|---------|--------|--------|

| RXOVF15 | RXOVF14 | RXOVF13 | RXOVF12 | RXOVF11 | RXOVF10 | RXOVF9 | RXOVF8 |

| bit 15  |         |         |         |         |         |        | bit 8  |

| R/C-0  |

|--------|--------|--------|--------|--------|--------|--------|--------|

| RXOVF7 | RXOVF6 | RXOVF5 | RXOVF4 | RXOVF3 | RXOVF2 | RXOVF1 | RXOVF0 |

| bit 7  |        |        |        |        |        |        | bit 0  |

| Legend:           | C = Clear only bit |                       |                    |

|-------------------|--------------------|-----------------------|--------------------|

| R = Readable bit  | W = Writable bit   | U = Unimplemented bit | , read as '0'      |

| -n = Value at POR | '1' = Bit is set   | '0' = Bit is cleared  | x = Bit is unknown |

bit 15-0 **RXOVF15:RXOVF0:** Receive Buffer n Overflow bits

1 = Module pointed a write to a full buffer (set by module)

0 = Overflow is cleared (clear by application software)

#### REGISTER 19-25: CIRXOVF2: ECAN™ MODULE RECEIVE BUFFER OVERFLOW REGISTER 2

| R/C-0   |

|---------|---------|---------|---------|---------|---------|---------|---------|

| RXOVF31 | RXOVF30 | RXOVF29 | RXOVF28 | RXOVF27 | RXOVF26 | RXOVF25 | RXOVF24 |

| bit 15  |         |         |         |         |         |         | bit 8   |

| R/C-0   |

|---------|---------|---------|---------|---------|---------|---------|---------|

| RXOVF23 | RXOVF22 | RXOVF21 | RXOVF20 | RXOVF19 | RXOVF18 | RXOVF17 | RXOVF16 |

| bit 7   |         |         |         |         |         |         | bit 0   |

| Legend:           | C = Clear only bit |                       |                                    |  |  |

|-------------------|--------------------|-----------------------|------------------------------------|--|--|

| R = Readable bit  | W = Writable bit   | U = Unimplemented bit | U = Unimplemented bit, read as '0' |  |  |

| -n = Value at POR | '1' = Bit is set   | '0' = Bit is cleared  | x = Bit is unknown                 |  |  |

bit 15-0 RXOVF31:RXOVF16: Receive Buffer n Overflow bits

1 = Module pointed a write to a full buffer (set by module)

0 = Overflow is cleared (clear by application software)

### REGISTER 19-29: CITRBnDLC: ECAN™ MODULE BUFFER n DATA LENGTH CONTROL

(n = 0, 1, ..., 31)

|               | (11 – 🖣                     | , .,,,                     |              |                                         |       |        |       |

|---------------|-----------------------------|----------------------------|--------------|-----------------------------------------|-------|--------|-------|

| R/W-x         | R/W-x                       | R/W-x                      | R/W-x        | R/W-x                                   | R/W-x | R/W-x  | R/W-x |

|               |                             | EID<                       | :5:0>        |                                         |       | RTR    | RB1   |

| bit 15        |                             |                            |              |                                         |       |        | bit 8 |

| U-0           | U-0                         | U-0                        | R/W-x        | R/W-x                                   | R/W-x | R/W-x  | R/W-x |

| _             | _                           | _                          | RB0          |                                         | DLC   | 2<3:0> |       |

| bit 7         |                             |                            |              |                                         |       |        | bit 0 |

|               |                             |                            |              |                                         |       |        |       |

| Legend:       |                             |                            |              |                                         |       |        |       |

| R = Readable  | e bit                       | W = Writable               | bit          | U = Unimplemented bit, read as '0'      |       |        |       |

| -n = Value at | POR                         | '1' = Bit is se            | t            | '0' = Bit is cleared x = Bit is unknown |       |        |       |

|               |                             |                            |              |                                         |       |        |       |

| bit 15-10     | EID<5:0>: E                 | xtended Identi             | fier bits    |                                         |       |        |       |

| bit 9         | RTR: Remote                 | e Transmission             | Request bit  |                                         |       |        |       |

|               | 1 = Message<br>0 = Normal n | will request re<br>ressage | mote transmi | ssion                                   |       |        |       |

| bit 8         | RB1: Reserv                 | ed Bit 1                   |              |                                         |       |        |       |

|               |                             |                            |              |                                         |       |        |       |

|         | User must set this bit to '0' per CAN protocol. |

|---------|-------------------------------------------------|

| bit 7-5 | Unimplemented: Read as '0'                      |

| bit 4   | RB0: Reserved Bit 0                             |

|         | User must set this bit to '0' per CAN protocol. |

bit 3-0 DLC<3:0>: Data Length Code bits

# REGISTER 19-30: CiTRBnDm: ECAN<sup>TM</sup> MODULE BUFFER n DATA FIELD BYTE m $(n = 0, 1, ..., 31; m = 0, 1, ..., 7)^{(1)}$

| R/W-x       | R/W-x | R/W-x | R/W-x | R/W-x | R/W-x | R/W-x | R/W-x |  |

|-------------|-------|-------|-------|-------|-------|-------|-------|--|

| TRBnDm<7:0> |       |       |       |       |       |       |       |  |

| bit 7       |       |       |       |       |       |       | bit 0 |  |

| Legend:           |                  |                             |                    |

|-------------------|------------------|-----------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, read | d as '0'           |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared        | x = Bit is unknown |

#### bit 7-0 TRnDm<7:0>: Data Field Buffer 'n' Byte 'm' bits

Note 1: The Most Significant Byte contains byte (m + 1) of the buffer.

# 20.6 ADC Control Registers

### **REGISTER 20-1:** ADxCON1: ADCx CONTROL REGISTER 1(where x = 1 or 2)

| R/W-0  | U-0       | R/W-0  | R/W-0   | U-0    | R/W-0 | R/W-0 | R/W-0  |

|--------|-----------|--------|---------|--------|-------|-------|--------|

| ADON   | _         | ADSIDL | ADDMABM |        | AD12B | FORM  | 1<1:0> |

| bit 15 |           |        |         |        |       |       | bit 8  |

|        |           |        |         |        |       |       |        |

| R/W-0  | R/W-0     | R/W-0  | U-0     | R/W-0  | R/W-0 | R/W-0 | R/C-0  |

|        |           |        |         |        |       | HC,HS | HC, HS |

|        | SSRC<2:0> |        | —       | SIMSAM | ASAM  | SAMP  | DONE   |

| bit 7  |           |        |         |        |       |       | bit 0  |

| Legend: HC = Cleared by hardware |                  | HS = Set by hardware      |                    |  |  |

|----------------------------------|------------------|---------------------------|--------------------|--|--|

| R = Readable bit                 | W = Writable bit | U = Unimplemented bit, re | ad as '0'          |  |  |

| -n = Value at POR                | '1' = Bit is set | '0' = Bit is cleared      | x = Bit is unknown |  |  |

| bit 15  | ADON: ADC Operating Mode bit                                                                                                                                                                                       |

|---------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|         | 1 = ADC module is operating                                                                                                                                                                                        |

|         | 0 = ADC module is off                                                                                                                                                                                              |

| bit 14  | Unimplemented: Read as '0'                                                                                                                                                                                         |

| bit 13  | ADSIDL: Stop in Idle Mode bit                                                                                                                                                                                      |

|         | 1 = Discontinue module operation when device enters Idle mode                                                                                                                                                      |

|         | 0 = Continue module operation in Idle mode                                                                                                                                                                         |

| bit 12  | ADDMABM: DMA Buffer Build Mode bit                                                                                                                                                                                 |

|         | 1 = DMA buffers are written in the order of conversion. The module will provide an address to the DMA channel that is the same as the address used for the non-DMA stand-alone buffer                              |

|         | <ul> <li>DMA buffers are written in Scatter/Gather mode. The module will provide a scatter/gather address<br/>to the DMA channel, based on the index of the analog input and the size of the DMA buffer</li> </ul> |

| bit 11  | Unimplemented: Read as '0'                                                                                                                                                                                         |

| bit 10  | AD12B: 10-Bit or 12-Bit Operation Mode bit                                                                                                                                                                         |

|         | 1 = 12-bit, 1-channel ADC operation                                                                                                                                                                                |

|         | 0 = 10-bit, 4-channel ADC operation                                                                                                                                                                                |

| bit 9-8 | FORM<1:0>: Data Output Format bits                                                                                                                                                                                 |

|         | For 10-bit operation:                                                                                                                                                                                              |

|         | 11 = Reserved                                                                                                                                                                                                      |

|         | 10 = Reserved                                                                                                                                                                                                      |

|         | 01 = Signed integer (Dout = ssss sssd dddd dddd, where s = .NOT.d<9>)<br>00 = Integer (Dout = 0000 00dd dddd dddd)                                                                                                 |

|         | For 12-bit operation:                                                                                                                                                                                              |

|         | 11 = Reserved                                                                                                                                                                                                      |

|         | 10 = Reserved                                                                                                                                                                                                      |

|         | 01 = Signed Integer (DOUT = ssss sddd dddd dddd, where s = .NOT.d<11>)                                                                                                                                             |

|         | 00 = Integer (DOUT = 0000  dddd  dddd  dddd)                                                                                                                                                                       |

| bit 7-5 | SSRC<2:0>: Sample Clock Source Select bits                                                                                                                                                                         |

|         | <ul><li>111 = Internal counter ends sampling and starts conversion (auto-convert)</li><li>110 = Reserved</li></ul>                                                                                                 |

|         | 100 - Reserved                                                                                                                                                                                                     |

|         | 100 = GP timer (Timer5 for ADC1, Timer3 for ADC2) compare ends sampling and starts conversion                                                                                                                      |

|         | 011 = Reserved<br>010 = GP timer (Timer3 for ADC1, Timer5 for ADC2) compare ends sampling and starts conversion                                                                                                    |

|         | 001 = Active transition on INT0 pin ends sampling and starts conversion                                                                                                                                            |

|         | 000 = Clearing sample bit ends sampling and starts conversion                                                                                                                                                      |

#### **REGISTER 20-1:** ADxCON1: ADCx CONTROL REGISTER 1(where x = 1 or 2) (CONTINUED)

| bit 4 | Unimplemented: Read as '0'                                                                                                                                                                                                                                                                                                                                                                                            |

|-------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| bit 3 | SIMSAM: Simultaneous Sample Select bit (only applicable when CHPS<1:0> = 01 or 1x)                                                                                                                                                                                                                                                                                                                                    |

|       | <pre>When AD12B = 1, SIMSAM is: U-0, Unimplemented, Read as '0' 1 = Samples CH0, CH1, CH2, CH3 simultaneously (when CHPS&lt;1:0&gt; = 1x); or Samples CH0 and CH1 simultaneously (when CHPS&lt;1:0&gt; = 01) 0 = Samples multiple channels individually in sequence</pre>                                                                                                                                             |

| bit 2 | ASAM: ADC Sample Auto-Start bit                                                                                                                                                                                                                                                                                                                                                                                       |

|       | <ul> <li>1 = Sampling begins immediately after last conversion. SAMP bit is auto-set</li> <li>0 = Sampling begins when SAMP bit is set</li> </ul>                                                                                                                                                                                                                                                                     |

| bit 1 | SAMP: ADC Sample Enable bit                                                                                                                                                                                                                                                                                                                                                                                           |

|       | <ul> <li>1 = ADC sample/hold amplifiers are sampling</li> <li>0 = ADC sample/hold amplifiers are holding</li> <li>If ASAM = 0, software may write '1' to begin sampling. Automatically set by hardware if ASAM = 1.</li> <li>If SSRC = 000, software may write '0' to end sampling and start conversion. If SSRC ≠ 000, automatically cleared by hardware to end sampling and start conversion.</li> </ul>            |

| bit 0 | DONE: ADC Conversion Status bit                                                                                                                                                                                                                                                                                                                                                                                       |

|       | <ul> <li>1 = ADC conversion cycle is completed.</li> <li>0 = ADC conversion not started or in progress</li> <li>Automatically set by hardware when analog-to-digital conversion is complete. Software may write '0' to clear DONE status (software not allowed to write '1'). Clearing this bit will NOT affect any operation in progress. Automatically cleared by hardware at start of a new conversion.</li> </ul> |

| R/W-0           | U-0                                      | U-0                                      | R/W-0           | R/W-0             | R/W-0                   | R/W-0           | R/W-0 |  |  |  |  |  |

|-----------------|------------------------------------------|------------------------------------------|-----------------|-------------------|-------------------------|-----------------|-------|--|--|--|--|--|

| CH0NB           |                                          |                                          |                 |                   | CH0SB<4:0>(1)           | )               |       |  |  |  |  |  |

| bit 15          |                                          | -                                        |                 |                   |                         |                 | bit 8 |  |  |  |  |  |

|                 |                                          |                                          |                 |                   |                         |                 |       |  |  |  |  |  |

| R/W-0           | U-0                                      | U-0                                      | R/W-0           | R/W-0             | R/W-0                   | R/W-0           | R/W-0 |  |  |  |  |  |

| CH0NA           |                                          |                                          |                 |                   | CH0SA<4:0>(1            | )               |       |  |  |  |  |  |

| bit 7           |                                          |                                          |                 |                   |                         |                 | bit 0 |  |  |  |  |  |

|                 |                                          |                                          |                 |                   |                         |                 |       |  |  |  |  |  |

| Legend:         |                                          |                                          |                 |                   |                         |                 |       |  |  |  |  |  |

| R = Readable    |                                          | W = Writable b                           | it              | •                 | nented bit, read        |                 |       |  |  |  |  |  |

| -n = Value at F | POR                                      | '1' = Bit is set                         |                 | '0' = Bit is clea | ared                    | x = Bit is unkr | nown  |  |  |  |  |  |

| h# 45           |                                          |                                          | Innut Calast    | far Camala D hi   |                         |                 |       |  |  |  |  |  |

| bit 15          |                                          | annel 0 Negative<br>0 negative input     | -               | Ior Sample B bi   | IL                      |                 |       |  |  |  |  |  |

|                 |                                          | 0 negative input                         |                 |                   |                         |                 |       |  |  |  |  |  |

| bit 14-13       | Unimplemer                               | nted: Read as '0                         | ,               |                   |                         |                 |       |  |  |  |  |  |

| bit 12-8        | CH0SB<4:0>                               | -: Channel 0 Pos                         | sitive Input Se | elect for Sample  | e B bits <sup>(1)</sup> |                 |       |  |  |  |  |  |

|                 | 11111 <b>= Ch</b> a                      | annel 0 positive i                       | nput is AN31    |                   |                         |                 |       |  |  |  |  |  |

|                 | 11110 = Channel 0 positive input is AN30 |                                          |                 |                   |                         |                 |       |  |  |  |  |  |

|                 | •                                        |                                          |                 |                   |                         |                 |       |  |  |  |  |  |

|                 | •                                        |                                          |                 |                   |                         |                 |       |  |  |  |  |  |

|                 |                                          | annel 0 positive i                       |                 |                   |                         |                 |       |  |  |  |  |  |

|                 |                                          | annel 0 positive i<br>annel 0 positive i |                 |                   |                         |                 |       |  |  |  |  |  |

| bit 7           |                                          | annel 0 Negative                         | •               | for Sample A bi   | it                      |                 |       |  |  |  |  |  |

|                 |                                          | 0 negative input                         |                 |                   |                         |                 |       |  |  |  |  |  |

|                 |                                          | 0 negative input                         |                 |                   |                         |                 |       |  |  |  |  |  |

| bit 6-5         | Unimplemer                               | nted: Read as '0                         | ,               |                   |                         |                 |       |  |  |  |  |  |

| bit 4-0         | CH0SA<4:0>                               | Channel 0 Pos                            | itive Input Se  | elect for Sample  | e A bits <sup>(1)</sup> |                 |       |  |  |  |  |  |

|                 |                                          | annel 0 positive i                       |                 |                   |                         |                 |       |  |  |  |  |  |

|                 | 11110 = Cha                              | annel 0 positive i                       | nput is AN30    |                   |                         |                 |       |  |  |  |  |  |

|                 | •                                        |                                          |                 |                   |                         |                 |       |  |  |  |  |  |

|                 | •                                        |                                          |                 |                   |                         |                 |       |  |  |  |  |  |

|                 |                                          | annel 0 positive i                       |                 |                   |                         |                 |       |  |  |  |  |  |

|                 |                                          | annel 0 positive i<br>annel 0 positive i |                 |                   |                         |                 |       |  |  |  |  |  |

|                 |                                          |                                          | 1               |                   |                         |                 |       |  |  |  |  |  |

#### REGISTER 20-6: ADxCHS0: ADCx INPUT CHANNEL 0 SELECT REGISTER

#### TABLE 24-17: PLL CLOCK TIMING SPECIFICATIONS (VDD = 3.0V TO 3.6V)

| AC CHARACTERISTICS |        |                                                                                    |    |     | ure -40°           | $C \le TA \le$ | +85°C f | (unless otherwise stated)<br>for Industrial<br>for Extended |

|--------------------|--------|------------------------------------------------------------------------------------|----|-----|--------------------|----------------|---------|-------------------------------------------------------------|

| Param<br>No.       | Symbol | bol Characteristic                                                                 |    | Min | Typ <sup>(1)</sup> | Max            | Units   | Conditions                                                  |

| OS50               | Fplli  | PLL Voltage Controlled<br>Oscillator (VCO) Input<br>Frequency Range <sup>(2)</sup> |    | 0.8 | _                  | 8              | MHz     | ECPLL, HSPLL, XTPLL<br>modes                                |

| OS51               | Fsys   | On-Chip VCO System<br>Frequency                                                    |    | 100 | —                  | 200            | MHz     | _                                                           |

| OS52               | TLOCK  | PLL Start-up Time (Lock Time)                                                      |    | 0.9 | 1.5                | 3.1            | mS      | —                                                           |

| OS53               | DCLK   | CLKO Stability (Jitter                                                             | .) | -3  | 0.5                | 3              | %       | Measured over 100 ms period                                 |

**Note 1:** Data in "Typ" column is at 3.3V, 25°C unless otherwise stated. Parameters are for design guidance only and are not tested.

2: These parameters are characterized by similarity but are not tested in manufacturing. This specification is based on clock cycle by clock cycle measurements. To calculate the effective jitter for individual time base or communication clocks used by peripherals use the formula:

Peripheral Clock Jitter = DCLK /  $\sqrt{(Fosc/Peripheral bit rate clock)}$

Example Only: Fosc = 80 MHz, DCLK = 3%, SPI bit rate clock, (i.e. SCK), is 5 MHz

SPI SCK Jitter = [ DCLK / \(\lambda(80 MHz/5 MHz))] = [3\(\lambda / 16] = [3\(\lambda / 4] = 0.75\)

#### TABLE 24-18: AC CHARACTERISTICS: INTERNAL FRC ACCURACY

| AC CHA       | RACTERISTICS                                      |     | d Operating temper |     | -40°0 | <b>3.0V to 3.6V (unless ot</b> $C \le TA \le +85^{\circ}C$ for Indu $C \le TA \le +125^{\circ}C$ for Extermine | strial         |  |  |  |  |

|--------------|---------------------------------------------------|-----|--------------------|-----|-------|----------------------------------------------------------------------------------------------------------------|----------------|--|--|--|--|

| Param<br>No. | Characteristic                                    | Min | Тур                | Max | Units | Conditions                                                                                                     |                |  |  |  |  |

|              | Internal FRC Accuracy @ 7.3728 MHz <sup>(1)</sup> |     |                    |     |       |                                                                                                                |                |  |  |  |  |

| F20a         | FRC                                               | -2  | _                  | +2  | %     | $-40^{\circ}C \leq TA \leq +85^{\circ}C$                                                                       | VDD = 3.0-3.6V |  |  |  |  |

| F20b         | FRC                                               | -5  | _                  | +5  | %     | $-40^{\circ}C \le TA \le +125^{\circ}C \qquad VDD = 3.0-3.6V$                                                  |                |  |  |  |  |

Note 1: Frequency calibrated at 25°C and 3.3V. TUN bits can be used to compensate for temperature drift.

#### TABLE 24-19: INTERNAL LPRC ACCURACY

| AC CH        | ARACTERISTICS                    | $\begin{array}{ll} \mbox{Standard Operating Conditions: 3.0V to 3.6V (unless otherwise stated)} \\ \mbox{Operating temperature} & -40^\circ C \leq TA \leq +85^\circ C \mbox{ for Industrial} \\ -40^\circ C \leq TA \leq +125^\circ C \mbox{ for Extended} \end{array}$ |     |     |       |                                                       |   |  |  |

|--------------|----------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|-----|-------|-------------------------------------------------------|---|--|--|

| Param<br>No. | Characteristic                   | Min                                                                                                                                                                                                                                                                      | Тур | Max | Units | Conditions                                            |   |  |  |

|              | LPRC @ 32.768 kHz <sup>(1)</sup> |                                                                                                                                                                                                                                                                          |     |     |       |                                                       |   |  |  |

| F21a         | LPRC                             | -30                                                                                                                                                                                                                                                                      | _   | +30 | %     | $-40^\circ C \le T A \le +85^\circ C$                 | — |  |  |

| F21b         | LPRC                             | -35                                                                                                                                                                                                                                                                      | _   | +35 | %     | $-40^{\circ}C \le TA \le +125^{\circ}C \qquad \qquad$ |   |  |  |

**Note 1:** Change of LPRC frequency as VDD changes.

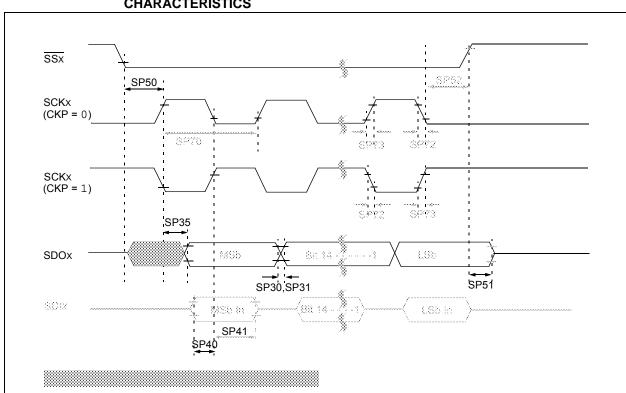

# FIGURE 24-16: SPIX SLAVE MODE (FULL-DUPLEX, CKE = 0, CKP = 0, SMP = 0) TIMING CHARACTERISTICS

| AC CHARACTERISTICS |        |                                | $\begin{array}{l} \mbox{Standard Operating Conditions: 3.0V to 3.6V} \\ \mbox{(unless otherwise stated)} \\ \mbox{Operating temperature} & -40^{\circ}C \leq TA \leq +85^{\circ}C \mbox{ for Industrial} \\ & -40^{\circ}C \leq TA \leq +125^{\circ}C \mbox{ for Extended} \end{array}$ |           |           |           |                                                  |

|--------------------|--------|--------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------|-----------|-----------|--------------------------------------------------|

| Param<br>No.       | Symbol | Characteristic                 | Min.                                                                                                                                                                                                                                                                                    | Тур       | Max.      | Units     | Conditions                                       |

|                    |        | ADC Accuracy (12-bit Mode      | e) – Meas                                                                                                                                                                                                                                                                               | uremen    | ts with e | xternal   | VREF+/VREF-                                      |

| AD20a              | Nr     | Resolution                     | 1:                                                                                                                                                                                                                                                                                      | 2 data bi | ts        | bits      |                                                  |

| AD21a              | INL    | Integral Nonlinearity          | -2                                                                                                                                                                                                                                                                                      | -         | +2        | LSb       | VINL = AVSS = VREFL = 0V,<br>AVDD = VREFH = 3.6V |

| AD22a              | DNL    | Differential Nonlinearity      | >-1                                                                                                                                                                                                                                                                                     | _         | <1        | LSb       | VINL = AVSS = VREFL = 0V,<br>AVDD = VREFH = 3.6V |