Welcome to E-XFL.COM

### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

### Details

E·XFI

| Details                    |                                                                                 |

|----------------------------|---------------------------------------------------------------------------------|

| Product Status             | Active                                                                          |

| Core Processor             | PIC                                                                             |

| Core Size                  | 16-Bit                                                                          |

| Speed                      | 40 MIPs                                                                         |

| Connectivity               | CANbus, I <sup>2</sup> C, IrDA, LINbus, SPI, UART/USART                         |

| Peripherals                | Brown-out Detect/Reset, DMA, POR, PWM, WDT                                      |

| Number of I/O              | 53                                                                              |

| Program Memory Size        | 64KB (22K x 24)                                                                 |

| Program Memory Type        | FLASH                                                                           |

| EEPROM Size                | -                                                                               |

| RAM Size                   | 8K x 8                                                                          |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 3.6V                                                                       |

| Data Converters            | A/D 18x10b/12b                                                                  |

| Oscillator Type            | Internal                                                                        |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                               |

| Mounting Type              | Surface Mount                                                                   |

| Package / Case             | 64-VFQFN Exposed Pad                                                            |

| Supplier Device Package    | 64-VQFN (9x9)                                                                   |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic24hj64gp506at-i-mr |

|                            |                                                                                 |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

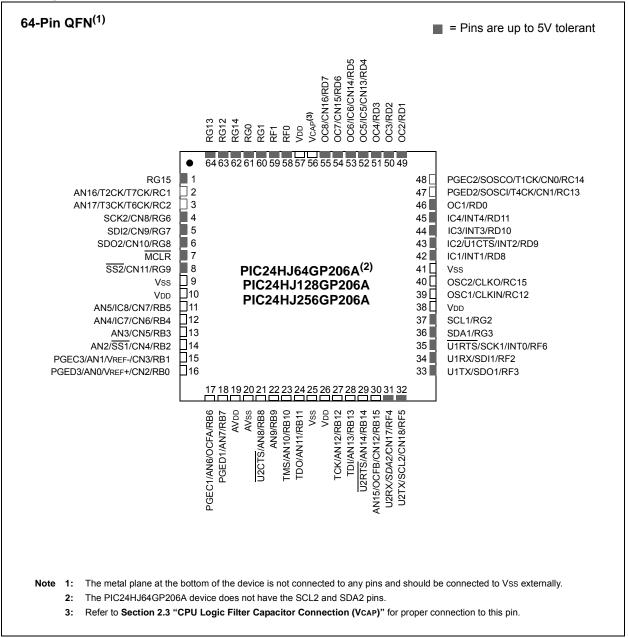

## Pin Diagrams

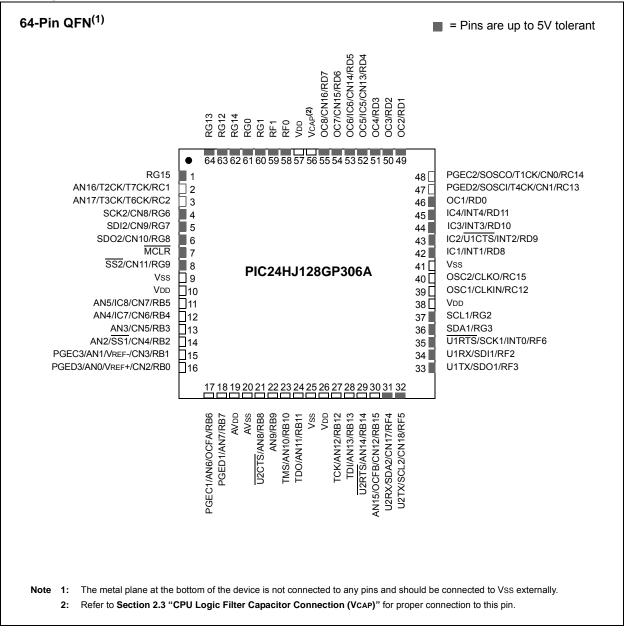

## Pin Diagrams (Continued)

## Referenced Sources

This device data sheet is based on the following individual chapters of the *"dsPlC33F/PlC24H Family Reference Manual"*. These documents should be considered as the general reference for the operation of a particular module or device feature.

Note: To access the documents listed below, browse to the documentation section of the PIC24HJ256GP610A product page on the Microchip web site (www.microchip.com) or by selecting a family reference manual section from the following list.

In addition to parameters, features, and other documentation, the resulting page provides links to the related family reference manual sections.

- Section 1. "Introduction" (DS70197)

- Section 2. "CPU" (DS70204)

- Section 3. "Data Memory" (DS70202)

- Section 4. "Program Memory" (DS70203)

- Section 5. "Flash Programming" (DS70191)

- Section 6. "Interrupts" (DS70184)

- Section 7. "Oscillator" (DS70186)

- Section 8. "Reset" (DS70192)

- Section 9. "Watchdog Timer and Power-Saving Modes" (DS70196)

- Section 10. "I/O Ports" (DS70193)

- Section 11. "Timers" (DS70205)

- Section 12. "Input Capture" (DS70198)

- Section 13. "Output Compare" (DS70209)

- Section 16. "Analog-to-Digital Converter (ADC)" (DS70183)

- Section 17. "UART" (DS70188)

- Section 18. "Serial Peripheral Interface (SPI)" (DS70206)

- Section 19. "Inter-Integrated Circuit<sup>™</sup> (I2C<sup>™</sup>)" (DS70195)

- Section 20. "Data Converter Interface (DCI)" (DS70288)

- Section 21. "Enhanced Controller Area Network (ECAN™)" (DS70185)

- Section 22. "Direct Memory Access (DMA)" (DS70182)

- Section 23. "CodeGuard™ Security" (DS70199)

- Section 24. "Programming and Diagnostics" (DS70207)

- Section 25. "Device Configuration" (DS70194)

| REGISTER 3-2. CORCON: CORE CONTROL REGISTER | REGISTER 3-2: | CORCON: CORE CONTROL REGISTER |

|---------------------------------------------|---------------|-------------------------------|

|---------------------------------------------|---------------|-------------------------------|

| U-0                        | U-0           | U-0               | U-0              | U-0                 | U-0                                | U-0              | U-0   |  |

|----------------------------|---------------|-------------------|------------------|---------------------|------------------------------------|------------------|-------|--|

| —                          | —             | —                 | —                | —                   | -                                  | —                | —     |  |

| bit 15                     |               |                   |                  |                     |                                    |                  | bit 8 |  |

|                            |               |                   |                  |                     |                                    |                  |       |  |

| U-0                        | U-0           | U-0               | U-0              | R/C-0               | R/W-0                              | U-0              | U-0   |  |

|                            | —             | —                 | —                | IPL3 <sup>(1)</sup> | PSV                                | —                | —     |  |

| bit 7                      |               |                   | •                |                     |                                    |                  | bit 0 |  |

|                            |               |                   |                  |                     |                                    |                  |       |  |

| Legend: C = Clear only bit |               |                   | y bit            |                     |                                    |                  |       |  |

| R = Readable               | e bit         | W = Writable      | bit              | -n = Value at       | POR                                | '1' = Bit is set |       |  |

| 0' = Bit is clea           | ared          | 'x = Bit is unk   | nown             | U = Unimpler        | U = Unimplemented bit, read as '0' |                  |       |  |

|                            |               |                   |                  |                     |                                    |                  |       |  |

| bit 15-4                   | Unimplemen    | ted: Read as '    | 0'               |                     |                                    |                  |       |  |

| bit 3                      | IPL3: CPU In  | terrupt Priority  | Level Status b   | oit 3(1)            |                                    |                  |       |  |

|                            | 1 = CPU inter | rupt priority lev | el is greater tl | han 7               |                                    |                  |       |  |

|                            | 0 = CPU inter | rupt priority lev | el is 7 or less  |                     |                                    |                  |       |  |

| bit 2                      | PSV: Program  | n Space Visibili  | ty in Data Spa   | ice Enable bit      |                                    |                  |       |  |

|                            | 1 = Program   | space visible in  | data space       |                     |                                    |                  |       |  |

|                            | 0 = Program   | space not visib   | le in data spac  | ce                  |                                    |                  |       |  |

| bit 1-0                    | Unimplemen    | ted: Read as '    | 0'               |                     |                                    |                  |       |  |

|                            |               |                   |                  |                     |                                    |                  |       |  |

Note 1: The IPL3 bit is concatenated with the IPL<2:0> bits (SR<7:5>) to form the CPU interrupt priority level.

## 4.0 MEMORY ORGANIZATION

Note: This data sheet summarizes the features of the PIC24HJXXXGPX06A/X08A/X10A family of devices. However, it is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to **Section 3.** "**Data Memory**" (DS70202) of the "dsPIC33F/PIC24H Family Reference Manual", which is available from the Microchip web site (www.microchip.com).

The PIC24HJXXXGPX06A/X08A/X10A architecture features separate program and data memory spaces and buses. This architecture also allows the direct access of program memory from the data space during code execution.

## 4.1 Program Address Space

The program address memory space of the PIC24HJXXXGPX06A/X08A/X10A devices is 4M instructions. The space is addressable by a 24-bit value derived from either the 23-bit Program Counter (PC) during program execution, or from table operation or data space remapping as described in **Section 4.4** "Interfacing Program and Data Memory Spaces".

User access to the program memory space is restricted to the lower half of the address range (0x000000 to 0x7FFFFF). The exception is the use of TBLRD/TBLWT operations, which use TBLPAG<7> to permit access to the Configuration bits and Device ID sections of the configuration memory space.

Memory maps for the PIC24HJXXXGPX06A/X08A/ X10A family of devices are shown in Figure 4-1.

|                            | PIC24HJ64XXXXXA                                    |  | PIC24HJ128XXXXXA                  | PIC24HJ256XXXXXA                      |                                  |

|----------------------------|----------------------------------------------------|--|-----------------------------------|---------------------------------------|----------------------------------|

| <b>▲</b>                   | GOTO Instruction                                   |  | GOTO Instruction                  | <br>GOTO Instruction                  | 0x000000<br>- 0x000002           |

|                            | Reset Address                                      |  | Reset Address                     | <br>Reset Address                     | 0x000004                         |

|                            | Interrupt Vector Table                             |  | Interrupt Vector Table            | Interrupt Vector Table                | 0x0000FE                         |

|                            | Reserved                                           |  | Reserved                          | <br>Reserved                          | 0x000100                         |

|                            | Alternate Vector Table                             |  | Alternate Vector Table            | Alternate Vector Table                | 0x000104<br>0x0001FE             |

| User Memory Space          | User Program<br>Flash Memory<br>(22K instructions) |  | User Program<br>Flash Memory      | <br>User Program<br>Flash Memory      | 0x000200                         |

| emory                      |                                                    |  | (44K instructions)                | (88K instructions)                    | 0x0157FE                         |

| ser Mo                     |                                                    |  |                                   | <br>                                  | 0x015800                         |

| Š                          | Unimplemented<br>(Read '0's)                       |  | Unimplemented<br>(Read '0's)      |                                       | 0x02ABFE<br>0x02AC00             |

|                            |                                                    |  |                                   | Unimplemented<br>(Read '0's)          |                                  |

|                            |                                                    |  |                                   |                                       | 0x7FFFE<br>0x800000              |

| ry Space                   | Reserved                                           |  | Reserved                          | Reserved                              | 0×F7FFE                          |

| IOU                        | Device Configuration<br>Registers                  |  | Device Configuration<br>Registers | <br>Device Configuration<br>Registers | 0xF80000                         |

| Configuration Memory Space | Registers                                          |  | Reserved                          | <br>Reserved                          | 0xF80017<br>0xF80010             |

|                            | DEVID (2)                                          |  | DEVID (2)                         | <br>DEVID (2)                         | 0xFEFFFE<br>0xFF0000<br>0xFFFFFE |

### FIGURE 4-1: PROGRAM MEMORY MAP FOR PIC24HJXXXGPX06A/X08A/X10A FAMILY DEVICES

| File Name  | Addr | Bit 15 | Bit 14    | Bit 13 | Bit 12 | Bit 11   | Bit 10   | Bit 9    | Bit 8    | Bit 7                        | Bit 6    | Bit 5 | Bit 4  | Bit 3  | Bit 2  | Bit 1 | Bit 0  | All<br>Resets |

|------------|------|--------|-----------|--------|--------|----------|----------|----------|----------|------------------------------|----------|-------|--------|--------|--------|-------|--------|---------------|

| C1RXF1EID  | 0446 |        | 1         | 1      | EID<   | :15:8>   |          |          |          | EID<7:0>                     |          |       |        |        |        |       | xxxx   |               |

| C1RXF2SID  | 0448 |        |           |        | SID<   | :10:3>   |          |          |          | SID<2:0> — EXIDE — EID<17:10 |          |       | 17:16> | xxxx   |        |       |        |               |

| C1RXF2EID  | 044A |        |           |        | EID<   | :15:8>   |          |          |          |                              |          |       | EID<   | 7:0>   |        |       |        | xxxx          |

| C1RXF3SID  | 044C |        |           |        | SID<   | :10:3>   |          |          |          |                              | SID<2:0> |       | _      | EXIDE  | _      | EID<  | 17:16> | xxxx          |

| C1RXF3EID  | 044E |        | EID<15:8> |        |        |          |          |          |          |                              | EID<     | 7:0>  |        |        |        | xxxx  |        |               |

| C1RXF4SID  | 0450 |        | SID<10:3> |        |        |          |          |          | SID<2:0> |                              | _        | EXIDE | _      | EID<   | 17:16> | xxxx  |        |               |

| C1RXF4EID  | 0452 |        | EID<15:8> |        |        |          |          |          |          |                              | EID<     | 7:0>  |        |        |        | xxxx  |        |               |

| C1RXF5SID  | 0454 |        |           |        | SID<   | :10:3>   |          |          |          |                              | SID<2:0> |       | _      | EXIDE  | —      | EID<' | 17:16> | xxxx          |

| C1RXF5EID  | 0456 |        |           |        | EID<   | :15:8>   |          |          |          |                              |          |       | EID<   | 7:0>   |        |       |        | xxxx          |

| C1RXF6SID  | 0458 |        |           |        | SID<   | :10:3>   |          |          |          | SID<2:0> — EXIDE — EID<1     |          |       |        |        | 17:16> | xxxx  |        |               |

| C1RXF6EID  | 045A |        | EID<15:8> |        |        |          | EID<7:0> |          |          |                              |          |       |        | xxxx   |        |       |        |               |

| C1RXF7SID  | 045C |        | SID<10:3> |        |        |          |          | SID<2:0> |          | —                            | EXIDE    | —     | EID<'  | 17:16> | xxxx   |       |        |               |

| C1RXF7EID  | 045E |        | EID<15:8> |        |        |          | EID<7:0> |          |          |                              |          |       | xxxx   |        |        |       |        |               |

| C1RXF8SID  | 0460 |        | SID<10:3> |        |        |          |          | SID<2:0> |          | —                            | EXIDE    | _     | EID<'  | 17:16> | xxxx   |       |        |               |

| C1RXF8EID  | 0462 |        |           |        | EID<   | :15:8>   |          |          |          | EID<7:0>                     |          |       |        |        |        | xxxx  |        |               |

| C1RXF9SID  | 0464 |        |           |        | SID<   | :10:3>   |          |          |          | SID<2:0> — EXIDE — EID<      |          |       |        |        | 17:16> | xxxx  |        |               |

| C1RXF9EID  | 0466 |        |           |        | EID<   | :15:8>   |          |          |          | EID<7:0>                     |          |       |        |        |        |       | xxxx   |               |

| C1RXF10SID | 0468 |        |           |        | SID<   | :10:3>   |          |          |          | SID<2:0> — EXIDE — EID<17:   |          |       |        |        | 17:16> | xxxx  |        |               |

| C1RXF10EID | 046A |        |           |        | EID<   | :15:8>   |          |          |          | EID<7:0>                     |          |       |        |        |        | xxxx  |        |               |

| C1RXF11SID | 046C |        |           |        | SID<   | :10:3>   |          |          |          |                              | SID<2:0> |       | —      | EXIDE  | —      | EID<' | 17:16> | xxxx          |

| C1RXF11EID | 046E |        |           |        | EID<   | :15:8>   |          |          |          |                              |          |       | EID<   | 7:0>   |        |       |        | xxxx          |

| C1RXF12SID | 0470 |        |           |        | SID<   | :10:3>   |          |          |          |                              | SID<2:0> |       | —      | EXIDE  | —      | EID<  | 17:16> | xxxx          |

| C1RXF12EID | 0472 |        |           |        | EID<   | :15:8>   |          |          |          |                              |          |       | EID<   | 7:0>   |        |       |        | xxxx          |

| C1RXF13SID | 0474 |        |           |        | SID<   | :10:3>   |          |          |          | SID<2:0> — EXIDE — EI        |          |       | EID<   | 17:16> | xxxx   |       |        |               |

| C1RXF13EID | 0476 |        | EID<15:8> |        |        | EID<7:0> |          |          |          |                              |          | xxxx  |        |        |        |       |        |               |

| C1RXF14SID | 0478 |        |           |        | SID<   | :10:3>   |          |          |          |                              | SID<2:0> |       | -      | EXIDE  | —      | EID<  | 17:16> | xxxx          |

| C1RXF14EID | 047A |        |           |        | EID<   | :15:8>   |          |          |          |                              |          |       | EID<   | 7:0>   |        |       |        | xxxx          |

| C1RXF15SID | 047C |        |           |        | SID<   | :10:3>   |          |          |          |                              | SID<2:0> |       | —      | EXIDE  | —      | EID<' | 17:16> | xxxx          |

| C1RXF15EID | 047E |        |           |        | EID<   | :15:8>   |          |          |          |                              |          |       | EID<   | 7:0>   |        |       |        | xxxx          |

#### ONILY (CONTINUED) DICOALLINNY ODEACA/E40A/C40A DEV/ICEO

Legend:

© 2009-2012 Microchip Technology Inc.

x = unknown value on Reset, — = unimplemented, read as '0'. Reset values are shown in hexadecimal for PinHigh devices.

| R/W-      | 0 R/W-0                                             | U-0                                                     | U-0                       | U-0                                                 | U-0                | U-0              | R/W-0                |

|-----------|-----------------------------------------------------|---------------------------------------------------------|---------------------------|-----------------------------------------------------|--------------------|------------------|----------------------|

| TRAP      | R IOPUWR                                            | —                                                       | —                         | —                                                   | —                  | —                | VREGS <sup>(3)</sup> |

| bit 15    | ·                                                   |                                                         |                           |                                                     |                    |                  | bit                  |

| R/W-      | 0 R/W-0                                             | R/W-0                                                   | R/W-0                     | R/W-0                                               | R/W-0              | R/W-1            | R/W-1                |

| EXTR      |                                                     | SWDTEN <sup>(2)</sup>                                   | WDTO                      | SLEEP                                               | IDLE               | BOR              | POR                  |

| bit 7     |                                                     |                                                         |                           |                                                     |                    |                  | bit                  |

| Legend:   |                                                     |                                                         |                           |                                                     |                    |                  |                      |

| R = Read  | able bit                                            | W = Writable                                            | bit                       | U = Unimpler                                        | nented bit, read   | as '0'           |                      |

| -n = Valu | e at POR                                            | '1' = Bit is set                                        |                           | '0' = Bit is cle                                    | ared               | x = Bit is unk   | nown                 |

| bit 15    | 1 = A Trap Co                                       | Reset Flag bit<br>onflict Reset ha<br>onflict Reset ha  | s occurred                | d                                                   |                    |                  |                      |

| bit 14    | 1 = An illega<br>Address                            | l opcode deter<br>Pointer caused                        | ction, an ille<br>a Reset | W Access Rese<br>gal address mo<br>Reset has not oo | ode or uninitiali  | zed W regist     | er used as a         |

| bit 13-9  | Unimplemen                                          | ted: Read as 'o                                         | )'                        |                                                     |                    |                  |                      |

| bit 8     | 1 = Voltage R                                       | age Regulator S<br>egulator is acti<br>egulator goes i  | ve during Sle             |                                                     | еер                |                  |                      |

| bit 7     | 1 = A Master                                        | al Reset (MCL<br>Clear (pin) Res<br>Clear (pin) Res     | et has occur              |                                                     |                    |                  |                      |

| bit 6     | 1 <b>= A</b> reset                                  | re Reset (Instru<br>instruction has<br>instruction has  | been execut               | ed                                                  |                    |                  |                      |

| bit 5     | <b>SWDTEN:</b> So<br>1 = WDT is en<br>0 = WDT is di |                                                         | Disable of W              | DT bit <sup>(2)</sup>                               |                    |                  |                      |

| bit 4     | 1 = WDT time                                        | hdog Timer Tim<br>e-out has occur<br>e-out has not oc   | red                       | it                                                  |                    |                  |                      |

| bit 3     | SLEEP: Wake<br>1 = Device ha                        | e-up from Sleep<br>as been in Slee<br>as not been in S  | o Flag bit<br>p mode      |                                                     |                    |                  |                      |

| bit 2     | IDLE: Wake-u<br>1 = Device wa                       | up from Idle Fla<br>as in Idle mode<br>as not in Idle m | g bit                     |                                                     |                    |                  |                      |

| bit 1     | 1 = A Brown-                                        | out Reset Flag<br>out Reset has c<br>out Reset has r    | occurred                  |                                                     |                    |                  |                      |

| bit 0     | <b>POR:</b> Power-<br>1 = A Power-                  | on Reset Flag I<br>on Reset has o<br>on Reset has n     | bit<br>ccurred            |                                                     |                    |                  |                      |

| Note 1:   | All of the Reset sta<br>cause a device Re           | -                                                       | set or cleare             | ed in software. S                                   | Setting one of the | ese bits in soff | tware does no        |

| 2:        | If the FWDTEN Co<br>SWDTEN bit settin               | ig.                                                     |                           | -                                                   | -                  | -                |                      |

| 3:        | For PIC24HJ256G                                     | PX06A/X08A/X                                            | (10A devices              | , this bit is unim                                  | plemented and      | reads back p     | rogrammed            |

**3:** For PIC24HJ256GPX06A/X08A/X10A devices, this bit is unimplemented and reads back programmed value.

| U-0            | R/W-1                                                                                                                                   | R/W-0                                                                                     | R/W-0           | U-0              | R/W-1           | R/W-0           | R/W-0 |  |  |  |  |  |

|----------------|-----------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------|-----------------|------------------|-----------------|-----------------|-------|--|--|--|--|--|

| —              |                                                                                                                                         | T6IP<2:0>                                                                                 |                 | —                |                 | DMA4IP<2:0>     |       |  |  |  |  |  |

| bit 15         |                                                                                                                                         |                                                                                           |                 |                  |                 |                 | bit   |  |  |  |  |  |

|                |                                                                                                                                         |                                                                                           |                 |                  |                 |                 |       |  |  |  |  |  |

| U-0            | U-0                                                                                                                                     | U-0                                                                                       | U-0             | U-0              | R/W-1           | R/W-0           | R/W-0 |  |  |  |  |  |

| _              | —                                                                                                                                       | —                                                                                         |                 |                  |                 | OC8IP<2:0>      |       |  |  |  |  |  |

| bit 7          |                                                                                                                                         |                                                                                           |                 |                  |                 |                 | bit   |  |  |  |  |  |

| Legend:        |                                                                                                                                         |                                                                                           |                 |                  |                 |                 |       |  |  |  |  |  |

| R = Readab     | ole bit                                                                                                                                 | W = Writable                                                                              | bit             | U = Unimple      | mented bit, rea | d as '0'        |       |  |  |  |  |  |

| -n = Value a   | at POR                                                                                                                                  | '1' = Bit is set                                                                          |                 | '0' = Bit is cle | eared           | x = Bit is unkn | iown  |  |  |  |  |  |

| bit 1 <i>5</i> | l inima la vere                                                                                                                         | nted. Deed at f                                                                           | <u>`</u>        |                  |                 |                 |       |  |  |  |  |  |

| bit 15         | -                                                                                                                                       | nted: Read as '                                                                           |                 |                  |                 |                 |       |  |  |  |  |  |

| bit 14-12      |                                                                                                                                         | Timer6 Interrupt                                                                          | •               |                  |                 |                 |       |  |  |  |  |  |

|                | 111 = Intern                                                                                                                            | <ul> <li>111 = Interrupt is priority 7 (highest priority interrupt)</li> <li>•</li> </ul> |                 |                  |                 |                 |       |  |  |  |  |  |

|                | •                                                                                                                                       | •                                                                                         |                 |                  |                 |                 |       |  |  |  |  |  |

|                | •                                                                                                                                       |                                                                                           |                 |                  |                 |                 |       |  |  |  |  |  |

|                |                                                                                                                                         | upt is priority 1                                                                         | ablad           |                  |                 |                 |       |  |  |  |  |  |

| L:1 11         |                                                                                                                                         | upt source is dis                                                                         |                 |                  |                 |                 |       |  |  |  |  |  |

| bit 11         | -                                                                                                                                       | nted: Read as '                                                                           |                 |                  |                 |                 |       |  |  |  |  |  |

| bit 10-8       | <b>DMA4IP&lt;2:0&gt;:</b> DMA Channel 4 Data Transfer Complete Interrupt Priority bits                                                  |                                                                                           |                 |                  |                 |                 |       |  |  |  |  |  |

|                | <ul> <li>111 = Interrupt is priority 7 (highest priority interrupt)</li> <li>•</li> </ul>                                               |                                                                                           |                 |                  |                 |                 |       |  |  |  |  |  |

|                | •                                                                                                                                       | •                                                                                         |                 |                  |                 |                 |       |  |  |  |  |  |

|                | •                                                                                                                                       | •                                                                                         |                 |                  |                 |                 |       |  |  |  |  |  |

|                |                                                                                                                                         | 001 = Interrupt is priority 1<br>000 = Interrupt source is disabled                       |                 |                  |                 |                 |       |  |  |  |  |  |

|                |                                                                                                                                         | •                                                                                         |                 |                  |                 |                 |       |  |  |  |  |  |

| bit 7-3        | -                                                                                                                                       | nted: Read as '                                                                           |                 |                  |                 |                 |       |  |  |  |  |  |

| bit 2-0        | <b>OC8IP&lt;2:0&gt;:</b> Output Compare Channel 8 Interrupt Priority bits<br>111 = Interrupt is priority 7 (highest priority interrupt) |                                                                                           |                 |                  |                 |                 |       |  |  |  |  |  |

|                | 111 = Interru<br>•                                                                                                                      | upt is priority 7 (i                                                                      | nignest priorit | y interrupt)     |                 |                 |       |  |  |  |  |  |

|                | •                                                                                                                                       |                                                                                           |                 |                  |                 |                 |       |  |  |  |  |  |

|                |                                                                                                                                         |                                                                                           |                 |                  |                 |                 |       |  |  |  |  |  |

|                | •                                                                                                                                       |                                                                                           |                 |                  |                 |                 |       |  |  |  |  |  |

|                |                                                                                                                                         | upt is priority 1<br>upt source is dis                                                    |                 |                  |                 |                 |       |  |  |  |  |  |

## REGISTER 7-26: IPC11: INTERRUPT PRIORITY CONTROL REGISTER 11

## REGISTER 8-2: DMAxREQ: DMA CHANNEL x IRQ SELECT REGISTER

| R/W-0                | U-0   |

|----------------------|-----|-----|-----|-----|-----|-----|-------|

| FORCE <sup>(1)</sup> | —   | —   | —   | —   | —   | —   | —     |

| bit 15               |     |     |     |     |     |     | bit 8 |

| U-0   | R/W-0                  | R/W-0                  | R/W-0      | R/W-0      | R/W-0                  | R/W-0      | R/W-0      |

|-------|------------------------|------------------------|------------|------------|------------------------|------------|------------|

| —     | IRQSEL6 <sup>(2)</sup> | IRQSEL5 <sup>(2)</sup> | IRQSEL4(2) | IRQSEL3(2) | IRQSEL2 <sup>(2)</sup> | IRQSEL1(2) | IRQSEL0(2) |

| bit 7 |                        |                        |            |            |                        |            | bit 0      |

| Legend:           |                             |                      |                    |

|-------------------|-----------------------------|----------------------|--------------------|

| R = Readable bit  | U = Unimplemented bit, read | l as '0'             |                    |

| -n = Value at POR | '1' = Bit is set            | '0' = Bit is cleared | x = Bit is unknown |

bit 15 **FORCE:** Force DMA Transfer bit<sup>(1)</sup>

1 = Force a single DMA transfer (Manual mode)

0 = Automatic DMA transfer initiation by DMA request

bit 14-7 Unimplemented: Read as '0'

- bit 6-0 IRQSEL<6:0>: DMA Peripheral IRQ Number Select bits<sup>(2)</sup> 0000000-1111111 = DMAIRQ0-DMAIRQ127 selected to be Channel DMAREQ

- **Note 1:** The FORCE bit cannot be cleared by the user. The FORCE bit is cleared by hardware when the forced DMA transfer is complete.

2: Please see Table 8-1 for a complete listing of IRQ numbers for all interrupt sources.

## REGISTER 8-7: DMACS0: DMA CONTROLLER STATUS REGISTER 0 (CONTINUED)

| bit 3 | <b>XWCOL3:</b> Channel 3 DMA RAM Write Collision Flag bit<br>1 = Write collision detected<br>0 = No write collision detected                          |

|-------|-------------------------------------------------------------------------------------------------------------------------------------------------------|

| bit 2 | <ul> <li>XWCOL2: Channel 2 DMA RAM Write Collision Flag bit</li> <li>1 = Write collision detected</li> <li>0 = No write collision detected</li> </ul> |

| bit 1 | <b>XWCOL1:</b> Channel 1 DMA RAM Write Collision Flag bit<br>1 = Write collision detected<br>0 = No write collision detected                          |

| bit 0 | <b>XWCOL0:</b> Channel 0 DMA RAM Write Collision Flag bit<br>1 = Write collision detected<br>0 = No write collision detected                          |

| R/W-0        | R/W-0        | R/W-0                                 | R/W-0   | R/W-0             | U-0             | U-0            | U-0                  |

|--------------|--------------|---------------------------------------|---------|-------------------|-----------------|----------------|----------------------|

| T5MD         | T4MD         | T3MD                                  | T2MD    | T1MD              | _               |                | _                    |

| bit 15       |              |                                       |         |                   |                 |                | bit 8                |

|              |              |                                       |         |                   |                 |                |                      |

| R/W-0        | R/W-0        | R/W-0                                 | R/W-0   | R/W-0             | R/W-0           | R/W-0          | R/W-0                |

| I2C1MD       | U2MD         | U1MD                                  | SPI2MD  | SPI1MD            | C2MD            | C1MD           | AD1MD <sup>(1)</sup> |

| bit 7        |              | ·                                     |         | ·                 |                 |                | bit C                |

|              |              |                                       |         |                   |                 |                |                      |

| Legend:      |              |                                       |         |                   |                 |                |                      |

| R = Readab   | le bit       | W = Writable                          | bit     | U = Unimplem      | nented bit, rea | d as '0'       |                      |

| -n = Value a | t POR        | '1' = Bit is set                      |         | '0' = Bit is clea | ared            | x = Bit is unk | nown                 |

|              |              |                                       |         |                   |                 |                |                      |

| bit 15       |              | 5 Module Disal                        |         |                   |                 |                |                      |

|              |              | nodule is disable<br>nodule is enable |         |                   |                 |                |                      |

| bit 14       |              | 4 Module Disal                        |         |                   |                 |                |                      |

| Sit 11       | -            | odule is disable                      |         |                   |                 |                |                      |

|              | 0 = Timer4 m | odule is enable                       | ed      |                   |                 |                |                      |

| bit 13       | T3MD: Timer  | 3 Module Disal                        | ole bit |                   |                 |                |                      |

|              |              | odule is disable                      |         |                   |                 |                |                      |

| h# 40        |              | odule is enable                       |         |                   |                 |                |                      |

| bit 12       | -            | 2 Module Disal                        |         |                   |                 |                |                      |

|              | -            | odule is enable                       |         |                   |                 |                |                      |

| bit 11       | T1MD: Timer  | 1 Module Disal                        | ole bit |                   |                 |                |                      |

|              | 1 = Timer1 m | nodule is disable                     | ed      |                   |                 |                |                      |

|              |              | odule is enable                       |         |                   |                 |                |                      |

| bit 10-8     | -            | nted: Read as '                       |         |                   |                 |                |                      |

| bit 7        | _            | 1 Module Disat                        | ole bit |                   |                 |                |                      |

|              | -            | lule is disabled<br>lule is enabled   |         |                   |                 |                |                      |

| bit 6        |              | T2 Module Disa                        | hle hit |                   |                 |                |                      |

| bit 0        |              | nodule is disabl                      |         |                   |                 |                |                      |

|              | 0 = UART2 m  | nodule is enable                      | ed      |                   |                 |                |                      |

| bit 5        | U1MD: UAR    | T1 Module Disa                        | ble bit |                   |                 |                |                      |

|              | -            | nodule is disabl                      |         |                   |                 |                |                      |

| L:1 4        |              | nodule is enable                      |         |                   |                 |                |                      |

| bit 4        |              | l2 Module Disa<br>dule is disabled    |         |                   |                 |                |                      |

|              |              | dule is disabled                      |         |                   |                 |                |                      |

| bit 3        | SPI1MD: SPI  | I1 Module Disa                        | ble bit |                   |                 |                |                      |

|              | 1 = SPI1 mod | dule is disabled                      |         |                   |                 |                |                      |

|              | 0 = SPI1 mod | dule is enabled                       |         |                   |                 |                |                      |

| bit 2        |              | N2 Module Disa                        |         |                   |                 |                |                      |

|              | -            | nodule is disabl                      |         |                   |                 |                |                      |

|              | v = ECAN2 n  | nodule is enabl                       | eu      |                   |                 |                |                      |

## REGISTER 10-1: PMD1: PERIPHERAL MODULE DISABLE CONTROL REGISTER 1

**Note 1:** PCFGx bits have no effect if ADC module is disabled by setting this bit. In this case all port pins multiplexed with ANx will be in Digital mode.

## 14.1 Input Capture Registers

## **REGISTER 14-1: ICxCON: INPUT CAPTURE x CONTROL REGISTER**

| U-0                  | U-0                                                                                                                   | R/W-0                              | U-0              | U-0               | U-0             | U-0              | U-0   |  |  |  |

|----------------------|-----------------------------------------------------------------------------------------------------------------------|------------------------------------|------------------|-------------------|-----------------|------------------|-------|--|--|--|

| _                    | _                                                                                                                     | ICSIDL                             |                  | —                 | —               |                  | —     |  |  |  |

| bit 15               |                                                                                                                       |                                    |                  |                   |                 |                  | bit 8 |  |  |  |

|                      |                                                                                                                       |                                    |                  |                   |                 |                  |       |  |  |  |

| R/W-0                | R/W-0                                                                                                                 | R/W-0                              | R-0, HC          | R-0, HC           | R/W-0           | R/W-0            | R/W-0 |  |  |  |

| ICTMR <sup>(1)</sup> | ICI<                                                                                                                  | <1:0>                              | ICOV             | ICBNE             |                 | ICM<2:0>         |       |  |  |  |

| bit 7                |                                                                                                                       |                                    |                  |                   |                 |                  | bit   |  |  |  |

| Legend:              |                                                                                                                       |                                    |                  |                   |                 |                  |       |  |  |  |

| R = Readable         | bit                                                                                                                   | W = Writable                       | bit              | U = Unimpler      | nented bit, rea | d as '0'         |       |  |  |  |

| -n = Value at F      | POR                                                                                                                   | '1' = Bit is set                   |                  | '0' = Bit is cle  | ared            | x = Bit is unkn  | own   |  |  |  |

|                      |                                                                                                                       |                                    |                  |                   |                 |                  |       |  |  |  |

| bit 15-14            | Unimplemer                                                                                                            | nted: Read as '                    | 0'               |                   |                 |                  |       |  |  |  |

| bit 13               | ICSIDL: Inpu                                                                                                          | t Capture Modu                     | ule Stop in Idle | e Control bit     |                 |                  |       |  |  |  |

|                      |                                                                                                                       | ture module wi                     |                  |                   |                 |                  |       |  |  |  |

|                      |                                                                                                                       | ture module wi                     |                  | operate in CPU    | Idle mode       |                  |       |  |  |  |

| bit 12-8             | -                                                                                                                     | ted: Read as '                     |                  |                   |                 |                  |       |  |  |  |

| bit 7                |                                                                                                                       | t Capture Time                     |                  |                   |                 |                  |       |  |  |  |

|                      |                                                                                                                       | ntents are capt<br>ntents are capt |                  |                   |                 |                  |       |  |  |  |

| bit 6-5              | ICI<1:0>: Se                                                                                                          | lect Number of                     | Captures per     | Interrupt bits    |                 |                  |       |  |  |  |

|                      | 11 = Interrupt on every fourth capture event                                                                          |                                    |                  |                   |                 |                  |       |  |  |  |

|                      | <ul> <li>10 = Interrupt on every third capture event</li> <li>01 = Interrupt on every second capture event</li> </ul> |                                    |                  |                   |                 |                  |       |  |  |  |

|                      |                                                                                                                       | t on every seco<br>t on every capt |                  | rent              |                 |                  |       |  |  |  |

| bit 4                | -                                                                                                                     | Capture Overflo                    |                  | ı bit (read-onlv) | 1               |                  |       |  |  |  |

|                      | -                                                                                                                     | ture overflow o                    | -                | , (               |                 |                  |       |  |  |  |

|                      | 0 = No input capture overflow occurred                                                                                |                                    |                  |                   |                 |                  |       |  |  |  |

| bit 3                | ICBNE: Input                                                                                                          | t Capture Buffe                    | r Empty Statu    | s bit (read-only  | )               |                  |       |  |  |  |

|                      | 1 = Input capture buffer is not empty, at least one more capture value can be read                                    |                                    |                  |                   |                 |                  |       |  |  |  |

|                      |                                                                                                                       | ture buffer is e                   |                  |                   |                 |                  |       |  |  |  |

| bit 2-0              |                                                                                                                       | put Capture Mo                     |                  |                   |                 |                  |       |  |  |  |

|                      |                                                                                                                       |                                    |                  |                   |                 | eep or Idle mode | •     |  |  |  |

|                      | (Rising edge detect only, all other control bits are not applicable.)<br>110 = Unused (module disabled)               |                                    |                  |                   |                 |                  |       |  |  |  |

|                      | 101 = Capture mode, every 16th rising edge                                                                            |                                    |                  |                   |                 |                  |       |  |  |  |

|                      |                                                                                                                       | re mode, every                     |                  | e                 |                 |                  |       |  |  |  |

|                      |                                                                                                                       | re mode, every<br>re mode, every   |                  |                   |                 |                  |       |  |  |  |

|                      |                                                                                                                       | re mode, every                     |                  | and falling)      |                 |                  |       |  |  |  |

|                      |                                                                                                                       | :0> bits do not                    |                  | pt generation f   | or this mode.)  |                  |       |  |  |  |

|                      | 000 = Input c                                                                                                         | apture module                      | turned off       |                   |                 |                  |       |  |  |  |

| R-0 HSC         | R-0 HSC                                                                                                                                                                                                                                                                                                                                                                               | U-0                                                                                                   | U-0                         | U-0              | R/C-0 HS                                         | R-0 HSC          | R-0 HSC         |  |

|-----------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------|-----------------------------|------------------|--------------------------------------------------|------------------|-----------------|--|

| ACKSTAT         | TRSTAT                                                                                                                                                                                                                                                                                                                                                                                |                                                                                                       | —                           |                  | BCL                                              | GCSTAT           | ADD10           |  |

| bit 15          |                                                                                                                                                                                                                                                                                                                                                                                       |                                                                                                       |                             | I                |                                                  | 1                | bit 8           |  |

| R/C-0 HS        | R/C-0 HS                                                                                                                                                                                                                                                                                                                                                                              | R-0 HSC                                                                                               | R/C-0 HSC                   | R/C-0 HSC        | R-0 HSC                                          | R-0 HSC          | R-0 HSC         |  |

| IWCOL           | I2COV                                                                                                                                                                                                                                                                                                                                                                                 | 1                                                                                                     | Р                           | S                | R W                                              | RBF              | TBF             |  |

| bit 7           | 12000                                                                                                                                                                                                                                                                                                                                                                                 | D_A                                                                                                   |                             | 3                | R_VV                                             | KDF              | bit 0           |  |

|                 |                                                                                                                                                                                                                                                                                                                                                                                       |                                                                                                       |                             |                  |                                                  |                  |                 |  |

| Legend:         | egend: U = Unimplemented bit, read as '0' C = Clear only b                                                                                                                                                                                                                                                                                                                            |                                                                                                       |                             |                  |                                                  |                  |                 |  |

| R = Readable    | bit                                                                                                                                                                                                                                                                                                                                                                                   | W = Writable                                                                                          | bit                         | HS = Set in h    | ardware                                          | HSC = Hardwa     | are set/cleared |  |

| -n = Value at P | POR                                                                                                                                                                                                                                                                                                                                                                                   | '1' = Bit is set                                                                                      |                             | '0' = Bit is cle | ared                                             | x = Bit is unkn  | iown            |  |

| bit 15          | (when operati<br>1 = NACK rec<br>0 = ACK rece                                                                                                                                                                                                                                                                                                                                         | cknowledge St<br>ing as I <sup>2</sup> C mas<br>ceived from slav<br>ived from slav<br>or clear at end | ter, applicable<br>ve<br>e  |                  | nsmit operation                                  | )                |                 |  |

| bit 14          | 1 = Master tra<br>0 = Master tra                                                                                                                                                                                                                                                                                                                                                      | ansmit is in pro<br>ansmit is not in                                                                  | gress (8 bits -<br>progress | + ACK)           |                                                  | to master trans  |                 |  |

| bit 13-11       | Unimplemen                                                                                                                                                                                                                                                                                                                                                                            | ted: Read as '                                                                                        | 0'                          |                  |                                                  |                  |                 |  |

| bit 10          | BCL: Master                                                                                                                                                                                                                                                                                                                                                                           | Bus Collision [                                                                                       | Detect bit                  |                  |                                                  |                  |                 |  |

|                 | 0 = No collisio                                                                                                                                                                                                                                                                                                                                                                       | lision has beer<br>on<br>at detection o                                                               |                             | -                | peration                                         |                  |                 |  |

| bit 9           | GCSTAT: Ger                                                                                                                                                                                                                                                                                                                                                                           | neral Call Statu                                                                                      | ıs bit                      |                  |                                                  |                  |                 |  |

|                 | 0 = General c                                                                                                                                                                                                                                                                                                                                                                         | all address wa<br>all address wa<br>when address                                                      | is not received             |                  | ess. Hardware o                                  | lear at Stop det | ection.         |  |

| bit 8           | ADD10: 10-B                                                                                                                                                                                                                                                                                                                                                                           | it Address Stat                                                                                       | us bit                      |                  |                                                  |                  |                 |  |

|                 | 0 = 10-bit add                                                                                                                                                                                                                                                                                                                                                                        | lress was mate<br>lress was not r<br>at match of 2r                                                   | natched                     | ched 10-bit ad   | dress. Hardwa                                    | re clear at Stop | detection.      |  |

| bit 7           | IWCOL: Write                                                                                                                                                                                                                                                                                                                                                                          | e Collision Dete                                                                                      | ect bit                     |                  |                                                  |                  |                 |  |

|                 | 0 = No collisio                                                                                                                                                                                                                                                                                                                                                                       | on                                                                                                    | C                           |                  | ause the I <sup>2</sup> C mo<br>ousy (cleared by |                  |                 |  |

| bit 6           |                                                                                                                                                                                                                                                                                                                                                                                       | ive Overflow F                                                                                        |                             |                  | 5 ( )                                            | ,                |                 |  |

|                 | 1 = A byte wa<br>0 = No overflo                                                                                                                                                                                                                                                                                                                                                       | as received wh                                                                                        | ile the I2CxRC              | -                | still holding the                                | -                |                 |  |

| L:1 F           |                                                                                                                                                                                                                                                                                                                                                                                       | -                                                                                                     |                             |                  | CV (cleared by s                                 | sottware).       |                 |  |

| bit 5           | <ul> <li>D_A: Data/Address bit (when operating as I<sup>2</sup>C slave)</li> <li>1 = Indicates that the last byte received was data</li> <li>0 = Indicates that the last byte received was device address</li> <li>Hardware clear at device address match. Hardware set by reception of slave byte</li> </ul>                                                                         |                                                                                                       |                             |                  |                                                  |                  |                 |  |

| bit 4           | <ul> <li>0 = Indicates that the last byte received was device address</li> <li>Hardware clear at device address match. Hardware set by reception of slave byte.</li> <li>P: Stop bit</li> <li>1 = Indicates that a Stop bit has been detected last</li> <li>0 = Stop bit was not detected last</li> <li>Hardware set or clear when Start, Repeated Start or Stop detected.</li> </ul> |                                                                                                       |                             |                  |                                                  |                  |                 |  |

## REGISTER 17-2: I2CxSTAT: I2Cx STATUS REGISTER

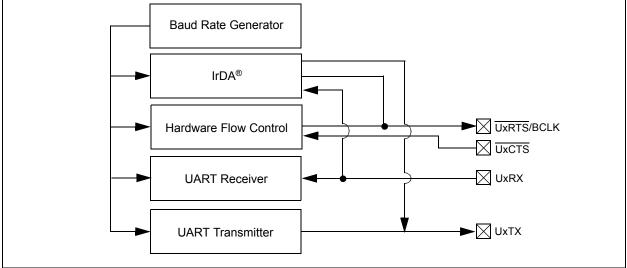

## 18.0 UNIVERSAL ASYNCHRONOUS RECEIVER TRANSMITTER (UART)

- Note 1: This data sheet summarizes the features of the PIC24HJXXXGPX06A/X08A/X10A family of devices. However, it is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to Section 17. "UART" (DS70188) of the "dsPIC33F/PIC24H Family Reference Manual", which is available from the Microchip web site (www.microchip.com).

- 2: Some registers and associated bits described in this section may not be available on all devices. Refer to Section 4.0 "Memory Organization" in this data sheet for device-specific register and bit information.