Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFI

| Product Status             | Active                                                                         |

|----------------------------|--------------------------------------------------------------------------------|

| Core Processor             | PIC                                                                            |

| Core Size                  | 16-Bit                                                                         |

| Speed                      | 40 MIPs                                                                        |

| Connectivity               | CANbus, I <sup>2</sup> C, IrDA, LINbus, SPI, UART/USART                        |

| Peripherals                | Brown-out Detect/Reset, DMA, POR, PWM, WDT                                     |

| Number of I/O              | 85                                                                             |

| Program Memory Size        | 64KB (22K x 24)                                                                |

| Program Memory Type        | FLASH                                                                          |

| EEPROM Size                | -                                                                              |

| RAM Size                   | 8K x 8                                                                         |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 3.6V                                                                      |

| Data Converters            | A/D 32x10b/12b                                                                 |

| Oscillator Type            | Internal                                                                       |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                              |

| Mounting Type              | Surface Mount                                                                  |

| Package / Case             | 100-TQFP                                                                       |

| Supplier Device Package    | 100-TQFP (12x12)                                                               |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic24hj64gp510a-i-pt |

|                            |                                                                                |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

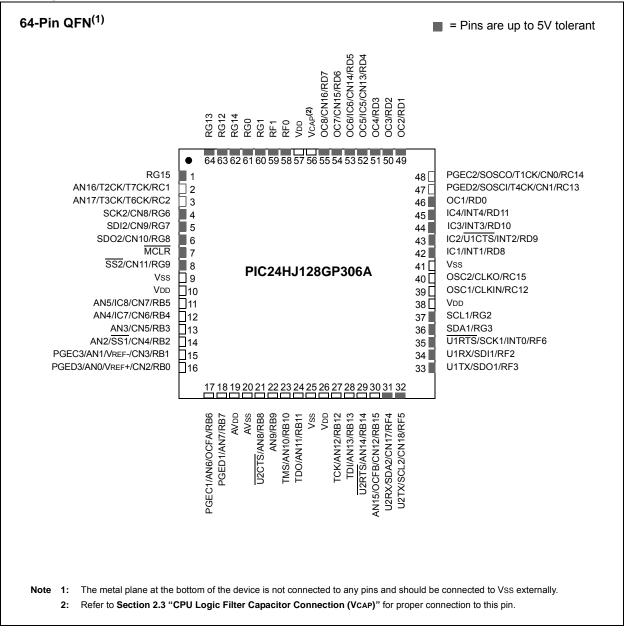

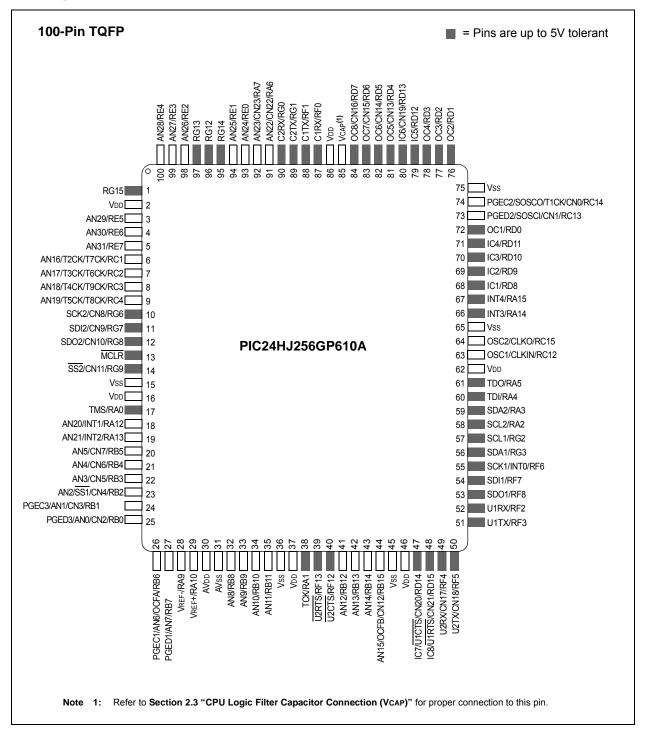

### Pin Diagrams (Continued)

#### Pin Diagrams (Continued)

© 2009-2012 Microchip Technology Inc.

# 2.0 GUIDELINES FOR GETTING STARTED WITH 16-BIT MICROCONTROLLERS

- Note 1: This data sheet summarizes the features of the PIC24HJXXXGPX06A/X08A/X10A family of devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to the "dsPIC33F/PIC24H Family Reference Manual". Please see the Microchip web site (www.microchip.com) for the latest dsPIC33F/PIC24H Family Reference Manual sections.

- 2: Some registers and associated bits described in this section may not be available on all devices. Refer to Section 4.0 "Memory Organization" in this data sheet for device-specific register and bit information.

### 2.1 Basic Connection Requirements

Getting started with the PIC24HJXXXGPX06A/X08A/X10A family of 16-bit Microcontrollers (MCUs) requires attention to a minimal set of device pin connections before proceeding with development. The following is a list of pin names, which must always be connected:

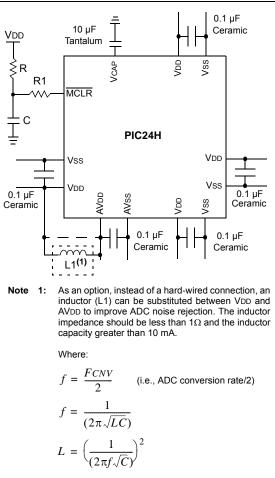

- All VDD and Vss pins (see Section 2.2 "Decoupling Capacitors")

- All AVDD and AVSS pins (regardless if ADC module is not used)

- (see Section 2.2 "Decoupling Capacitors") VCAP

- (see Section 2.3 "CPU Logic Filter Capacitor Connection (VCAP)")

- MCLR pin (see Section 2.4 "Master Clear (MCLR) Pin")

- PGECx/PGEDx pins used for In-Circuit Serial Programming<sup>™</sup> (ICSP<sup>™</sup>) and debugging purposes (see **Section 2.5 "ICSP Pins**")

- OSC1 and OSC2 pins when external oscillator source is used

(see Section 2.6 "External Oscillator Pins")

Additionally, the following pins may be required:

• VREF+/VREF- pins used when external voltage reference for ADC module is implemented

| Note: | The AVDD  |         | and AVss |        | pins | mu  | st be |

|-------|-----------|---------|----------|--------|------|-----|-------|

|       | connected |         | indep    | endent | of   | the | ADC   |

|       | volta     | ge refe |          |        |      |     |       |

# 2.2 Decoupling Capacitors

The use of decoupling capacitors on every pair of power supply pins, such as VDD, VSS, AVDD and AVSS is required.

Consider the following criteria when using decoupling capacitors:

- Value and type of capacitor: Recommendation of 0.1  $\mu$ F (100 nF), 10-20V. This capacitor should be a low-ESR and have resonance frequency in the range of 20 MHz and higher. It is recommended that ceramic capacitors be used.

- Placement on the printed circuit board: The decoupling capacitors should be placed as close to the pins as possible. It is recommended to place the capacitors on the same side of the board as the device. If space is constricted, the capacitor can be placed on another layer on the PCB using a via; however, ensure that the trace length from the pin to the capacitor is within one-quarter inch (6 mm) in length.

- Handling high frequency noise: If the board is experiencing high frequency noise, upward of tens of MHz, add a second ceramic-type capacitor in parallel to the above described decoupling capacitor. The value of the second capacitor can be in the range of 0.01  $\mu$ F to 0.001  $\mu$ F. Place this second capacitor next to the primary decoupling capacitor. In high-speed circuit designs, consider implementing a decade pair of capacitances as close to the power and ground pins as possible. For example, 0.1  $\mu$ F in parallel with 0.001  $\mu$ F.

- **Maximizing performance:** On the board layout from the power supply circuit, run the power and return traces to the decoupling capacitors first, and then to the device pins. This ensures that the decoupling capacitors are first in the power chain. Equally important is to keep the trace length between the capacitor and the power pins to a minimum thereby reducing PCB track inductance.

### 2.2.1 TANK CAPACITORS

On boards with power traces running longer than six inches in length, it is suggested to use a tank capacitor for integrated circuits including MCUs to supply a local power source. The value of the tank capacitor should be determined based on the trace resistance that connects the power supply source to the device, and the maximum current drawn by the device in the application. In other words, select the tank capacitor so that it meets the acceptable voltage sag at the device. Typical values range from 4.7  $\mu$ F to 47  $\mu$ F.

### 2.3 CPU Logic Filter Capacitor Connection (VCAP)

A low-ESR (< 5 Ohms) capacitor is required on the VCAP pin, which is used to stabilize the voltage regulator output voltage. The VCAP pin must not be connected to VDD, and must have a capacitor between 4.7  $\mu$ F and 10  $\mu$ F, 16V connected to ground. The type can be ceramic or tantalum. Refer to **Section 24.0** "**Electrical Characteristics**" for additional information.

The placement of this capacitor should be close to the VCAP. It is recommended that the trace length not exceed one-quarter inch (6 mm). Refer to **Section 21.2 "On-Chip Voltage Regulator"** for details.

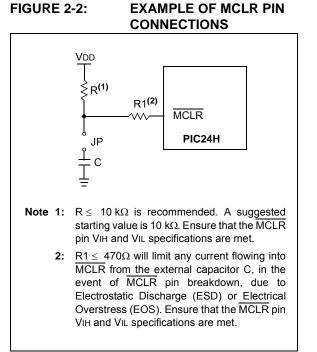

# 2.4 Master Clear (MCLR) Pin

The  $\overline{\text{MCLR}}$  pin provides for two specific device functions:

- Device Reset

- · Device programming and debugging

During device programming and debugging, the resistance and capacitance that can be added to the pin must be considered. Device programmers and debuggers drive the  $\overline{MCLR}$  pin. Consequently, specific voltage levels (VIH and VIL) and fast signal transitions must not be adversely affected. Therefore, specific values of R and C will need to be adjusted based on the application and PCB requirements.

For example, as shown in Figure 2-2, it is recommended that the capacitor C, be isolated from the MCLR pin during programming and debugging operations.

Place the components shown in Figure 2-2 within one-quarter inch (6 mm) from the MCLR pin.

| TABLE       | 4-6:        | TIME                                                 | R REG           | ISTER N | IAP    |        |        |              |              |                |                      |       |        |       |       |       |       |               |

|-------------|-------------|------------------------------------------------------|-----------------|---------|--------|--------|--------|--------------|--------------|----------------|----------------------|-------|--------|-------|-------|-------|-------|---------------|

| SFR<br>Name | SFR<br>Addr | Bit 15                                               | Bit 14          | Bit 13  | Bit 12 | Bit 11 | Bit 10 | Bit 9        | Bit 8        | Bit 7          | Bit 6                | Bit 5 | Bit 4  | Bit 3 | Bit 2 | Bit 1 | Bit 0 | All<br>Resets |

| TMR1        | 0100        |                                                      | Timer1 Register |         |        |        |        |              |              |                |                      |       | 0000   |       |       |       |       |               |

| PR1         | 0102        |                                                      |                 |         |        |        |        |              | Period F     | Register 1     |                      |       |        |       |       |       |       | FFFF          |

| T1CON       | 0104        | TON                                                  |                 | TSIDL   |        | _      | _      | _            | _            | _              | TGATE                | TCKP  | S<1:0> | _     | TSYNC | TCS   | _     | 0000          |

| TMR2        | 0106        |                                                      | Timer2 Register |         |        |        |        |              |              |                |                      |       |        | 0000  |       |       |       |               |

| TMR3HLD     | 0108        |                                                      |                 |         |        |        | Tim    | ner3 Holding | Register (fo | r 32-bit time  | operations c         | only) |        |       |       |       |       | xxxx          |

| TMR3        | 010A        |                                                      |                 |         |        |        |        |              | Timer3       | Register       |                      |       |        |       |       |       |       | 0000          |

| PR2         | 010C        |                                                      |                 |         |        |        |        |              | Period F     | Register 2     |                      |       |        |       |       |       |       | FFFF          |

| PR3         | 010E        |                                                      |                 |         |        |        |        |              | Period F     | Register 3     |                      |       |        |       |       |       |       | FFFF          |

| T2CON       | 0110        | TON                                                  |                 | TSIDL   | _      | _      | _      | _            | _            | _              | TGATE                | TCKP  | S<1:0> | T32   | —     | TCS   | _     | 0000          |

| T3CON       | 0112        | TON                                                  |                 | TSIDL   | _      | _      | _      | _            | _            | _              | TGATE                | TCKP  | S<1:0> | _     | _     | TCS   | _     | 0000          |

| TMR4        | 0114        |                                                      |                 |         |        |        |        |              | Timer4       | Register       |                      |       |        |       |       |       |       | 0000          |

| TMR5HLD     | 0116        | Timer5 Holding Register (for 32-bit operations only) |                 |         |        |        |        |              |              |                | xxxx                 |       |        |       |       |       |       |               |

| TMR5        | 0118        |                                                      | Timer5 Register |         |        |        |        |              |              |                |                      | 0000  |        |       |       |       |       |               |

| PR4         | 011A        |                                                      |                 |         |        |        |        |              | Period F     | Register 4     |                      |       |        |       |       |       |       | FFFF          |

| PR5         | 011C        |                                                      |                 |         |        |        |        |              | Period F     | Register 5     |                      |       |        |       |       |       |       | FFFF          |

| T4CON       | 011E        | TON                                                  | _               | TSIDL   | _      | _      | _      | _            | _            | _              | TGATE                | TCKP  | S<1:0> | T32   | _     | TCS   | _     | 0000          |

| T5CON       | 0120        | TON                                                  | _               | TSIDL   | _      | _      | _      | _            | _            | _              | TGATE                | TCKP  | S<1:0> | _     | _     | TCS   | —     | 0000          |

| TMR6        | 0122        |                                                      |                 |         |        |        |        |              | Timer6       | Register       |                      |       |        |       |       |       |       | 0000          |

| TMR7HLD     | 0124        |                                                      |                 |         |        |        | -      | Timer7 Hold  | ing Register | (for 32-bit op | perations only       | /)    |        |       |       |       |       | xxxx          |

| TMR7        | 0126        |                                                      |                 |         |        |        |        |              | Timer7       | Register       |                      |       |        |       |       |       |       | 0000          |

| PR6         | 0128        |                                                      |                 |         |        |        |        |              | Period F     | Register 6     |                      |       |        |       |       |       |       | FFFF          |

| PR7         | 012A        |                                                      |                 |         |        |        |        |              | Period F     | Register 7     |                      |       |        |       |       |       |       | FFFF          |

| T6CON       | 012C        | TON                                                  |                 | TSIDL   | _      | _      | _      | _            | _            | _              | TGATE                | TCKP  | S<1:0> | T32   | _     | TCS   | _     | 0000          |

| T7CON       | 012E        | TON                                                  |                 | TSIDL   | _      | _      | _      | _            | _            | _              | TGATE                | TCKP  | S<1:0> | _     | _     | TCS   | _     | 0000          |

| TMR8        | 0130        |                                                      |                 |         |        |        |        |              | Timer8       | Register       |                      |       |        |       |       |       |       | 0000          |

| TMR9HLD     | 0132        |                                                      |                 |         |        |        | -      | Timer9 Hold  | ing Register | (for 32-bit op | perations only       | /)    |        |       |       |       |       | xxxx          |

| TMR9        | 0134        |                                                      |                 |         |        |        |        |              | Timer9       | Register       |                      |       |        |       |       |       |       | 0000          |

| PR8         | 0136        |                                                      |                 |         |        |        |        |              | Period F     | Register 8     |                      |       |        |       |       |       |       | FFFF          |

| PR9         | 0138        |                                                      |                 |         |        |        |        |              | Period F     | Register 9     |                      |       |        |       |       |       |       | FFFF          |

| T8CON       | 013A        | TON                                                  | _               | TSIDL   | —      | —      | —      | —            | —            | —              | TGATE                | TCKP  | S<1:0> | T32   | _     | TCS   | —     | 0000          |

| T9CON       | 013C        | TON                                                  | _               | TSIDL   | _      | _      | _      | _            | _            | _              | TGATE                | TCKP  | S<1:0> | _     | _     | TCS   | _     | 0000          |

| L           |             |                                                      | har an Daa      |         |        |        |        |              |              |                | Dire Liberte al avai |       |        |       |       |       |       |               |

#### . . TIMED DEGIGTED MAD

Legend: x = unknown value on Reset, — = unimplemented, read as '0'. Reset values are shown in hexadecimal for PinHigh devices.

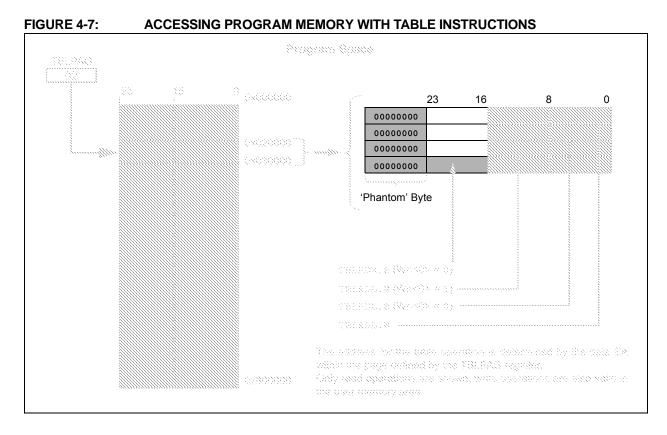

#### 4.4.2 DATA ACCESS FROM PROGRAM MEMORY USING TABLE INSTRUCTIONS

The TBLRDL and TBLWTL instructions offer a direct method of reading or writing the lower word of any address within the program space without going through data space. The TBLRDH and TBLWTH instructions are the only method to read or write the upper 8 bits of a program space word as data.

The PC is incremented by two for each successive 24-bit program word. This allows program memory addresses to directly map to data space addresses. Program memory can thus be regarded as two 16-bit, word wide address spaces, residing side by side, each with the same address range. TBLRDL and TBLWTL access the space which contains the least significant data word and TBLRDH and TBLWTH access the space which contains the upper data byte.

Two table instructions are provided to move byte or word sized (16-bit) data to and from program space. Both function as either byte or word operations.

TBLRDL (Table Read Low): In Word mode, it maps the lower word of the program space location (P<15:0>) to a data address (D<15:0>).

In Byte mode, either the upper or lower byte of the lower program word is mapped to the lower byte of a data address. The upper byte is selected when Byte Select is '1'; the lower byte is selected when it is '0'.  TBLRDH (Table Read High): In Word mode, it maps the entire upper word of a program address (P<23:16>) to a data address. Note that D<15:8>, the 'phantom byte', will always be '0'.

In Byte mode, it maps the upper or lower byte of the program word to D<7:0> of the data address, as above. Note that the data will always be '0' when the upper 'phantom' byte is selected (Byte Select = 1).

In a similar fashion, two table instructions, TBLWTH and TBLWTL, are used to write individual bytes or words to a program space address. The details of their operation are explained in **Section 5.0 "Flash Program Memory"**.

For all table operations, the area of program memory space to be accessed is determined by the Table Page register (TBLPAG). TBLPAG covers the entire program memory space of the device, including user and configuration spaces. When TBLPAG<7> = 0, the table page is located in the user memory space. When TBLPAG<7> = 1, the page is located in configuration space.

#### 4.4.3 READING DATA FROM PROGRAM MEMORY USING PROGRAM SPACE VISIBILITY

The upper 32 Kbytes of data space may optionally be mapped into any 16K word page of the program space. This option provides transparent access of stored constant data from the data space without the need to use special instructions (i.e., TBLRDL/H).

Program space access through the data space occurs if the Most Significant bit of the data space EA is '1' and program space visibility is enabled by setting the PSV bit in the Core Control register (CORCON<2>). The location of the program memory space to be mapped into the data space is determined by the Program Space Visibility Page register (PSVPAG). This 8-bit register defines any one of 256 possible pages of 16K words in program space. In effect, PSVPAG functions as the upper 8 bits of the program memory address, with the 15 bits of the EA functioning as the lower bits. Note that by incrementing the PC by 2 for each program memory word, the lower 15 bits of data space addresses directly map to the lower 15 bits in the corresponding program space addresses.

Data reads to this area add an additional cycle to the instruction being executed, since two program memory fetches are required.

Although each data space address, 0x8000 and higher, maps directly into a corresponding program memory address (see Figure 4-8), only the lower 16 bits of the 24-bit program word are used to contain the data. The upper 8 bits of any program space location used as data should be programmed with '1111 1111' or '0000 0000' to force a NOP. This prevents possible issues should the area of code ever be accidentally executed.

| Note: | PSV access is temporarily disabled during |

|-------|-------------------------------------------|

|       | table reads/writes.                       |

For operations that use PSV and are executed outside a REPEAT loop, the MOV and MOV.D instructions require one instruction cycle in addition to the specified execution time. All other instructions require two instruction cycles in addition to the specified execution time.

For operations that use PSV, which are executed inside a REPEAT loop, there will be some instances that require two instruction cycles in addition to the specified execution time of the instruction:

- · Execution in the first iteration

- · Execution in the last iteration

- Execution prior to exiting the loop due to an interrupt

- Execution upon re-entering the loop after an interrupt is serviced

Any other iteration of the REPEAT loop will allow the instruction accessing data, using PSV, to execute in a single cycle.

#### When CORCON < 2 > = 1 and EA < 15 > = 1: **Program Space Data Space PSVPAG** 15 0 0x000000 0x0000 02 Data EA<14:0> 0x010000 0x018000 The data in the page designated by **PSVPAG** is mapped into the upper half of the data memory 0x8000 space... **PSV** Area ...while the lower 15 bits of the EA specify an exact address within 0xFFFF the PSV area. This corresponds exactly to the same lower 15 bits of the actual program space address. 0x800000

#### FIGURE 4-8: PROGRAM SPACE VISIBILITY OPERATION

# 5.0 FLASH PROGRAM MEMORY

- Note 1: This data sheet summarizes the features of the PIC24HJXXXGPX06A/X08A/X10A family of devices. However, it is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to Section 5. "Flash Programming" (DS70191) of the "dsPIC33F/PIC24H Family Reference Manual", which is available from the Microchip web site (www.microchip.com).

- Some registers and associated bits described in this section may not be available on all devices. Refer to Section 4.0 "Memory Organization" in this data sheet for device-specific register and bit information.

The PIC24HJXXXGPX06A/X08A/X10A devices contain internal Flash program memory for storing and executing application code. The memory is readable, writable and erasable during normal operation over the entire VDD range.

Flash memory can be programmed in two ways:

- In-Circuit Serial Programming<sup>™</sup> (ICSP<sup>™</sup>) programming capability

- 2. Run-Time Self-Programming (RTSP)

ICSP programming capability allows a PIC24HJXXXGPX06A/X08A/X10A device to be serially programmed while in the end application circuit. This is simply done with two lines for programming clock and programming data (one of the alternate programming pin pairs: PGECx/PGEDx, and three other lines for power (VDD), ground (VSS) and Master Clear (MCLR). This allows customers to manufacture boards with unprogrammed devices and then program the digital signal controller just before shipping the product. This also allows the most recent firmware or a custom firmware to be programmed.

RTSP is accomplished using TBLRD (table read) and TBLWT (table write) instructions. With RTSP, the user can write program memory data either in blocks or 'rows' of 64 instructions (192 bytes) at a time, or single instructions and erase program memory in blocks or 'pages' of 512 instructions (1536 bytes) at a time.

## 5.1 Table Instructions and Flash Programming

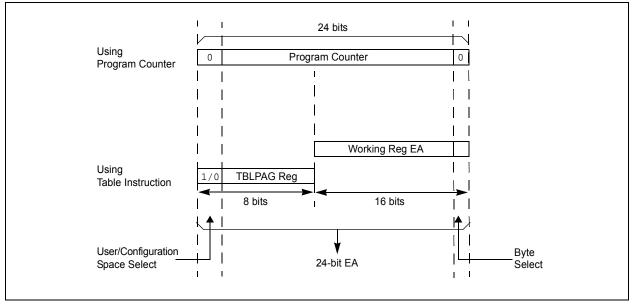

Regardless of the method used, all programming of Flash memory is done with the table read and table write instructions. These allow direct read and write access to the program memory space from the data memory while the device is in normal operating mode. The 24-bit target address in the program memory is formed using bits<7:0> of the TBLPAG register and the Effective Address (EA) from a W register specified in the table instruction, as shown in Figure 5-1.

The TBLRDL and the TBLWTL instructions are used to read or write to bits<15:0> of program memory. TBLRDL and TBLWTL can access program memory in both Word and Byte modes.

The TBLRDH and TBLWTH instructions are used to read or write to bits<23:16> of program memory. TBLRDH and TBLWTH can also access program memory in Word or Byte mode.

#### FIGURE 5-1: ADDRESSING FOR TABLE REGISTERS

| U-0          | R/W-1                                                      | R/W-0                                              | R/W-0           | U-0              | R/W-1           | R/W-0           | R/W-0 |  |  |  |  |  |  |

|--------------|------------------------------------------------------------|----------------------------------------------------|-----------------|------------------|-----------------|-----------------|-------|--|--|--|--|--|--|

| _            |                                                            | U2TXIP<2:0>                                        |                 |                  |                 | U2RXIP<2:0>     |       |  |  |  |  |  |  |

| bit 15       |                                                            |                                                    |                 |                  |                 |                 | bit   |  |  |  |  |  |  |

| U-0          | R/W-1                                                      | R/W-0                                              | R/W-0           | U-0              | R/W-1           | R/W-0           | R/W-0 |  |  |  |  |  |  |

|              |                                                            | INT2IP<2:0>                                        |                 | _                |                 | T5IP<2:0>       |       |  |  |  |  |  |  |

| bit 7        |                                                            |                                                    |                 |                  | 1               |                 | bit   |  |  |  |  |  |  |

| Legend:      |                                                            |                                                    |                 |                  |                 |                 |       |  |  |  |  |  |  |

| R = Readab   | le bit                                                     | W = Writable                                       | bit             | U = Unimplei     | mented bit, rea | id as '0'       |       |  |  |  |  |  |  |

| -n = Value a | t POR                                                      | '1' = Bit is set                                   |                 | '0' = Bit is cle | eared           | x = Bit is unkr | iown  |  |  |  |  |  |  |

| bit 15       | Unimpleme                                                  | ented: Read as '                                   | כי              |                  |                 |                 |       |  |  |  |  |  |  |

| bit 14-12    |                                                            | <b>0&gt;:</b> UART2 Trans<br>rupt is priority 7 (I |                 |                  |                 |                 |       |  |  |  |  |  |  |

|              | •                                                          |                                                    |                 |                  |                 |                 |       |  |  |  |  |  |  |

|              | •<br>001 = Interrupt is priority 1                         |                                                    |                 |                  |                 |                 |       |  |  |  |  |  |  |

|              |                                                            | upt source is dis                                  | abled           |                  |                 |                 |       |  |  |  |  |  |  |

| bit 11       | Unimpleme                                                  | ented: Read as '                                   | o'              |                  |                 |                 |       |  |  |  |  |  |  |

| bit 10-8     | U2RXIP<2:0>: UART2 Receiver Interrupt Priority bits        |                                                    |                 |                  |                 |                 |       |  |  |  |  |  |  |

|              | 111 = Interrupt is priority 7 (highest priority interrupt) |                                                    |                 |                  |                 |                 |       |  |  |  |  |  |  |

|              | •                                                          |                                                    |                 |                  |                 |                 |       |  |  |  |  |  |  |

|              | •                                                          |                                                    |                 |                  |                 |                 |       |  |  |  |  |  |  |

|              | 001 = Interrupt is priority 1                              |                                                    |                 |                  |                 |                 |       |  |  |  |  |  |  |

|              |                                                            | upt source is dis                                  |                 |                  |                 |                 |       |  |  |  |  |  |  |

| bit 7        | -                                                          | ented: Read as '                                   |                 |                  |                 |                 |       |  |  |  |  |  |  |

| bit 6-4      |                                                            | >: External Interr                                 |                 |                  |                 |                 |       |  |  |  |  |  |  |

|              | 111 = Interr                                               | rupt is priority 7 (I                              | nighest priori  | ty interrupt)    |                 |                 |       |  |  |  |  |  |  |

|              | •                                                          |                                                    |                 |                  |                 |                 |       |  |  |  |  |  |  |

|              | •                                                          |                                                    |                 |                  |                 |                 |       |  |  |  |  |  |  |

|              |                                                            | upt is priority 1                                  | ablad           |                  |                 |                 |       |  |  |  |  |  |  |

| bit 3        |                                                            | upt source is dis<br>ented: Read as 'o             |                 |                  |                 |                 |       |  |  |  |  |  |  |

| bit 2-0      | -                                                          | Timer5 Interrupt                                   |                 |                  |                 |                 |       |  |  |  |  |  |  |

| DIL 2-0      |                                                            | upt is priority 7 (I                               | -               | tv interrupt)    |                 |                 |       |  |  |  |  |  |  |

|              | •                                                          | арт ю р. ю. т.) · (.                               | ingineer priori | ()               |                 |                 |       |  |  |  |  |  |  |

|              | •                                                          |                                                    |                 |                  |                 |                 |       |  |  |  |  |  |  |

|              | •                                                          |                                                    |                 |                  |                 |                 |       |  |  |  |  |  |  |

|              | ()()   = Interr                                            | upt is priority 1                                  |                 |                  |                 |                 |       |  |  |  |  |  |  |

### 7.4 Interrupt Setup Procedures

#### 7.4.1 INITIALIZATION

To configure an interrupt source:

- 1. Set the NSTDIS bit (INTCON1<15>) if nested interrupts are not desired.

- Select the user-assigned priority level for the interrupt source by writing the control bits in the appropriate IPCx register. The priority level will depend on the specific application and type of interrupt source. If multiple priority levels are not desired, the IPCx register control bits for all enabled interrupt sources may be programmed to the same non-zero value.

| Note: | At a device Reset, the IPCx registers are |  |  |  |  |  |  |  |  |

|-------|-------------------------------------------|--|--|--|--|--|--|--|--|

|       | initialized, such that all user interrupt |  |  |  |  |  |  |  |  |

|       | sources are assigned to priority level 4. |  |  |  |  |  |  |  |  |

- 3. Clear the interrupt flag status bit associated with the peripheral in the associated IFSx register.

- 4. Enable the interrupt source by setting the interrupt enable control bit associated with the source in the appropriate IECx register.

### 7.4.2 INTERRUPT SERVICE ROUTINE

The method that is used to declare an ISR and initialize the IVT with the correct vector address will depend on the programming language (i.e., C or assembler) and the language development toolsuite that is used to develop the application. In general, the user must clear the interrupt flag in the appropriate IFSx register for the source of interrupt that the ISR handles. Otherwise, the ISR will be re-entered immediately after exiting the routine. If the ISR is coded in assembly language, it must be terminated using a RETFIE instruction to unstack the saved PC value, SRL value and old CPU priority level.

#### 7.4.3 TRAP SERVICE ROUTINE

A Trap Service Routine (TSR) is coded like an ISR, except that the appropriate trap status flag in the INTCON1 register must be cleared to avoid re-entry into the TSR.

#### 7.4.4 INTERRUPT DISABLE

All user interrupts can be disabled using the following procedure:

- 1. Push the current SR value onto the software stack using the PUSH instruction.

- 2. Force the CPU to priority level 7 by inclusive ORing the value 0x0E with SRL.

To enable user interrupts, the POP instruction may be used to restore the previous SR value.

Note that only user interrupts with a priority level of 7 or less can be disabled. Trap sources (level 8-level 15) cannot be disabled.

The DISI instruction provides a convenient way to disable interrupts of priority levels 1-6 for a fixed period of time. Level 7 interrupt sources are not disabled by the DISI instruction.

#### REGISTER 8-8: DMACS1: DMA CONTROLLER STATUS REGISTER 1

| U-0           | U-0                                                                                                      | U-0                                                                                              | U-0            | R-1               | R-1              | R-1             | R-1        |  |  |  |  |  |  |

|---------------|----------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------|----------------|-------------------|------------------|-----------------|------------|--|--|--|--|--|--|

| _             | _                                                                                                        | _                                                                                                | —              |                   | LSTC             | +<3:0>          |            |  |  |  |  |  |  |

| bit 15        |                                                                                                          |                                                                                                  |                |                   |                  |                 | bit 8      |  |  |  |  |  |  |

|               | <b>D</b> 0                                                                                               |                                                                                                  |                |                   | <b>D</b> 0       |                 | <b>D</b> 0 |  |  |  |  |  |  |

| R-0           | R-0                                                                                                      | R-0                                                                                              | R-0            | R-0               | R-0              | R-0             | R-0        |  |  |  |  |  |  |

| PPST7         | PPST6                                                                                                    | PPST5                                                                                            | PPST4          | PPST3             | PPST2            | PPST1           | PPST0      |  |  |  |  |  |  |

| bit 7         |                                                                                                          |                                                                                                  |                |                   |                  |                 | bit 0      |  |  |  |  |  |  |

| Legend:       |                                                                                                          |                                                                                                  |                |                   |                  |                 |            |  |  |  |  |  |  |

| R = Readable  | e bit                                                                                                    | W = Writable                                                                                     | bit            | U = Unimplem      | nented bit, read | l as '0'        |            |  |  |  |  |  |  |

| -n = Value at | POR                                                                                                      | '1' = Bit is set                                                                                 |                | '0' = Bit is clea |                  | x = Bit is unkr | nown       |  |  |  |  |  |  |

|               |                                                                                                          |                                                                                                  |                |                   |                  |                 |            |  |  |  |  |  |  |

| bit 15-12     | Unimplemen                                                                                               | ted: Read as '                                                                                   | 0'             |                   |                  |                 |            |  |  |  |  |  |  |

| bit 11-8      | LSTCH<3:0>                                                                                               | : Last DMA Ch                                                                                    | annel Active b | oits              |                  |                 |            |  |  |  |  |  |  |

|               |                                                                                                          |                                                                                                  | s occurred sin | ce system Res     | et               |                 |            |  |  |  |  |  |  |

|               | 1110-1000 =                                                                                              | Reserved                                                                                         |                | annol 7           |                  |                 |            |  |  |  |  |  |  |

|               |                                                                                                          |                                                                                                  |                |                   |                  |                 |            |  |  |  |  |  |  |

|               |                                                                                                          | 0110 = Last data transfer was by DMA Channel 6<br>0101 = Last data transfer was by DMA Channel 5 |                |                   |                  |                 |            |  |  |  |  |  |  |

|               |                                                                                                          | 0100 = Last data transfer was by DMA Channel 4                                                   |                |                   |                  |                 |            |  |  |  |  |  |  |

|               | 0011 = Last data transfer was by DMA Channel 3                                                           |                                                                                                  |                |                   |                  |                 |            |  |  |  |  |  |  |

|               | 0010 = Last data transfer was by DMA Channel 2<br>0001 = Last data transfer was by DMA Channel 1         |                                                                                                  |                |                   |                  |                 |            |  |  |  |  |  |  |

|               |                                                                                                          |                                                                                                  |                |                   |                  |                 |            |  |  |  |  |  |  |

| bit 7         | 0000 = Last data transfer was by DMA Channel 0<br><b>PPST7:</b> Channel 7 Ping-Pong Mode Status Flag bit |                                                                                                  |                |                   |                  |                 |            |  |  |  |  |  |  |

|               |                                                                                                          | B register selec                                                                                 |                |                   |                  |                 |            |  |  |  |  |  |  |

|               |                                                                                                          | A register selec                                                                                 |                |                   |                  |                 |            |  |  |  |  |  |  |

| bit 6         |                                                                                                          | inel 6 Ping-Por                                                                                  | -              | s Flag bit        |                  |                 |            |  |  |  |  |  |  |

|               |                                                                                                          | B register select<br>A register select                                                           |                |                   |                  |                 |            |  |  |  |  |  |  |

| bit 5         | PPST5: Chan                                                                                              | nel 5 Ping-Por                                                                                   | ng Mode Statu  | s Flag bit        |                  |                 |            |  |  |  |  |  |  |

|               | 1 = DMA5STB register selected                                                                            |                                                                                                  |                |                   |                  |                 |            |  |  |  |  |  |  |

|               |                                                                                                          | A register selec                                                                                 |                |                   |                  |                 |            |  |  |  |  |  |  |

| bit 4         |                                                                                                          | inel 4 Ping-Por                                                                                  | -              | s Flag bit        |                  |                 |            |  |  |  |  |  |  |

|               |                                                                                                          | B register select<br>A register select                                                           |                |                   |                  |                 |            |  |  |  |  |  |  |

| bit 3         | PPST3: Chan                                                                                              | nel 3 Ping-Por                                                                                   | ng Mode Statu  | s Flag bit        |                  |                 |            |  |  |  |  |  |  |

|               |                                                                                                          | B register selec<br>A register selec                                                             |                |                   |                  |                 |            |  |  |  |  |  |  |

| bit 2         | <ul> <li>DMA3STA register selected</li> <li>PPST2: Channel 2 Ping-Pong Mode Status Flag bit</li> </ul>   |                                                                                                  |                |                   |                  |                 |            |  |  |  |  |  |  |

|               | 1 = DMA2ST                                                                                               | B register selec                                                                                 | cted           |                   |                  |                 |            |  |  |  |  |  |  |

|               |                                                                                                          | A register selec                                                                                 |                | <b>—</b> , ,,,    |                  |                 |            |  |  |  |  |  |  |

| bit 1         |                                                                                                          | inel 1 Ping-Por                                                                                  | -              | s Flag bit        |                  |                 |            |  |  |  |  |  |  |

|               |                                                                                                          | B register seled<br>A register seled                                                             |                |                   |                  |                 |            |  |  |  |  |  |  |

| bit 0         | PPST0: Chan                                                                                              | nel 0 Ping-Por                                                                                   | ng Mode Statu  | s Flag bit        |                  |                 |            |  |  |  |  |  |  |

|               |                                                                                                          | B register seled                                                                                 | -              |                   |                  |                 |            |  |  |  |  |  |  |

| Bit Field | Register | RTSP<br>Effect | Description                                                                                                                                                                                                                    |  |  |  |

|-----------|----------|----------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| SSS<2:0>  | FSS      | Immediate      | Secure Segment Program Flash Code Protection Size<br>(FOR 128K and 256K DEVICES)<br>x11 = No Secure program Flash segment                                                                                                      |  |  |  |

|           |          |                | Secure space is 8K IW less BS<br>110 = Standard security; secure program Flash segment starts at End of<br>BS, ends at 0x003FFE<br>010 = High security; secure program Flash segment starts at End of BS,<br>ends at 0x003FFE  |  |  |  |

|           |          |                | Secure space is 16K IW less BS<br>101 = Standard security; secure program Flash segment starts at End of<br>BS, ends at 0x007FFE<br>001 = High security; secure program Flash segment starts at End of BS,<br>ends at 0x007FFE |  |  |  |

|           |          |                | Secure space is 32K IW less BS<br>100 = Standard security; secure program Flash segment starts at End of<br>BS, ends at 0x00FFFE<br>000 = High security; secure program Flash segment starts at End of BS,<br>ends at 0x00FFFE |  |  |  |

|           |          |                | (FOR 64K DEVICES)<br>x11 = No Secure program Flash segment                                                                                                                                                                     |  |  |  |

|           |          |                | Secure space is 4K IW less BS<br>110 = Standard security; secure program Flash segment starts at End of<br>BS, ends at 0x001FFE<br>010 = High security; secure program Flash segment starts at End of BS,<br>ends at 0x001FFE  |  |  |  |

|           |          |                | Secure space is 8K IW less BS<br>101 = Standard security; secure program Flash segment starts at End of<br>BS, ends at 0x003FFE<br>001 = High security; secure program Flash segment starts at End of BS,<br>ends at 0x003FFE  |  |  |  |

|           |          |                | Secure space is 16K IW less BS<br>100 = Standard security; secure program Flash segment starts at End of<br>BS, ends at 0x007FFE<br>000 = High security; secure program Flash segment starts at End of BS,<br>ends at 0x007FFE |  |  |  |

| RSS<1:0>  | FSS      | Immediate      | Secure Segment RAM Code Protection<br>11 = No Secure RAM defined<br>10 = Secure RAM is 256 Bytes less BS RAM<br>01 = Secure RAM is 2048 Bytes less BS RAM<br>00 = Secure RAM is 4096 Bytes less BS RAM                         |  |  |  |

| GSS<1:0>  | FGS      | Immediate      |                                                                                                                                                                                                                                |  |  |  |

| GWRP      | FGS      | Immediate      | General Segment Write-Protect bit<br>1 = User program memory is not write-protected<br>0 = User program memory is write-protected                                                                                              |  |  |  |

#### TABLE 21-2: CONFIGURATION BITS DESCRIPTION (CONTINUED)

| TABLE 21-2: | CONFIGURATION BITS DESCRIPTION (CONTINUED) |                                                                                                              |                                                                                                                                                                                                                                                                                                                                                          |  |  |  |  |  |

|-------------|--------------------------------------------|--------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|

| Bit Field   | Register                                   | RTSP<br>Effect                                                                                               | Description                                                                                                                                                                                                                                                                                                                                              |  |  |  |  |  |

| IESO        | FOSCSEL                                    | Immediate                                                                                                    | Internal External Start-up Option bit<br>1 = Start-up device with FRC, then automatically switch to the<br>user-selected oscillator source when ready<br>0 = Start-up device with user-selected oscillator source                                                                                                                                        |  |  |  |  |  |

| FNOSC<2:0>  | FOSCSEL                                    | If clock<br>switch is<br>enabled,<br>RTSP<br>effect is on<br>any device<br>Reset;<br>otherwise,<br>Immediate | Initial Oscillator Source Selection bits<br>111 = Internal Fast RC (FRC) oscillator with postscaler<br>110 = Reserved<br>101 = LPRC oscillator<br>100 = Secondary (LP) oscillator<br>011 = Primary (XT, HS, EC) oscillator with PLL<br>010 = Primary (XT, HS, EC) oscillator<br>001 = Internal Fast RC (FRC) oscillator with PLL<br>000 = FRC oscillator |  |  |  |  |  |

| FCKSM<1:0>  | FOSC                                       | Immediate                                                                                                    | Clock Switching Mode bits<br>1x = Clock switching is disabled, Fail-Safe Clock Monitor is disabled<br>01 = Clock switching is enabled, Fail-Safe Clock Monitor is disabled<br>00 = Clock switching is enabled, Fail-Safe Clock Monitor is enabled                                                                                                        |  |  |  |  |  |

| OSCIOFNC    | FOSC                                       | Immediate                                                                                                    | OSC2 Pin Function bit (except in XT and HS modes)<br>1 = OSC2 is clock output<br>0 = OSC2 is general purpose digital I/O pin                                                                                                                                                                                                                             |  |  |  |  |  |

| POSCMD<1:0> | FOSC                                       | Immediate                                                                                                    | Primary Oscillator Mode Select bits<br>11 = Primary oscillator disabled<br>10 = HS Crystal Oscillator mode<br>01 = XT Crystal Oscillator mode<br>00 = EC (External Clock) mode                                                                                                                                                                           |  |  |  |  |  |

| FWDTEN      | FWDT                                       | Immediate                                                                                                    | <ul> <li>Watchdog Timer Enable bit</li> <li>1 = Watchdog Timer always enabled (LPRC oscillator cannot be disabled.<br/>Clearing the SWDTEN bit in the RCON register will have no effect.)</li> <li>0 = Watchdog Timer enabled/disabled by user software (LPRC can be disabled by clearing the SWDTEN bit in the RCON register)</li> </ul>                |  |  |  |  |  |

| WINDIS      | FWDT                                       | Immediate                                                                                                    | Watchdog Timer Window Enable bit<br>1 = Watchdog Timer in Non-Window mode<br>0 = Watchdog Timer in Window mode                                                                                                                                                                                                                                           |  |  |  |  |  |

| PLLKEN      | FWDT                                       | Immediate                                                                                                    | PLL Lock Enable bit<br>1 = Clock switch to PLL source will wait until the PLL lock signal is valid.<br>0 = Clock switch will not wait for the PLL lock signal.                                                                                                                                                                                           |  |  |  |  |  |

| WDTPRE      | FWDT                                       | Immediate                                                                                                    | Watchdog Timer Prescaler bit<br>1 = 1:128<br>0 = 1:32                                                                                                                                                                                                                                                                                                    |  |  |  |  |  |

| WDTPOST     | FWDT                                       | Immediate                                                                                                    | Watchdog Timer Postscaler bits<br>1111 = 1:32,768<br>1110 = 1:16,384<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•                                                                                                                                                                                                                    |  |  |  |  |  |

#### TABLE 21-2: CONFIGURATION BITS DESCRIPTION (CONTINUED)

| Base<br>Instr<br># | Assembly<br>Mnemonic |         |               |                                                          | # of<br>Words | # of<br>Cycles | Status Flags<br>Affected |

|--------------------|----------------------|---------|---------------|----------------------------------------------------------|---------------|----------------|--------------------------|

| 12 B'              | BTST                 | BTST    | f,#bit4       | Bit Test f                                               | 1             | 1              | Z                        |

|                    |                      | BTST.C  | Ws,#bit4      | Bit Test Ws to C                                         | 1             | 1              | С                        |

|                    |                      | BTST.Z  | Ws,#bit4      | Bit Test Ws to Z                                         | 1             | 1              | Z                        |

|                    |                      | BTST.C  | Ws,Wb         | Bit Test Ws <wb> to C</wb>                               | 1             | 1              | С                        |

|                    |                      | BTST.Z  | Ws,Wb         | Bit Test Ws <wb> to Z</wb>                               | 1             | 1              | Z                        |

| 13                 | BTSTS                | BTSTS   | f,#bit4       | Bit Test then Set f                                      | 1             | 1              | Z                        |

|                    |                      | BTSTS.C | Ws,#bit4      | Bit Test Ws to C, then Set                               | 1             | 1              | С                        |

|                    |                      | BTSTS.Z | Ws,#bit4      | Bit Test Ws to Z, then Set                               | 1             | 1              | Z                        |

| 14                 | CALL                 | CALL    | lit23         | Call subroutine                                          | 2             | 2              | None                     |

|                    |                      | CALL    | Wn            | Call indirect subroutine                                 | 1             | 2              | None                     |

| 15                 | CLR                  | CLR     | f             | f = 0x0000                                               | 1             | 1              | None                     |

|                    |                      | CLR     | WREG          | WREG = 0x0000                                            | 1             | 1              | None                     |

|                    |                      | CLR     | Ws            | Ws = 0x0000                                              | 1             | 1              | None                     |

| 16                 | CLRWDT               | CLRWDT  |               | Clear Watchdog Timer                                     | 1             | 1              | WDTO,Sleep               |

| 17                 | COM                  | COM     | f             | f = Ī                                                    | 1             | 1              | N,Z                      |

|                    |                      | COM     | f,WREG        | WREG = Ī                                                 | 1             | 1              | N,Z                      |

|                    |                      | COM     | Ws,Wd         | $Wd = \overline{Ws}$                                     | 1             | 1              | N,Z                      |

| 18                 | CP                   | CP      | f             | Compare f with WREG                                      | 1             | 1              | C,DC,N,OV,Z              |

|                    | -                    | CP      | -<br>Wb,#lit5 | Compare Wb with lit5                                     | 1             | 1              | C,DC,N,OV,Z              |

|                    |                      | CP      | Wb,Ws         | Compare Wb with Ws (Wb – Ws)                             | 1             | 1              | C,DC,N,OV,Z              |

| 19                 | CP0                  | CPO     | f             | Compare f with 0x0000                                    | 1             | 1              | C,DC,N,OV,Z              |

|                    |                      | CP0     | Ws            | Compare Ws with 0x0000                                   | 1             | 1              | C,DC,N,OV,Z              |

| 20                 | CPB                  | CPB     | f             | Compare f with WREG, with Borrow                         | 1             | 1              | C,DC,N,OV,Z              |

|                    |                      | CPB     | Wb,#lit5      | Compare Wb with lit5, with Borrow                        | 1             | 1              | C,DC,N,OV,Z              |

|                    |                      | CPB     | Wb,Ws         | Compare Wb <u>w</u> ith Ws, with Borrow<br>(Wb – Ws – C) | 1             | 1              | C,DC,N,OV,Z              |

| 21                 | CPSEQ                | CPSEQ   | Wb, Wn        | Compare Wb with Wn, skip if =                            | 1             | 1<br>(2 or 3)  | None                     |

| 22                 | CPSGT                | CPSGT   | Wb, Wn        | Compare Wb with Wn, skip if >                            | 1             | 1<br>(2 or 3)  | None                     |

| 23                 | CPSLT                | CPSLT   | Wb, Wn        | Compare Wb with Wn, skip if <                            | 1             | 1<br>(2 or 3)  | None                     |

| 24                 | CPSNE                | CPSNE   | Wb, Wn        | Compare Wb with Wn, skip if ≠                            | 1             | 1<br>(2 or 3)  | None                     |

| 25                 | DAW                  | DAW     | Wn            | Wn = decimal adjust Wn                                   | 1             | 1              | С                        |

| 26                 | DEC                  | DEC     | f             | f = f - 1                                                | 1             | 1              | C,DC,N,OV,Z              |

|                    |                      | DEC     | f,WREG        | WREG = f – 1                                             | 1             | 1              | C,DC,N,OV,Z              |

|                    |                      | DEC     | Ws,Wd         | Wd = Ws - 1                                              | 1             | 1              | C,DC,N,OV,Z              |

| 27                 | DEC2                 | DEC2    | f             | f = f - 2                                                | 1             | 1              | C,DC,N,OV,Z              |

|                    |                      | DEC2    | f,WREG        | WREG = $f - 2$                                           | 1             | 1              | C,DC,N,OV,Z              |

|                    |                      | DEC2    | Ws,Wd         | Wd = Ws - 2                                              | 1             | 1              | C,DC,N,OV,Z              |

| 28                 | DISI                 | DISI    | #lit14        | Disable Interrupts for k instruction cycles              | 1             | 1              | None                     |

| 29                 | DIV                  | DIV.S   | Wm,Wn         | Signed 16/16-bit Integer Divide                          | 1             | 18             | N,Z,C,OV                 |

|                    |                      | DIV.SD  | Wm,Wn         | Signed 32/16-bit Integer Divide                          | 1             | 18             | N,Z,C,OV                 |

|                    |                      | DIV.U   | Wm,Wn         | Unsigned 16/16-bit Integer Divide                        | 1             | 18             | N,Z,C,OV                 |

|                    |                      | DIV.UD  | Wm,Wn         | Unsigned 32/16-bit Integer Divide                        | 1             | 18             | N,Z,C,OV                 |

| 30                 | EXCH                 | EXCH    | Wns,Wnd       | Swap Wns with Wnd                                        | 1             | 1              | None                     |

| 31                 | FBCL                 | FBCL    | Ws,Wnd        | Find Bit Change from Left (MSb) Side                     | 1             | 1              | С                        |

| 32                 | FF1L                 | FF1L    | Ws,Wnd        | Find First One from Left (MSb) Side                      | 1             | 1              | С                        |

| 33                 | FF1R                 | FF1R    | Ws,Wnd        | Find First One from Right (LSb) Side                     | 1             | 1              | С                        |

| 34                 | GOTO                 | GOTO    | Expr          | Go to address                                            | 2             | 2              | None                     |

|                    |                      | GOTO    | Wn            | Go to indirect                                           | 1             | 2              | None                     |

| DC CHARACTERISTICS |        |                                                                       | $\begin{array}{llllllllllllllllllllllllllllllllllll$ |                    |                       |       |                                                                                                                             |  |

|--------------------|--------|-----------------------------------------------------------------------|------------------------------------------------------|--------------------|-----------------------|-------|-----------------------------------------------------------------------------------------------------------------------------|--|

| Param<br>No.       | Symbol | Characteristic                                                        | Min                                                  | Typ <sup>(1)</sup> | Max                   | Units | Conditions                                                                                                                  |  |

| DI60a              | licl   | Input Low Injection Current                                           | 0                                                    | _                  | <sub>-5</sub> (5,8)   | mA    | All pins except VDD, Vss, AVDD,<br>AVss, MCLR, VcAP, SOSCI,<br>SOSCO, and RB11                                              |  |

| DI60b              | Іісн   | Input High Injection Current                                          | 0                                                    | _                  | +5 <sup>(6,7,8)</sup> | mA    | All pins except VDD, VSS, AVDD,<br>AVSS, MCLR, VCAP, SOSCI,<br>SOSCO, RB11, and all 5V<br>tolerant pins <sup>(7)</sup>      |  |

| DI60c              | ∑ ІІСТ | Total Input Injection Current<br>(sum of all I/O and control<br>pins) | -20 <sup>(9)</sup>                                   | _                  | +20 <sup>(9)</sup>    | mA    | Absolute instantaneous sum of all $\pm$ input injection currents from all I/O pins (   IICL +   IICH   ) $\leq \Sigma$ IICT |  |

#### TABLE 24-9: DC CHARACTERISTICS: I/O PIN INPUT SPECIFICATIONS (CONTINUED)

Note 1: Data in "Typ" column is at 3.3V, 25°C unless otherwise stated.

2: The leakage current on the MCLR pin is strongly dependent on the applied voltage level. The specified levels represent normal operating conditions. Higher leakage current may be measured at different input voltages.

- **3:** Negative current is defined as current sourced by the pin.

- 4: See "Pin Diagrams" for a list of 5V tolerant pins.

- **5:** VIL source < (Vss 0.3). Characterized but not tested.

- **6:** Non-5V tolerant pins VIH source > (VDD + 0.3), 5V tolerant pins VIH source > 5.5V. Characterized but not tested.

- 7: Digital 5V tolerant pins cannot tolerate any "positive" input injection current from input sources > 5.5V.

- 8: Injection currents > | 0 | can affect the ADC results by approximately 4-6 counts.

- **9:** Any number and/or combination of I/O pins not excluded under IICL or IICH conditions are permitted provided the mathematical "absolute instantaneous" sum of the input injection currents from all pins do not exceed the specified limit. Characterized but not tested.

| AC CHARACTERISTICS |               |                                                                                    | $\begin{array}{llllllllllllllllllllllllllllllllllll$ |                    |                |                   |                          |  |

|--------------------|---------------|------------------------------------------------------------------------------------|------------------------------------------------------|--------------------|----------------|-------------------|--------------------------|--|

| Param<br>No.       | Symbol        | Characteristic                                                                     | Min                                                  | Typ <sup>(1)</sup> | Max            | Units             | Conditions               |  |

| OS10               | FIN           | External CLKI Frequency<br>(External clocks allowed only<br>in EC and ECPLL modes) | DC                                                   |                    | 40             | MHz               | EC                       |  |

|                    |               | Oscillator Crystal Frequency                                                       | 3.5<br>10                                            |                    | 10<br>40<br>33 | MHz<br>MHz<br>kHz | XT<br>HS<br>SOSC         |  |

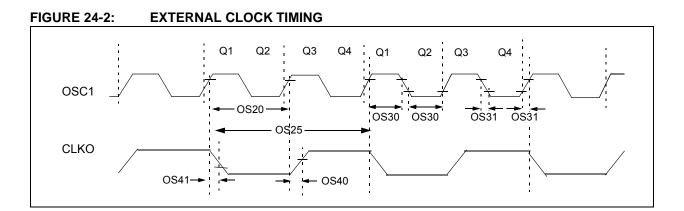

| OS20               | Tosc          | Tosc = 1/Fosc                                                                      | 12.5                                                 | _                  | DC             | ns                | _                        |  |

| OS25               | Тсү           | Instruction Cycle Time <sup>(2)</sup>                                              | 25                                                   |                    | DC             | ns                | —                        |  |

| OS30               | TosL,<br>TosH | External Clock in (OSC1)<br>High or Low Time                                       | 0.375 x Tosc                                         | _                  | 0.625 x Tosc   | ns                | EC                       |  |

| OS31               | TosR,<br>TosF | External Clock in (OSC1)<br>Rise or Fall Time                                      | —                                                    | _                  | 20             | ns                | EC                       |  |

| OS40               | TckR          | CLKO Rise Time <sup>(3)</sup>                                                      | <u> </u>                                             | 5.2                | —              | ns                | —                        |  |

| OS41               | TckF          | CLKO Fall Time <sup>(3)</sup>                                                      |                                                      | 5.2                | _              | ns                | —                        |  |

| OS42               | Gм            | External Oscillator<br>Transconductance <sup>(4)</sup>                             | 14                                                   | 16                 | 18             | mA/V              | VDD = 3.3V<br>TA = +25°C |  |

#### TABLE 24-16: EXTERNAL CLOCK TIMING REQUIREMENTS

Note 1: Data in "Typ" column is at 3.3V, 25°C unless otherwise stated.