Welcome to **E-XFL.COM**

What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded - Microcontrollers</u>"

| Details                    |                                                                                  |

|----------------------------|----------------------------------------------------------------------------------|

| Product Status             | Not For New Designs                                                              |

| Core Processor             | C166SV2                                                                          |

| Core Size                  | 16/32-Bit                                                                        |

| Speed                      | 66MHz                                                                            |

| Connectivity               | CANbus, EBI/EMI, I <sup>2</sup> C, LINbus, SPI, SSC, UART/USART, USI             |

| Peripherals                | I <sup>2</sup> S, POR, PWM, WDT                                                  |

| Number of I/O              | 116                                                                              |

| Program Memory Size        | 768KB (768K x 8)                                                                 |

| Program Memory Type        | FLASH                                                                            |

| EEPROM Size                | -                                                                                |

| RAM Size                   | 51K x 8                                                                          |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 5.5V                                                                        |

| Data Converters            | A/D 24x10b                                                                       |

| Oscillator Type            | Internal                                                                         |

| Operating Temperature      | -40°C ~ 125°C (TA)                                                               |

| Mounting Type              | Surface Mount                                                                    |

| Package / Case             | 144-LQFP Exposed Pad                                                             |

| Supplier Device Package    | PG-LQFP-144-4                                                                    |

| Purchase URL               | https://www.e-xfl.com/product-detail/infineon-technologies/xc2786x96f66lackxuma1 |

## 2 General Device Information

The XC2786X derivatives are high-performance members of the Infineon XC2000 Family of full-feature single-chip CMOS microcontrollers. These devices extend the functionality and performance of the C166 Family in terms of instructions (MAC unit), peripherals, and speed. They combine high CPU performance (up to 80 million instructions per second) with extended peripheral functionality and enhanced IO capabilities. Optimized peripherals can be adapted flexibly to meet the application requirements. These derivatives utilize clock generation via PLL and internal or external clock sources. On-chip memory modules include program Flash, program RAM, and data RAM.

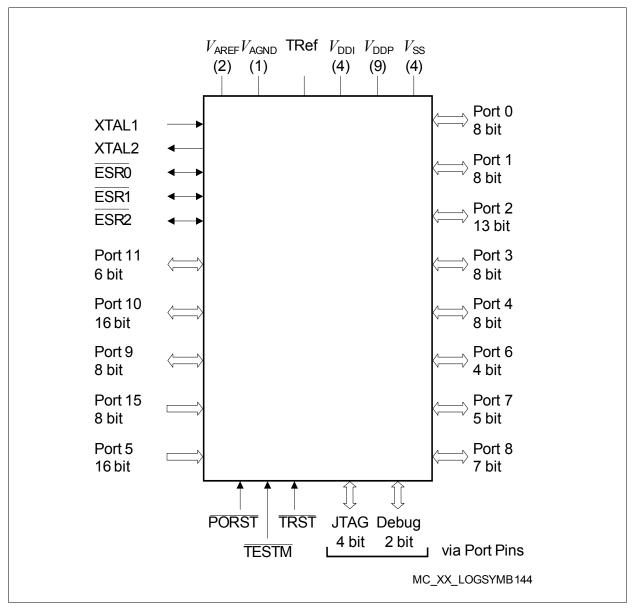

Figure 1 Logic Symbol

Table 4

Pin Definitions and Functions (cont'd)

| Pin | Symbol            | Ctrl.  | Туре | Function                                      |

|-----|-------------------|--------|------|-----------------------------------------------|

| 8   | P7.0              | O0 / I | St/B | Bit 0 of Port 7, General Purpose Input/Output |

|     | T3OUT             | 01     | St/B | GPT1 Timer T3 Toggle Latch Output             |

|     | T6OUT             | O2     | St/B | GPT2 Timer T6 Toggle Latch Output             |

|     | TDO_A             | ОН     | St/B | JTAG Test Data Output                         |

|     | ESR2_1            | I      | St/B | ESR2 Trigger Input 1                          |

| 9   | P7.3              | O0 / I | St/B | Bit 3 of Port 7, General Purpose Input/Output |

|     | EMUX1             | 01     | St/B | External Analog MUX Control Output 1 (ADC1)   |

|     | U0C1_DOUT         | O2     | St/B | USIC0 Channel 1 Shift Data Output             |

|     | U0C0_DOUT         | О3     | St/B | USIC0 Channel 0 Shift Data Output             |

|     | CCU62_<br>CCPOS1A | I      | St/B | CCU62 Position Input 1                        |

|     | TMS_C             | I      | St/B | JTAG Test Mode Selection Input                |

|     | U0C1_DX0F         | I      | St/B | USIC0 Channel 1 Shift Data Input              |

| 10  | P8.2              | O0 / I | St/B | Bit 2 of Port 8, General Purpose Input/Output |

|     | CCU60_<br>CC62    | O1 / I | St/B | CCU60 Channel 2 Input/Output                  |

| 11  | P7.1              | O0 / I | St/B | Bit 1 of Port 7, General Purpose Input/Output |

|     | EXTCLK            | 01     | St/B | Programmable Clock Signal Output              |

|     | CCU62_<br>CTRAPA  | I      | St/B | CCU62 Emergency Trap Input                    |

|     | BRKIN_C           |        | St/B | OCDS Break Signal Input                       |

| 12  | P7.4              | O0 / I | St/B | Bit 4 of Port 7, General Purpose Input/Output |

|     | EMUX2             | 01     | St/B | External Analog MUX Control Output 2 (ADC1)   |

|     | U0C1_DOUT         | O2     | St/B | USIC0 Channel 1 Shift Data Output             |

|     | U0C1_<br>SCLKOUT  | O3     | St/B | USIC0 Channel 1 Shift Clock Output            |

|     | CCU62_<br>CCPOS2A | I      | St/B | CCU62 Position Input 2                        |

|     | TCK_C             | I      | St/B | JTAG Clock Input                              |

|     | U0C0_DX0D         | I      | St/B | USIC0 Channel 0 Shift Data Input              |

|     | U0C1_DX1E         | I      | St/B | USIC0 Channel 1 Shift Clock Input             |

Table 4

Pin Definitions and Functions (cont'd)

| Pin | Symbol           | Ctrl.  | Туре | Function                                      |

|-----|------------------|--------|------|-----------------------------------------------|

| 13  | P8.1             | O0 / I | St/B | Bit 1 of Port 8, General Purpose Input/Output |

|     | CCU60_<br>CC61   | 01/I   | St/B | CCU60 Channel 1 Input/Output                  |

| 14  | P8.0             | O0 / I | St/B | Bit 0 of Port 8, General Purpose Input/Output |

|     | CCU60_<br>CC60   | 01/1   | St/B | CCU60 Channel 0 Input/Output                  |

| 16  | P6.0             | O0 / I | St/A | Bit 0 of Port 6, General Purpose Input/Output |

|     | EMUX0            | 01     | St/A | External Analog MUX Control Output 0 (ADC0)   |

|     | BRKOUT           | О3     | St/A | OCDS Break Signal Output                      |

|     | ADCx_<br>REQGTyC | I      | St/A | External Request Gate Input for ADC0/1        |

|     | U1C1_DX0E        | I      | St/A | USIC1 Channel 1 Shift Data Input              |

| 17  | P6.1             | O0 / I | St/A | Bit 1 of Port 6, General Purpose Input/Output |

|     | EMUX1            | 01     | St/A | External Analog MUX Control Output 1 (ADC0)   |

|     | T3OUT            | O2     | St/A | GPT1 Timer T3 Toggle Latch Output             |

|     | U1C1_DOUT        | O3     | St/A | USIC1 Channel 1 Shift Data Output             |

|     | ADCx_<br>REQTRyC | I      | St/A | External Request Trigger Input for ADC0/1     |

| 18  | P6.2             | O0 / I | St/A | Bit 2 of Port 6, General Purpose Input/Output |

|     | EMUX2            | 01     | St/A | External Analog MUX Control Output 2 (ADC0)   |

|     | T6OUT            | O2     | St/A | GPT2 Timer T6 Toggle Latch Output             |

|     | U1C1_<br>SCLKOUT | О3     | St/A | USIC1 Channel 1 Shift Clock Output            |

|     | U1C1_DX1C        | I      | St/A | USIC1 Channel 1 Shift Clock Input             |

| 19  | P6.3             | O0 / I | St/A | Bit 3 of Port 6, General Purpose Input/Output |

|     | T3OUT            | 02     | St/A | GPT1 Timer T3 Toggle Latch Output             |

|     | U1C1_<br>SELO0   | О3     | St/A | USIC1 Channel 1 Select/Control 0 Output       |

|     | U1C1_DX2D        | I      | St/A | USIC1 Channel 1 Shift Control Input           |

|     | ADCx_<br>REQTRyD | I      | St/A | External Request Trigger Input for ADC0/1     |

Table 4

Pin Definitions and Functions (cont'd)

| P15.4   I   In/A   Bit 4 of Port 15, General Purpose Input   ADC1_CH4   I   In/A   Analog Input Channel 4 for ADC1   T6IN   I   In/A   GPT2 Timer T6 Count/Gate Input                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | Pin | Symbol      | Ctrl. | Туре | Function                                     |  |  |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|-------------|-------|------|----------------------------------------------|--|--|

| P15.1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 21  | P15.0       | I     | In/A | Bit 0 of Port 15, General Purpose Input      |  |  |

| ADC1_CH1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |     | ADC1_CH0    | 1     | In/A | Analog Input Channel 0 for ADC1              |  |  |

| P15.2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 22  | P15.1       | I     | In/A | Bit 1 of Port 15, General Purpose Input      |  |  |

| ADC1_CH2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |     | ADC1_CH1    | ļ     | In/A | Analog Input Channel 1 for ADC1              |  |  |

| T5IN                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 23  | P15.2       | I     | In/A | <del></del>                                  |  |  |

| P15.3                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |     | ADC1_CH2    | I     | In/A | Analog Input Channel 2 for ADC1              |  |  |

| ADC1_CH3                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |     | T5IN        | I     | In/A | GPT2 Timer T5 Count/Gate Input               |  |  |

| T5EUD                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 24  | P15.3       | I     | In/A | Bit 3 of Port 15, General Purpose Input      |  |  |

| P15.4                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |     | ADC1_CH3    | I     | In/A | Analog Input Channel 3 for ADC1              |  |  |

| ADC1_CH4 I In/A Analog Input Channel 4 for ADC1 T6IN I In/A GPT2 Timer T6 Count/Gate Input  P15.5 I In/A Bit 5 of Port 15, General Purpose Input ADC1_CH5 I In/A Analog Input Channel 5 for ADC1 T6EUD I In/A GPT2 Timer T6 External Up/Down Control In  P15.6 I In/A Bit 6 of Port 15, General Purpose Input ADC1_CH6 I In/A Analog Input Channel 6 for ADC1  P15.7 I In/A Bit 7 of Port 15, General Purpose Input ADC1_CH7 I In/A Analog Input Channel 7 for ADC1  PS/A Reference Voltage for A/D Converter ADC1  VAREF0 - PS/A Reference Voltage for A/D Converter ADC0  VAREF0 - PS/A Reference Ground for A/D Converter ADC0  P5.0 I In/A Bit 0 of Port 5, General Purpose Input ADC0_CH0 I In/A Bit 1 of Port 5, General Purpose Input ADC0_CH1 I In/A Analog Input Channel 1 for ADC0  ADC0_CH1 I In/A Analog Input Channel 1 for ADC0  In/A Bit 2 of Port 5, General Purpose Input ADC0_CH2 I In/A Bit 2 of Port 5, General Purpose Input                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |     | T5EUD       | I     | In/A | GPT2 Timer T5 External Up/Down Control Input |  |  |

| T6IN                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 25  | P15.4       | I     | In/A | Bit 4 of Port 15, General Purpose Input      |  |  |

| P15.5 I In/A Bit 5 of Port 15, General Purpose Input ADC1_CH5 I In/A Analog Input Channel 5 for ADC1 T6EUD I In/A GPT2 Timer T6 External Up/Down Control In P15.6 I In/A Bit 6 of Port 15, General Purpose Input ADC1_CH6 I In/A Analog Input Channel 6 for ADC1  P15.7 I In/A Bit 7 of Port 15, General Purpose Input ADC1_CH7 I In/A Analog Input Channel 7 for ADC1  PS/A Reference Voltage for A/D Converter ADC1  VAREF1 - PS/A Reference Voltage for A/D Converter ADC1  VAREF0 - PS/A Reference Ground for A/D Converter ADC0  PS/A Reference Ground for A/D Converter ADC0  PS/A Bit 0 of Port 5, General Purpose Input ADC0_CH0 I In/A Analog Input Channel 0 for ADC0  PS.1 I In/A Bit 1 of Port 5, General Purpose Input ADC0_CH1 I In/A Analog Input Channel 1 for ADC0  In/A Bit 2 of Port 5, General Purpose Input ADC0_CH2 I In/A Analog Input Channel 2 for ADC0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |     | ADC1_CH4    | I     | In/A |                                              |  |  |

| ADC1_CH5 I In/A Analog Input Channel 5 for ADC1 T6EUD I In/A GPT2 Timer T6 External Up/Down Control In P15.6 I In/A Bit 6 of Port 15, General Purpose Input ADC1_CH6 I In/A Analog Input Channel 6 for ADC1  P15.7 I In/A Bit 7 of Port 15, General Purpose Input ADC1_CH7 I In/A Analog Input Channel 7 for ADC1  PS/A Reference Voltage for A/D Converter ADC1  PS/A Reference Voltage for A/D Converter ADC0  PS/A Reference Ground for A/D Converters ADC0  In/A Analog Input Channel 1 for ADC0  In/A Analog Input Channel 1 for ADC0  In/A Bit 2 of Port 5, General Purpose Input  ADC0_CH2 I In/A Analog Input Channel 2 for ADC0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |     | T6IN        | I     | In/A | GPT2 Timer T6 Count/Gate Input               |  |  |

| T6EUD I In/A GPT2 Timer T6 External Up/Down Control Ir  P15.6 I In/A Bit 6 of Port 15, General Purpose Input  ADC1_CH6 I In/A Analog Input Channel 6 for ADC1  P15.7 I In/A Bit 7 of Port 15, General Purpose Input  ADC1_CH7 I In/A Analog Input Channel 7 for ADC1  PS/A Reference Voltage for A/D Converter ADC1  VAREFO - PS/A Reference Voltage for A/D Converter ADC0  VAGND - PS/A Reference Ground for A/D Converters ADC0  In/A Bit 0 of Port 5, General Purpose Input  ADC0_CH0 I In/A Bit 1 of Port 5, General Purpose Input  ADC0_CH1 I In/A Analog Input Channel 1 for ADC0  In/A Bit 2 of Port 5, General Purpose Input  ADC0_CH2 I In/A Analog Input Channel 2 for ADC0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 26  | P15.5       | I     | In/A | Bit 5 of Port 15, General Purpose Input      |  |  |

| P15.6                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |     | ADC1_CH5    | I     | In/A |                                              |  |  |

| ADC1_CH6 I In/A Analog Input Channel 6 for ADC1  28 P15.7 I In/A Bit 7 of Port 15, General Purpose Input  ADC1_CH7 I In/A Analog Input Channel 7 for ADC1  29 V_{AREF1} - PS/A Reference Voltage for A/D Converter ADC1  30 V_{AREF0} - PS/A Reference Voltage for A/D Converter ADC0  31 V_{AGND} - PS/A Reference Ground for A/D Converters ADC0  32 P5.0 I In/A Bit 0 of Port 5, General Purpose Input  ADC0_CH0 I In/A Analog Input Channel 0 for ADC0  33 P5.1 I In/A Bit 1 of Port 5, General Purpose Input  ADC0_CH1 I In/A Analog Input Channel 1 for ADC0  34 P5.2 I In/A Bit 2 of Port 5, General Purpose Input  ADC0_CH2 I In/A Analog Input Channel 2 for ADC0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |     | T6EUD       | I     | In/A | GPT2 Timer T6 External Up/Down Control Input |  |  |

| P15.7 I In/A Bit 7 of Port 15, General Purpose Input  ADC1_CH7 I In/A Analog Input Channel 7 for ADC1  PS/A Reference Voltage for A/D Converter ADC1  VAREFO - PS/A Reference Voltage for A/D Converter ADC0  VAGND - PS/A Reference Ground for A/D Converters ADC0  In/A Bit 0 of Port 5, General Purpose Input  ADC0_CH0 I In/A Bit 1 of Port 5, General Purpose Input  ADC0_CH1 I In/A Analog Input Channel 1 for ADC0  In/A Bit 2 of Port 5, General Purpose Input  ADC0_CH2 I In/A Analog Input Channel 2 for ADC0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 27  | P15.6       | I     | In/A | Bit 6 of Port 15, General Purpose Input      |  |  |

| ADC1_CH7 I In/A Analog Input Channel 7 for ADC1  29  V_{AREF1} - PS/A Reference Voltage for A/D Converter ADC1  30  V_{AREF0} - PS/A Reference Voltage for A/D Converter ADC0  31  V_{AGND} - PS/A Reference Ground for A/D Converters ADC  32  P5.0 I In/A Bit 0 of Port 5, General Purpose Input  ADC0_CH0 I In/A Analog Input Channel 0 for ADC0  33  P5.1 I In/A Bit 1 of Port 5, General Purpose Input  ADC0_CH1 I In/A Analog Input Channel 1 for ADC0  34  P5.2 I In/A Bit 2 of Port 5, General Purpose Input  ADC0_CH2 I In/A Analog Input Channel 2 for ADC0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |     | ADC1_CH6    | I     | In/A | Analog Input Channel 6 for ADC1              |  |  |

| 29  V <sub>AREF1</sub> - PS/A Reference Voltage for A/D Converter ADC1 30  V <sub>AREF0</sub> - PS/A Reference Voltage for A/D Converter ADC0 31  V <sub>AGND</sub> - PS/A Reference Ground for A/D Converters ADC 32  P5.0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 28  | P15.7       | I     | In/A | Bit 7 of Port 15, General Purpose Input      |  |  |

| PS/A   Reference Voltage for A/D Converter ADCO   31   V <sub>AGND</sub>   - PS/A   Reference Ground for A/D Converters ADCO   32   P5.0   I   In/A   Bit 0 of Port 5, General Purpose Input   ADCO_CH0   I   In/A   Analog Input Channel 0 for ADCO   33   P5.1   I   In/A   Bit 1 of Port 5, General Purpose Input   ADCO_CH1   I   In/A   Analog Input Channel 1 for ADCO   34   P5.2   I   In/A   Bit 2 of Port 5, General Purpose Input   ADCO_CH2   I   In/A   Analog Input Channel 2 for ADCO   ADCO_CH2   I   In/A   Analog Input Channel 2 for ADCO   Analog Input Channel 2 for ADCO   In/A   In/A |     | ADC1_CH7    | I     | In/A | Analog Input Channel 7 for ADC1              |  |  |

| PS/A   Reference Ground for A/D Converters ADC                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 29  | $V_{AREF1}$ | -     | PS/A | Reference Voltage for A/D Converter ADC1     |  |  |

| PS/A   Reference Ground for A/D Converters ADC                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 30  | $V_{AREF0}$ | -     | PS/A | Reference Voltage for A/D Converter ADC0     |  |  |

| ADC0_CH0 I In/A Analog Input Channel 0 for ADC0  33 P5.1 I In/A Bit 1 of Port 5, General Purpose Input  ADC0_CH1 I In/A Analog Input Channel 1 for ADC0  34 P5.2 I In/A Bit 2 of Port 5, General Purpose Input  ADC0_CH2 I In/A Analog Input Channel 2 for ADC0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 31  |             | -     | PS/A | Reference Ground for A/D Converters ADC0/1   |  |  |

| P5.1 I In/A Bit 1 of Port 5, General Purpose Input ADC0_CH1 I In/A Analog Input Channel 1 for ADC0 In/A Bit 2 of Port 5, General Purpose Input ADC0_CH2 I In/A Analog Input Channel 2 for ADC0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 32  | P5.0        | 1     | In/A | Bit 0 of Port 5, General Purpose Input       |  |  |

| ADC0_CH1   In/A Analog Input Channel 1 for ADC0  34   P5.2   In/A   Bit 2 of Port 5, General Purpose Input  ADC0_CH2   In/A   Analog Input Channel 2 for ADC0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |     | ADC0_CH0    | I     | In/A | Analog Input Channel 0 for ADC0              |  |  |

| 34 P5.2 I In/A Bit 2 of Port 5, General Purpose Input ADC0_CH2 I In/A Analog Input Channel 2 for ADC0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 33  | P5.1        | I     | In/A | Bit 1 of Port 5, General Purpose Input       |  |  |

| ADC0_CH2 I In/A Analog Input Channel 2 for ADC0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |     | ADC0_CH1    |       | In/A | Analog Input Channel 1 for ADC0              |  |  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 34  | P5.2        | 1     | In/A | Bit 2 of Port 5, General Purpose Input       |  |  |

| TDI_A In/A JTAG Test Data Input                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |     | ADC0_CH2    |       | In/A | Analog Input Channel 2 for ADC0              |  |  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |     | TDI_A       |       | In/A | JTAG Test Data Input                         |  |  |

Table 4

Pin Definitions and Functions (cont'd)

| Pin | Symbol           | Ctrl.  | Type | Function                                                                                                                                     |

|-----|------------------|--------|------|----------------------------------------------------------------------------------------------------------------------------------------------|

| 122 | P9.3             | O0 / I | St/B | Bit 3 of Port 9, General Purpose Input/Output                                                                                                |

|     | CCU63_<br>COUT60 | O1     | St/B | CCU63 Channel 0 Output                                                                                                                       |

|     | BRKOUT           | 02     | St/B | OCDS Break Signal Output                                                                                                                     |

| 123 | P10.13           | O0 / I | St/B | Bit 13 of Port 10, General Purpose Input/Output                                                                                              |

|     | U1C0_DOUT        | 01     | St/B | USIC1 Channel 0 Shift Data Output                                                                                                            |

|     | U1C0_<br>SELO3   | О3     | St/B | USIC1 Channel 0 Select/Control 3 Output                                                                                                      |

|     | WR/WRL           | ОН     | St/B | External Bus Interface Write Strobe Output Active for each external write access, when WR, active for ext. writes to the low byte, when WRL. |

|     | U1C0_DX0D        | I      | St/B | USIC1 Channel 0 Shift Data Input                                                                                                             |

| 124 | P1.3             | O0 / I | St/B | Bit 3 of Port 1, General Purpose Input/Output                                                                                                |

|     | CCU62_<br>COUT63 | O1     | St/B | CCU62 Channel 3 Output                                                                                                                       |

|     | U1C0_<br>SELO7   | O2     | St/B | USIC1 Channel 0 Select/Control 7 Output                                                                                                      |

|     | U2C0_<br>SELO4   | О3     | St/B | USIC2 Channel 0 Select/Control 4 Output                                                                                                      |

|     | A11              | ОН     | St/B | External Bus Interface Address Line 11                                                                                                       |

|     | ESR2_4           | 1      | St/B | ESR2 Trigger Input 4                                                                                                                         |

|     | CCU62_<br>T12HRB | 1      | St/B | External Run Control Input for T12 of CCU62                                                                                                  |

|     | EX3AINA          | 1      | St/B | External Interrupt Trigger Input                                                                                                             |

| 125 | P9.4             | O0 / I | St/B | Bit 4 of Port 9, General Purpose Input/Output                                                                                                |

|     | CCU63_<br>COUT61 | O1     | St/B | CCU63 Channel 1 Output                                                                                                                       |

|     | U2C0_DOUT        | O2     | St/B | USIC2 Channel 0 Shift Data Output                                                                                                            |

## **Functional Description**

# 3.1 Memory Subsystem and Organization