Welcome to **E-XFL.COM**

Understanding <u>Embedded - DSP (Digital Signal Processors)</u>

Embedded - DSP (Digital Signal Processors) are specialized microprocessors designed to perform complex mathematical computations on digital signals in real-time. Unlike general-purpose processors, DSPs are optimized for high-speed numeric processing tasks, making them ideal for applications that require efficient and precise manipulation of digital data. These processors are fundamental in converting and processing signals in various forms, including audio, video, and communication signals, ensuring that data is accurately interpreted and utilized in embedded systems.

Applications of <u>Embedded - DSP (Digital Signal Processors)</u>

| Details                 |                                                                            |

|-------------------------|----------------------------------------------------------------------------|

| Product Status          | Obsolete                                                                   |

| Туре                    | Fixed Point                                                                |

| Interface               | Serial Port                                                                |

| Clock Rate              | 20MHz                                                                      |

| Non-Volatile Memory     | External                                                                   |

| On-Chip RAM             | 1.5kB                                                                      |

| Voltage - I/O           | 5.00V                                                                      |

| Voltage - Core          | 5V                                                                         |

| Operating Temperature   | -40°C ~ 85°C (TA)                                                          |

| Mounting Type           | Surface Mount                                                              |

| Package / Case          | 68-LCC (J-Lead)                                                            |

| Supplier Device Package | 68-PLCC (24.23x24.23)                                                      |

| Purchase URL            | https://www.e-xfl.com/product-detail/rochester-electronics/adsp-2105bpz-80 |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

Fabricated in a high speed, submicron, double-layer metal CMOS process, the highest-performance ADSP-21xx processors operate at 25 MHz with a 40 ns instruction cycle time. Every instruction can execute in a single cycle. Fabrication in CMOS results in low power dissipation.

The ADSP-2100 Family's flexible architecture and comprehensive instruction set support a high degree of parallelism. In one cycle the ADSP-21xx can perform all of the following operations:

- Generate the next program address

- Fetch the next instruction

- Perform one or two data moves

- Update one or two data address pointers

- Perform a computation

- Receive and transmit data via one or two serial ports

- Receive and/or transmit data via the host interface port (ADSP-2111 only)

The ADSP-2101, ADSP-2105, and ADSP-2115 comprise the basic set of processors of the family. Each of these three devices contains program and data memory RAM, an interval timer, and one or two serial ports. The ADSP-2103 is a 3.3 volt power supply version of the ADSP-2101; it is identical to the ADSP-2101 in all other characteristics. Table I shows the features of each ADSP-21xx processor.

The ADSP-2111 adds a 16-bit host interface port (HIP) to the basic set of ADSP-21xx integrated features. The host port provides a simple interface to host microprocessors or microcontrollers such as the 8031, 68000, or ISA bus.

| TABLE OF CONTENTS                                    | Capacitive Loading                           | 23       |

|------------------------------------------------------|----------------------------------------------|----------|

| GENERAL DESCRIPTION                                  | Test Conditions                              | 24       |

| Development Tools 4                                  | SPECIFICATIONS (ADSP-2103/2162/2164)         | 25       |

| Additional Information                               | Recommended Operating Conditions             | 25       |

| ARCHITECTURE OVERVIEW 4                              | Electrical Characteristics                   |          |

| Serial Ports                                         | Supply Current & Power                       |          |

| Host Interface Port (ADSP-2111) 6                    | Power Dissipation Example                    | 27       |

| Interrupts                                           | Environmental Conditions                     | 27       |

| Pin Definitions                                      | Capacitive Loading                           |          |

| SYSTEM INTERFACE                                     | Test Conditions                              |          |

| Clock Signals                                        | TIMING PARAMETERS                            |          |

| Reset                                                | (ADSP-2101/2105/2111/2115/2161/2163)         | 29       |

| Program Memory Interface                             | Clock Signals                                |          |

| Program Memory Maps                                  | Interrupts & Flags                           |          |

| Data Memory Interface                                | Bus Request-Bus Grant                        |          |

| Data Memory Map                                      | Memory Read                                  |          |

| Boot Memory Interface                                | Memory Write                                 |          |

| Bus Interface                                        | Serial Ports                                 | 35       |

| Low Power IDLE Instruction                           | Host Interface Port (ADSP-2111)              | 36       |

| ADSP-216x Prototyping                                | TIMING PARAMETERS (ADSP-2103/2162/2164)      |          |

| Ordering Procedure for ADSP-216x ROM Processors 13   | Clock Signals                                |          |

| Wafer Products                                       | Interrupts & Flags                           |          |

| Functional Differences for Older Revision Devices 14 | Bus Request-Bus Grant                        |          |

| Instruction Set                                      | Memory Read                                  | 48       |

| SPECIFICATIONS                                       | Memory Write                                 | 49       |

| (ADSP-2101/2105/2115/2161/2163)                      | Serial Ports                                 |          |

| Recommended Operating Conditions                     | PIN CONFIGURATIONS                           |          |

| Electrical Characteristics                           | 68-Pin PGA (ADSP-2101)                       | 51       |

| Supply Current & Power (ADSP-2101/2161/2163) 18      | 68-Lead PLCC (ADSP-2101/2103/2105/2115/216x) |          |

| Power Dissipation Example                            | 80-Lead PQFP (ADSP-2101/2103/2105/2105/      |          |

| Environmental Conditions                             | 80-Lead TQFP (ADSP-2115)                     |          |

| Capacitive Loading                                   | 100-Pin PGA (ADSP-2111)                      | 54       |

| Test Conditions                                      | 100-Lead PQFP (ADSP-2111)                    | 55       |

| SPECIFICATIONS                                       | PACKAGE OUTLINE DIMENSIONS                   | 00       |

| (ADSP-2111)                                          | 68-Pin PGA                                   | r 0      |

| Recommended Operating Conditions                     | 68-Lead PLCC                                 |          |

| Electrical Characteristics                           |                                              |          |

| Supply Current & Power                               | 80-Lead PQFP, 80-Lead TQFP                   |          |

| Power Dissipation Example                            | 100-Pm PGA<br>100-Lead PQFP                  | 99<br>60 |

| Environmental Conditions                             | •                                            |          |

| Liivii Oiiiiiciitai Ooiiaittoiis                     | ORDERING GUIDE                               | -62      |

-2- REV. C

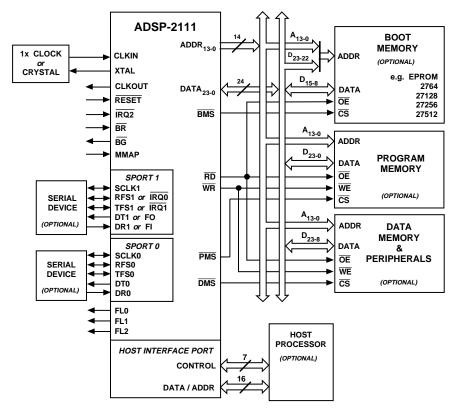

THE TWO MSBs OF THE DATA BUS (D $_{23-22}$ ) ARE USED TO SUPPLY THE TWO MSBs OF THE BOOT MEMORY EPROM ADDRESS. THIS IS ONLY REQUIRED FOR THE 27256 AND 27512.

Figure 5. ADSP-2111 System

The  $\overline{RESET}$  input resets all internal stack pointers to the empty stack condition, masks all interrupts, and clears the MSTAT register. When  $\overline{RESET}$  is released, the boot loading sequence is performed (provided there is no pending bus request and the chip is configured for booting, with MMAP = 0). The first instruction is then fetched from internal program memory location 0x0000.

### **Program Memory Interface**

The on-chip program memory address bus (PMA) and on-chip program memory data bus (PMD) are multiplexed with the on-chip data memory buses (DMA, DMD), creating a single external data bus and a single external address bus. The external data bus is bidirectional and is 24 bits wide to allow instruction fetches from external program memory. Program memory may contain code and data.

The external address bus is 14 bits wide. For the ADSP-2101, ADSP-2103, and ADSP-2111, these lines can directly address up to 16K words, of which 2K are on-chip. For the ADSP-2105 and ADSP-2115, the address lines can directly address up to 15K words, of which 1K is on-chip.

The data lines are bidirectional. The program memory select  $(\overline{PMS})$  signal indicates accesses to program memory and can be used as a chip select signal. The write  $(\overline{WR})$  signal indicates a write operation and is used as a write strobe. The read  $(\overline{RD})$  signal indicates a read operation and is used as a read strobe or output enable signal.

The ADSP-21xx processors write data from their 16-bit registers to 24-bit program memory using the PX register to provide the lower eight bits. When the processor reads 16-bit data from 24-bit program memory to a 16-bit data register, the lower eight bits are placed in the PX register.

The program memory interface can generate 0 to 7 wait states for external memory devices; default is to 7 wait states after RESET.

### **Program Memory Maps**

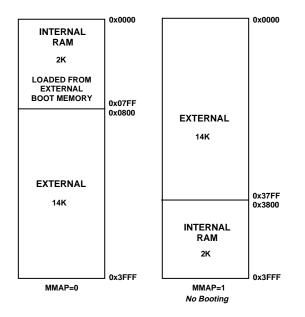

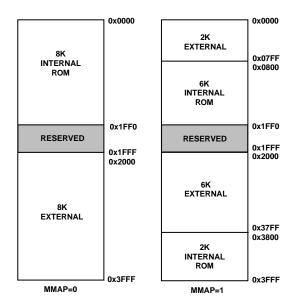

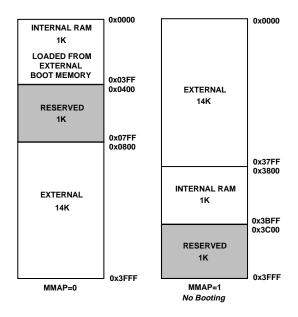

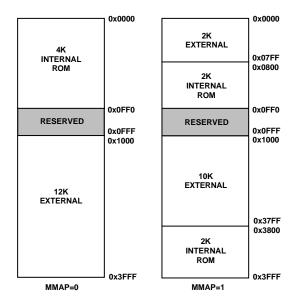

Program memory can be mapped in two ways, depending on the state of the MMAP pin. Figure 6 shows the two program memory maps for the ADSP-2101, ADSP-2103, and ADSP-2111. Figure 8 shows the program memory maps for the ADSP-2105 and ADSP-2115. Figures 7 and 9 show the program memory maps for the ADSP-2161/62 and ADSP-2163/64, respectively.

-10- REV. C

### ADSP-2101/ADSP-2103/ADSP-2111

When MMAP = 0, on-chip program memory RAM occupies 2K words beginning at address 0x0000. Off-chip program memory uses the remaining 14K words beginning at address 0x0800. In this configuration—when MMAP = 0-the boot loading sequence (described below in "Boot Memory Interface") is automatically initiated when RESET is released.

When MMAP = 1, 14K words of off-chip program memory begin at address 0x0000 and on-chip program memory RAM is located in the upper 2K words, beginning at address 0x3800. In this configuration, program memory is not booted although it can be written to and read under program control.

Figure 6. ADSP-2101/ADSP-2103/ADSP-2111 Program Memory Maps

Figure 7. ADSP-2161/62 Program Memory Maps

### ADSP-2105/ADSP-2115

When MMAP = 0, on-chip program memory RAM occupies 1K words beginning at address 0x0000. Off-chip program memory uses the remaining 14K words beginning at address 0x0800. In this configuration—when MMAP = 0-the boot loading sequence (described below in "Boot Memory Interface") is automatically initiated when RESET is released.

When MMAP = 1, 14K words of off-chip program memory begin at address 0x0000 and on-chip program memory RAM is located in the 1K words between addresses 0x3800–0x3BFF. In this configuration, program memory is not booted although it can be written to and read under program control.

Figure 8. ADSP-2105/ADSP-2115 Program Memory Maps

Figure 9. ADSP-2163/64 Program Memory Maps

REV. C

### **Data Memory Interface**

The data memory address bus (DMA) is 14 bits wide. The bidirectional external data bus is 24 bits wide, with the upper 16 bits used for data memory data (DMD) transfers.

The data memory select  $(\overline{DMS})$  signal indicates access to data memory and can be used as a chip select signal. The write  $(\overline{WR})$  signal indicates a write operation and can be used as a write strobe. The read  $(\overline{RD})$  signal indicates a read operation and can be used as a read strobe or output enable signal.

The ADSP-21xx processors support memory-mapped I/O, with the peripherals memory-mapped into the data memory address space and accessed by the processor in the same manner as data memory.

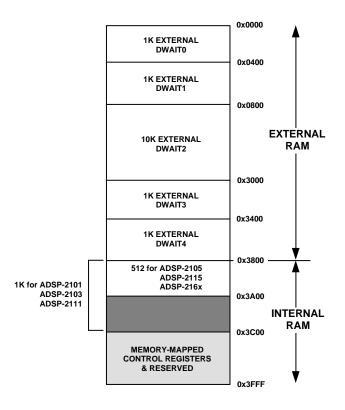

### Data Memory Map ADSP-2101/ADSP-2103/ADSP-2111

For the ADSP-2101, ADSP-2103, and ADSP-2111, on-chip data memory RAM resides in the 1K words beginning at address 0x3800, as shown in Figure 10. Data memory locations from 0x3C00 to the end of data memory at 0x3FFF are reserved. Control and status registers for the system, timer, wait-state configuration, and serial port operations are located in this region of memory.

### ADSP-2105/ADSP-2115

For the ADSP-2105 and ADSP-2115, on-chip data memory RAM resides in the 512 words beginning at address 0x3800, also shown in Figure 10. Data memory locations from 0x3A00 to the end of data memory at 0x3FFF are reserved. Control and status registers for the system, timer, wait-state configuration, and serial port operations are located in this region of memory.

Figure 10. Data Memory Map (All Processors)

#### **All Processors**

The remaining 14K of data memory is located off-chip. This external data memory is divided into five zones, each associated with its own wait-state generator. This allows slower peripherals to be memory-mapped into data memory for which wait states are specified. By mapping peripherals into different zones, you can accommodate peripherals with different wait-state requirements. All zones default to seven wait states after  $\overline{\text{RESET}}$ .

### **Boot Memory Interface**

On the ADSP-2101, ADSP-2103, and ADSP-2111, boot memory is an external 64K by 8 space, divided into eight separate 8K by 8 pages. On the ADSP-2105 and ADSP-2115, boot memory is a 32K by 8 space, divided into eight separate 4K by 8 pages. The 8-bit bytes are automatically packed into 24-bit instruction words by each processor, for loading into on-chip program memory.

Three bits in the processors' System Control Register select which page is loaded by the boot memory interface. Another bit in the System Control Register allows the forcing of a boot loading sequence under software control. Boot loading from Page 0 after  $\overline{RESET}$  is initiated automatically if MMAP = 0.

The boot memory interface can generate zero to seven wait states; it defaults to three wait states after RESET. This allows the ADSP-21xx to boot from a single low cost EPROM such as a 27C256. Program memory is booted one byte at a time and converted to 24-bit program memory words.

The BMS and RD signals are used to select and to strobe the boot memory interface. Only 8-bit data is read over the data bus, on pins D8-D15. To accommodate up to eight pages of boot memory, the two MSBs of the data bus are used in the boot memory interface as the two MSBs of the boot memory address: D23, D22, and A13 supply the boot page number.

The ADSP-2100 Family Assembler and Linker allow the creation of programs and data structures requiring multiple boot pages during execution.

The  $\overline{BR}$  signal is recognized during the booting sequence. The bus is granted after loading the current byte is completed.  $\overline{BR}$  during booting may be used to implement booting under control of a host processor.

### **Bus Interface**

The ADSP-21xx processors can relinquish control of their data and address buses to an external device. When the external device requires control of the buses, it asserts the bus request signal  $(\overline{BR})$ . If the ADSP-21xx is not performing an external memory access, it responds to the active  $\overline{BR}$  input in the next cycle by:

- Three-stating the data and address buses and the PMS, DMS, BMS, RD, WR output drivers,

- Asserting the bus grant (BG) signal,

- and halting program execution.

If the Go mode is set, however, the ADSP-21xx will not halt program execution until it encounters an instruction that requires an external memory access.

-12- REV. C

## ADSP-2101/2105/2115/2161/2163-SPECIFICATIONS

ADSP-21xx

## RECOMMENDED OPERATING CONDITIONS

| Parame                                              | ter                           | K G<br>Min | rade<br>Max | B Gi<br>Min | rade<br>Max | T Gi<br>Min | rade<br>Max | Unit |

|-----------------------------------------------------|-------------------------------|------------|-------------|-------------|-------------|-------------|-------------|------|

| $egin{array}{c} V_{ m DD} \ T_{ m AMB} \end{array}$ | Supply Voltage                | 4.50       | 5.50        | 4.50        | 5.50        | 4.50        | 5.50        | V    |

|                                                     | Ambient Operating Temperature | 0          | +70         | -40         | +85         | -55         | +125        | °C   |

See "Environmental Conditions" for information on thermal specifications.

### **ELECTRICAL CHARACTERISTICS**

| Parameter           |                                               | Test Conditions                                                                           | Min               | Max | Unit |

|---------------------|-----------------------------------------------|-------------------------------------------------------------------------------------------|-------------------|-----|------|

| $\overline{V_{IH}}$ | Hi-Level Input Voltage <sup>3, 5</sup>        | @ V <sub>DD</sub> = max                                                                   | 2.0               |     | V    |

| $V_{IH}$            | Hi-Level CLKIN Voltage                        | $@V_{DD} = max$                                                                           | 2.2               |     | V    |

| $V_{IL}$            | Lo-Level Input Voltage <sup>I, 3</sup>        | $@V_{DD} = min$                                                                           |                   | 0.8 | V    |

| $V_{OH}$            | Hi-Level Output Voltage <sup>2, 3, 7</sup>    | @ $V_{DD} = min, I_{OH} = -0.5 \text{ mA}$                                                | 2.4               |     | V    |

|                     |                                               | @ $V_{DD} = min, I_{OH} = -100  \mu A^8$                                                  | $V_{ m DD} - 0.3$ |     | V    |

| $V_{\mathrm{OL}}$   | Lo-Level Output Voltage <sup>2, 3, 7</sup>    | $@V_{DD} = min, I_{OL} = 2 mA$                                                            |                   | 0.4 | V    |

| $I_{IH}$            | Hi-Level Input Current <sup>1</sup>           | $@V_{DD} = max, V_{IN} = V_{DD} max$                                                      |                   | 10  | μA   |

| $[_{ m IL}$         | Lo-Level Input Current <sup>1</sup>           | $@V_{DD} = max, V_{IN} = 0 V$                                                             |                   | 10  | μA   |

| [ <sub>OZH</sub>    | Tristate Leakage Current <sup>4</sup>         | $@V_{DD} = max, V_{IN} = V_{DD} max^6$                                                    |                   | 10  | μA   |

| OZL                 | Tristate Leakage Current <sup>4</sup>         | @ $V_{DD} = \max_{i} V_{IN} = 0 V^6$                                                      |                   | 10  | μA   |

| $C_{\rm I}$         | Input Pin Capacitance <sup>1, 8, 9</sup>      | @ $V_{IN} = 2.5 \text{ V}$ , $f_{IN} = 1.0 \text{ MHz}$ , $T_{AMB} = 25 ^{\circ}\text{C}$ |                   | 8   | pF   |

| $C_0$               | Output Pin Capacitance <sup>4, 8, 9, 10</sup> | @ $V_{IN} = 2.5 \text{ V}$ , $f_{IN} = 1.0 \text{ MHz}$ , $T_{AMB} = 25^{\circ}\text{C}$  |                   | 8   | pF   |

#### NOTES

Specifications subject to change without notice.

### ABSOLUTE MAXIMUM RATINGS\*

| Supply Voltage0.3 V to +7 V                                       |

|-------------------------------------------------------------------|

| Input Voltage0.3 V to $V_{DD}$ + 0.3 V                            |

| Output Voltage Swing $-0.3 \text{ V}$ to $V_{DD} + 0.3 \text{ V}$ |

| Operating Temperature Range (Ambient)55°C to +125°C               |

| Storage Temperature Range65°C to +150°C                           |

| Lead Temperature (10 sec) PGA+300°C                               |

| Lead Temperature (5 sec) PLCC, PQFP, TQFP +280°C                  |

\*Stresses greater than those listed above may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions greater than those indicated in the operational sections of this specification is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

### CAUTION

ESD (electrostatic discharge) sensitive device. Electrostatic charges as high as 4000 V readily accumulate on the human body and test equipment and can discharge without detection. Although the ADSP-21xx processors feature proprietary ESD protection circuitry to dissipate high energy electrostatic discharges (Human Body Model), permanent damage may occur to devices subjected to such discharges. Therefore, proper ESD precautions are recommended to avoid performance degradation or loss of functionality. Unused devices must be stored in conductive foam or shunts, and the foam should be discharged to the destination socket before the devices are removed. Per method 3015 of MIL-STD-883, the ADSP-21xx processors have been classified as Class 1 devices.

REV. C –17–

<sup>&</sup>lt;sup>1</sup>Input-only pins: CLKIN, RESET, IRQ2, BR, MMAP, DR1, DR0 (not on ADSP-2105).

<sup>&</sup>lt;sup>2</sup>Output pins:  $\overline{BG}$ ,  $\overline{PMS}$ ,  $\overline{DMS}$ ,  $\overline{BMS}$ ,  $\overline{RD}$ ,  $\overline{WR}$ , A0-A13, CLKOUT, DT1, DT0 (not on ADSP-2105).

<sup>&</sup>lt;sup>3</sup>Bidirectional pins: D0-D23, SCLK1, RFS1, TFS1, SCLK0 (not on ADSP-2105), RFS0 (not on ADSP-2105), TFS0 (not on ADSP-2105).

<sup>&</sup>lt;sup>4</sup>Tristatable pins: A0–A13, D0–D23, <u>PMS</u>, <u>DMS</u>, <u>BMS</u>, <u>RD</u>, <u>WR</u>, DT1, SCLK1, RSF1, TFS1, DT0 (not on ADSP-2105), SCLK0 (not on ADSP-2105), RFS0 (not on ADSP-2105), TFS0 (not on ADSP-2105).

<sup>&</sup>lt;sup>5</sup>Input-only pins: RESET, IRQ2, BR, MMAP, DR1, DR0 (not on ADSP-2105).

$<sup>^{6}</sup>$ 0 V on  $\overline{BR}$ , CLKIN Active (to force tristate condition).

$<sup>^7</sup>$ Although specified for TTL outputs, all ADSP-21xx outputs are CMOS-compatible and will drive to  $V_{\,

m DD}$  and GND, assuming no dc loads.

<sup>&</sup>lt;sup>8</sup>Guaranteed but not tested.

<sup>&</sup>lt;sup>9</sup>Applies to PGA, PLCC, PQFP package types.

<sup>&</sup>lt;sup>10</sup>Output pin capacitance is the capacitive load for any three-stated output pin.

### SPECIFICATIONS (ADSP-2111)

### POWER DISSIPATION EXAMPLE

To determine total power dissipation in a specific application, the following equation should be applied for each output:

$$C \times V_{DD}^2 \times f$$

C =load capacitance, f =output switching frequency.

### **Example:**

In an ADSP-2111 application where external data memory is used and no other outputs are active, power dissipation is calculated as follows:

Assumptions:

- External data memory is accessed every cycle with 50% of the address pins switching.

- External data memory writes occur every other cycle with 50% of the data pins switching

- Each address and data pin has a 10 pF total load at the pin.

- The application operates at  $V_{DD} = 5.0 \text{ V}$  and  $t_{CK} = 50 \text{ ns}$ .

Total Power Dissipation =  $P_{INT} + (C \times V_{DD}^2 \times f)$

$P_{INT}$  = internal power dissipation (from Figure 17).

$(C \times V_{DD}^2 \times f)$  is calculated for each output:

| Output                 | # of<br>Pins |                        | $\times V_{DD}^2$      | ×f                                       |

|------------------------|--------------|------------------------|------------------------|------------------------------------------|

| Address, DMS           | 8            | × 10 pF                | $\times 5^2 \text{ V}$ | $\times$ 20 MHz = 40.0 mW                |

| Data, $\overline{WR}$  | 9            | $\times 10 \text{ pF}$ | $\times 5^2 \text{ V}$ | $\times$ 10 MHz = 22.5 mW                |

| $\overline{\text{RD}}$ | 1            | $\times$ 10 pF         | $\times 5^2 \text{ V}$ | $\times 10 \text{ MHz} = 2.5 \text{ mW}$ |

| CLKOUT                 | 1            | $\times$ 10 pF         | $\times 5^2 \text{ V}$ | $\times 20 \text{ MHz} = 5.0 \text{ mW}$ |

70.0 mW

Total power dissipation for this example =  $P_{INT}$  + 70.0 mW.

### **ENVIRONMENTAL CONDITIONS**

**Ambient Temperature Rating:**

$$T_{AMB} = T_{CASE} - (PD \times \theta_{CA})$$

$$\begin{split} T_{AMB} &= T_{CASE} - (PD \times \theta_{CA}) \\ T_{CASE} &= Case \ Temperature \ in \ ^{\circ}C \end{split}$$

PD = Power Dissipation in W

$\theta_{CA}$  = Thermal Resistance (Case-to-Ambient)

$\theta_{JA}$  = Thermal Resistance (Junction-to-Ambient)

$\theta_{JC}$  = Thermal Resistance (Junction-to-Case)

#### **Package** $\theta_{JA}$ $\theta_{IC}$ $\theta_{CA}$ **PGA** 35°C/W 18°C/W 17°C/W **PQFP** 42°C/W 18°C/W 23°C/W

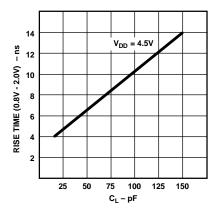

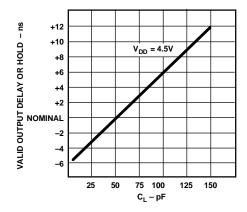

### CAPACITIVE LOADING

Figures 18 and 19 show capacitive loading characteristics for the ADSP-2111.

Figure 18. Typical Output Rise Time vs. Load Capacitance, C (at Maximum Ambient Operating Temperature)

Figure 19. Typical Output Valid Delay or Hold vs. Load Capacitance, C<sub>L</sub> (at Maximum Ambient Operating Temperature)

REV. C -23-

## SPECIFICATIONS (ADSP-2103/2162/2164)

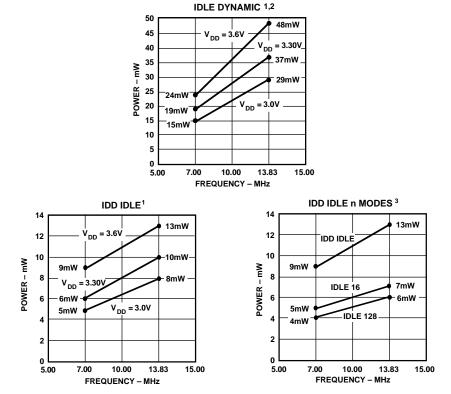

SUPPLY CURRENT & POWER (ADSP-2103/2162/2164)

| Para                    | meter                                                                          | Test Conditions                                                                           | Min | Max     | Unit     |

|-------------------------|--------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------|-----|---------|----------|

| $I_{ m DD}$ $I_{ m DD}$ | Supply Current (Dynamic) <sup>1</sup><br>Supply Current (Idle) <sup>1, 3</sup> | @ $V_{DD}$ = max, $t_{CK}$ = 72.3 ns <sup>2</sup><br>@ $V_{DD}$ = max, $t_{CK}$ = 72.3 ns |     | 14<br>4 | mA<br>mA |

#### NOTES

For typical supply current (internal power dissipation) figures, see Figure 23.

VALID FOR ALL TEMPERATURE GRADES.

- 1 POWER REFLECTS DEVICE OPERATING WITH NO OUTPUT LOADS.

- <sup>2</sup> IDLE REFERS TO ADSP-21xx OPERATION DURING EXECUTION OF IDLE INSTRUCTION. DEASSERTED PINS ARE DRIVEN TO EITHER V  $_{\rm DD}$  OR GND. 3 MAXIMUM POWER DISSIPATION AT V  $_{\rm DD}$  = 3.6V DURING EXECUTION OF *IDLE n* INSTRUCTION.

Figure 23. ADSP-2103 Power (Typical) vs. Frequency

REV. C -26-

<sup>&</sup>lt;sup>1</sup>Current reflects device operating with no output loads.

$<sup>^{2}</sup>V_{IN} = 0.4 \text{ V} \text{ and } 2.4 \text{ V}.$

$<sup>^3</sup>$ Idle refers to ADSP-21xx state of operation during execution of IDLE instruction. Deasserted pins are driven to either V  $_{

m DD}$  or GND.

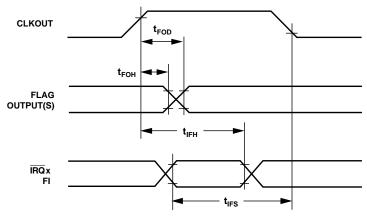

## TIMING PARAMETERS (ADSP-2101/2105/2111/2115/2161/2163) INTERRUPTS & FLAGS

| Parar              | neter                                     | 13 MH<br>Min | Iz<br>Max | 13.824<br>Min | MHz<br>Max |    | MHz<br>Max | 20 M<br>Min | Hz<br>Max | 25 M<br>Min | Hz<br>Max | Frequency<br>Dependency<br>Min Max | Unit |

|--------------------|-------------------------------------------|--------------|-----------|---------------|------------|----|------------|-------------|-----------|-------------|-----------|------------------------------------|------|

| Timin              | g Requirement:                            |              |           |               |            |    |            |             |           |             |           |                                    |      |

| $t_{IFS}$          | IRQx <sup>1</sup> or FI Setup before      | 34.2         |           | 33.1          |            | 30 |            | 27.5        |           | 25          |           | $0.25t_{CK} + 15^4$                | ns   |

|                    | CLKOUT Low <sup>2, 3</sup>                |              |           |               |            |    |            |             |           |             |           |                                    |      |

| $t_{IFS}$          | IRQx <sup>1</sup> or FI Setup before      | 37.2         |           | 36.1          |            | 33 |            | 30.5        |           | 28          |           | $0.25t_{CK} + 18^4$                | ns   |

|                    | CLKOUT Low (ADSP-2111) <sup>2, 3</sup>    |              |           |               |            |    |            |             |           |             |           |                                    |      |

| $t_{\mathrm{IFH}}$ | IRQx <sup>1</sup> or FI Hold after CLKOUT | 19.2         |           | 18.1          |            | 15 |            | 12.5        |           | 10          |           | $0.25t_{\rm CK}$                   | ns   |

|                    | High <sup>2, 3</sup>                      |              |           |               |            |    |            |             |           |             |           |                                    |      |

| Switch             | ning Characteristic:                      |              |           |               |            |    |            |             |           |             |           |                                    |      |

| $t_{FOH}$          | FO Hold after CLKOUT High <sup>5</sup>    | 0            |           | 0             |            | 0  |            | 0           |           | 0           |           | 0                                  | ns   |

| $t_{FOD}$          | FO Delay from CLKOUT High                 |              | 15        |               | 15         |    | 15         |             | 15        |             | 12        |                                    | ns   |

### NOTES

$<sup>^{5}</sup>t_{FOH}$  (min) = -5 ns for ADSP-2111TG-52 and ADSP-2111TG/883B-52 (Extended Temperature Range devices).

Figure 30. Interrupts & Flags

REV. C -31-

<sup>&</sup>lt;sup>1</sup>IRQx=IRQ0, IRQ1, and IRQ2.

<sup>&</sup>lt;sup>2</sup>If IRQx and FI inputs meet t<sub>IFS</sub> and t<sub>IFH</sub> setup/hold requirements, they will be recognized during the current clock cycle; otherwise they will be recognized during the following cycle. (Refer to the "Interrupt Controller" section in Chapter 3, Program Control, of the ADSP-2100 Family User's Manual for further information on interrupt servicing.)

<sup>&</sup>lt;sup>3</sup>Edge-sensitive interrupts require pulse widths greater than 10 ns. Level-sensitive interrupts must be held low until serviced.

$<sup>^4</sup>$ t<sub>IFS</sub> (min) = 0.25t<sub>CK</sub> +  $^2$ 0 ns for ADSP-2101TG-50, ADSP-2101TG/883B-50, ADSP-2111TG-52, and ADSP-2111TG/883B-52 (Extended Temperature Range devices).

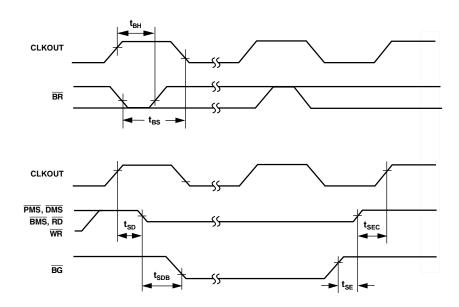

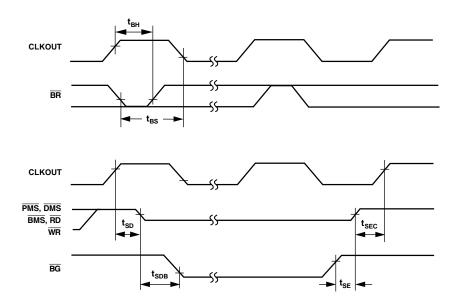

## TIMING PARAMETERS (ADSP-2101/2105/2111/2115/2161/2163) BUS REQUEST/GRANT

| Parameter                                                                                            | 13 MHz<br>Min Max |      | 4 MHz<br>Max |    | MHz<br>Max | 20 M<br>Min | IHz<br>Max | 25 M<br>Min | Hz<br>Max | Frequency<br>Dependency<br>Min | Max               | Unit |

|------------------------------------------------------------------------------------------------------|-------------------|------|--------------|----|------------|-------------|------------|-------------|-----------|--------------------------------|-------------------|------|

| Timing Requirement:                                                                                  |                   |      |              |    |            |             |            |             |           |                                |                   |      |

| $t_{BH}$ $\overline{BR}$ Hold after CLKOUT High <sup>1</sup>                                         | 24.2              | 23.1 |              | 20 |            | 17.5        |            | 15          |           | $0.25t_{CK} + 5$               |                   | ns   |

| $t_{BS}$ BR Setup before CLKOUT Low <sup>1</sup>                                                     | 39.2              | 38.1 |              | 35 |            | 32.5        |            | 30          |           | $0.25t_{CK} + 20$              |                   | ns   |

| Switching Characteristic:                                                                            |                   |      |              |    |            |             |            |             |           |                                |                   |      |

| $t_{SD}$ CLKOUT High to $\overline{DMS}$ ,                                                           | 39.2              |      | 38.1         |    | 35         |             | 32.5       |             | 30        |                                | $0.25t_{CK} + 20$ | ns   |

| $\overline{PMS}$ , $\overline{BMS}$ , $\overline{RD}$ , $\overline{WR}$ Disable                      |                   |      |              |    |            |             |            |             |           |                                |                   |      |

| $t_{SDB}$ $\overline{DMS}$ , $\overline{PMS}$ , $\overline{BMS}$ , $\overline{RD}$ , $\overline{WR}$ | 0                 | 0    |              | 0  |            | 0           |            | 0           |           | 0                              |                   | ns   |

| Disable to $\overline{BG}$ Low                                                                       |                   |      |              |    |            |             |            |             |           |                                |                   |      |

| $t_{SE}$ $\overline{BG}$ High to $\overline{DMS}$ , $\overline{PMS}$ ,                               | 0                 | 0    |              | 0  |            | 0           |            | 0           |           | 0                              |                   | ns   |

| $\overline{\mathrm{BMS}}, \overline{\mathrm{RD}}, \overline{\mathrm{WR}}$ Enable                     |                   |      |              |    |            |             |            |             |           |                                |                   |      |

| $t_{SEC}$ $\overline{DMS}$ , $\overline{PMS}$ , $\overline{BMS}$ , $\overline{RD}$ , $\overline{WR}$ | 9.2               | 8.1  |              | 5  |            | 2.5         |            | $1.5^{2}$   |           | $0.25t_{CK} - 10^2$            |                   | ns   |

| Enable to CLKOUT High                                                                                |                   |      |              |    |            |             |            |             |           |                                |                   |      |

### NOTES

Section 10.2.4, "Bus Request/Grant," on page 212 of the ADSP-2100 Family User's Manual (1st Edition, 1993) states that "When  $\overline{BR}$  is recognized, the processor responds immediately by asserting  $\overline{BG}$  during the same cycle." This is incorrect for the current versions of all ADSP-21xx processors:  $\overline{BG}$  is asserted in the cycle after  $\overline{BR}$  is recognized. No external synchronization circuit is needed when  $\overline{BR}$  is generated as an asynchronous signal.

Figure 31. Bus Request/Grant

-32- REV. C

$<sup>{}^{1}</sup>$ If  $\overline{BR}$  meets the  $t_{BS}$  and  $t_{BH}$  setup/hold requirements, it will be recognized in the current processor cycle; otherwise it is recognized in the following cycle.  $\overline{BR}$  requires a pulse width greater than 10 ns.

$<sup>^2</sup> For 25$  MHz only the minimum frequency dependency formula for  $t_{SEC}$  = (0.25  $t_{CK} - 8.5$ ).

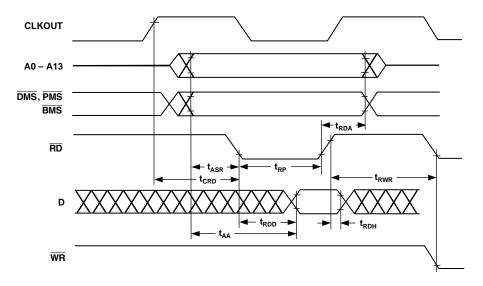

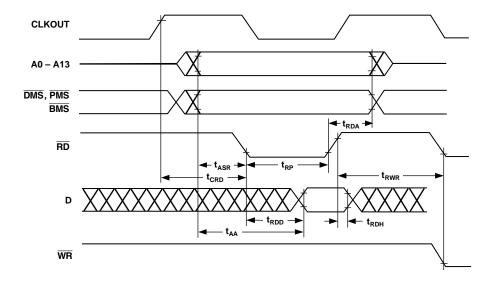

## TIMING PARAMETERS (ADSP-2101/2105/2111/2115/2161/2163) MEMORY READ

| Parameter                                                                                                         | 13 M<br>Min | Hz<br>Max | 13.824<br>Min | 4 MHz<br>Max | 16.67<br>Min | MHz<br>Max | 20 M<br>Min | Hz<br>Max | 25 M<br>Min | Hz<br>Max | Unit |

|-------------------------------------------------------------------------------------------------------------------|-------------|-----------|---------------|--------------|--------------|------------|-------------|-----------|-------------|-----------|------|

| Timing Requirement:                                                                                               |             |           |               |              |              |            |             |           |             |           |      |

| t <sub>RDD</sub> RD Low to Data Valid                                                                             |             | 23.5      |               | 23.2         |              | 17         |             | 12        |             | 7         | ns   |

| t <sub>AA</sub> A0–A13, $\overline{\text{PMS}}$ , $\overline{\text{DMS}}$ , $\overline{\text{BMS}}$ to Data Valid |             | 37.7      |               | 36.2         |              | 27         |             | 19.5      |             | 12        | ns   |

| t <sub>RDH</sub> Data Hold from RD High                                                                           | 0           |           | 0             |              | 0            |            | 0           |           | 0           |           | ns   |

| Switching Characteristic:                                                                                         |             |           |               |              |              |            |             |           |             |           |      |

| t <sub>RP</sub> RD Pulse Width                                                                                    | 33.5        |           | 28.2          |              | 22           |            | 17          |           | 12          |           | ns   |

| $t_{CRD}$ CLKOUT High to $\overline{RD}$ Low                                                                      | 14.2        | 29.2      | 13.1          | 28.1         | 10           | 25         | 7.5         | 22.5      | 5           | 20        | ns   |

| $t_{ASR}$ A0–A13, $\overline{PMS}$ , $\overline{DMS}$ , $\overline{BMS}$ Setup before                             | 9.2         |           | 8.1           |              | 5            |            | 2.5         |           | $1.5^{1}$   |           | ns   |

| $\overline{ m RD}$ Low                                                                                            |             |           |               |              |              |            |             |           |             |           |      |

| $t_{RDA}$ A0–A13, $\overline{PMS}$ , $\overline{DMS}$ , $\overline{BMS}$ Hold after $\overline{RD}$               | 10.2        |           | 9.1           |              | 6            |            | 3.5         |           | 1           |           | ns   |

| Deasserted                                                                                                        |             |           |               |              |              |            |             |           |             |           |      |

| $t_{RWR}$ $\overline{RD}$ High to $\overline{RD}$ or $\overline{WR}$ Low                                          | 33.5        |           | 31.2          |              | 25           |            | 20          |           | 15          |           | ns   |

| Parameter                                                                                           | Frequency Depende<br>(CLKIN ≤ 25 MHz)<br>Min | ncy<br>Max            | Unit |

|-----------------------------------------------------------------------------------------------------|----------------------------------------------|-----------------------|------|

|                                                                                                     | IVIIII                                       | IVIAX                 |      |

| Timing Requirement:                                                                                 |                                              |                       |      |

| t <sub>RDD</sub> RD Low to Data Valid                                                               |                                              | $0.5t_{CK} - 13 + w$  | ns   |

| $t_{AA}$ A0–A13, $\overline{PMS}$ , $\overline{DMS}$ , $\overline{BMS}$ to Data Valid               |                                              | $0.75t_{CK} - 18 + w$ | ns   |

| $t_{RDH}$ Data Hold from $\overline{RD}$ High                                                       | 0                                            |                       |      |

| Switching Characteristic:                                                                           |                                              |                       |      |

| $t_{RP}$ RD Pulse Width                                                                             | $0.5t_{CK} - 8 + w$                          |                       | ns   |

| t <sub>CRD</sub> CLKOUT High to $\overline{\text{RD}}$ Low                                          | $0.25t_{CK} - 5$                             | $0.25t_{CK} + 10$     | ns   |

| $t_{ASR}$ A0–A13, $\overline{PMS}$ , $\overline{DMS}$ , $\overline{BMS}$ Setup before               |                                              |                       |      |

| $\overline{ m RD}$ Low                                                                              | $0.25t_{CK} - 10^1$                          |                       | ns   |

| $t_{RDA}$ A0–A13, $\overline{PMS}$ , $\overline{DMS}$ , $\overline{BMS}$ Hold after $\overline{RD}$ |                                              |                       |      |

| Deasserted                                                                                          | 0.25t <sub>CK</sub> – 9                      |                       | ns   |

| $t_{RWR}$ $\overline{RD}$ High to $\overline{RD}$ or $\overline{WR}$ Low                            | 0.5t <sub>CK</sub> – 5                       |                       | ns   |

#### NOTES

$^1For~25$  MHz only minimum frequency dependency formula for  $t_{ASR}$  = (0.25  $t_{CK}$  – 8.5). w = wait states  $\times~t_{CK.}$

Figure 32. Memory Read

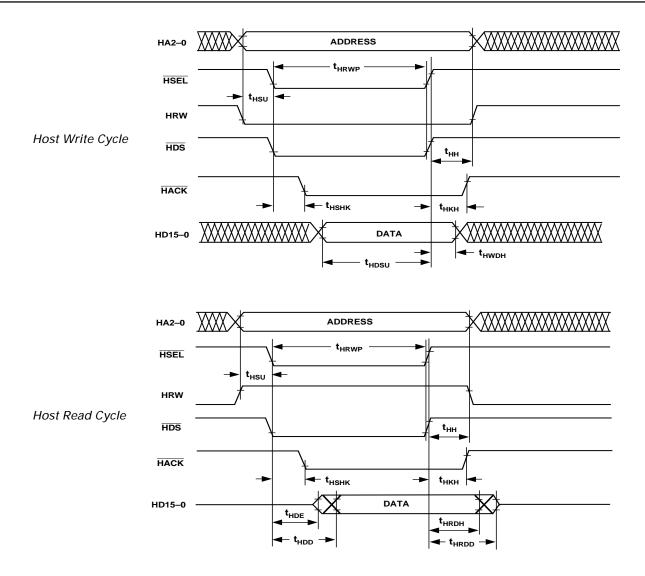

## TIMING PARAMETERS (ADSP-2111)

HOST INTERFACE PORT

Separate Data & Address (HMD1 = 0)

Read/Write Strobe & Data Strobe (HMD0 = 1)

| Parameter                                                                    | 13.0<br>Min | MHz<br>Max | 16.67<br>Min | MHz<br>Max | 20 M<br>Min | Hz<br>Max | No Frequency<br>Dependency | Unit |

|------------------------------------------------------------------------------|-------------|------------|--------------|------------|-------------|-----------|----------------------------|------|

| Timing Requirement:                                                          |             |            |              |            |             |           |                            |      |

| t <sub>HSU</sub> HA2-0, HRW Setup before Start of Write or Read <sup>1</sup> | 8           |            | 8            |            | 8           |           |                            | ns   |

| t <sub>HDSU</sub> Data Setup before End of Write <sup>2</sup>                | 8           |            | 8            |            | 8           |           |                            | ns   |

| t <sub>HWDH</sub> Data Hold after End of Write <sup>2</sup>                  | 3           |            | 3            |            | 3           |           |                            | ns   |

| t <sub>HH</sub> HA2-0, HRW Hold after End of Write or Read <sup>2</sup>      | 3           |            | 3            |            | 3           |           |                            | ns   |

| t <sub>HRWP</sub> Read or Write Pulse Width <sup>3</sup>                     | 30          |            | 30           |            | 30          |           |                            | ns   |

| Switching Characteristic:                                                    |             |            |              |            |             |           |                            |      |

| t <sub>HSHK</sub> HACK Low after Start of Write or Read <sup>1</sup>         | 0           | 20         | 0            | 20         | 0           | 20        |                            | ns   |

| t <sub>HKH</sub> HACK Hold after End of Write or Read <sup>2</sup>           | 0           | 20         | 0            | 20         | 0           | 20        |                            | ns   |

| t <sub>HDE</sub> Data Enabled after Start of Read <sup>1</sup>               | 0           |            | 0            |            | 0           |           |                            | ns   |

| t <sub>HDD</sub> Data Valid after Start of Read <sup>1</sup>                 |             | 23         |              | 23         |             | 23        |                            | ns   |

| t <sub>HRDH</sub> Data Hold after End of Read <sup>2</sup>                   | 0           |            | 0            |            | 0           |           |                            | ns   |

| t <sub>HRDD</sub> Data Disabled after End of Read <sup>2</sup>               |             | 10         |              | 10         |             | 10        |                            | ns   |

REV. C -38-

<sup>&</sup>lt;sup>1</sup>Start of Write or Read =  $\overline{HDS}$  Low and  $\overline{HSEL}$  Low.

<sup>2</sup>End of Write or Read =  $\overline{HDS}$  High or  $\overline{HSEL}$  High.

<sup>3</sup>Read or Write Pulse Width =  $\overline{HDS}$  Low and  $\overline{HSEL}$  Low.

Figure 36. Host Interface Port (HMD1 = 0, HMD0 =1)

REV. C -39-

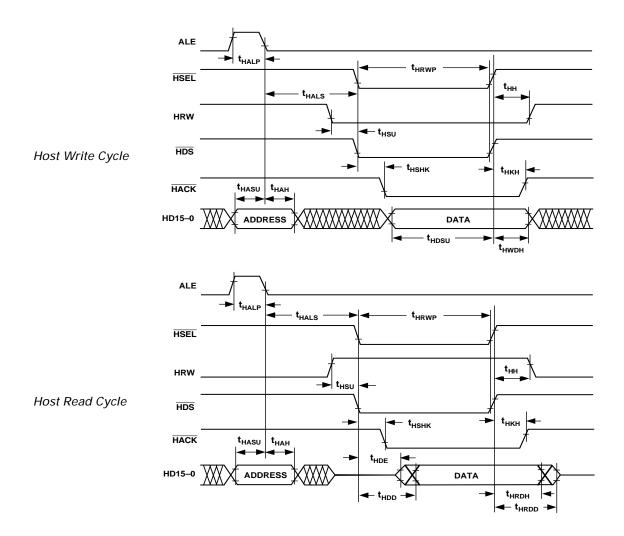

## **TIMING PARAMETERS (ADSP-2111)**

HOST INTERFACE PORT Multiplexed Data & Address (HMD1 = 1) Read Strobe & Write Strobe (HMD0 = 0)

| Parameter                                                               | 13.0<br>Min | MHz<br>Max | 16.67<br>Min | MHz<br>Max | 20 M<br>Min | Hz<br>Max | No Frequency<br>Dependency | Unit |

|-------------------------------------------------------------------------|-------------|------------|--------------|------------|-------------|-----------|----------------------------|------|

| Timing Requirement:                                                     |             |            |              |            |             |           |                            |      |

| t <sub>HALP</sub> ALE Pulse Width                                       | 15          |            | 15           |            | 15          |           |                            | ns   |

| t <sub>HASU</sub> HAD15-0 Address Setup before ALE Low                  | 5           |            | 5            |            | 5           |           |                            | ns   |

| t <sub>HAH</sub> HAD15-0 Address Hold after ALE Low                     | 2           |            | 2            |            | 2           |           |                            | ns   |

| t <sub>HALS</sub> Start of Write or Read after ALE Low <sup>1, 2</sup>  | 15          |            | 15           |            | 15          |           |                            | ns   |

| t <sub>HDSU</sub> HAD15-0 Data Setup before End of Write <sup>3</sup>   | 8           |            | 8            |            | 8           |           |                            | ns   |

| t <sub>HWDH</sub> HAD15-0 Data Hold after End of Write <sup>3</sup>     | 3           |            | 3            |            | 3           |           |                            | ns   |

| t <sub>HRWP</sub> Read or Write Pulse Width <sup>5</sup>                | 30          |            | 30           |            | 30          |           |                            | ns   |

| Switching Characteristic:                                               |             |            |              |            |             |           |                            |      |

| t <sub>HSHK</sub> HACK Low after Start of Write or Read <sup>1, 2</sup> | 0           | 20         | 0            | 20         | 0           | 20        |                            | ns   |

| t <sub>HKH</sub> HACK Hold after End of Write or Read <sup>3, 4</sup>   | 0           | 20         | 0            | 20         | 0           | 20        |                            | ns   |

| t <sub>HDE</sub> HAD15-0 Data Enabled after Start of Read <sup>2</sup>  | 0           |            | 0            |            | 0           |           |                            | ns   |

| t <sub>HDD</sub> HAD15-0 Data Valid after Start of Read <sup>2</sup>    |             | 23         |              | 23         |             | 23        |                            | ns   |

| t <sub>HRDH</sub> HAD15-0 Data Hold after End of Read <sup>4</sup>      | 0           |            | 0            |            | 0           |           |                            | ns   |

| t <sub>HRDD</sub> HAD15-0 Data Disabled after End of Read <sup>4</sup>  |             | 10         |              | 10         |             | 10        |                            | ns   |

### NOTES

REV. C -40-

NOTES

1Start of Write = HWR Low and HSEL Low.

2Start of Read = HRD Low and HSEL Low.

3End of Write = HWR High or HSEL High.

4End of Read = HRD High or HSEL High.

5Read Pulse Width = HRD Low and HSEL Low, Write Pulse Width = HWR Low and HSEL Low.

## **TIMING PARAMETERS (ADSP-2111)**

HOST INTERFACE PORT Multiplexed Data & Address (HMD1 = 1) Read/Write Strobe & Data Strobe (HMD0 = 1)

| Parameter                                                              |    | MHz<br>Max | 16.67<br>Min | MHz<br>Max | 20 M<br>Min | Hz<br>Max | No Frequency<br>Dependency | Unit |

|------------------------------------------------------------------------|----|------------|--------------|------------|-------------|-----------|----------------------------|------|

| Timing Requirement:                                                    |    |            |              |            |             |           |                            |      |

| t <sub>HALP</sub> ALE Pulse Width                                      | 15 |            | 15           |            | 15          |           |                            | ns   |

| t <sub>HASU</sub> HAD15-0 Address Setup before ALE Low                 | 5  |            | 5            |            | 5           |           |                            | ns   |

| t <sub>HAH</sub> HAD15-0 Address Hold after ALE Low                    | 2  |            | 2            |            | 2           |           |                            | ns   |

| t <sub>HALS</sub> Start of Write or Read after ALE Low <sup>1</sup>    | 15 |            | 15           |            | 15          |           |                            | ns   |

| t <sub>HSU</sub> HRW Setup before Start of Write or Read <sup>1</sup>  | 8  |            | 8            |            | 8           |           |                            | ns   |

| t <sub>HDSU</sub> HAD15-0 Data Setup before End of Write <sup>2</sup>  | 5  |            | 5            |            | 5           |           |                            | ns   |

| t <sub>HWDH</sub> HAD15-0 Data Hold after End of Write <sup>2</sup>    | 3  |            | 3            |            | 3           |           |                            | ns   |

| t <sub>HH</sub> HRW Hold after End of Write or Read <sup>2</sup>       | 3  |            | 3            |            | 3           |           |                            | ns   |

| t <sub>HRWP</sub> Read or Write Pulse Width <sup>3</sup>               | 30 |            | 30           |            | 30          |           |                            | ns   |

| Switching Characteristic:                                              |    |            |              |            |             |           |                            |      |

| t <sub>HSHK</sub> HACK Low after Start of Write or Read <sup>1</sup>   | 0  | 20         | 0            | 20         | 0           | 20        |                            | ns   |

| t <sub>HKH</sub> HACK Hold after End of Write or Read <sup>2</sup>     | 0  | 20         | 0            | 20         | 0           | 20        |                            | ns   |

| t <sub>HDE</sub> HAD15-0 Data Enabled after Start of Read <sup>1</sup> | 0  |            | 0            |            | 0           |           |                            | ns   |

| t <sub>HDD</sub> HAD15-0 Data Valid after Start of Read <sup>1</sup>   |    | 23         |              | 23         |             | 23        |                            | ns   |

| t <sub>HRDH</sub> HAD15-0 Data Hold after End of Read <sup>2</sup>     | 0  |            | 0            |            | 0           |           |                            | ns   |

| t <sub>HRDD</sub> HAD15-0 Data Disabled after End of Read <sup>2</sup> |    | 10         |              | 10         |             | 10        |                            | ns   |

### NOTES

REV. C -42-

In the state of Write or Read =  $\overline{HDS}$  Low and  $\overline{HSEL}$  Low.

2 End of Write or Read =  $\overline{HDS}$  High or  $\overline{HSEL}$  High.

3 Read or Write Pulse Width =  $\overline{HDS}$  Low and  $\overline{HSEL}$  Low.

Figure 38. Host Interface Port (HMD1 = 1, HMD0 = 1)

REV. C -43-

# TIMING PARAMETERS (ADSP-2103/2162/2164) BUS REQUEST/GRANT

| Parameter                                                                                                                           | 10.24 Min | MHz<br>Max | Frequency<br>Dependency<br>Min | Max               | Unit |

|-------------------------------------------------------------------------------------------------------------------------------------|-----------|------------|--------------------------------|-------------------|------|

| Timing Requirement:                                                                                                                 |           |            |                                |                   |      |

| t <sub>BH</sub> BR Hold after CLKOUT High <sup>1</sup>                                                                              | 29.4      |            | $0.25t_{CK} + 5$               |                   | ns   |

| t <sub>BS</sub> BR Setup before CLKOUT Low <sup>1</sup>                                                                             | 44.4      |            | $0.25t_{CK} + 20$              |                   | ns   |

| Switching Characteristic:                                                                                                           |           |            |                                |                   |      |

| $t_{SD}$ CLKOUT High to $\overline{DMS}$ , $\overline{PMS}$ , $\overline{BMS}$ , $\overline{RD}$ , $\overline{WR}$ Disable          |           | 44.4       |                                | $0.25t_{CK} + 20$ | ns   |

| $t_{SDB}$ $\overline{DMS}$ , $\overline{PMS}$ , $\overline{BMS}$ , $\overline{RD}$ , $\overline{WR}$ Disable to $\overline{BG}$ Low |           |            |                                |                   | ns   |

| $t_{SE}$ $\overline{BG}$ High to $\overline{DMS}$ , $\overline{PMS}$ , $\overline{BMS}$ , $\overline{RD}$ , $\overline{WR}$ Enable  | 0         |            |                                |                   | ns   |

| $t_{SEC}$ $\overline{DMS}$ , $\overline{PMS}$ , $\overline{BMS}$ , $\overline{RD}$ , $\overline{WR}$ Enable to CLKOUT High          | 14.4      |            | $0.25t_{CK} - 10$              |                   | ns   |

### NOTES

Section 10.2.4, "Bus Request/Grant," of the ADSP-2100 Family User's Manual (1st Edition, ©1993) states that "When  $\overline{BR}$  is recognized, the processor responds immediately by asserting  $\overline{BG}$  during the same cycle." This is incorrect for the current versions of all ADSP-21xx processors:  $\overline{BG}$  is asserted in the cycle after  $\overline{BR}$  is recognized. No external synchronization circuit is needed when  $\overline{BR}$  is generated as an asynchronous signal.

Figure 41. Bus Request/Grant

REV. C -47-

$<sup>^{1}</sup>$ If  $\overline{BR}$  meets the  $t_{BS}$  and  $t_{BH}$  setup/hold requirements, it will be recognized in the current processor cycle; otherwise it is recognized in the following cycle.  $\overline{BR}$  requires a pulse width greater than 10 ns.

## TIMING PARAMETERS (ADSP-2103/2162/2164)

### **MEMORY READ**

| Parameter        |                                                                                                      |      | MHz<br>Max | Frequency<br>Dependency<br>Min | Max                   | Unit |

|------------------|------------------------------------------------------------------------------------------------------|------|------------|--------------------------------|-----------------------|------|

| Timing           | Requirement:                                                                                         |      |            |                                |                       |      |

| $t_{ m RDD}$     | RD Low to Data Valid                                                                                 |      | 33.8       |                                | $0.5t_{CK} - 15 + w$  | ns   |

| $t_{AA}$         | A0–A13, $\overline{\text{PMS}}$ , $\overline{\text{DMS}}$ , $\overline{\text{BMS}}$ to Data Valid    |      | 49.2       |                                | $0.75t_{CK} - 24 + w$ | ns   |

| $t_{RDH}$        | Data Hold from $\overline{\mathrm{RD}}$ High                                                         | 0    |            |                                |                       | ns   |

| Switchi          | ing Characteristic:                                                                                  |      |            |                                |                       |      |

| $t_{RP}$         | RD Pulse Width                                                                                       | 43.8 |            | $0.5t_{CK} - 5 + w$            |                       | ns   |

| $t_{CRD}$        | CLKOUT High to $\overline{\text{RD}}$ Low                                                            | 19.4 | 34.4       | $0.25t_{CK} - 5$               | $0.25t_{CK} + 10$     | ns   |

| t <sub>ASR</sub> | A0–A13, $\overline{PMS}$ , $\overline{DMS}$ , $\overline{BMS}$ Setup before $\overline{RD}$ Low      | 12.4 |            | $0.25t_{CK} - 12$              |                       | ns   |

| $t_{RDA}$        | A0–A13, $\overline{PMS}$ , $\overline{DMS}$ , $\overline{BMS}$ Hold after $\overline{RD}$ Deasserted | 14.4 |            | $0.25t_{CK} - 10$              |                       | ns   |

| $t_{RWR}$        | $\overline{\mathrm{RD}}$ High to $\overline{\mathrm{RD}}$ or $\overline{\mathrm{WR}}$ Low            | 38.8 |            | $0.5t_{CK} - 10$               |                       | ns   |

$w = wait \ states \times \ t_{CK.}$

Figure 42. Memory Read

-48- REV. C

NC = NO CONNECT

## PIN CONFIGURATIONS 68-Pin PGA

|    | L          | K               | J    | н                     | G     | F              | E               | D               | С   | В   | Α   | _  |

|----|------------|-----------------|------|-----------------------|-------|----------------|-----------------|-----------------|-----|-----|-----|----|

| 1  |            | V <sub>DD</sub> | А3   | A1                    | RESET | BR             | V <sub>DD</sub> | D22             | D20 | GND |     | 1  |

| 2  | A5         | A6              | A4   | A2                    | A0    | IRQ2           | ММАР            | D23             | D21 | D19 | D18 | 2  |

| 3  | GND        | A7              |      | •                     | D17   | D16            | 3               |                 |     |     |     |    |

| 4  | A8         | <b>A9</b>       |      | PGA PACKAGE ADSP-2101 |       |                |                 |                 |     |     |     | 4  |

| 5  | A10        | A11             |      |                       |       |                |                 |                 |     |     |     | 5  |

| 6  | A12        | A13             |      |                       |       |                |                 |                 |     | GND | D11 | 6  |

| 7  | PMS        | DMS             |      |                       | T     | OP VIE         | w               |                 |     | D10 | D9  | 7  |

| 8  | BMS        | BG              |      |                       | (PII  | NS DO          | WN)             |                 |     | D8  | D7  | 8  |

| 9  | XTAL       | CLK<br>IN       |      |                       |       |                |                 |                 |     | D6  | D5  | 9  |

| 10 | CLK<br>OUT | RD              | TFS0 | GND                   | SCLK0 | IRQ1<br>(TFS1) | FI<br>(DR1)     | V <sub>DD</sub> | D1  | D4  | D3  | 10 |

| 11 |            | WR              | DT0  | RFS0                  | DR0   | FO<br>(DT1)    | IRQ0<br>(RFS1)  | SCLK1           | D0  | D2  |     | 11 |

|    | L          | к               | J    | н                     | G     | F              | Е               | D               | С   | В   | Α   | •  |

|    | Α   | В   | С             | D                        | E               | F              | G     | н    | J    | ĸ               | L          |    |

|----|-----|-----|---------------|--------------------------|-----------------|----------------|-------|------|------|-----------------|------------|----|

| 1  |     | GND | D20           | D22                      | V <sub>DD</sub> | BR             | RESET | A1   | А3   | V <sub>DD</sub> |            | 1  |

| 2  | D18 | D19 | D21           | D23                      | ММАР            | IRQ2           | A0    | A2   | A4   | A6              | A5         | 2  |

| 3  | D16 | D17 | INDEX<br>(NC) |                          | -               |                | -     |      |      | A7              | GND        | 3  |

| 4  | D14 | D15 |               | _                        | А9              | A8             | 4     |      |      |                 |            |    |

| 5  | D12 | D13 |               | PGA PACKAGE<br>ADSP-2101 |                 |                |       |      |      |                 |            | 5  |

| 6  | D11 | GND |               |                          |                 |                |       |      |      | A13             | A12        | 6  |

| 7  | D9  | D10 |               |                          | вот             | том            | VIEW  |      |      | DMS             | PMS        | 7  |

| 8  | D7  | D8  |               |                          | (F              | PINS U         | IP)   |      |      | BG              | BMS        | 8  |

| 9  | D5  | D6  |               |                          |                 |                |       |      |      | CLK<br>IN       | XTAL       | 9  |

| 10 | D3  | D4  | D1            | V <sub>DD</sub>          | FI<br>(DR 1)    | IRQ1<br>(TFS1) | SCLK0 | GND  | TFS0 | RD              | CLK<br>OUT | 10 |

| 11 |     | D2  | D0            | SCLK1                    | IRQ0<br>(RFS1)  | FO<br>(DT1)    | DR0   | RFS0 | DT0  | WR              |            | 11 |

|    | Α   | В   | С             | D                        | Е               | F              | G     | н    | J    | ĸ               | L          | •  |

| PGA<br>Number | Pin<br>Name     |

|---------------|-----------------|

| K11           | WR              |

| K10           | RD              |

| J11           | DT0             |

| J10           | TFS0            |

| H11           | RFS0            |

| H10           | GND             |

| G11           | DR0             |

| G10           | SCLK0           |

| F11           | FO <i>(DT1)</i> |

| F10           | IRQ1 (TFS1)     |

| E11           | IRQ0 (RFS1)     |

| E10           | FI <i>(DR1)</i> |

| D11           | SCLK1           |

| D10           | $V_{ m DD}$     |

| C11           | D0              |

| C10           | D1              |

| B11           | D2              |

| PGA<br>Number | Pin<br>Name |

|---------------|-------------|

| A10           | D3          |

| B10           | D4          |

| A9            | D5          |

| B9            | D6          |

| A8            | D7          |

| B8            | D8          |

| A7            | D9          |

| B7            | D10         |

| A6            | D11         |

| B6            | GND         |

| A5            | D12         |

| B5            | D13         |

| A4            | D14         |

| B4            | D15         |

| A3            | D16         |

| B3            | D17         |

| A2            | D18         |

| PGA<br>Number | Pin<br>Name            |

|---------------|------------------------|

| B1            | GND                    |

| B2            | D19                    |

| C1            | D20                    |

| C2            | D21                    |

| D1            | D22                    |

| D2            | D23                    |

| E1            | $V_{ m DD}$            |

| E2            | MMAP                   |

| F1            | $\overline{\text{BR}}$ |

| F2            | ĪRQ2                   |

| G1            | RESET                  |

| G2            | A0                     |

| H1            | A1                     |

| H2            | A2                     |

| J1            | A3                     |

| J2            | A4                     |

| K1            | $V_{ m DD}$            |

| PGA<br>Number | Pin<br>Name               |

|---------------|---------------------------|

| L2            | A5                        |

| K2            | A6                        |

| L3            | GND                       |

| K3            | A7                        |

| L4            | A8                        |

| K4            | A9                        |

| L5            | A10                       |

| K5            | A11                       |

| L6            | A12                       |

| K6            | A13                       |

| L7            | PMS                       |

| K7            | $\overline{\mathrm{DMS}}$ |

| L8            | $\overline{\mathrm{BMS}}$ |

| K8            | $\overline{\text{BG}}$    |

| L9            | XTAL                      |

| K9            | CLKIN                     |

| L10           | CLKOUT                    |

| C3            | Index (NC)                |

REV. C -51-

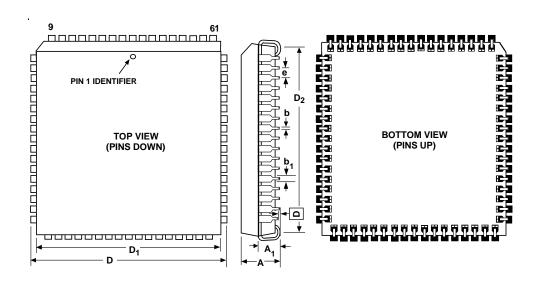

# OUTLINE DIMENSIONS ADSP-21xx 68-Lead Plastic Leaded Chip Carrier (PLCC)

|                       | INCHES |       |       | MIL   | LIMETE | RS    |

|-----------------------|--------|-------|-------|-------|--------|-------|

| SYMBOL                | MIN    | TYP   | MAX   | MIN   | TYP    | MAX   |

| Α                     | 0.169  | 0.172 | 0.175 | 4.29  | 4.37   | 4.45  |

| <b>A</b> <sub>1</sub> |        | 0.104 |       |       | 2.64   |       |

| b                     | 0.017  | 0.018 | 0.019 | 0.43  | 0.46   | 0.48  |

| b <sub>1</sub>        | 0.027  | 0.028 | 0.029 | 0.69  | 0.71   | 0.74  |

| D                     | 0.985  | 0.990 | 0.995 | 25.02 | 25.15  | 25.27 |

| D <sub>1</sub>        | 0.950  | 0.952 | 0.954 | 24.13 | 24.18  | 24.23 |

| D <sub>2</sub>        | 0.895  | 0.910 | 0.925 | 22.73 | 23.11  | 23.50 |

| е                     |        | 0.050 |       |       | 1.27   |       |

| ٥                     |        |       | 0.004 |       |        | 0.10  |

REV. C -57-