Welcome to E-XFL.COM

### Understanding <u>Embedded - DSP (Digital</u> <u>Signal Processors)</u>

#### Embedded - DSP (Digital Signal Processors) are specialized microprocessors designed to perform complex mathematical computations on digital signals in real-time. Unlike general-purpose processors, DSPs are optimized for high-speed numeric processing tasks, making them ideal for applications that require efficient and precise manipulation of digital data. These processors are fundamental in converting and processing signals in various forms, including audio, video, and communication signals, ensuring that data is accurately interpreted and utilized in embedded systems.

### Applications of <u>Embedded - DSP (Digital</u> <u>Signal Processors)</u>

#### Details

| Details                 |                                                                      |

|-------------------------|----------------------------------------------------------------------|

| Product Status          | Obsolete                                                             |

| Туре                    | Fixed Point                                                          |

| Interface               | Synchronous Serial Port (SSP)                                        |

| Clock Rate              | 25MHz                                                                |

| Non-Volatile Memory     | External                                                             |

| On-Chip RAM             | 3kB                                                                  |

| Voltage - I/O           | 5.00V                                                                |

| Voltage - Core          | 5.00V                                                                |

| Operating Temperature   | -40°C ~ 85°C (TA)                                                    |

| Mounting Type           | Surface Mount                                                        |

| Package / Case          | 68-LCC (J-Lead)                                                      |

| Supplier Device Package | 68-PLCC (24.23x24.23)                                                |

| Purchase URL            | https://www.e-xfl.com/product-detail/analog-devices/adsp-2115bpz-100 |

|                         |                                                                      |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

#### ĴĹ INSTRUCTION FLAGS PROGRAM DATA (ADSP-2111 Only REGISTER MEMOR) MEMORY воот DATA DATA SRAM SRAM ADDRESS ADDRESS ADDRESS TIMER or RON PROGRAM SEQUENCER GENERATOR GENERATOR GENERATOR #2 PMA BUS PMA BUS 14 EXTERNAL MUX ADDRESS DMA BUS DMA BUS 14 BUS PMD BUS PMD BUS 24 EXTERNAL BUS EXCHANGE MUX DATA DMD BUS BUS DMD BUS 16 ſ INPUT REGS INPUT REGS COMPANDING CIRCUITRY INPUT REGS HOST PORT SHIFTER CONTROL ALU MAC EXTERNAL TRANSMIT REG TRANSMIT REG HOST PORT OUTPUT REGS OUTPUT REGS OUTPUT REGS RECEIVE REG RECEIVE REG 16 BUS HOST SERIAL ٦Ļ ٦Ļ ٦Ļ SERIAI PORT PORT 0 PORT 1 DATA (Not on ADSP-2105) R Bus HOST INTERFACE PORT ۶Ł (ADSP-2111 Only)

Figure 1. ADSP-21xx Block Diagram

One bus grant execution mode (GO Mode) allows the ADSP-21xx to continue running from internal memory. A second execution mode requires the processor to halt while buses are granted.

Each ADSP-21xx processor can respond to several different interrupts. There can be up to three external interrupts, configured as edge- or level-sensitive. Internal interrupts can be generated by the timer, serial ports, and, on the ADSP-2111, the host interface port. There is also a master **RESET** signal.

Booting circuitry provides for loading on-chip program memory automatically from byte-wide external memory. After reset, three wait states are automatically generated. This allows, for example, a 60 ns ADSP-2101 to use a 200 ns EPROM as external boot memory. Multiple programs can be selected and loaded from the EPROM with no additional hardware.

The data receive and transmit pins on SPORT1 (Serial Port 1) can be alternatively configured as a general-purpose input flag and output flag. You can use these pins for event signalling to and from an external device. The ADSP-2111 has three additional flag outputs whose states are controlled through software.

A programmable interval timer can generate periodic interrupts. A 16-bit count register (TCOUNT) is decremented every n cycles, where n-1 is a scaling value stored in an 8-bit register (TSCALE). When the value of the count register reaches zero, an interrupt is generated and the count register is reloaded from a 16-bit period register (TPERIOD).

### **Serial Ports**

The ADSP-21xx processors include two synchronous serial ports ("SPORTs") for serial communications and multiprocessor communication. All of the ADSP-21xx processors have two serial ports (SPORT0, SPORT1) except for the ADSP-2105, which has only SPORT1.

ADSP-21xx

The serial ports provide a complete synchronous serial interface with optional companding in hardware. A wide variety of framed or frameless data transmit and receive modes of operation are available. Each SPORT can generate an internal programmable serial clock or accept an external serial clock.

Each serial port has a 5-pin interface consisting of the following signals:

| Signal Name | Function                             |

|-------------|--------------------------------------|

| SCLK        | Serial Clock (I/O)                   |

| RFS         | Receive Frame Synchronization (I/O)  |

| TFS         | Transmit Frame Synchronization (I/O) |

| DR          | Serial Data Receive                  |

| DT          | Serial Data Transmit                 |

The ADSP-21xx serial ports offer the following capabilities:

**Bidirectional**—Each SPORT has a separate, double-buffered transmit and receive function.

**Flexible Clocking**—Each SPORT can use an external serial clock or generate its own clock internally.

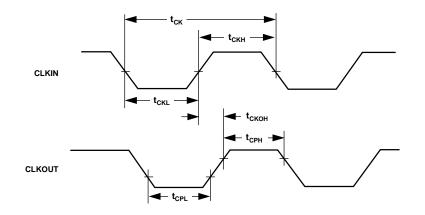

A clock output signal (CLKOUT) is generated by the processor, synchronized to the processor's internal cycles.

### Reset

The **RESET** signal initiates a complete reset of the ADSP-21xx. The **RESET** signal must be asserted when the chip is powered up to assure proper initialization. If the **RESET** signal is applied during initial power-up, it must be held long enough to allow the processor's internal clock to stabilize. If **RESET** is activated at any time after power-up and the input clock frequency does not change, the processor's internal clock continues and does not require this stabilization time.

The power-up sequence is defined as the total time required for the crystal oscillator circuit to stabilize after a valid  $V_{DD}$  is applied to the processor and for the internal phase-locked loop (PLL) to lock onto the specific crystal frequency. A minimum of 2000  $t_{CK}$  cycles will ensure that the PLL has locked (this does not, however, include the crystal oscillator start-up time). During this power-up sequence the  $\overline{\text{RESET}}$  signal should be held low. On any subsequent resets, the RESET signal must meet the minimum pulse width specification,  $t_{RSP}$ .

To generate the **RESET** signal, use either an RC circuit with an external Schmidt trigger or a commercially available reset IC. (Do not use only an RC circuit.)

| Pin<br>Name(s)                                 | # of<br>Pins | Input /<br>Output | Function                                                                                                                                             |

|------------------------------------------------|--------------|-------------------|------------------------------------------------------------------------------------------------------------------------------------------------------|

| Address                                        | 14           | 0                 | Address outputs for program, data and boot memory.                                                                                                   |

| Data <sup>1</sup>                              | 24           | I/O               | Data I/O pins for program and data memories. Input only for                                                                                          |

|                                                |              |                   | boot memory, with two MSBs used for boot memory addresses.                                                                                           |

|                                                |              |                   | Unused data lines may be left floating.                                                                                                              |

| RESET                                          | 1            | I                 | Processor Reset Input                                                                                                                                |

| IRQ2                                           | 1            | I                 | External Interrupt Request #2                                                                                                                        |

| $\overline{\mathrm{BR}}^2$                     | 1            | Ι                 | External Bus Request Input                                                                                                                           |

| BG                                             | 1            | 0                 | External Bus Grant Output                                                                                                                            |

| PMS                                            | 1            | 0                 | External Program Memory Select                                                                                                                       |

| DMS                                            | 1            | 0                 | External Data Memory Select                                                                                                                          |

| BMS                                            | 1            | 0                 | Boot Memory Select                                                                                                                                   |

| RD                                             | 1            | 0                 | External Memory Read Enable                                                                                                                          |

| WR                                             | 1            | 0                 | External Memory Write Enable                                                                                                                         |

| MMAP                                           | 1            | I                 | Memory Map Select Input                                                                                                                              |

| CLKIN, XTAL                                    | 2            | I                 | External Clock or Quartz Crystal Input                                                                                                               |

| CLKOUT                                         | 1            | 0                 | Processor Clock Output                                                                                                                               |

| V <sub>DD</sub><br>GND                         |              |                   | Power Supply Pins<br>Ground Pins                                                                                                                     |

| SPORT0 <sup>3</sup>                            | F            | I/O               |                                                                                                                                                      |

| SPORT1                                         | 55           | I/O<br>I/O        | Serial Port 0 Pins ( <i>TFS0, RFS0, DT0, DR0, SCLK0</i> )<br>Serial Port 1 Pins ( <i>TFS1, RFS1, DT1, DR1, SCLK1</i> )                               |

| or Interrupts & Flags:                         | 5            | 1/0               | Selial Folt I Fills (IFSI, IFSI, DII, DII, SCLM)                                                                                                     |

| IRQ0 (RFS1)                                    | 1            | I                 | External Interrupt Request #0                                                                                                                        |

| $\frac{1RQ0}{IRQ1}$ (TFS1)                     |              | I                 | External Interrupt Request #1                                                                                                                        |

| FI (DR1)                                       | 1            | I                 | Flag Input Pin                                                                                                                                       |

| FO (DT1)                                       | 1            | 0                 | Flag Output Pin                                                                                                                                      |

| FL2-0 (ADSP-2111 Only)                         | 3            | 0                 | General Purpose Flag Output Pins                                                                                                                     |

| Host Interface Port                            | 0            | Ŭ                 | ochorar i alpose i lag o'alput i lis                                                                                                                 |

|                                                |              |                   |                                                                                                                                                      |

| $\frac{(ADSP-2111 \text{ Only})}{\text{HOEL}}$ | 1            |                   | LUD Colort Lourt                                                                                                                                     |

| HSEL                                           | 1            | I                 | HIP Select Input                                                                                                                                     |

| HACK<br>HSIZE                                  |              | O<br>I            | HIP Acknowledge Output                                                                                                                               |

|                                                |              | I                 | 8/16-Bit Host Select $(0 = 16\text{-}Bit, 1 = 8\text{-}Bit)$<br>Root Mode Select $(0 = Standard EBROM Resting 1 = UIR Resting)$                      |

| BMODE                                          | 1            | I                 | Boot Mode Select ( $0 = Standard EPROM Booting, 1 = HIP Booting$ )<br>Bug Strade Select ( $0 = \overline{PD}(\overline{WP} = 1 - PW(\overline{DS}))$ |

| HMD0                                           | 1            |                   | Bus Strobe Select $(0 = \overline{RD}/\overline{WR}, 1 = RW/\overline{DS})$<br>HID Addrees/Data Mode Select $(0 = Senarate 1 = Multiplexed)$         |

| HMD1<br>HRD/HRW                                |              | I<br>I            | HIP Address/Data Mode Select (0 = Separate, 1 = Multiplexed)<br>HIP Read Strobe or Read/Write Select                                                 |

| $\frac{HRD}{HWR}$                              |              | I                 | HIP Kead Strobe or Kead write Select<br>HIP Write Strobe or Host Data Strobe Select                                                                  |

| HWR/HDS<br>HD15-0/HAD15-0                      | 16           | I<br>I/O          | HIP Write Strobe or Host Data Strobe Select<br>HIP Data or HIP Data and Address                                                                      |

| HA2/ALE                                        | 10           | I/O<br>I          |                                                                                                                                                      |

| HA1–0/Unused                                   | 2            | I                 | Host Address 2 Input <i>or</i> Address Latch Enable Input                                                                                            |

|                                                | 6            | 1                 | Host Address 1 and 0 Inputs                                                                                                                          |

#### **Table IV. ADSP-21xx Pin Definitions**

NOTES

<sup>1</sup>Unused data bus lines may be left floating.

$^{2}\overline{\text{BR}}$  must be tied high (to  $V_{\text{DD}}$ ) if not used.

<sup>3</sup>ADSP-2105 does not have SPORT0. (SPORT0 pins are No Connects on the ADSP-2105.)

THE TWO  $\,$  MSBs of the data BUS (D\_{23-22}) are used to supply the two MSBs of the boot memory eprom address. This is only required for the 27256 and 27512.

THE TWO MSBs OF THE DATA BUS (D $_{23-22}$ ) ARE USED TO SUPPLY THE TWO MSBs OF THE BOOT MEMORY EPROM ADDRESS. THIS IS ONLY REQUIRED FOR THE 27256 AND 27512.

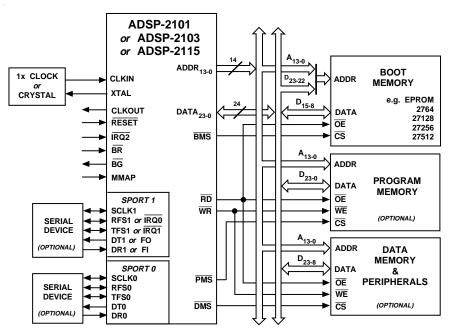

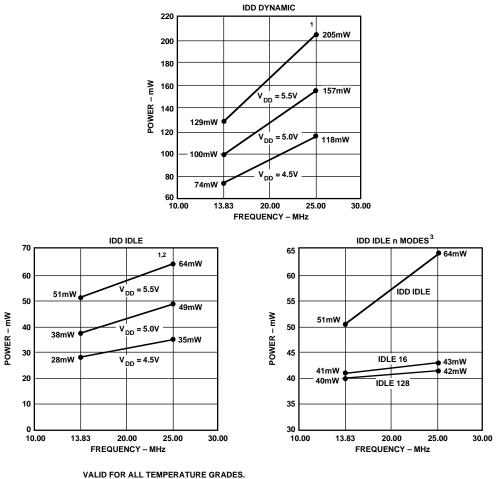

Figure 4. ADSP-2105 System

### **Data Memory Interface**

The data memory address bus (DMA) is 14 bits wide. The bidirectional external data bus is 24 bits wide, with the upper 16 bits used for data memory data (DMD) transfers.

The data memory select  $(\overline{DMS})$  signal indicates access to data memory and can be used as a chip select signal. The write  $(\overline{WR})$  signal indicates a write operation and can be used as a write strobe. The read  $(\overline{RD})$  signal indicates a read operation and can be used as a read strobe or output enable signal.

The ADSP-21xx processors support memory-mapped I/O, with the peripherals memory-mapped into the data memory address space and accessed by the processor in the same manner as data memory.

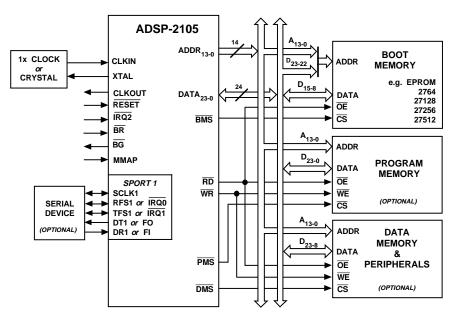

### Data Memory Map ADSP-2101/ADSP-2103/ADSP-2111

For the ADSP-2101, ADSP-2103, and ADSP-2111, on-chip data memory RAM resides in the 1K words beginning at address 0x3800, as shown in Figure 10. Data memory locations from 0x3C00 to the end of data memory at 0x3FFF are reserved. Control and status registers for the system, timer, wait-state configuration, and serial port operations are located in this region of memory.

### ADSP-2105/ADSP-2115

For the ADSP-2105 and ADSP-2115, on-chip data memory RAM resides in the 512 words beginning at address 0x3800, also shown in Figure 10. Data memory locations from 0x3A00 to the end of data memory at 0x3FFF are reserved. Control and status registers for the system, timer, wait-state configuration, and serial port operations are located in this region of memory.

Figure 10. Data Memory Map (All Processors)

### **All Processors**

The remaining 14K of data memory is located off-chip. This external data memory is divided into five zones, each associated with its own wait-state generator. This allows slower peripherals to be memory-mapped into data memory for which wait states are specified. By mapping peripherals into different zones, you can accommodate peripherals with different wait-state requirements. All zones default to seven wait states after RESET.

#### **Boot Memory Interface**

On the ADSP-2101, ADSP-2103, and ADSP-2111, boot memory is an external 64K by 8 space, divided into eight separate 8K by 8 pages. On the ADSP-2105 and ADSP-2115, boot memory is a 32K by 8 space, divided into eight separate 4K by 8 pages. The 8-bit bytes are automatically packed into 24-bit instruction words by each processor, for loading into onchip program memory.

Three bits in the processors' System Control Register select which page is loaded by the boot memory interface. Another bit in the System Control Register allows the forcing of a boot loading sequence under software control. Boot loading from Page 0 after  $\overrightarrow{\text{RESET}}$  is initiated automatically if MMAP = 0.

The boot memory interface can generate zero to seven wait states; it defaults to three wait states after **RESET**. This allows the ADSP-21xx to boot from a single low cost EPROM such as a 27C256. Program memory is booted one byte at a time and converted to 24-bit program memory words.

The  $\overline{BMS}$  and  $\overline{RD}$  signals are used to select and to strobe the boot memory interface. Only 8-bit data is read over the data bus, on pins D8-D15. To accommodate up to eight pages of boot memory, the two MSBs of the data bus are used in the boot memory interface as the two MSBs of the boot memory address: D23, D22, and A13 supply the boot page number.

The ADSP-2100 Family Assembler and Linker allow the creation of programs and data structures requiring multiple boot pages during execution.

The  $\overline{BR}$  signal is recognized during the booting sequence. The bus is granted after loading the current byte is completed.  $\overline{BR}$  during booting may be used to implement booting under control of a host processor.

### **Bus Interface**

The ADSP-21xx processors can relinquish control of their data and address buses to an external device. When the external device requires control of the buses, it asserts the bus request signal ( $\overline{BR}$ ). If the ADSP-21xx is not performing an external memory access, it responds to the active  $\overline{BR}$  input in the next cycle by:

- Three-stating the data and address buses and the PMS, DMS, BMS, RD, WR output drivers,

- Asserting the bus grant  $(\overline{BG})$  signal,

- and halting program execution.

If the Go mode is set, however, the ADSP-21xx will not halt program execution until it encounters an instruction that requires an external memory access.

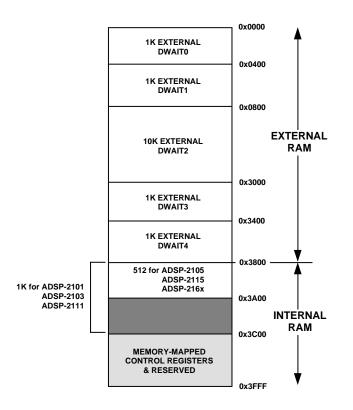

# SPECIFICATIONS (ADSP-2101/2105/2115/2161/2163)

SUPPLY CURRENT & POWER (ADSP-2101/2105/2115/2161/2163)

| Para            | meter                                 | Test Conditions                                 | Min | Max | Unit |

|-----------------|---------------------------------------|-------------------------------------------------|-----|-----|------|

| I <sub>DD</sub> | Supply Current (Dynamic) <sup>1</sup> | @ $V_{DD}$ = max, $t_{CK}$ = 40 ns <sup>2</sup> |     | 38  | mA   |

|                 |                                       | @ $V_{DD} = max$ , $t_{CK} = 50 ns^2$           |     | 31  | mA   |

|                 |                                       | @ $V_{DD} = max$ , $t_{CK} = 72.3 ns^2$         |     | 24  | mA   |

| I <sub>DD</sub> | Supply Current (Idle) <sup>1, 3</sup> | @ $V_{DD} = max$ , $t_{CK} = 40 \text{ ns}^4$   |     | 12  | mA   |

|                 |                                       | @ $V_{DD} = max$ , $t_{CK} = 50 ns$             |     | 11  | mA   |

|                 |                                       | @ $V_{DD}$ = max, $t_{CK}$ = 72.3 ns            |     | 10  | mA   |

NOTES

<sup>1</sup>Current reflects device operating with no output loads.

$^{2}V_{IN} = 0.4 \text{ V} \text{ and } 2.4 \text{ V}.$ <sup>3</sup>Idle refers to ADSP-21xx state of operation during execution of IDLE instruction. Deasserted pins are driven to either V<sub>DD</sub> or GND.

<sup>4</sup>ADSP-2105 is not available in a 25 MHz speed grade.

For typical supply current (internal power dissipation) figures, see Figure 11.

1 POWER REFLECTS DEVICE OPERATING WITH NO OUTPUT LOADS.

2 IDLE REFERS TO ADSP-21xx OPERATION DURING EXECUTION OF IDLE INSTRUCTION.

DEASSERTED PINS ARE DRIVEN TO EITHER  $V_{DD}$  OR GND. 3 MAXIMUM POWER DISSIPATION AT  $V_{DD}$  = 5.5V DURING EXECUTION OF *IDLE n* INSTRUCTION.

Figure 11. ADSP-2101 Power (Typical) vs. Frequency

### SPECIFICATIONS (ADSP-2101/2105/2115/2161/2163)

### **TEST CONDITIONS**

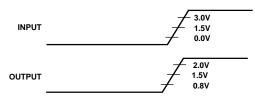

Figure 14 shows voltage reference levels for ac measurements.

Figure 14. Voltage Reference Levels for AC Measurements (Except Output Enable/Disable)

### **Output Disable Time**

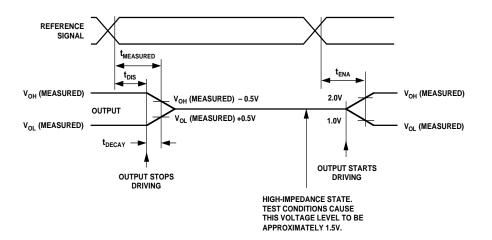

Output pins are considered to be disabled when they have stopped driving and started a transition from the measured output high or low voltage to a high impedance state. The output disable time ( $t_{DIS}$ ) is the difference of  $t_{MEASURED}$  and  $t_{DECAY}$ , as shown in Figure 15. The time  $t_{MEASURED}$  is the interval from when a reference signal reaches a high or low voltage level to when the output voltages have changed by 0.5 V from the measured output high or low voltage.

The decay time,  $t_{DECAY}$ , is dependent on the capacitative load,  $C_L$ , and the current load,  $i_L$ , on the output pin. It can be approximated by the following equation:

$$t_{DECAY} = \frac{C_L \times 0.5 V}{i_L}$$

from which

$$t_{DIS} = t_{MEASURED} - t_{DECAY}$$

is calculated. If multiple pins (such as the data bus) are disabled, the measurement value is that of the last pin to stop driving.

### **Output Enable Time**

Output pins are considered to be enabled when they have made a transition from a high-impedance state to when they start driving. The output enable time ( $t_{ENA}$ ) is the interval from when a reference signal reaches a high or low voltage level to when the output has reached a specified high or low trip point, as shown in Figure 15. If multiple pins (such as the data bus) are enabled, the measurement value is that of the first pin to start driving.

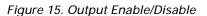

Figure 16. Equivalent Device Loading for AC Measurements (Except Output Enable/Disable)

### SPECIFICATIONS (ADSP-2111) POWER DISSIPATION EXAMPLE

To determine total power dissipation in a specific application, the following equation should be applied for each output:

$C \times V_{DD}^2 \times f$

C =load capacitance, f =output switching frequency.

### **Example:**

In an ADSP-2111 application where external data memory is used and no other outputs are active, power dissipation is calculated as follows:

Assumptions:

- External data memory is accessed every cycle with 50% of the address pins switching.

- · External data memory writes occur every other cycle with 50% of the data pins switching.

- Each address and data pin has a 10 pF total load at the pin.

- The application operates at  $V_{DD} = 5.0$  V and  $t_{CK} = 50$  ns. Total Power Dissipation =  $P_{INT} + (C \times V_{DD}^2 \times f)$

- $P_{INT}$  = internal power dissipation (from Figure 17).

$(C \times V_{DD}^2 \times f)$  is calculated for each output:

| Output       | # of<br>Pins | ×C                     | $	imes V_{DD}^2$       | ×f                                        |

|--------------|--------------|------------------------|------------------------|-------------------------------------------|

| Address, DMS | 8            | × 10 pF                | $	imes 5^2  { m V}$    | $\times$ 20 MHz = 40.0 mW                 |

| Data, WR     | 9            | $\times 10 \text{ pF}$ | $	imes 5^2  m V$       | $\times 10 \text{ MHz} = 22.5 \text{ mW}$ |

| RD           | 1            | $\times 10 \text{ pF}$ | $\times 5^2 \text{ V}$ | $\times 10 \text{ MHz} = 2.5 \text{ mW}$  |

| CLKOUT       | 1            | × 10 pF                | $	imes 5^2  m V$       | $\times$ 20 MHz = 5.0 mW                  |

Total power dissipation for this example =  $P_{INT}$  + 70.0 mW.

### **ENVIRONMENTAL CONDITIONS**

**Ambient Temperature Rating:**

- $$\begin{split} T_{AMB} &= T_{CASE} (PD \times \theta_{CA}) \\ T_{CASE} &= Case \ Temperature \ in \ ^{\circ}C \end{split}$$

- PD = Power Dissipation in W

- $\theta_{CA}$  = Thermal Resistance (Case-to-Ambient)

- $\theta_{JA}$  = Thermal Resistance (Junction-to-Ambient)

- $\theta_{JC}$  = Thermal Resistance (Junction-to-Case)

| Package | $\theta_{JA}$ | θ <sub>JC</sub> | $\theta_{CA}$ |

|---------|---------------|-----------------|---------------|

| PGA     | 35°C/W        | 18°C/W          | 17°C/W        |

| PQFP    | 42°C/W        | 18°C/W          | 23°C/W        |

### **CAPACITIVE LOADING**

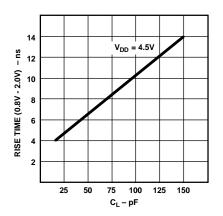

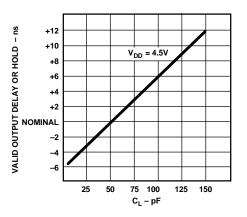

Figures 18 and 19 show capacitive loading characteristics for the ADSP-2111.

Figure 18. Typical Output Rise Time vs. Load Capacitance, C<sub>1</sub> (at Maximum Ambient Operating Temperature)

Figure 19. Typical Output Valid Delay or Hold vs. Load Capacitance, C<sub>L</sub> (at Maximum Ambient Operating Temperature)

70.0 mW

# SPECIFICATIONS (ADSP-2103/2162/2164)

### POWER DISSIPATION EXAMPLE

To determine total power dissipation in a specific application, the following equation should be applied for each output:

$C \times V_{DD}^2 \times f$

C = load capacitance, f = output switching frequency.

### **Example:**

In an ADSP-2103 application where external data memory is used and no other outputs are active, power dissipation is calculated as follows:

Assumptions:

- External data memory is accessed every cycle with 50% of the address pins switching.

- External data memory writes occur every other cycle with 50% of the data pins switching.

- Each address and data pin has a 10 pF total load at the pin.

- The application operates at  $V_{DD} = 3.3$  V and  $t_{CK} = 100$  ns. Total Power Dissipation =  $P_{INT} + (C \times V_{DD}^2 \times f)$

$P_{INT}$  = internal power dissipation (from Figure 23).

$(C \times V_{DD}^2 \times f)$  is calculated for each output:

| Output       | # of<br>Pins | ×C                       | $	imes V_{DD}^2$ | ×f                                                                                 |

|--------------|--------------|--------------------------|------------------|------------------------------------------------------------------------------------|

| Address, DMS | 8            | × 10 pF                  | $	imes 3.3^2$ V  | × 10 MHz = 8.71 mW<br>× 5 MHz = 4.90 mW<br>× 5 MHz = 0.55 mW<br>× 10 MHz = 1.09 mW |

| Data, WR     | 9            | $\times 10  \mathrm{pF}$ | $	imes 3.3^2$ V  | $\times 5 \text{ MHz} = 4.90 \text{ mW}$                                           |

| RD           | 1            | $\times 10  \mathrm{pF}$ | $	imes 3.3^2$ V  | $\times 5 \text{ MHz} = 0.55 \text{ mW}$                                           |

| CLKOUT       | 1            | × 10 pF                  | $	imes 3.3^2$ V  | $\times$ 10 MHz = 1.09 mW                                                          |

|              |              |                          |                  | 15.25 mW                                                                           |

Total power dissipation for this example =  $P_{INT}$  + 15.25 mW.

### **ENVIRONMENTAL CONDITIONS**

**Ambient Temperature Rating:**

$$\begin{split} T_{AMB} &= T_{CASE} - (PD \times \theta_{CA}) \\ T_{CASE} &= Case \ Temperature \ in \ ^{\circ}C \end{split}$$

- PD = Power Dissipation in W

- $\theta_{CA}$  = Thermal Resistance (Case-to-Ambient)

$\theta_{JA}$  = Thermal Resistance (Junction-to-Ambient)

$\theta_{IC}$  = Thermal Resistance (Junction-to-Case)

| Package | $\theta_{JA}$ | θ <sub>JC</sub> | θ <sub>CA</sub> |

|---------|---------------|-----------------|-----------------|

| PGA     | 27°C/W        | 16°C/W          | 11°C/W          |

| PQFP    | 60°C/W        | 18°C/W          | 42°C/W          |

### **CAPACITIVE LOADING**

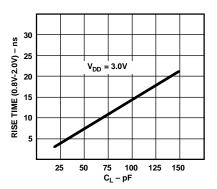

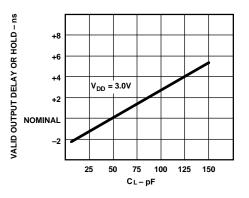

Figures 24 and 25 show capacitive loading characteristics for the ADSP-2103, ADSP-2162, and ADSP-2164.

Figure 24. Typical Output Rise Time vs. Load Capacitance, C (at Maximum Ambient Operating Temperature)

Figure 25. Typical Output Valid Delay or Hold vs. Load Capacitance, C<sub>1</sub> (at Maximum Ambient Operating Temperature)

## TIMING PARAMETERS (ADSP-2101/2105/2111/2115/2161/2163)

### GENERAL NOTES

Use the exact timing information given. Do not attempt to derive parameters from the addition or subtraction of others. While addition or subtraction would yield meaningful results for an individual device, the values given in this data sheet reflect statistical variations and worst cases. Consequently, you cannot meaningfully add parameters to derive longer times.

### TIMING NOTES

*Switching characteristics* specify how the processor changes its signals. You have no control over this timing—circuitry external to the processor must be designed for compatibility with these signal characteristics. Switching characteristics tell you what the processor will do in a given circumstance. You can also use

switching characteristics to ensure that any timing requirement of a device connected to the processor (such as memory) is satisfied.

*Timing requirements* apply to signals that are controlled by circuitry external to the processor, such as the data input for a read operation. Timing requirements guarantee that the processor operates correctly with other devices.

### MEMORY REQUIREMENTS

The table below shows common memory device specifications and the corresponding ADSP-21xx timing parameters, for your convenience.

| Memory                                                                                                                                  | ADSP-21xx                                                                                                | Timing                                                                                                                                                                                                                                                                                                                                                                |

|-----------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Device                                                                                                                                  | Timing                                                                                                   | Parameter                                                                                                                                                                                                                                                                                                                                                             |

| Specification                                                                                                                           | Parameter                                                                                                | Definition                                                                                                                                                                                                                                                                                                                                                            |

| Address Setup to Write StartAddress Setup to Write EndAddress Hold TimeData Setup TimeData Hold TimeOE to Data ValidAddress Access Time | $t_{ m ASW}$<br>$t_{ m AW}$<br>$t_{ m WRA}$<br>$t_{ m DW}$<br>$t_{ m DH}$<br>$t_{ m RDD}$<br>$t_{ m AA}$ | A0–A13, <u>DMS</u> , <u>PMS</u> Setup before <u>WR</u> Low<br>A0–A13, <u>DMS</u> , <u>PMS</u> Setup before <u>WR</u> Deasserted<br>A0–A13, <u>DMS</u> , <u>PMS</u> Hold after <u>WR</u> Deasserted<br>Data Setup before <u>WR</u> High<br>Data Hold after <u>WR</u> High<br><u>RD</u> Low to Data Valid<br>A0–A13, <u>DMS</u> , <u>PMS</u> , <u>BMS</u> to Data Valid |

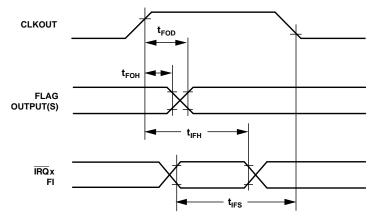

### TIMING PARAMETERS (ADSP-2101/2105/2111/2115/2161/2163) INTERRUPTS & FLAGS

| Parai            | neter                                            | 13 MI<br>Min | Hz<br>Max | 13.824<br>Min | 4 MHz<br>Max | 16.67<br>Min |    | 20 M<br>Min | Hz<br>Max | 25 M<br>Min | Hz<br>Max | Frequency<br>Dependency<br>Min Max | Unit |

|------------------|--------------------------------------------------|--------------|-----------|---------------|--------------|--------------|----|-------------|-----------|-------------|-----------|------------------------------------|------|

| Timin            | g Requirement:                                   |              |           |               |              |              |    |             |           |             |           |                                    |      |

| t <sub>IFS</sub> | $\overline{IRQx}^1$ or FI Setup before           | 34.2         |           | 33.1          |              | 30           |    | 27.5        |           | 25          |           | $0.25t_{CK} + 15^4$                | ns   |

|                  | CLKOUT Low <sup>2, 3</sup>                       |              |           |               |              |              |    |             |           |             |           |                                    |      |

| $t_{IFS}$        | IRQx <sup>1</sup> or FI Setup before             | 37.2         |           | 36.1          |              | 33           |    | 30.5        |           | 28          |           | $0.25t_{CK} + 18^4$                | ns   |

|                  | CLKOUT Low (ADSP-2111) <sup>2, 3</sup>           |              |           |               |              |              |    |             |           |             |           |                                    |      |

| $t_{\rm IFH}$    | <b>IRQx</b> <sup>1</sup> or FI Hold after CLKOUT | 19.2         |           | 18.1          |              | 15           |    | 12.5        |           | 10          |           | 0.25t <sub>CK</sub>                | ns   |

|                  | High <sup>2, 3</sup>                             |              |           |               |              |              |    |             |           |             |           |                                    |      |

| Switch           | ning Characteristic:                             |              |           |               |              |              |    |             |           |             |           |                                    |      |

| t <sub>FOH</sub> | FO Hold after CLKOUT High <sup>5</sup>           | 0            |           | 0             |              | 0            |    | 0           |           | 0           |           | 0                                  | ns   |

| t <sub>FOD</sub> | FO Delay from CLKOUT High                        |              | 15        |               | 15           |              | 15 |             | 15        |             | 12        |                                    | ns   |

NOTES

<sup>1</sup>IRQx=IRQ0, IRQ1, and IRQ2.

<sup>2</sup>If IROx and FI inputs meet t<sub>IFS</sub> and t<sub>IFH</sub> setup/hold requirements, they will be recognized during the current clock cycle; otherwise they will be recognized during the following cycle. (Refer to the "Interrupt Controller" section in Chapter 3, Program Control, of the *ADSP-2100 Family User's Manual* for further information on interrupt servicing.)

<sup>3</sup>Edge-sensitive interrupts require pulse widths greater than 10 ns. Level-sensitive interrupts must be held low until serviced.

$^{4}$ t<sub>IFS</sub> (min) = 0.25t<sub>CK</sub> + 20 ns for ADSP-2101TG-50, ADSP-2101TG/883B-50, ADSP-2111TG-52, and ADSP-2111TG/883B-52 (Extended Temperature Range devices).

<sup>5</sup>t<sub>FOH</sub> (min) = -5 ns for ADSP-2111TG-52 and ADSP-2111TG/883B-52 (Extended Temperature Range devices).

Figure 30. Interrupts & Flags

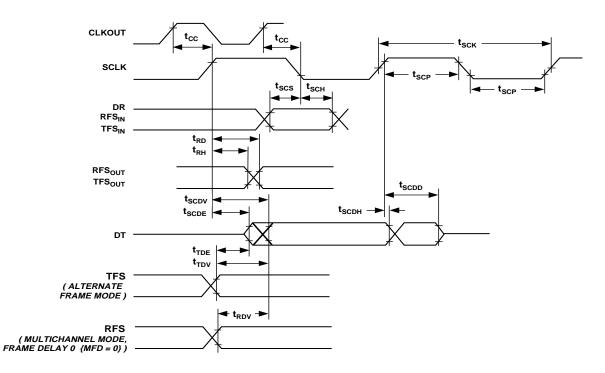

# TIMING PARAMETERS (ADSP-2101/2105/2111/2115/2161/2163) serial ports

|                                                     |     | 12.5 MHz |      | 13.0 MHz |      | 4 MHz* | Frequency<br>Dependency |                     |      |

|-----------------------------------------------------|-----|----------|------|----------|------|--------|-------------------------|---------------------|------|

| Parameter                                           | Min | Max      | Min  | Max      | Min  | Max    | Min                     | Max                 | Unit |

| Timing Requirement:                                 |     |          |      |          |      |        |                         |                     |      |

| t <sub>SCK</sub> SCLK Period                        | 80  |          | 76.9 |          | 72.3 |        |                         |                     | ns   |

| t <sub>SCS</sub> DR/TFS/RFS Setup before SCLK Low   | 8   |          | 8    |          | 8    |        |                         |                     | ns   |

| SCH DR/TFS/RFS Hold after SCLK Low                  | 10  |          | 10   |          | 10   |        |                         |                     | ns   |

| SCP SCLK <sub>IN</sub> Width                        | 30  |          | 28   |          | 28   |        |                         |                     | ns   |

| Switching Characteristic:                           |     |          |      |          |      |        |                         |                     |      |

| CC CLKOUT High to SCLK <sub>OUT</sub>               | 20  | 35       | 19.2 | 34.2     | 18.1 | 33.1   | 0.25t <sub>CK</sub>     | $0.25t_{CK} + 15ns$ | ;    |

| SCDE SCLK High to DT Enable                         | 0   |          | 0    |          | 0    |        |                         |                     | ns   |

| SCDV SCLK High to DT Valid                          |     | 20       |      | 20       |      | 20     |                         |                     | ns   |

| RH TFS/RFS <sub>OUT</sub> Hold after SCLK High      | 0   |          | 0    |          | 0    |        |                         |                     | ns   |

| TFS/RFS <sub>OUT</sub> Delay from SCLK High         |     | 20       |      | 20       |      | 20     |                         |                     | ns   |

| SCDH DT Hold after SCLK High                        | 0   |          | 0    |          | 0    |        |                         |                     | ns   |

| TTE TFS (Alt) to DT Enable                          | 0   |          | 0    |          | 0    |        |                         |                     | ns   |

| TFS (Alt) to DT Valid                               |     | 18       |      | 18       |      | 18     |                         |                     | ns   |

| SCDD SCLK High to DT Disable                        |     | 25       |      | 25       |      | 25     |                         |                     | ns   |

| RFS (Multichannel, Frame Delay Zero)<br>to DT Valid |     | 20       |      | 20       |      | 20     |                         |                     | ns   |

\*Maximum serial port operating frequency is 13.824 MHz for all processor speed grades except the 12.5 MHz ADSP-2101 and 13.0 MHz ADSP-2111.

Figure 34. Serial Ports

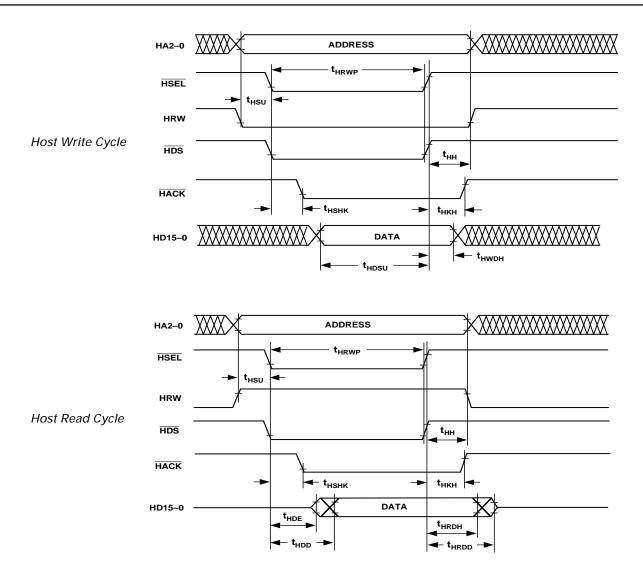

# TIMING PARAMETERS (ADSP-2111)

### HOST INTERFACE PORT

Separate Data & Address (HMD1 = 0) Read Strobe & Write Strobe (HMD0 = 0)

| Parameter                                                                  | 13.0<br>Min | MHz<br>Max | 16.67<br>Min | 7 MHz<br>Max | 20 M<br>Min |    | No Frequency<br>Dependency | Unit |

|----------------------------------------------------------------------------|-------------|------------|--------------|--------------|-------------|----|----------------------------|------|

| Timing Requirement:                                                        |             |            |              |              |             |    |                            |      |

| t <sub>HSU</sub> HA2-0 Setup before Start of Write or Read <sup>1, 2</sup> | 8           |            | 8            |              | 8           |    |                            | ns   |

| t <sub>HDSU</sub> Data Setup before End of Write <sup>3</sup>              | 8           |            | 8            |              | 8           |    |                            | ns   |

| t <sub>HWDH</sub> Data Hold after End of Write <sup>3</sup>                | 3           |            | 3            |              | 3           |    |                            | ns   |

| $t_{\rm HH}$ HA2-0 Hold after End of Write or Read <sup>3, 4</sup>         | 3           |            | 3            |              | 3           |    |                            | ns   |

| t <sub>HRWP</sub> Read or Write Pulse Width <sup>5</sup>                   | 30          |            | 30           |              | 30          |    |                            | ns   |

| Switching Characteristic:                                                  |             |            |              |              |             |    |                            |      |

| t <sub>HSHK</sub> HACK Low after Start of Write or Read <sup>1, 2</sup>    | 0           | 20         | 0            | 20           | 0           | 20 |                            | ns   |

| $t_{\rm HKH}$ HACK Hold after End of Write or Read <sup>3, 4</sup>         | 0           | 20         | 0            | 20           | 0           | 20 |                            | ns   |

| t <sub>HDE</sub> Data Enabled after Start of Read <sup>2</sup>             | 0           |            | 0            |              | 0           |    |                            | ns   |

| t <sub>HDD</sub> Data Valid after Start of Read <sup>2</sup>               |             | 23         |              | 23           |             | 23 |                            | ns   |

| t <sub>HRDH</sub> Data Hold after End of Read <sup>4</sup>                 | 0           |            | 0            |              | 0           |    |                            | ns   |

| t <sub>HRDD</sub> Data Disabled after End of Read <sup>4</sup>             |             | 10         |              | 10           |             | 10 |                            | ns   |

NOTES <sup>1</sup>Start of Write = <u>HWR</u> Low and <u>HSEL</u> Low. <sup>2</sup>Start of Read = <u>HRD</u> Low and <u>HSEL</u> Low. <sup>3</sup>End of Write = <u>HWR</u> High or <u>HSEL</u> High. <sup>4</sup>End of Read = <u>HRD</u> High or <u>HSEL</u> High. <sup>5</sup>Read Pulse Width = <u>HRD</u> Low and <u>HSEL</u> Low, Write Pulse Width = <u>HWR</u> Low and <u>HSEL</u> Low.

Figure 36. Host Interface Port (HMD1 = 0, HMD0 = 1)

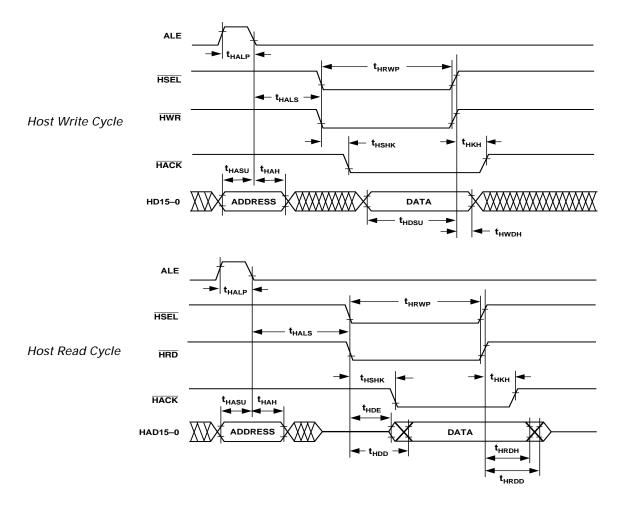

# TIMING PARAMETERS (ADSP-2111)

### HOST INTERFACE PORT

Multiplexed Data & Address (HMD1 = 1) Read Strobe & Write Strobe (HMD0 = 0)

| Parameter                                                               |    | MHz<br>Max |    | ' MHz<br>Max | 20 M<br>Min | Hz<br>Max | No Frequency<br>Dependency | Unit |

|-------------------------------------------------------------------------|----|------------|----|--------------|-------------|-----------|----------------------------|------|

| Timing Requirement:                                                     |    |            |    |              |             |           |                            |      |

| t <sub>HALP</sub> ALE Pulse Width                                       | 15 |            | 15 |              | 15          |           |                            | ns   |

| t <sub>HASU</sub> HAD15-0 Address Setup before ALE Low                  | 5  |            | 5  |              | 5           |           |                            | ns   |

| t <sub>HAH</sub> HAD15-0 Address Hold after ALE Low                     | 2  |            | 2  |              | 2           |           |                            | ns   |

| t <sub>HALS</sub> Start of Write or Read after ALE Low <sup>1, 2</sup>  | 15 |            | 15 |              | 15          |           |                            | ns   |

| t <sub>HDSU</sub> HAD15-0 Data Setup before End of Write <sup>3</sup>   | 8  |            | 8  |              | 8           |           |                            | ns   |

| t <sub>HWDH</sub> HAD15-0 Data Hold after End of Write <sup>3</sup>     | 3  |            | 3  |              | 3           |           |                            | ns   |

| t <sub>HRWP</sub> Read or Write Pulse Width <sup>5</sup>                | 30 |            | 30 |              | 30          |           |                            | ns   |

| Switching Characteristic:                                               |    |            |    |              |             |           |                            |      |

| t <sub>HSHK</sub> HACK Low after Start of Write or Read <sup>1, 2</sup> | 0  | 20         | 0  | 20           | 0           | 20        |                            | ns   |

| $t_{HKH}$ HACK Hold after End of Write or Read <sup>3, 4</sup>          | 0  | 20         | 0  | 20           | 0           | 20        |                            | ns   |

| t <sub>HDE</sub> HAD15-0 Data Enabled after Start of Read <sup>2</sup>  | 0  |            | 0  |              | 0           |           |                            | ns   |

| t <sub>HDD</sub> HAD15-0 Data Valid after Start of Read <sup>2</sup>    |    | 23         |    | 23           |             | 23        |                            | ns   |

| t <sub>HRDH</sub> HAD15-0 Data Hold after End of Read <sup>4</sup>      | 0  |            | 0  |              | 0           |           |                            | ns   |

| t <sub>HRDD</sub> HAD15-0 Data Disabled after End of Read <sup>4</sup>  |    | 10         |    | 10           |             | 10        |                            | ns   |

NOTES

NOTES <sup>1</sup>Start of Write = <u>HWR</u> Low and <u>HSEL</u> Low. <sup>2</sup>Start of Read = <u>HRD</u> Low and <u>HSEL</u> Low. <sup>3</sup>End of Write = <u>HWR</u> High or <u>HSEL</u> High. <sup>4</sup>End of Read = <u>HRD</u> High or <u>HSEL</u> High. <sup>5</sup>Read Pulse Width = <u>HRD</u> Low and <u>HSEL</u> Low, Write Pulse Width = <u>HWR</u> Low and <u>HSEL</u> Low.

Figure 37. Host Interface Port (HMD1 = 1, HMD0 = 0)

### TIMING PARAMETERS (ADSP-2103/2162/2164) CLOCK SIGNALS & RESET

| Parameter         |                           | 10.24 N<br>Min | /IHz<br>Max | Frequency<br>Dependency<br>Min Max   |  | Unit |  |

|-------------------|---------------------------|----------------|-------------|--------------------------------------|--|------|--|

| Timing            | Requirement:              |                |             |                                      |  |      |  |

| t <sub>CK</sub>   | CLKIN Period              | 97.6           | 150         |                                      |  | ns   |  |

| t <sub>CKL</sub>  | CLKIN Width Low           | 20             |             |                                      |  | ns   |  |

| t <sub>CKH</sub>  | CLKIN Width High          | 20             |             |                                      |  | ns   |  |

| t <sub>RSP</sub>  | <b>RESET</b> Width Low    | 488            |             | $5t_{CK}^{1}$                        |  | ns   |  |

| Switchi           | ng Characteristic:        |                |             |                                      |  |      |  |

| t <sub>CPL</sub>  | CLKOUT Width Low          | 38.8           |             | 0.5t <sub>CK</sub> – 10              |  | ns   |  |

| t <sub>CPH</sub>  | CLKOUT Width High         | 38.8           |             | $0.5t_{CK} - 10$<br>$0.5t_{CK} - 10$ |  | ns   |  |

| t <sub>CKOH</sub> | CLKIN High to CLKOUT High | 0              | 20          |                                      |  | ns   |  |

NOTES

<sup>1</sup>Applies after powerup sequence is complete. Internal phase lock loop requires no more than 2000 CLKIN cycles assuming stable CLKIN (not including crystal oscillator startup time).

Figure 39. Clock Signals

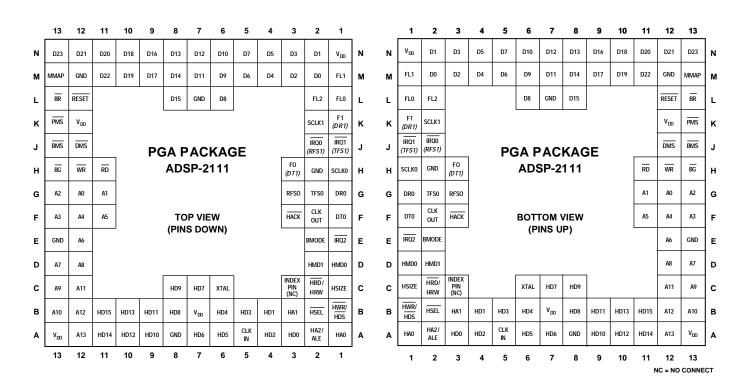

### **PIN CONFIGURATIONS**

100-Pin PGA

| PGA<br>Number | Pin<br>Name          | PGA<br>Number | Pin<br>Name     |

|---------------|----------------------|---------------|-----------------|

| N13           | D23                  | B13           | A10             |

| N12           | D21                  | A13           | V <sub>DD</sub> |

| M13           | MMAP                 | A12           | A13             |

| M12           | GND                  | B12           | A12             |

| L13           | BR                   | A11           | HD14            |

| L12           | RESET                | B11           | HD15            |

| K13           | PMS                  | A10           | HD12            |

| K12           | $\underline{V_{DD}}$ | B10           | HD13            |

| J13           | BMS                  | A9            | HD10            |

| J12           | DMS                  | B9            | HD11            |

| H13           | BG                   | A8            | GND             |

| H12           | WR                   | B8            | HD8             |

| H11           | RD                   | C8            | HD9             |

| G13           | A2                   | A7            | HD6             |

| G12           | A0                   | B7            | V <sub>DD</sub> |

| G11           | A1                   | C7            | HD7             |

| F13           | A3                   | A6            | HD5             |

| F12           | A4                   | B6            | HD4             |

| F11           | A5                   | C6            | XTAL            |

| E13           | GND                  | A5            | CLKIN           |

| E12           | A6                   | B5            | HD3             |

| D13           | A7                   | A4            | HD2             |

| D12           | A8                   | B4            | HD1             |

| C13           | A9                   | A3            | HD0             |

| C12           | A11                  | B3            | HA1             |

| PGA<br>Number | Pin<br>Name     |   | PGA<br>Number | Pin<br>Name     |

|---------------|-----------------|---|---------------|-----------------|

| C3            | Index (NC)      |   | L2            | FL2             |

| A2            | HA2/ALE         |   | M1            | FL1             |

| A1            | HA0             |   | N1            | V <sub>DD</sub> |

| B1            | HWR/HDS         |   | N2            | DI              |

| B2            | HSEL            |   | M2            | D0              |

| C1            | HSIZE           |   | N3            | D3              |

| C2            | HRD/HRW         |   | M3            | D2              |

| D1            | HMD0            |   | N4            | D5              |

| D2            | HMD1            |   | M4            | D4              |

| E1            | IRQ2            |   | N5            | D7              |

| E2            | BMODE           |   | M5            | D6              |

| F1            | DT0             |   | N6            | D10             |

| F2            | CLKOUT          |   | M6            | D9              |

| F3            | HACK            |   | L6            | D8              |

| G1            | DR0             |   | N7            | D12             |

| G2            | TFS0            |   | M7            | D11             |

| G3            | RFS0            |   | L7            | GND             |

| H1            | SCLK0           |   | N8            | D13             |

| H2            | GND             |   | M8            | D14             |

| H3            | FO <i>(DT1)</i> |   | L8            | D15             |

| J1            | IRQ1 (TFS1)     |   | N9            | D16             |

| J2            | IRQ0 (RFS1)     |   | M9            | D17             |

| K1            | FI <i>(DR1)</i> |   | N10           | D18             |

| K2            | SCLK1           |   | M10           | D19             |

| L1            | FL0             |   | N11           | D20             |

| L             | 1               | 1 | M11           | D22             |

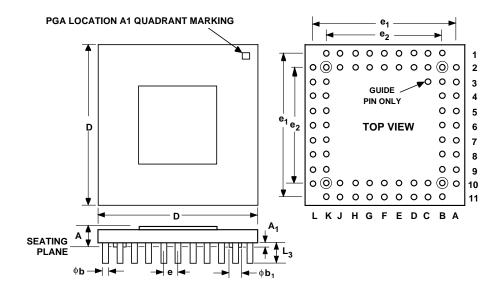

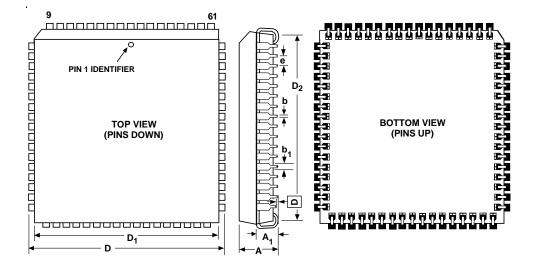

### OUTLINE DIMENSIONS ADSP-2101 68-Pin Grid Array (PGA)

|                       | INCHES |       |       | MILLIMETERS |      |       |

|-----------------------|--------|-------|-------|-------------|------|-------|

| SYMBOL                | MIN    | ТҮР   | MAX   | MIN         | ТҮР  | MAX   |

| Α                     | 0.123  |       | 0.164 | 3.12        |      | 4.17  |

| <b>A</b> <sub>1</sub> |        | 0.50  |       |             | 1.27 |       |

| φb                    | 0.016  | 0.018 | 0.020 |             | 0.46 |       |

| φ <b>b</b> 1          |        | 0.050 |       |             | 1.27 |       |

| D                     | 1.086  |       | 1.110 | 27.58       |      | 28.19 |

| e <sub>1</sub>        | 0.988  |       | 1.012 | 25.10       |      | 25.70 |

| e <sub>2</sub>        | 0.788  |       | 0.812 | 20.02       |      | 20.62 |

| е                     |        | 0.100 |       |             | 2.54 |       |

| L <sub>3</sub>        |        | 0.180 |       |             | 4.57 |       |

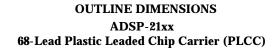

|                       | INCHES |       |       | MILLIMETERS |       |       |  |  |

|-----------------------|--------|-------|-------|-------------|-------|-------|--|--|

| SYMBOL                | MIN    | ТҮР   | MAX   | MIN         | ТҮР   | MAX   |  |  |

| А                     | 0.169  | 0.172 | 0.175 | 4.29        | 4.37  | 4.45  |  |  |

| <b>A</b> <sub>1</sub> |        | 0.104 |       |             | 2.64  |       |  |  |

| b                     | 0.017  | 0.018 | 0.019 | 0.43        | 0.46  | 0.48  |  |  |

| b <sub>1</sub>        | 0.027  | 0.028 | 0.029 | 0.69        | 0.71  | 0.74  |  |  |

| D                     | 0.985  | 0.990 | 0.995 | 25.02       | 25.15 | 25.27 |  |  |

| <b>D</b> <sub>1</sub> | 0.950  | 0.952 | 0.954 | 24.13       | 24.18 | 24.23 |  |  |

| <b>D</b> <sub>2</sub> | 0.895  | 0.910 | 0.925 | 22.73       | 23.11 | 23.50 |  |  |

| е                     |        | 0.050 |       |             | 1.27  |       |  |  |

| ٥                     |        |       | 0.004 |             |       | 0.10  |  |  |

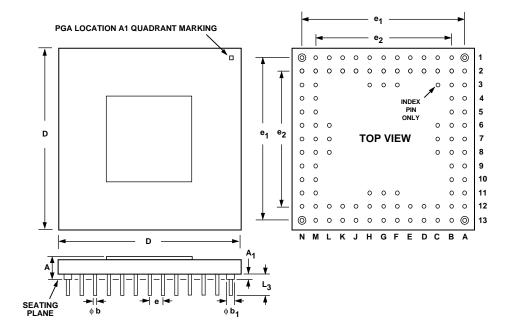

### **OUTLINE DIMENSIONS**

ADSP-2111 100-Pin Grid Array (PGA)

|                       | INCHES |       |       | MILLIMETERS |       |       |

|-----------------------|--------|-------|-------|-------------|-------|-------|

| SYMBOL                | MIN    | ТҮР   | MAX   | MIN         | ТҮР   | MAX   |

| А                     | 0.123  |       | 0.169 | 3.12        |       | 4.29  |

| <b>A</b> <sub>1</sub> |        | 0.050 |       |             | 1.27  |       |

| φb                    | 0.016  | 0.018 | 0.020 | 0.41        | 0.46  | 0.51  |

| φ <b>b</b> 1          |        | 0.050 |       |             | 1.27  |       |

| D                     | 1.308  | 1.32  | 1.342 | 33.22       | 33.53 | 34.09 |

| e <sub>1</sub>        | 1.188  | 1.20  | 1.212 | 30.18       | 30.48 | 30.78 |

| e <sub>2</sub>        | 0.988  | 1.00  | 1.012 | 25.10       | 25.4  | 25.70 |

| е                     |        | 0.100 |       |             | 2.54  |       |

| L <sub>3</sub>        |        | 0.180 |       |             | 4.57  |       |