Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                                               |

|----------------------------|--------------------------------------------------------------------------------------|

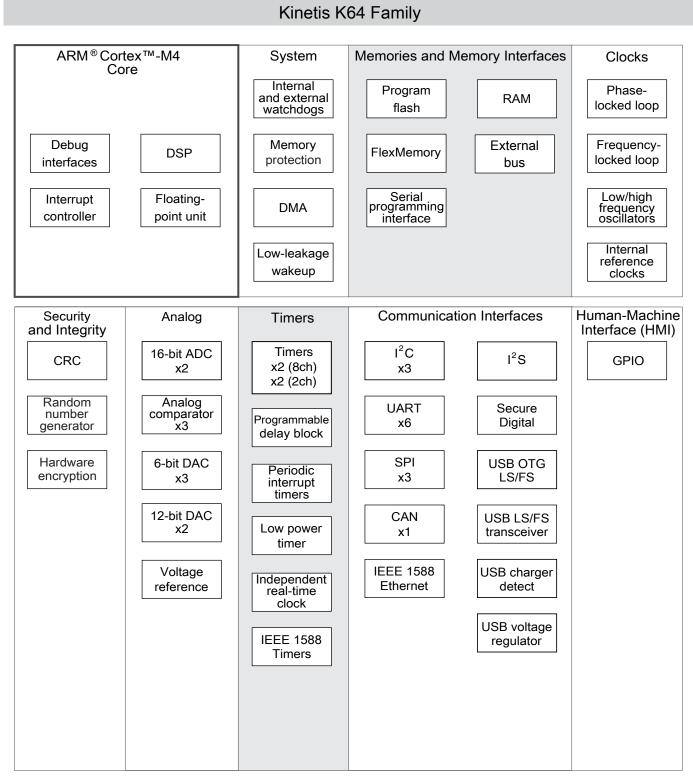

| Core Processor             | ARM® Cortex®-M4                                                                      |

| Core Size                  | 32-Bit Single-Core                                                                   |

| Speed                      | 120MHz                                                                               |

| Connectivity               | CANbus, EBI/EMI, Ethernet, I <sup>2</sup> C, IrDA, SD, SPI, UART/USART, USB, USB OTG |

| Peripherals                | DMA, I <sup>2</sup> S, LVD, POR, PWM, WDT                                            |

| Number of I/O              | 100                                                                                  |

| Program Memory Size        | 1MB (1M x 8)                                                                         |

| Program Memory Type        | FLASH                                                                                |

| EEPROM Size                | -                                                                                    |

| RAM Size                   | 256K x 8                                                                             |

| Voltage - Supply (Vcc/Vdd) | 1.71V ~ 3.6V                                                                         |

| Data Converters            | A/D 41x16b; D/A 2x12b                                                                |

| Oscillator Type            | Internal                                                                             |

| Operating Temperature      | -40°C ~ 105°C (TA)                                                                   |

| Mounting Type              | Surface Mount                                                                        |

| Package / Case             | 144-LBGA                                                                             |

| Supplier Device Package    | 144-MAPBGA (13x13)                                                                   |

| Purchase URL               | https://www.e-xfl.com/product-detail/nxp-semiconductors/mk64fn1m0vmd12               |

|                            |                                                                                      |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

## 2.2.1 Voltage and current operating requirements Table 1. Voltage and current operating requirements

| Symbol                             | Description                                                                                             | Min.                  | Max.                 | Unit | Notes |

|------------------------------------|---------------------------------------------------------------------------------------------------------|-----------------------|----------------------|------|-------|

| V <sub>DD</sub>                    | Supply voltage                                                                                          | 1.71                  | 3.6                  | V    |       |

| V <sub>DDA</sub>                   | Analog supply voltage                                                                                   | 1.71                  | 3.6                  | V    |       |

| V <sub>DD</sub> – V <sub>DDA</sub> | V <sub>DD</sub> -to-V <sub>DDA</sub> differential voltage                                               | -0.1                  | 0.1                  | V    |       |

| V <sub>SS</sub> – V <sub>SSA</sub> | V <sub>SS</sub> -to-V <sub>SSA</sub> differential voltage                                               | -0.1                  | 0.1                  | V    |       |

| V <sub>BAT</sub>                   | RTC battery supply voltage                                                                              | 1.71                  | 3.6                  | V    |       |

| V <sub>IH</sub>                    | Input high voltage                                                                                      |                       |                      |      |       |

|                                    | • 2.7 V $\leq$ V <sub>DD</sub> $\leq$ 3.6 V                                                             | $0.7 \times V_{DD}$   | _                    | V    |       |

|                                    | • $1.7 \text{ V} \le \text{V}_{\text{DD}} \le 2.7 \text{ V}$                                            | $0.75 \times V_{DD}$  | _                    | V    |       |

| V <sub>IL</sub>                    | Input low voltage                                                                                       |                       |                      |      |       |

|                                    | • $2.7 \text{ V} \le \text{V}_{\text{DD}} \le 3.6 \text{ V}$                                            | _                     | $0.35 \times V_{DD}$ | V    |       |

|                                    | • $1.7 \text{ V} \le \text{V}_{\text{DD}} \le 2.7 \text{ V}$                                            | —                     | $0.3 \times V_{DD}$  | V    |       |

| V <sub>HYS</sub>                   | Input hysteresis                                                                                        | $0.06 \times V_{DD}$  |                      | V    |       |

| I <sub>ICDIO</sub>                 | Digital pin negative DC injection current — single pin                                                  | _                     |                      | _    | 1     |

|                                    | • V <sub>IN</sub> < V <sub>SS</sub> -0.3V                                                               | -5                    | _                    | mA   |       |

| I <sub>ICAIO</sub>                 | Analog <sup>2</sup> , EXTAL, and XTAL pin DC injection current                                          |                       |                      |      | 3     |

|                                    | — single pin                                                                                            | _                     |                      | mA   |       |

|                                    | <ul> <li>V<sub>IN</sub> &lt; V<sub>SS</sub>-0.3V (Negative current injection)</li> </ul>                | -5                    | —                    |      |       |

|                                    | • V <sub>IN</sub> > V <sub>DD</sub> +0.3V (Positive current injection)                                  | _                     | +5                   |      |       |

| I <sub>ICcont</sub>                | Contiguous pin DC injection current —regional limit,                                                    |                       |                      |      |       |

|                                    | includes sum of negative injection currents or sum of positive injection currents of 16 contiguous pins |                       |                      |      |       |

|                                    |                                                                                                         | -25                   | _                    | mA   |       |

|                                    | Negative current injection                                                                              | _                     | +25                  |      |       |

|                                    | Positive current injection                                                                              |                       |                      |      |       |

| V <sub>ODPU</sub>                  | Open drain pullup voltage level                                                                         | $V_{DD}$              | V <sub>DD</sub>      | V    | 4     |

| V <sub>RAM</sub>                   | V <sub>DD</sub> voltage required to retain RAM                                                          | 1.2                   | —                    | V    |       |

| V <sub>RFVBAT</sub>                | V <sub>BAT</sub> voltage required to retain the VBAT register file                                      | V <sub>POR_VBAT</sub> |                      | V    |       |

- All 5 V tolerant digital I/O pins are internally clamped to V<sub>SS</sub> through an ESD protection diode. There is no diode connection to V<sub>DD</sub>. If V<sub>IN</sub> is less than V<sub>DIO\_MIN</sub>, a current limiting resistor is required. If V<sub>IN</sub> greater than V<sub>DIO\_MIN</sub> (=VSS-0.3V) is observed, then there is no need to provide current limiting resistors at the pads. The negative DC injection current limiting resistor is calculated as R=(V<sub>DIO\_MIN</sub>-V<sub>IN</sub>)/II<sub>ICDIO</sub>I.

- 2. Analog pins are defined as pins that do not have an associated general purpose I/O port function. Additionally, EXTAL and XTAL are analog pins.

- 3. All analog pins are internally clamped to V<sub>SS</sub> and V<sub>DD</sub> through ESD protection diodes. If V<sub>IN</sub> is less than V<sub>AIO\_MIN</sub> or greater than V<sub>AIO\_MAX</sub>, a current limiting resistor is required. The negative DC injection current limiting resistor is calculated as R=(V<sub>AIO\_MIN</sub>-V<sub>IN</sub>)/II<sub>ICAIO</sub>I. The positive injection current limiting resistor is calculated as R=(V<sub>IN</sub>-V<sub>AIO\_MAX</sub>)/II<sub>ICAIO</sub>I. Select the larger of these two calculated resistances if the pin is exposed to positive and negative injection currents.

- 4. Open drain outputs must be pulled to VDD.

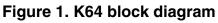

- No GPIOs toggled

- Code execution from flash with cache enabled

- For the ALLOFF curve, all peripheral clocks are disabled except FTFE

Figure 3. Run mode supply current vs. core frequency

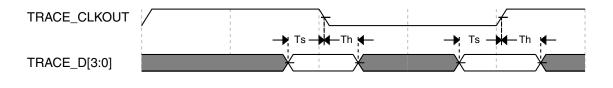

Figure 6. Trace data specifications

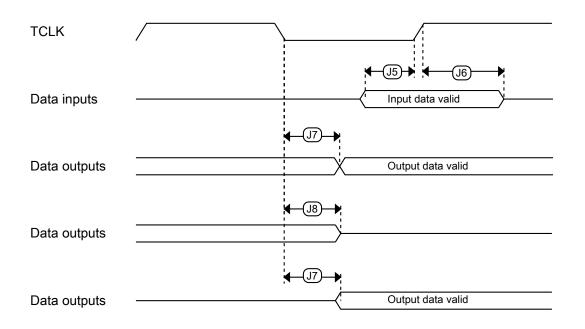

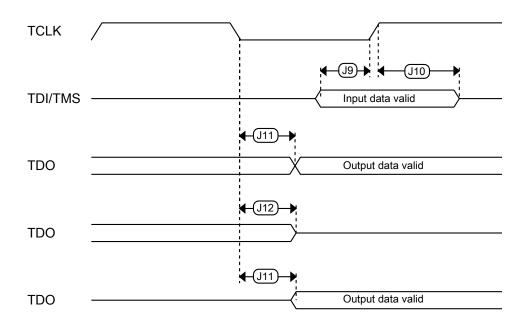

# 3.1.2 JTAG electricals

| Symbol | Description                                        | Min. | Max. | Unit |

|--------|----------------------------------------------------|------|------|------|

|        | Operating voltage                                  | 2.7  | 3.6  | V    |

| J1     | TCLK frequency of operation                        |      |      | MHz  |

|        | Boundary Scan                                      | 0    | 10   |      |

|        | JTAG and CJTAG                                     | 0    | 25   |      |

|        | Serial Wire Debug                                  | 0    | 50   |      |

| J2     | TCLK cycle period                                  | 1/J1 | _    | ns   |

| JЗ     | TCLK clock pulse width                             |      |      |      |

|        | Boundary Scan                                      | 50   | _    | ns   |

|        | JTAG and CJTAG                                     | 20   | _    | ns   |

|        | Serial Wire Debug                                  | 10   | _    | ns   |

| J4     | TCLK rise and fall times                           |      | 3    | ns   |

| J5     | Boundary scan input data setup time to TCLK rise   | 20   | _    | ns   |

| J6     | Boundary scan input data hold time after TCLK rise | 2.6  | _    | ns   |

| J7     | TCLK low to boundary scan output data valid        | _    | 25   | ns   |

| J8     | TCLK low to boundary scan output high-Z            | _    | 25   | ns   |

| J9     | TMS, TDI input data setup time to TCLK rise        | 8    | —    | ns   |

| J10    | TMS, TDI input data hold time after TCLK rise      | 1    | _    | ns   |

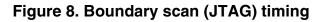

Figure 9. Test Access Port timing

| Symbol                   | Description                                                                                                                                           |                                    | Min.                            | Тур.  | Max.    | Unit    | Notes |

|--------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------|---------------------------------|-------|---------|---------|-------|

| f <sub>loc_low</sub>     | Loss of external c<br>RANGE = 00                                                                                                                      | lock minimum frequency —           | (3/5) x<br>f <sub>ints_t</sub>  | —     | -       | kHz     |       |

| f <sub>loc_high</sub>    | Loss of external c<br>RANGE = 01, 10,                                                                                                                 | lock minimum frequency —<br>or 11  | (16/5) x<br>f <sub>ints_t</sub> | _     | —       | kHz     |       |

|                          |                                                                                                                                                       |                                    | LL                              |       |         |         |       |

| f <sub>fll_ref</sub>     | FLL reference free                                                                                                                                    |                                    | 31.25                           | _     | 39.0625 | kHz     |       |

| f <sub>dco</sub>         | DCO output                                                                                                                                            | Low range (DRS=00)                 | 20                              | 20.97 | 25      | MHz     | 3, 4  |

| uoo                      | frequency range                                                                                                                                       | 640 × f <sub>fll_ref</sub>         |                                 |       |         |         |       |

|                          |                                                                                                                                                       | Mid range (DRS=01)                 | 40                              | 41.94 | 50      | MHz     | 1     |

|                          |                                                                                                                                                       | 1280 × f <sub>fll_ref</sub>        |                                 |       |         |         |       |

|                          |                                                                                                                                                       | Mid-high range (DRS=10)            | 60                              | 62.91 | 75      | MHz     | -     |

|                          |                                                                                                                                                       | $1920 \times f_{fll_ref}$          |                                 |       |         |         |       |

|                          |                                                                                                                                                       | High range (DRS=11)                | 80                              | 83.89 | 100     | MHz     | -     |

|                          |                                                                                                                                                       | $2560 \times f_{\text{fll ref}}$   |                                 | 00.00 |         |         |       |

| dco_t_DMX3 DCO output    |                                                                                                                                                       | Low range (DRS=00)                 |                                 | 23.99 |         | MHz     | 5, 6  |

| 2                        | frequency                                                                                                                                             | $732 \times f_{\text{fll_ref}}$    |                                 | 20.00 |         | 1411 12 | 0,0   |

|                          |                                                                                                                                                       | Mid range (DRS=01)                 |                                 | 47.97 |         | MHz     | 1     |

|                          |                                                                                                                                                       | $1464 \times f_{fll_ref}$          |                                 | 47.57 |         |         |       |

|                          |                                                                                                                                                       | Mid-high range (DRS=10)            |                                 | 71.99 |         | MHz     | +     |

|                          |                                                                                                                                                       | $2197 \times f_{\text{fll ref}}$   |                                 | 71.55 |         |         |       |

|                          |                                                                                                                                                       | High range (DRS=11)                |                                 | 95.98 |         | MHz     | -     |

|                          |                                                                                                                                                       | $2929 \times f_{\text{fil}_{ref}}$ |                                 | 95.90 |         |         |       |

| 1                        | FLL period jitter                                                                                                                                     | 2929 X IfII_ref                    |                                 |       |         |         |       |

| J <sub>cyc_fll</sub>     |                                                                                                                                                       | 11 1-                              | —                               | 180   | _       | ps      |       |

|                          | <ul> <li>f<sub>DCO</sub> = 48 MHz</li> <li>f<sub>DCO</sub> = 98 MHz</li> </ul>                                                                        |                                    | —                               | 150   | _       |         |       |

| t <sub>fll_acquire</sub> |                                                                                                                                                       | ncy acquisition time               | _                               | _     | 1       | ms      | 7     |

|                          |                                                                                                                                                       | P                                  | LL                              |       |         |         |       |

| f <sub>vco</sub>         | VCO operating fre                                                                                                                                     | equency                            | 48.0                            | _     | 120     | MHz     |       |

| I <sub>pll</sub>         | <ul> <li>PLL operating current</li> <li>PLL @ 96 MHz (f<sub>osc_hi_1</sub> = 8 MHz, f<sub>pll_ref</sub><br/>= 2 MHz, VDIV multiplier = 48)</li> </ul> |                                    | _                               | 1060  | _       | μA      | 8     |

| I <sub>pll</sub>         | <ul> <li>PLL operating current</li> <li>PLL @ 48 MHz (f<sub>osc_hi_1</sub> = 8 MHz, f<sub>pll_ref</sub> = 2 MHz, VDIV multiplier = 24)</li> </ul>     |                                    | _                               | 600   | _       | μA      | 8     |

| f <sub>pll_ref</sub>     | PLL reference frequency range                                                                                                                         |                                    | 2.0                             | _     | 4.0     | MHz     |       |

| J <sub>cyc_pll</sub>     | PLL period jitter (l                                                                                                                                  | RMS)                               |                                 |       |         |         | 9     |

|                          | • f <sub>vco</sub> = 48 MH                                                                                                                            | Hz                                 | _                               | 120   | _       | ps      |       |

|                          | • $f_{vco} = 120 \text{ MHz}$                                                                                                                         |                                    | _                               | 80    | _       | ps      |       |

| J <sub>acc_pll</sub>     |                                                                                                                                                       | jitter over 1µs (RMS)              |                                 |       |         |         | 9     |

| Table 17. MC | G specifications | (continued) |

|--------------|------------------|-------------|

|--------------|------------------|-------------|

| 3.3.3.2 | Oscillator frequency specifications |                             |

|---------|-------------------------------------|-----------------------------|

|         | Table 20. Oscillator frequency      | <sup>,</sup> specifications |

| Symbol                | Description                                                                                           | Min. | Тур. | Max. | Unit | Notes |

|-----------------------|-------------------------------------------------------------------------------------------------------|------|------|------|------|-------|

| f <sub>osc_lo</sub>   | Oscillator crystal or resonator frequency — low-<br>frequency mode (MCG_C2[RANGE]=00)                 | 32   | _    | 40   | kHz  |       |

| f <sub>osc_hi_1</sub> | Oscillator crystal or resonator frequency — high-<br>frequency mode (low range)<br>(MCG_C2[RANGE]=01) | 3    | _    | 8    | MHz  |       |

| f <sub>osc_hi_2</sub> | Oscillator crystal or resonator frequency — high<br>frequency mode (high range)<br>(MCG_C2[RANGE]=1x) | 8    | _    | 32   | MHz  |       |

| f <sub>ec_extal</sub> | Input clock frequency (external clock mode)                                                           | —    | —    | 50   | MHz  | 1, 2  |

| t <sub>dc_extal</sub> | Input clock duty cycle (external clock mode)                                                          | 40   | 50   | 60   | %    |       |

| t <sub>cst</sub>      | Crystal startup time — 32 kHz low-frequency,<br>low-power mode (HGO=0)                                | —    | 750  | _    | ms   | 3, 4  |

|                       | Crystal startup time — 32 kHz low-frequency,<br>high-gain mode (HGO=1)                                | —    | 250  | _    | ms   |       |

|                       | Crystal startup time — 8 MHz high-frequency<br>(MCG_C2[RANGE]=01), low-power mode<br>(HGO=0)          | _    | 0.6  | _    | ms   |       |

|                       | Crystal startup time — 8 MHz high-frequency<br>(MCG_C2[RANGE]=01), high-gain mode<br>(HGO=1)          | _    | 1    | _    | ms   |       |

1. Other frequency limits may apply when external clock is being used as a reference for the FLL

- 2. When transitioning from FEI or FBI to FBE mode, restrict the frequency of the input clock so that, when it is divided by FRDIV, it remains within the limits of the DCO input clock frequency.

- 3. Proper PC board layout procedures must be followed to achieve specifications.

- 4. Crystal startup time is defined as the time between the oscillator being enabled and the OSCINIT bit in the MCG\_S register being set.

## NOTE

The 32 kHz oscillator works in low power mode by default and cannot be moved into high power/gain mode.

## 3.3.4 32 kHz oscillator electrical characteristics

### 3.3.4.1 32 kHz oscillator DC electrical specifications Table 21. 32kHz oscillator DC electrical specifications

| Symbol           | Description                | Min. | Тур. | Max. | Unit |

|------------------|----------------------------|------|------|------|------|

| V <sub>BAT</sub> | Supply voltage             | 1.71 | —    | 3.6  | V    |

| R <sub>F</sub>   | Internal feedback resistor | —    | 100  | —    | MΩ   |

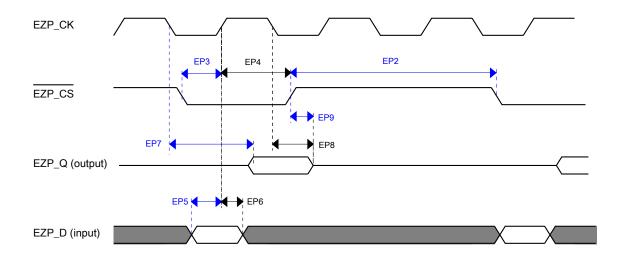

| Num  | Description                                              | Min.                    | Max.                | Unit |

|------|----------------------------------------------------------|-------------------------|---------------------|------|

|      | Operating voltage                                        | 1.71                    | 3.6                 | V    |

| EP1  | EZP_CK frequency of operation (all commands except READ) | -                       | f <sub>SYS</sub> /2 | MHz  |

| EP1a | EZP_CK frequency of operation (READ command)             | _                       | f <sub>SYS</sub> /8 | MHz  |

| EP2  | EZP_CS negation to next EZP_CS assertion                 | 2 x t <sub>EZP_CK</sub> | _                   | ns   |

| EP3  | EZP_CS input valid to EZP_CK high (setup)                | 5                       | —                   | ns   |

| EP4  | EZP_CK high to EZP_CS input invalid (hold)               | 5                       | —                   | ns   |

| EP5  | EZP_D input valid to EZP_CK high (setup)                 | 2                       | _                   | ns   |

| EP6  | EZP_CK high to EZP_D input invalid (hold)                | 5                       | _                   | ns   |

| EP7  | EZP_CK low to EZP_Q output valid                         | —                       | 18                  | ns   |

| EP8  | EZP_CK low to EZP_Q output invalid (hold)                | 0                       | _                   | ns   |

| EP9  | EZP_CS negation to EZP_Q tri-state                       |                         | 12                  | ns   |

## 3.4.2 EzPort switching specifications Table 27. EzPort switching specifications

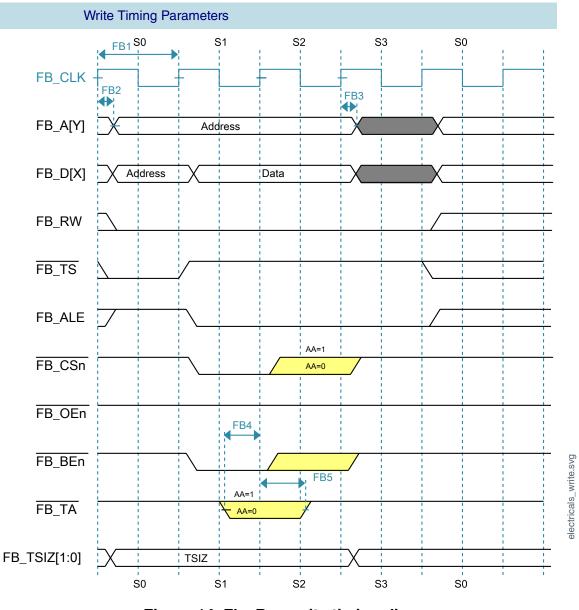

Figure 14. FlexBus write timing diagram

# 3.5 Security and integrity modules

There are no specifications necessary for the device's security and integrity modules.

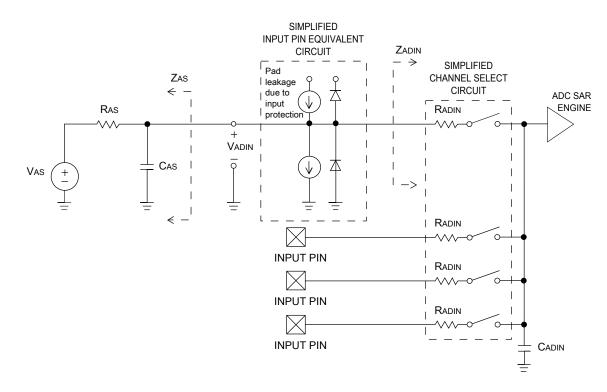

# 3.6 Analog

- 1. Typical values assume V<sub>DDA</sub> = 3.0 V, Temp = 25 °C, f<sub>ADCK</sub> = 1.0 MHz, unless otherwise stated. Typical values are for reference only, and are not tested in production.

- 2. DC potential difference.

- 3. This resistance is external to MCU. To achieve the best results, the analog source resistance must be kept as low as possible. The results in this data sheet were derived from a system that had < 8  $\Omega$  analog source resistance. The R<sub>AS</sub>/C<sub>AS</sub> time constant should be kept to < 1 ns.

- 4. To use the maximum ADC conversion clock frequency, CFG2[ADHSC] must be set and CFG1[ADLPC] must be clear.

- 5. For guidelines and examples of conversion rate calculation, download the ADC calculator tool.

Figure 15. ADC input impedance equivalency diagram

## 3.6.1.2 16-bit ADC electrical characteristics

| Table 31. | 16-bit ADC | characteristics | $(V_{REFH} = V_{I})$ | $DDA$ , $V_{REFL} = V_{SSA}$ |

|-----------|------------|-----------------|----------------------|------------------------------|

|-----------|------------|-----------------|----------------------|------------------------------|

| Symbol               | Description      | Conditions <sup>1</sup>                       | Min.  | Typ. <sup>2</sup> | Max. | Unit | Notes                   |

|----------------------|------------------|-----------------------------------------------|-------|-------------------|------|------|-------------------------|

| I <sub>DDA_ADC</sub> | Supply current   |                                               | 0.215 | —                 | 1.7  | mA   | 3                       |

|                      | ADC asynchronous | • ADLPC = 1, ADHSC = 0                        | 1.2   | 2.4               | 3.9  | MHz  | t <sub>ADACK</sub> = 1/ |

|                      | clock source     | • ADLPC = 1, ADHSC = 1                        | 2.4   | 4.0               | 6.1  | MHz  | f <sub>ADACK</sub>      |

| f <sub>ADACK</sub>   |                  | • ADLPC = 0, ADHSC = 0                        | 3.0   | 5.2               | 7.3  | MHz  |                         |

|                      |                  | • ADLPC = 0, ADHSC = 1                        | 4.4   | 6.2               | 9.5  | MHz  |                         |

|                      | Sample Time      | See Reference Manual chapter for sample times |       |                   |      |      |                         |

| Symbol              | Description            | Conditions <sup>1</sup>                         | Min. | Typ. <sup>2</sup> | Max. | Unit  | Notes                            |

|---------------------|------------------------|-------------------------------------------------|------|-------------------|------|-------|----------------------------------|

|                     |                        |                                                 |      |                   |      |       | current<br>operating<br>ratings) |

|                     | Temp sensor slope      | Across the full temperature range of the device | 1.55 | 1.62              | 1.69 | mV/°C | 8                                |

| V <sub>TEMP25</sub> | Temp sensor<br>voltage | 25 °C                                           | 706  | 716               | 726  | mV    | 8                                |

Table 31. 16-bit ADC characteristics ( $V_{REFH} = V_{DDA}$ ,  $V_{REFL} = V_{SSA}$ ) (continued)

1. All accuracy numbers assume the ADC is calibrated with  $V_{\mathsf{REFH}}$  =  $V_{\mathsf{DDA}}$

Typical values assume V<sub>DDA</sub> = 3.0 V, Temp = 25 °C, f<sub>ADCK</sub> = 2.0 MHz unless otherwise stated. Typical values are for reference only and are not tested in production.

- 3. The ADC supply current depends on the ADC conversion clock speed, conversion rate and ADC\_CFG1[ADLPC] (low power). For lowest power operation, ADC\_CFG1[ADLPC] must be set, the ADC\_CFG2[ADHSC] bit must be clear with 1 MHz ADC conversion clock speed.

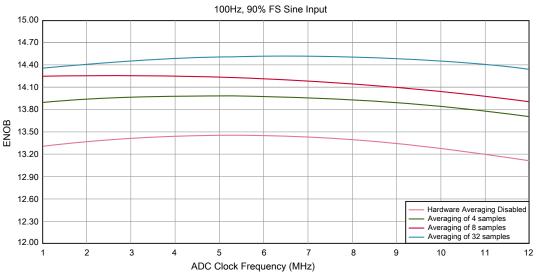

- 4. 1 LSB =  $(V_{REFH} V_{REFL})/2^N$

- 5. ADC conversion clock < 16 MHz, Max hardware averaging (AVGE = %1, AVGS = %11)

- 6. Input data is 100 Hz sine wave. ADC conversion clock < 12 MHz.

- 7. Input data is 1 kHz sine wave. ADC conversion clock < 12 MHz.

- 8. ADC conversion clock < 3 MHz

Typical ADC 16-bit Differential ENOB vs ADC Clock

Figure 16. Typical ENOB vs. ADC\_CLK for 16-bit differential mode

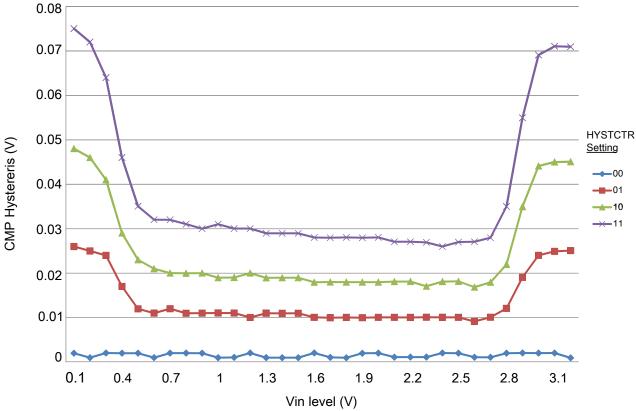

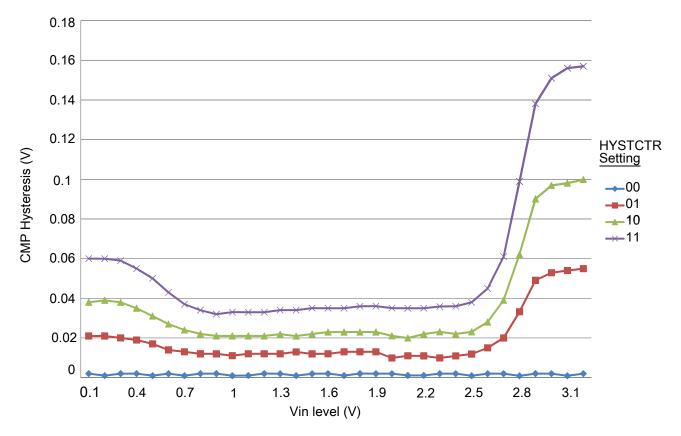

- 1. Typical hysteresis is measured with input voltage range limited to 0.6 to  $V_{DD}$ -0.6 V.

- Comparator initialization delay is defined as the time between software writes to change control inputs (Writes to CMP\_DACCR[DACEN], CMP\_DACCR[VRSEL], CMP\_DACCR[VOSEL], CMP\_MUXCR[PSEL], and CMP\_MUXCR[MSEL]) and the comparator output settling to a stable level.

Figure 18. Typical hysteresis vs. Vin level (VDD = 3.3 V, PMODE = 0)

3. 1 LSB = V<sub>reference</sub>/64

Figure 19. Typical hysteresis vs. Vin level (VDD = 3.3 V, PMODE = 1)

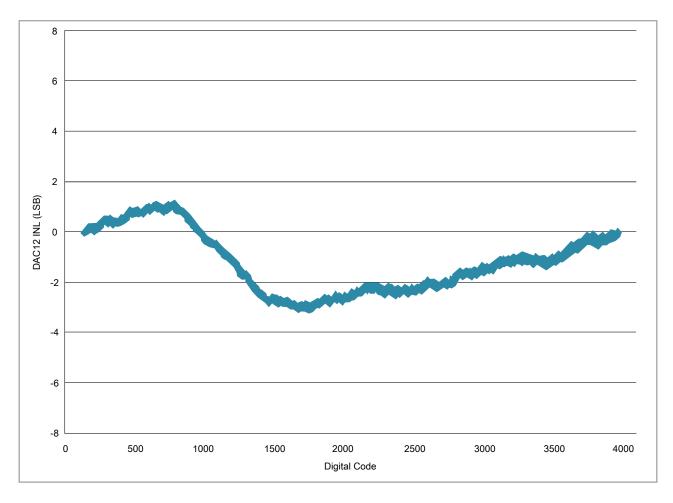

# 3.6.3 12-bit DAC electrical characteristics

## 3.6.3.1 12-bit DAC operating requirements Table 33. 12-bit DAC operating requirements

| Symbol           | Desciption              | Min. | Max. | Unit | Notes |

|------------------|-------------------------|------|------|------|-------|

| V <sub>DDA</sub> | Supply voltage          | 1.71 | 3.6  | V    |       |

| VDACR            | Reference voltage       | 1.13 | 3.6  | V    | 1     |

| CL               | Output load capacitance | —    | 100  | pF   | 2     |

| ١L               | Output load current     | —    | 1    | mA   |       |

1. The DAC reference can be selected to be  $V_{\text{DDA}}$  or  $V_{\text{REFH}}.$

2. A small load capacitance (47 pF) can improve the bandwidth performance of the DAC.

#### Peripheral operating requirements and behaviors

V<sub>DDA</sub> = 3.0 V, reference select set for V<sub>DDA</sub> (DACx\_CO:DACRFS = 1), high power mode (DACx\_CO:LPEN = 0), DAC set to 0x800, temperature range is across the full range of the device

Figure 20. Typical INL error vs. digital code

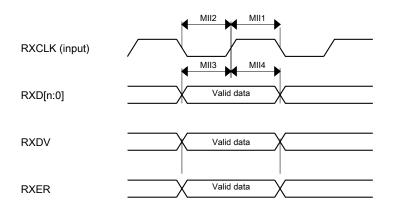

## Figure 23. RMII/MII receive signal timing diagram

## 3.8.1.2 RMII signal switching specifications

The following timing specs meet the requirements for RMII style interfaces for a range of transceiver devices.

| Num   | Description                                 | Min. | Max. | Unit               |

|-------|---------------------------------------------|------|------|--------------------|

| —     | EXTAL frequency (RMII input clock RMII_CLK) | —    | 50   | MHz                |

| RMII1 | RMII_CLK pulse width high                   | 35%  | 65%  | RMII_CLK<br>period |

| RMII2 | RMII_CLK pulse width low                    | 35%  | 65%  | RMII_CLK<br>period |

| RMII3 | RXD[1:0], CRS_DV, RXER to RMII_CLK setup    | 4    | —    | ns                 |

| RMII4 | RMII_CLK to RXD[1:0], CRS_DV, RXER hold     | 2    | —    | ns                 |

| RMII7 | RMII_CLK to TXD[1:0], TXEN invalid          | 4    | —    | ns                 |

| RMII8 | RMII_CLK to TXD[1:0], TXEN valid            |      | 15   | ns                 |

Table 40. RMII signal switching specifications

## 3.8.1.3 MDIO serial management timing specifications Table 41. MDIO serial management channel signal timing

| Num | Characteristic             | Symbol           | Min | Max | Unit               |

|-----|----------------------------|------------------|-----|-----|--------------------|

| E10 | MDC cycle time             | t <sub>MDC</sub> | 400 | —   | ns                 |

| E11 | MDC pulse width            |                  | 40  | 60  | % t <sub>MDC</sub> |

| E12 | MDC to MDIO output valid   |                  |     | 375 | ns                 |

| E13 | MDC to MDIO output invalid |                  | 25  | —   | ns                 |

| E14 | MDIO input to MDC setup    |                  | 10  | —   | ns                 |

| E15 | MDIO input to MDC hold     |                  | 0   | _   | ns                 |

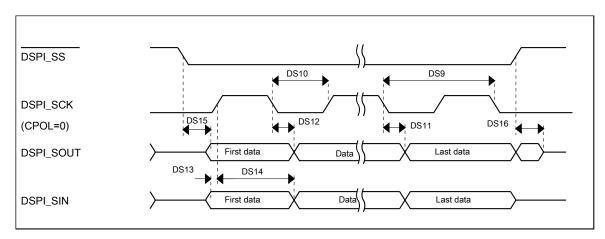

| Num  | Description                              | Min.                      | Max.                      | Unit |

|------|------------------------------------------|---------------------------|---------------------------|------|

|      | Operating voltage                        | 2.7                       | 3.6                       | V    |

|      | Frequency of operation                   |                           | 15 <sup>1</sup>           | MHz  |

| DS9  | DSPI_SCK input cycle time                | 4 x t <sub>BUS</sub>      | _                         | ns   |

| DS10 | DSPI_SCK input high/low time             | (t <sub>SCK</sub> /2) – 2 | (t <sub>SCK</sub> /2) + 2 | ns   |

| DS11 | DSPI_SCK to DSPI_SOUT valid              | —                         | 10                        | ns   |

| DS12 | DSPI_SCK to DSPI_SOUT invalid            | 0                         | —                         | ns   |

| DS13 | DSPI_SIN to DSPI_SCK input setup         | 2                         |                           | ns   |

| DS14 | DSPI_SCK to DSPI_SIN input hold          | 7                         | —                         | ns   |

| DS15 | DSPI_SS active to DSPI_SOUT driven       | —                         | 14                        | ns   |

| DS16 | DSPI_SS inactive to DSPI_SOUT not driven |                           | 14                        | ns   |

Table 45. Slave mode DSPI timing (limited voltage range)

1. The maximum operating frequency is measured with non-continuous CS and SCK. When DSPI is configured with continuous CS and SCK, there is a constraint that SPI clock should not be greater than 1/6 of bus clock, for example, when bus clock is 60MHz, SPI clock should not be greater than 10MHz

Figure 26. DSPI classic SPI timing — slave mode

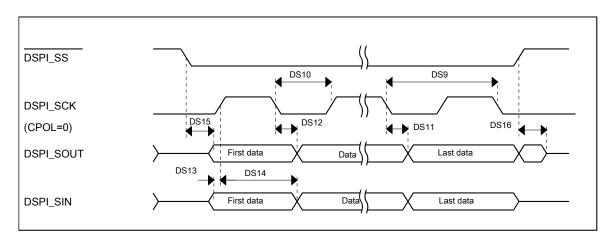

| Num  | Description                              | Min.                      | Max.              | Unit |

|------|------------------------------------------|---------------------------|-------------------|------|

|      | Frequency of operation                   | —                         | 7.5               | MHz  |

| DS9  | DSPI_SCK input cycle time                | 8 x t <sub>BUS</sub>      | —                 | ns   |

| DS10 | DSPI_SCK input high/low time             | (t <sub>SCK</sub> /2) - 4 | $(t_{SCK/2)} + 4$ | ns   |

| DS11 | DSPI_SCK to DSPI_SOUT valid              | —                         | 23.5              | ns   |

| DS12 | DSPI_SCK to DSPI_SOUT invalid            | 0                         | —                 | ns   |

| DS13 | DSPI_SIN to DSPI_SCK input setup         | 4                         | —                 | ns   |

| DS14 | DSPI_SCK to DSPI_SIN input hold          | 7                         | —                 | ns   |

| DS15 | DSPI_SS active to DSPI_SOUT driven       | —                         | 21                | ns   |

| DS16 | DSPI_SS inactive to DSPI_SOUT not driven | —                         | 19                | ns   |

Figure 28. DSPI classic SPI timing — slave mode

## 3.8.8 Inter-Integrated Circuit Interface (I<sup>2</sup>C) timing Table 48. I<sup>2</sup>C timing

| Characteristic                                                                                     | Symbol Standard Mode  |                | Fast Mode         |                | Unit             |     |

|----------------------------------------------------------------------------------------------------|-----------------------|----------------|-------------------|----------------|------------------|-----|

|                                                                                                    |                       | Minimum        | Maximum           | Minimum        | Maximum          |     |

| SCL Clock Frequency                                                                                | f <sub>SCL</sub>      | 0              | 100               | 0              | 400 <sup>1</sup> | kHz |

| Hold time (repeated) START condition.<br>After this period, the first clock pulse is<br>generated. | t <sub>HD</sub> ; STA | 4              | _                 | 0.6            | _                | μs  |

| LOW period of the SCL clock                                                                        | t <sub>LOW</sub>      | 4.7            | —                 | 1.25           | —                | μs  |

| HIGH period of the SCL clock                                                                       | t <sub>HIGH</sub>     | 4              | —                 | 0.6            | —                | μs  |

| Set-up time for a repeated START condition                                                         | t <sub>SU</sub> ; STA | 4.7            | —                 | 0.6            | —                | μs  |

| Data hold time for I <sup>2</sup> C bus devices                                                    | t <sub>HD</sub> ; DAT | 0 <sup>2</sup> | 3.45 <sup>3</sup> | 0 <sup>4</sup> | 0.9 <sup>2</sup> | μs  |

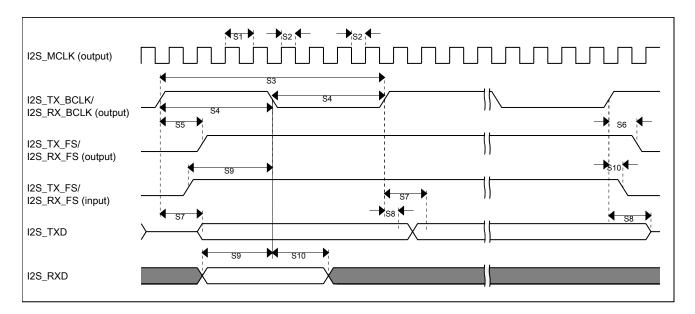

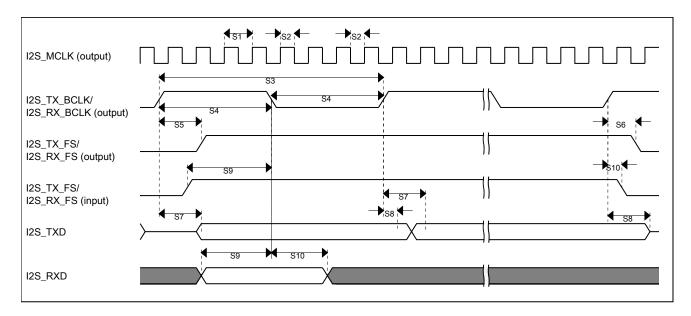

### Figure 33. I2S/SAI timing — master modes

| Num. | Characteristic                                                    | Min. | Max. | Unit        |

|------|-------------------------------------------------------------------|------|------|-------------|

|      | Operating voltage                                                 | 1.71 | 3.6  | V           |

| S11  | I2S_TX_BCLK/I2S_RX_BCLK cycle time (input)                        | 80   | —    | ns          |

| S12  | I2S_TX_BCLK/I2S_RX_BCLK pulse width high/low (input)              | 45%  | 55%  | MCLK period |

| S13  | I2S_TX_FS/I2S_RX_FS input setup before<br>I2S_TX_BCLK/I2S_RX_BCLK | 7    | —    | ns          |

| S14  | I2S_TX_FS/I2S_RX_FS input hold after<br>I2S_TX_BCLK/I2S_RX_BCLK   | 2    | —    | ns          |

| S15  | I2S_TX_BCLK to I2S_TXD/I2S_TX_FS output valid                     | —    | 25.5 | ns          |

| S16  | I2S_TX_BCLK to I2S_TXD/I2S_TX_FS output invalid                   | 3    | —    | ns          |

| S17  | I2S_RXD setup before I2S_RX_BCLK                                  | 5.8  | —    | ns          |

| S18  | I2S_RXD hold after I2S_RX_BCLK                                    | 2    | —    | ns          |

| S19  | I2S_TX_FS input assertion to I2S_TXD output valid <sup>1</sup>    | —    | 25   | ns          |

### Table 54. I2S/SAI slave mode timing

1. Applies to first bit in each frame and only if the TCR4[FSE] bit is clear

Figure 35. I2S/SAI timing — master modes

### Table 56. I2S/SAI slave mode timing in VLPR, VLPW, and VLPS modes (full voltage range)

| Num. | Characteristic                                                    | Min. | Max. | Unit        |

|------|-------------------------------------------------------------------|------|------|-------------|

|      | Operating voltage                                                 | 1.71 | 3.6  | V           |

| S11  | I2S_TX_BCLK/I2S_RX_BCLK cycle time (input)                        | 250  | —    | ns          |

| S12  | I2S_TX_BCLK/I2S_RX_BCLK pulse width high/low (input)              | 45%  | 55%  | MCLK period |

| S13  | I2S_TX_FS/I2S_RX_FS input setup before<br>I2S_TX_BCLK/I2S_RX_BCLK | 30   | -    | ns          |

| S14  | I2S_TX_FS/I2S_RX_FS input hold after<br>I2S_TX_BCLK/I2S_RX_BCLK   | 11   | -    | ns          |

| S15  | I2S_TX_BCLK to I2S_TXD/I2S_TX_FS output valid                     | —    |      | ns          |

| S16  | I2S_TX_BCLK to I2S_TXD/I2S_TX_FS output invalid                   | 0    | —    | ns          |

| S17  | I2S_RXD setup before I2S_RX_BCLK                                  | 30   | —    | ns          |

| S18  | I2S_RXD hold after I2S_RX_BCLK                                    | 11   | —    | ns          |

| S19  | I2S_TX_FS input assertion to I2S_TXD output valid <sup>1</sup>    | —    | 72   | ns          |

1. Applies to first bit in each frame and only if the TCR4[FSE] bit is clear

#### How to Reach Us:

Home Page: nxp.com

Web Support: nxp.com/support Information in this document is provided solely to enable system and software implementers to use NXP products. There are no express or implied copyright licenses granted hereunder to design or fabricate any integrated circuits based on the information in this document. NXP reserves the right to make changes without further notice to any products herein.

NXP makes no warranty, representation, or guarantee regarding the suitability of its products for any particular purpose, nor does NXP assume any liability arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without limitation consequential or incidental damages. "Typical" parameters that may be provided in NXP data sheets and/or specifications can and do vary in different applications, and actual performance may vary over time. All operating parameters, including "typicals," must be validated for each customer application by customer's technical experts. NXP does not convey any license under its patent rights nor the rights of others. NXP sells products pursuant to standard terms and conditions of sale, which can be found at the following address: nxp.com/salestermsandconditions.

NXP, NXP logo, and Kinetis are trademarks of NXP B.V. All other product or service names are the property of their respective owners. ARM and Cortex are registered trademarks of ARM Limited (or its subsidiaries) in the EU and/or elsewhere. The USB-IF Logo is a registered trademark of USB Implementers Forum, Inc. All rights reserved.

©2014-2016 NXP B.V.

Document Number K64P144M120SF5 Revision 7, 10/2016