Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                                    |

|----------------------------|---------------------------------------------------------------------------|

| Core Processor             | ARM® Cortex®-M0                                                           |

| Core Size                  | 32-Bit Single-Core                                                        |

| Speed                      | 50MHz                                                                     |

| Connectivity               | I <sup>2</sup> C, Microwire, SPI, SSI, SSP, UART/USART, USB               |

| Peripherals                | Brown-out Detect/Reset, POR, WDT                                          |

| Number of I/O              | 40                                                                        |

| Program Memory Size        | 24KB (24K x 8)                                                            |

| Program Memory Type        | FLASH                                                                     |

| EEPROM Size                | 1K x 8                                                                    |

| RAM Size                   | 8K x 8                                                                    |

| Voltage - Supply (Vcc/Vdd) | 1.8V ~ 3.6V                                                               |

| Data Converters            | A/D 8x10b                                                                 |

| Oscillator Type            | Internal                                                                  |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                         |

| Mounting Type              | Surface Mount                                                             |

| Package / Case             | 48-LQFP                                                                   |

| Supplier Device Package    | 48-LQFP (7x7)                                                             |

| Purchase URL               | https://www.e-xfl.com/product-detail/nxp-semiconductors/lpc11u23fbd48-301 |

|                            |                                                                           |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

- Standard JTAG (Joint Test Action Group) test interface for BSDL (Boundary Scan Description Language).

- Serial Wire Debug.

- Digital peripherals:

- ◆ Up to 54 General-Purpose I/O (GPIO) pins with configurable pull-up/pull-down resistors, repeater mode, and open-drain mode.

- Up to 8 GPIO pins can be selected as edge and level sensitive interrupt sources.

- Two GPIO grouped interrupt modules enable an interrupt based on a programmable pattern of input states of a group of GPIO pins.

- ♦ High-current source output driver (20 mA) on one pin.

- ♦ High-current sink driver (20 mA) on true open-drain pins.

- Four general-purpose counter/timers with a total of up to 5 capture inputs and 13 match outputs.

- Programmable Windowed WatchDog Timer (WWDT) with a dedicated, internal low-power WatchDog Oscillator (WDO).

- Analog peripherals:

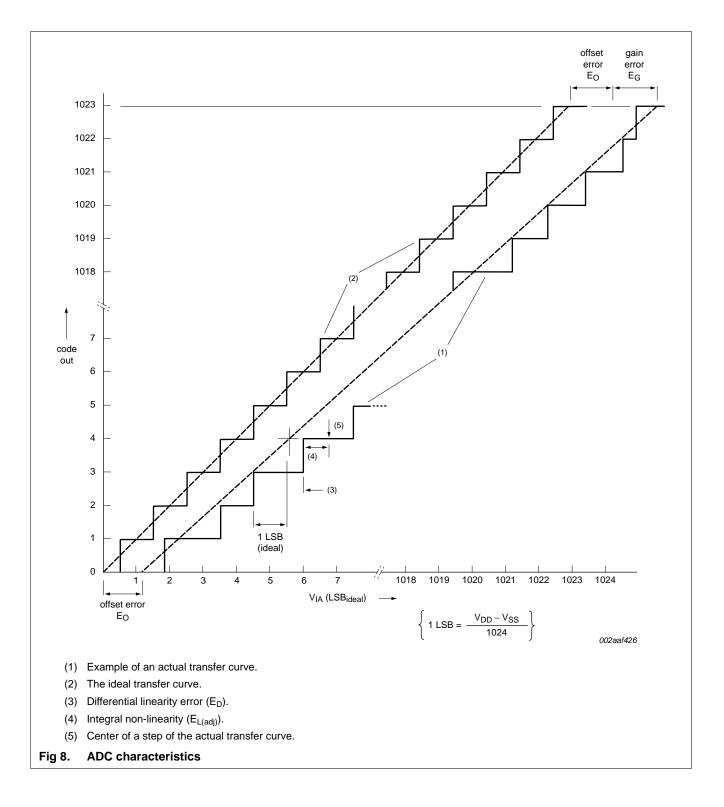

- ◆ 10-bit ADC with input multiplexing among eight pins.

- Serial interfaces:

- ◆ USB 2.0 full-speed device controller.

- USART (Universal Synchronous Asynchronous Receiver/Transmitter) with fractional baud rate generation, internal FIFO, a full modem control handshake interface, and support for RS-485/9-bit mode and synchronous mode. USART supports an asynchronous smart card interface (ISO 7816-3).

- Two SSP (Synchronous Serial Port) controllers with FIFO and multi-protocol capabilities.

- ♦ I<sup>2</sup>C-bus interface supporting the full I<sup>2</sup>C-bus specification and Fast-mode Plus with a data rate of up to 1 Mbit/s with multiple address recognition and monitor mode.

- Clock generation:

- Crystal Oscillator with an operating range of 1 MHz to 25 MHz (system oscillator).

- 12 MHz high-frequency Internal RC oscillator (IRC) that can optionally be used as a system clock.

- Internal low-power, low-frequency WatchDog Oscillator (WDO) with programmable frequency output.

- PLL allows CPU operation up to the maximum CPU rate with the system oscillator or the IRC as clock sources.

- ◆ A second, dedicated PLL is provided for USB.

- Clock output function with divider that can reflect the crystal oscillator, the main clock, the IRC, or the watchdog oscillator.

- Power control:

- Integrated PMU (Power Management Unit) to minimize power consumption during Sleep, Deep-sleep, Power-down, and Deep power-down modes.

- Power profiles residing in boot ROM provide optimized performance and minimized power consumption for any given application through one simple function call.

- Four reduced power modes: Sleep, Deep-sleep, Power-down, and Deep power-down.

- Processor wake-up from Deep-sleep and Power-down modes via reset, selectable GPIO pins, watchdog interrupt, or USB port activity.

### 32-bit ARM Cortex-M0 microcontroller

# 32-bit ARM Cortex-M0 microcontroller

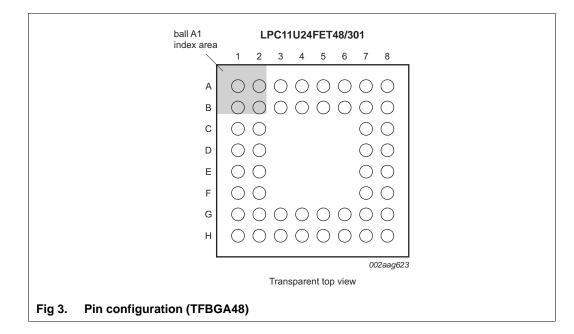

### Table 3. Pin description

| Symbol                             | Pin HVQFN33 | Pin TFBGA48 | Pin LQFP48 | Pin LQFP64 |            | Reset<br>state<br>[1] | Туре | Description                                                                                                                                                                      |

|------------------------------------|-------------|-------------|------------|------------|------------|-----------------------|------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| PIO0_5/SDA                         | 11          | H3          | 16         | 21         | <u>[4]</u> | I; IA                 | I/O  | <b>PIO0_5</b> — General purpose digital input/output pin (open-drain).                                                                                                           |

|                                    |             |             |            |            |            | -                     | I/O  | <b>SDA</b> — I <sup>2</sup> C-bus data input/output (open-drain).<br>High-current sink only if I <sup>2</sup> C Fast-mode Plus is<br>selected in the I/O configuration register. |

| PIO0_6/USB_CONNECT/                | 15          | H6          | 22         | 29         | [3]        | I; PU                 | I/O  | PIO0_6 — General purpose digital input/output pin.                                                                                                                               |

| SCK0                               |             |             |            |            |            | -                     | 0    | <b>USB_CONNECT</b> — Signal used to switch an external 1.5 k $\Omega$ resistor under software control. Used with the SoftConnect USB feature.                                    |

|                                    |             |             |            |            |            | -                     | I/O  | SCK0 — Serial clock for SSP0.                                                                                                                                                    |

| PIO0_7/CTS                         | 16          | G7          | 23         | 30         | [5]        | I; PU                 | I/O  | <b>PIO0_7</b> — General purpose digital input/output pin (high-current output driver).                                                                                           |

|                                    |             |             |            |            |            | -                     | I    | CTS — Clear To Send input for USART.                                                                                                                                             |

| PIO0_8/MISO0/                      | 17          | F8          | 27         | 36         | [3]        | I; PU                 | I/O  | PIO0_8 — General purpose digital input/output pin.                                                                                                                               |

| CT16B0_MAT0                        |             |             |            |            |            | -                     | I/O  | MISO0 — Master In Slave Out for SSP0.                                                                                                                                            |

|                                    |             |             |            |            |            | -                     | 0    | CT16B0_MAT0 — Match output 0 for 16-bit timer 0.                                                                                                                                 |

| PIO0_9/MOSI0/                      | 18          | F7          | 28         | 37         | [3]        | I; PU                 | I/O  | PIO0_9 — General purpose digital input/output pin.                                                                                                                               |

| CT16B0_MAT1                        |             |             |            |            |            | -                     | I/O  | MOSI0 — Master Out Slave In for SSP0.                                                                                                                                            |

|                                    |             |             |            |            |            | -                     | 0    | CT16B0_MAT1 — Match output 1 for 16-bit timer 0.                                                                                                                                 |

| SWCLK/PIO0_10/SCK0/<br>CT16B0_MAT2 | 19          | E7          | 29         | 38         | <u>[3]</u> | I; PU                 | I    | <b>SWCLK</b> — Serial wire clock and test clock TCK for JTAG interface.                                                                                                          |

|                                    |             |             |            |            |            | -                     | I/O  | PIO0_10 — General purpose digital input/output pin.                                                                                                                              |

|                                    |             |             |            |            |            | -                     | 0    | SCK0 — Serial clock for SSP0.                                                                                                                                                    |

|                                    |             |             |            |            |            | -                     | 0    | CT16B0_MAT2 — Match output 2 for 16-bit timer 0.                                                                                                                                 |

| TDI/PIO0_11/AD0/                   | 21          | D8          | 32         | 42         | [6]        | I; PU                 | I    | <b>TDI</b> — Test Data In for JTAG interface.                                                                                                                                    |

| CT32B0_MAT3                        |             |             |            |            |            | -                     | I/O  | PIO0_11 — General purpose digital input/output pin.                                                                                                                              |

|                                    |             |             |            |            |            | -                     | I    | AD0 — A/D converter, input 0.                                                                                                                                                    |

|                                    |             |             |            |            |            | -                     | 0    | CT32B0_MAT3 — Match output 3 for 32-bit timer 0.                                                                                                                                 |

| TMS/PIO0_12/AD1/                   | 22          | C7          | 33         | 44         | [6]        | I; PU                 | I    | <b>TMS</b> — Test Mode Select for JTAG interface.                                                                                                                                |

| CT32B1_CAP0                        |             |             |            |            |            | -                     | I/O  | PIO_12 — General purpose digital input/output pin.                                                                                                                               |

|                                    |             |             |            |            |            | -                     | I    | AD1 — A/D converter, input 1.                                                                                                                                                    |

|                                    |             |             |            |            |            | -                     | I    | CT32B1_CAP0 — Capture input 0 for 32-bit timer 1.                                                                                                                                |

| TDO/PIO0_13/AD2/                   | 23          | C8          | 34         | 45         | [6]        | I; PU                 | 0    | <b>TDO</b> — Test Data Out for JTAG interface.                                                                                                                                   |

| CT32B1_MAT0                        |             |             |            |            |            | -                     | I/O  | PIO0_13 — General purpose digital input/output pin.                                                                                                                              |

|                                    |             |             |            |            |            | -                     | I    | AD2 — A/D converter, input 2.                                                                                                                                                    |

|                                    |             |             |            |            |            | -                     | 0    | CT32B1_MAT0 — Match output 0 for 32-bit timer 1.                                                                                                                                 |

# 32-bit ARM Cortex-M0 microcontroller

#### Table 3. **Pin description**

| Table 3.Pin descriptionSymbol |             | m           |            |            |     | Reset        | Туре | Description                                                            |

|-------------------------------|-------------|-------------|------------|------------|-----|--------------|------|------------------------------------------------------------------------|

| Symbol                        | Pin HVQFN33 | Pin TFBGA48 | Pin LQFP48 | Pin LQFP64 |     | state<br>[1] | туре | Description                                                            |

| PIO1_17/CT16B0_CAP1/          | -           | -           | -          | 23         | [3] | I; PU        | I/O  | <b>PIO1_17</b> — General purpose digital input/output pin.             |

| RXD                           |             |             |            |            |     | -            | I    | CT16B0_CAP1 — Capture input 1 for 16-bit timer 0.                      |

|                               |             |             |            |            |     | -            | I    | <b>RXD</b> — Receiver input for USART.                                 |

| PIO1_18/CT16B1_CAP1/          | -           | -           | -          | 28         | [3] | I; PU        | I/O  | PIO1_18 — General purpose digital input/output pin.                    |

| TXD                           |             |             |            |            |     | -            | I    | CT16B1_CAP1 — Capture input 1 for 16-bit timer 1.                      |

|                               |             |             |            |            |     | -            | 0    | <b>TXD</b> — Transmitter output for USART.                             |

| PIO1_19/DTR/SSEL1             | 1           | B1          | 2          | 3          | [3] | I; PU        | I/O  | <b>PIO1_19</b> — General purpose digital input/output pin.             |

|                               |             |             |            |            |     | -            | 0    | <b>DTR</b> — Data Terminal Ready output for USART.                     |

|                               |             |             |            |            |     | -            | I/O  | SSEL1 — Slave select for SSP1.                                         |

| PIO1_20/DSR/SCK1              | -           | H1          | 13         | 18         | [3] | I; PU        | I/O  | PIO1_20 — General purpose digital input/output pin.                    |

|                               |             |             |            |            |     | -            | I    | <b>DSR</b> — Data Set Ready input for USART.                           |

|                               |             |             |            |            |     | -            | I/O  | SCK1 — Serial clock for SSP1.                                          |

| PIO1_21/DCD/MISO1             | -           | G8          | 26         | 35         | [3] | I; PU        | I/O  | PIO1_21 — General purpose digital input/output pin.                    |

|                               |             |             |            |            |     | -            | I    | DCD — Data Carrier Detect input for USART.                             |

|                               |             |             |            |            |     | -            | I/O  | MISO1 — Master In Slave Out for SSP1.                                  |

| PIO1_22/RI/MOSI1              | -           | A7          | 38         | 51         | [3] | I; PU        | I/O  | PIO1_22 — General purpose digital input/output pin.                    |

|                               |             |             |            |            |     | -            | I    | RI — Ring Indicator input for USART.                                   |

|                               |             |             |            |            |     | -            | I/O  | MOSI1 — Master Out Slave In for SSP1.                                  |

| PIO1_23/CT16B1_MAT1/          | -           | H4          | 18         | 24         | [3] | I; PU        | I/O  | PIO1_23 — General purpose digital input/output pin.                    |

| SSEL1                         |             |             |            |            |     | -            | 0    | CT16B1_MAT1 — Match output 1 for 16-bit timer 1.                       |

|                               |             |             |            |            |     | -            | I/O  | SSEL1 — Slave select for SSP1.                                         |

| PIO1_24/CT32B0_MAT0           | -           | G6          | 21         | 27         | [3] | I; PU        | I/O  | PIO1_24 — General purpose digital input/output pin.                    |

|                               |             |             |            |            |     | -            | 0    | CT32B0_MAT0 — Match output 0 for 32-bit timer 0.                       |

| PIO1_25/CT32B0_MAT1           | -           | A1          | 1          | 2          | [3] | I; PU        | I/O  | PIO1_25 — General purpose digital input/output pin.                    |

|                               |             |             |            |            |     | -            | 0    | CT32B0_MAT1 — Match output 1 for 32-bit timer 0.                       |

| PIO1_26/CT32B0_MAT2/          | -           | G2          | 11         | 14         | [3] | I; PU        | I/O  | PIO1_26 — General purpose digital input/output pin.                    |

| RXD                           |             |             |            |            |     | -            | 0    | CT32B0_MAT2 — Match output 2 for 32-bit timer 0.                       |

|                               |             |             |            |            |     | -            | I    | <b>RXD</b> — Receiver input for USART.                                 |

| PIO1_27/CT32B0_MAT3/          | -           | G1          | 12         | 15         | [3] | I; PU        | I/O  | PIO1_27 — General purpose digital input/output pin.                    |

| TXD                           |             |             |            |            |     | -            | 0    | CT32B0_MAT3 — Match output 3 for 32-bit timer 0.                       |

|                               |             |             |            |            |     | -            | 0    | <b>TXD</b> — Transmitter output for USART.                             |

| PIO1_28/CT32B0_CAP0/          | -           | H7          | 24         | 31         | [3] | I; PU        | I/O  | PIO1_28 — General purpose digital input/output pin.                    |

| SCLK                          |             |             |            |            |     | -            | I    | CT32B0_CAP0 — Capture input 0 for 32-bit timer 0.                      |

|                               |             |             |            |            |     | -            | I/O  | <b>SCLK</b> — Serial clock input/output for USART in synchronous mode. |

| PIO1_29/SCK0/                 | -           | D7          | 31         | 41         | [3] | I; PU        | I/O  | PIO1_29 — General purpose digital input/output pin.                    |

| CT32B0_CAP1                   |             |             |            |            |     | -            | I/O  | SCK0 — Serial clock for SSP0.                                          |

|                               |             |             |            |            |     | -            | I    | CT32B0_CAP1 — Capture input 1 for 32-bit timer 0.                      |

LPC11U2X Product data sheet

### 7.8.1 Features

- GPIO pins can be configured as input or output by software.

- All GPIO pins default to inputs with interrupt disabled at reset.

- Pin registers allow pins to be sensed and set individually.

- Up to eight GPIO pins can be selected from all GPIO pins to create an edge- or level-sensitive GPIO interrupt request.

- Any pin or pins in each port can trigger a port interrupt.

### 7.9 USB interface

The Universal Serial Bus (USB) is a 4-wire bus that supports communication between a host and one or more (up to 127) peripherals. The host controller allocates the USB bandwidth to attached devices through a token-based protocol. The bus supports hot-plugging and dynamic configuration of the devices. The host controller initiates all transactions.

The LPC11U2x USB interface consists of a full-speed device controller with on-chip PHY (PHYsical layer) for device functions.

**Remark:** Configure the LPC11U2x in default power mode with the power profiles before using the USB (see <u>Section 7.17.5.1</u>). Do not use the USB with the part in performance, efficiency, or low-power mode.

### 7.9.1 Full-speed USB device controller

The device controller enables 12 Mbit/s data exchange with a USB Host controller. It consists of a register interface, serial interface engine, and endpoint buffer memory. The serial interface engine decodes the USB data stream and writes data to the appropriate endpoint buffer. The status of a completed USB transfer or error condition is indicated via status registers. If enabled, an interrupt is generated.

### 7.9.1.1 Features

- Dedicated USB PLL available.

- Fully compliant with USB 2.0 specification (full speed).

- Supports 10 physical (5 logical) endpoints including one control endpoint.

- Single and double buffering supported.

- Each non-control endpoint supports bulk, interrupt, or isochronous endpoint types.

- Supports wake-up from Deep-sleep mode and Power-down mode on USB activity and remote wake-up.

- Supports SoftConnect.

# 7.10 USART

The LPC11U2x contains one USART.

The USART includes full modem control, support for synchronous mode, and a smart card interface. The RS-485/9-bit mode allows both software address detection and automatic address detection using 9-bit mode.

### 32-bit ARM Cortex-M0 microcontroller

- Four match registers per timer that allow:

- Continuous operation with optional interrupt generation on match.

- Stop timer on match with optional interrupt generation.

- Reset timer on match with optional interrupt generation.

- Up to four external outputs corresponding to match registers, with the following capabilities:

- Set LOW on match.

- Set HIGH on match.

- Toggle on match.

- Do nothing on match.

- The timer and prescaler can be configured to be cleared on a designated capture event. This feature permits easy pulse-width measurement by clearing the timer on the leading edge of an input pulse and capturing the timer value on the trailing edge.

### 7.15 System tick timer

The ARM Cortex-M0 includes a system tick timer (SYSTICK) that is intended to generate a dedicated SYSTICK exception at a fixed time interval (typically 10 ms).

# 7.16 Windowed WatchDog Timer (WWDT)

The purpose of the WWDT is to prevent an unresponsive system state. If software fails to update the watchdog within a programmable time window, the watchdog resets the microcontroller

### 7.16.1 Features

- Internally resets chip if not periodically reloaded during the programmable time-out period.

- Optional windowed operation requires reload to occur between a minimum and maximum time period, both programmable.

- Optional warning interrupt can be generated at a programmable time before watchdog time-out.

- Software enables the WWDT, but a hardware reset or a watchdog reset/interrupt is required to disable the WWDT.

- Incorrect feed sequence causes reset or interrupt, if enabled.

- Flag to indicate watchdog reset.

- Programmable 24-bit timer with internal prescaler.

- Selectable time period from  $(T_{cy(WDCLK)} \times 256 \times 4)$  to  $(T_{cy(WDCLK)} \times 2^{24} \times 4)$  in multiples of  $T_{cy(WDCLK)} \times 4$ .

- The Watchdog Clock (WDCLK) source can be selected from the IRC or the dedicated watchdog oscillator (WDO). The clock source selection provides a wide range of potential timing choices of watchdog operation under different power conditions.

### 7.17.1.2 System oscillator

The system oscillator can be used as the clock source for the CPU, with or without using the PLL. On the LPC11U2x, use the system oscillator to provide the clock source to USB.

The system oscillator operates at frequencies of 1 MHz to 25 MHz. This frequency can be boosted to a higher frequency, up to the maximum CPU operating frequency, by the system PLL.

### 7.17.1.3 Watchdog oscillator

The watchdog oscillator can be used as a clock source that directly drives the CPU, the watchdog timer, or the CLKOUT pin. The watchdog oscillator nominal frequency is programmable between 7.8 kHz and 1.7 MHz. The frequency spread over processing and temperature is  $\pm 40$  % (see also Table 13).

### 7.17.2 System PLL and USB PLL

The LPC11U2x contain a system PLL and a dedicated PLL for generating the 48 MHz USB clock. The system and USB PLLs are identical.

The PLL accepts an input clock frequency in the range of 10 MHz to 25 MHz. The input frequency is multiplied up to a high frequency with a Current Controlled Oscillator (CCO). The multiplier can be an integer value from 1 to 32. The CCO operates in the range of 156 MHz to 320 MHz. To support this frequency range, an additional divider keeps the CCO within its frequency range while the PLL is providing the desired output frequency. The output divider can be set to divide by 2, 4, 8, or 16 to produce the output clock. The PLL output frequency must be lower than 100 MHz. Since the minimum output divider value is 2, it is insured that the PLL output has a 50 % duty cycle. The PLL is turned off and bypassed following a chip reset. Software can enable the PLL later. The program must configure and activate the PLL, wait for the PLL to lock, and then connect to the PLL as a clock source. The PLL settling time is 100  $\mu$ s.

### 7.17.3 Clock output

The LPC11U2x feature a clock output function that routes the IRC oscillator, the system oscillator, the watchdog oscillator, or the main clock to an output pin.

### 7.17.4 Wake-up process

The LPC11U2x begin operation by using the 12 MHz IRC oscillator as the clock source at power-up and when awakened from Deep power-down mode. This mechanism allows chip operation to resume quickly. If the application uses the main oscillator or the PLL, software must enable these components and wait for them to stabilize. Only then can the system use the PLL and main oscillator as a clock source.

### 7.17.5 Power control

The LPC11U2x support various power control features. There are four special modes of processor power reduction: Sleep mode, Deep-sleep mode, Power-down mode, and Deep power-down mode. The CPU clock rate can also be controlled as needed by changing clock sources, reconfiguring PLL values, and/or altering the CPU clock divider value. This power control mechanism allows a trade-off of power versus processing speed based on application requirements. In addition, a register is provided for shutting down the clocks to individual on-chip peripherals. This register allows fine-tuning of power

- 1. CRP1 disables access to the chip via the SWD and allows partial flash update (excluding flash sector 0) using a limited set of the ISP commands. This mode is useful when CRP is required and flash field updates are needed but all sectors cannot be erased.

- 2. CRP2 disables access to the chip via the SWD and only allows full flash erase and update using a reduced set of the ISP commands.

- 3. Running an application with level CRP3 selected, fully disables any access to the chip via the SWD pins and the ISP. This mode effectively disables ISP override using PIO0\_1 pin as well. If necessary, the application must provide a flash update mechanism using IAP calls or using a call to the reinvoke ISP command to enable flash update via the USART.

### CAUTION

If level three Code Read Protection (CRP3) is selected, no future factory testing can be performed on the device.

In addition to the three CRP levels, sampling of pin PIO0\_1 for valid user code can be disabled. For details, see the *LPC11Uxx user manual*.

### 7.17.6.4 APB interface

The APB peripherals are located on one APB bus.

#### 7.17.6.5 AHBLite

The AHBLite connects the CPU bus of the ARM Cortex-M0 to the flash memory, the main static RAM, and the ROM.

#### 7.17.6.6 External interrupt inputs

All GPIO pins can be level or edge sensitive interrupt inputs.

### 32-bit ARM Cortex-M0 microcontroller

| Symbol                                      | Parameter                                                                   | Conditions                                                                                                                                                                                                   |         | Min         | Typ <u>[1]</u> | Max         | Unit |

|---------------------------------------------|-----------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------|-------------|----------------|-------------|------|

| l <sup>2</sup> C-bus                        | pins (PIO0_4 and PIO0_5                                                     | 5)                                                                                                                                                                                                           |         |             |                |             |      |

| V <sub>IH</sub>                             | HIGH-level input voltage                                                    |                                                                                                                                                                                                              |         | $0.7V_{DD}$ | -              | -           | V    |

| V <sub>IL</sub>                             | LOW-level input voltage                                                     |                                                                                                                                                                                                              |         | -           | -              | $0.3V_{DD}$ | V    |

| V <sub>hys</sub>                            | hysteresis voltage                                                          |                                                                                                                                                                                                              |         | -           | $0.05V_{DD}$   | -           | V    |

| I <sub>OL</sub>                             | LOW-level output<br>current                                                 | $\label{eq:Vol} \begin{split} V_{OL} &= 0.4 \text{ V}; \ l^2C\text{-bus pins configured} \\ \text{as standard mode pins} \\ 2.0 \text{ V} &\leq \text{V}_{DD} \leq 3.6 \text{ V} \end{split}$                |         | 3.5         | -              | -           | mA   |

|                                             |                                                                             | $1.8~V \leq V_{DD} < 2.0~V$                                                                                                                                                                                  |         | 3           | -              | -           |      |

| I <sub>OL</sub> LOW-level output<br>current |                                                                             | $\label{eq:Volume} \begin{array}{l} V_{OL} = 0.4 \ \text{V}; \ \text{I}^2\text{C}\text{-bus pins configured} \\ \text{as Fast-mode Plus pins} \\ 2.0 \ \text{V} \leq V_{DD} \leq 3.6 \ \text{V} \end{array}$ |         | 20          | -              | -           | mA   |

|                                             |                                                                             | $1.8 \text{ V} \le \text{V}_{\text{DD}} < 2.0 \text{ V}$                                                                                                                                                     |         | 16          | -              | -           |      |

| ILI                                         | input leakage current                                                       | $V_{I} = V_{DD}$                                                                                                                                                                                             | [15]    | -           | 2              | 4           | μA   |

|                                             |                                                                             | V <sub>1</sub> = 5 V                                                                                                                                                                                         |         | -           | 10             | 22          | μA   |

| Oscillate                                   | or pins                                                                     |                                                                                                                                                                                                              |         | I           |                |             |      |

| V <sub>i(xtal)</sub>                        | crystal input voltage                                                       |                                                                                                                                                                                                              |         | -0.5        | 1.8            | 1.95        | V    |

| V <sub>o(xtal)</sub>                        | crystal output voltage                                                      |                                                                                                                                                                                                              |         | -0.5        | 1.8            | 1.95        | V    |

| USB pin                                     | S                                                                           |                                                                                                                                                                                                              |         | I           |                |             |      |

| I <sub>OZ</sub>                             | OFF-state output current                                                    | 0 V < V <sub>I</sub> < 3.3 V                                                                                                                                                                                 | [2]     | -           | -              | ±10         | μA   |

| V <sub>BUS</sub>                            | bus supply voltage                                                          |                                                                                                                                                                                                              | [2]     | -           | -              | 5.25        | V    |

| V <sub>DI</sub>                             | differential input sensitivity voltage                                      | (D+) – (D–)                                                                                                                                                                                                  | [2]     | 0.2         | -              | -           | V    |

| V <sub>CM</sub>                             | differential common mode voltage range                                      | includes V <sub>DI</sub> range                                                                                                                                                                               | [2]     | 0.8         | -              | 2.5         | V    |

| V <sub>th(rs)se</sub>                       | single-ended receiver<br>switching threshold<br>voltage                     |                                                                                                                                                                                                              | [2]     | 0.8         | -              | 2.0         | V    |

| V <sub>OL</sub>                             | LOW-level output voltage                                                    | for low-/full-speed; $R_L$ of 1.5 k $\Omega$ to 3.6 V                                                                                                                                                        | [2]     | -           | -              | 0.18        | V    |

| V <sub>OH</sub>                             | HIGH-level output voltage                                                   | driven; for low-/full-speed; $R_L$ of 15 k $\Omega$ to GND                                                                                                                                                   | [2]     | 2.8         | -              | 3.5         | V    |

| C <sub>trans</sub>                          | transceiver capacitance                                                     | pin to GND                                                                                                                                                                                                   | [2]     | -           | -              | 20          | pF   |

| Z <sub>DRV</sub>                            | driver output<br>impedance for driver<br>which is not high-speed<br>capable | with 33 $\Omega$ series resistor; steady state drive                                                                                                                                                         | [16][2] | 36          | -              | 44.1        | Ω    |

# Table 5. Static characteristics ...continued

$T_{amb} = -40 \text{ °C to } +85 \text{ °C}$ , unless otherwise specified.

| Symbo                                       | ol Parameter                                  | Conditions              | Min      | Typ <u>[1]</u> | Max | Unit |

|---------------------------------------------|-----------------------------------------------|-------------------------|----------|----------------|-----|------|

| Pin ca                                      | pacitance                                     |                         | <u>.</u> | <u>.</u>       |     |      |

| C <sub>io</sub> input/output<br>capacitance | pins configured for analog function           | -                       | -        | 7.1            | pF  |      |

|                                             | I <sup>2</sup> C-bus pins (PIO0_4 and PIO0_5) | -                       | -        | 2.5            | pF  |      |

|                                             |                                               | pins configured as GPIO | -        | -              | 2.8 | pF   |

#### Table 5. Static characteristics ...continued

$T_{amb} = -40 \ ^{\circ}C$  to +85  $^{\circ}C$ , unless otherwise specified.

[1] Typical ratings are not guaranteed. The values listed are at room temperature (25 °C), nominal supply voltages.

[2] For USB operation 3.0 V  $\leq$  V\_{DD}  $\leq$  3.6 V. Guaranteed by design.

[3] IRC enabled; system oscillator disabled; system PLL disabled.

[4] I<sub>DD</sub> measurements were performed with all pins configured as GPIO outputs driven LOW and pull-up resistors disabled.

[5] BOD disabled.

- [6] All peripherals disabled in the AHBCLKCTRL register. Peripheral clocks to USART, SSP0/1 disabled in the SYSCON block.

- [7] USB\_DP and USB\_DM pulled LOW externally.

- [8] Low-current mode PWR\_LOW\_CURRENT selected when running the set\_power routine in the power profiles.

[9] IRC disabled; system oscillator enabled; system PLL enabled.

[10] WAKEUP pin pulled HIGH externally. An external pull-up resistor is required on the RESET pin for the Deep power-down mode.

- [11] Including voltage on outputs in 3-state mode.

- [12]  $V_{DD}$  supply voltage must be present.

- [13] 3-state outputs go into 3-state mode in Deep power-down mode.

- [14] Allowed as long as the current limit does not exceed the maximum current allowed by the device.

[15] To V<sub>SS</sub>.

[16] Includes external resistors of 33  $\Omega\pm$  1 % on USB\_DP and USB\_DM.

# **NXP Semiconductors**

# LPC11U2x

### 32-bit ARM Cortex-M0 microcontroller

### 32-bit ARM Cortex-M0 microcontroller

# 9.1 BOD static characteristics

# Table 7. BOD static characteristics<sup>[1]</sup>

$T_{amb} = 25 \ ^{\circ}C.$

| Symbol          | Parameter         | Conditions        | Min | Тур  | Max | Unit |

|-----------------|-------------------|-------------------|-----|------|-----|------|

| V <sub>th</sub> | threshold voltage | interrupt level 1 |     |      |     |      |

|                 |                   | assertion         | -   | 2.22 | -   | V    |

|                 |                   | de-assertion      | -   | 2.35 | -   | V    |

|                 |                   | interrupt level 2 |     |      |     |      |

|                 |                   | assertion         | -   | 2.52 | -   | V    |

|                 |                   | de-assertion      | -   | 2.66 | -   | V    |

|                 |                   | interrupt level 3 |     |      |     |      |

|                 |                   | assertion         | -   | 2.80 | -   | V    |

|                 |                   | de-assertion      | -   | 2.90 | -   | V    |

|                 |                   | reset level 0     |     |      |     |      |

|                 |                   | assertion         | -   | 1.46 | -   | V    |

|                 |                   | de-assertion      | -   | 1.63 | -   | V    |

|                 |                   | reset level 1     |     |      |     |      |

|                 |                   | assertion         | -   | 2.06 | -   | V    |

|                 |                   | de-assertion      | -   | 2.15 | -   | V    |

|                 |                   | reset level 2     |     |      |     |      |

|                 |                   | assertion         | -   | 2.35 | -   | V    |

|                 |                   | de-assertion      | -   | 2.43 | -   | V    |

|                 |                   | reset level 3     |     |      |     |      |

|                 |                   | assertion         | -   | 2.63 | -   | V    |

|                 |                   | de-assertion      | -   | 2.71 | -   | V    |

[1] Interrupt levels are selected by writing the level value to the BOD control register BODCTRL, see *the* LPC11Uxx user manual.

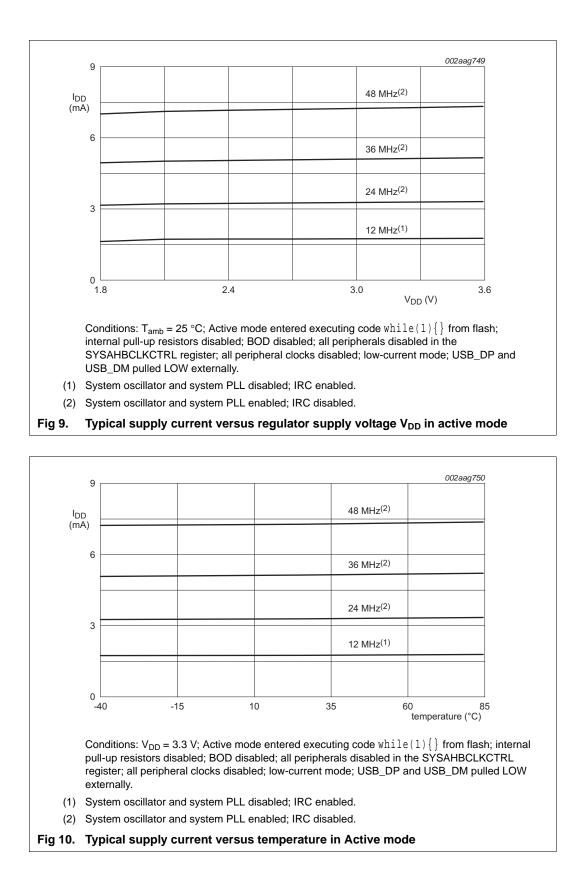

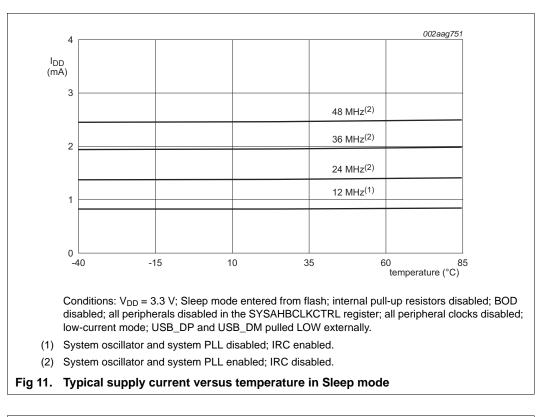

### 9.2 Power consumption

Power measurements in Active, Sleep, and Deep-sleep modes were performed under the following conditions (see the *LPC11Uxx user manual*):

- Configure all pins as GPIO with pull-up resistor disabled in the IOCON block.

- Configure GPIO pins as outputs using the GPIOnDIR registers.

- Write 0 to all GPIOnDATA registers to drive the outputs LOW.

### 32-bit ARM Cortex-M0 microcontroller

### 32-bit ARM Cortex-M0 microcontroller

### 32-bit ARM Cortex-M0 microcontroller

# **10.** Dynamic characteristics

### 10.1 Flash memory

### Table 9. Flash characteristics

$T_{amb} = -40$  °C to +85 °C, unless otherwise specified.

| Symbol            | Parameter        | Conditions                                |     | Min   | Тур    | Max  | Unit   |

|-------------------|------------------|-------------------------------------------|-----|-------|--------|------|--------|

| N <sub>endu</sub> | endurance        |                                           | [1] | 10000 | 100000 | -    | cycles |

| t <sub>ret</sub>  | retention time   | powered                                   |     | 10    | -      | -    | years  |

|                   |                  | unpowered                                 |     | 20    | -      | -    | years  |

| t <sub>er</sub>   | erase time       | sector or multiple<br>consecutive sectors |     | 95    | 100    | 105  | ms     |

| t <sub>prog</sub> | programming time |                                           | [2] | 0.95  | 1      | 1.05 | ms     |

[1] Number of program/erase cycles.

[2] Programming times are given for writing 256 bytes from RAM to the flash. Data must be written to the flash in blocks of 256 bytes.

#### Table 10. EEPROM characteristics

$T_{amb} = -40 \text{ }^{\circ}\text{C}$  to +85  $\text{}^{\circ}\text{C}$ ;  $V_{DD} = 2.7 \text{ V}$  to 3.6 V. Based on JEDEC NVM qualification. Failure rate < 10 ppm for parts as specified below.

| Symbol            | Parameter           | Conditions | Min    | Тур     | Max | Unit   |

|-------------------|---------------------|------------|--------|---------|-----|--------|

| N <sub>endu</sub> | endurance           |            | 100000 | 1000000 | -   | cycles |

| t <sub>ret</sub>  | retention time      | powered    | 100    | 200     | -   | years  |

|                   |                     | unpowered  | 150    | 300     | -   | years  |

| t <sub>prog</sub> | programming<br>time | 64 bytes   | -      | 2.9     | -   | ms     |

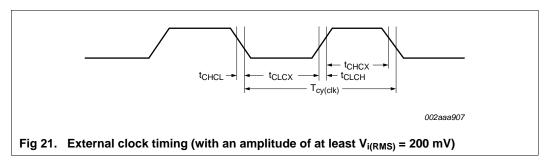

# 10.2 External clock

#### Table 11. Dynamic characteristic: external clock

$T_{amb} = -40 \ ^{\circ}C$  to +85  $^{\circ}C$ ;  $V_{DD}$  over specified ranges.[1]

| Symbol               | Parameter            | Conditions | Min                             | Typ[2] | Max  | Unit |

|----------------------|----------------------|------------|---------------------------------|--------|------|------|

| f <sub>osc</sub>     | oscillator frequency |            | 1                               | -      | 25   | MHz  |

| T <sub>cy(clk)</sub> | clock cycle time     |            | 40                              | -      | 1000 | ns   |

| t <sub>CHCX</sub>    | clock HIGH time      |            | $T_{\text{cy(clk)}} \times 0.4$ | -      | -    | ns   |

| t <sub>CLCX</sub>    | clock LOW time       |            | $T_{\text{cy(clk)}} \times 0.4$ | -      | -    | ns   |

| t <sub>CLCH</sub>    | clock rise time      |            | -                               | -      | 5    | ns   |

| t <sub>CHCL</sub>    | clock fall time      |            | -                               | -      | 5    | ns   |

[1] Parameters are valid over operating temperature range unless otherwise specified.

[2] Typical ratings are not guaranteed. The values listed are at room temperature (25 °C), nominal supply voltages.

#### 32-bit ARM Cortex-M0 microcontroller

### 10.3 Internal oscillators

#### Table 12. Dynamic characteristics: IRC

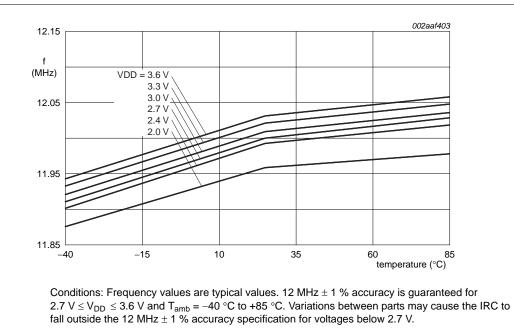

$T_{amb} = -40 \ ^{\circ}C \ to +85 \ ^{\circ}C; 2.7 \ V \le V_{DD} \le 3.6 \ V_{11}.$

| Symbol               | Parameter                           | Conditions | Min   | Typ[2] | Max   | Unit |

|----------------------|-------------------------------------|------------|-------|--------|-------|------|

| f <sub>osc(RC)</sub> | internal RC oscillator<br>frequency | -          | 11.88 | 12     | 12.12 | MHz  |

[1] Parameters are valid over operating temperature range unless otherwise specified.

[2] Typical ratings are not guaranteed. The values listed are at room temperature (25 °C), nominal supply voltages.

Fig 22. Internal RC oscillator frequency versus temperature

#### Table 13. Dynamic characteristics: Watchdog oscillator

| Symbol                | Parameter | Conditions                                                  |        | Min | Typ[1] | Max | Unit |

|-----------------------|-----------|-------------------------------------------------------------|--------|-----|--------|-----|------|

| f <sub>osc(int)</sub> |           | DIVSEL = 0x1F, FREQSEL = 0x1<br>in the WDTOSCCTRL register; | [2][3] | -   | 7.8    | -   | kHz  |

|                       |           | DIVSEL = 0x00, FREQSEL = 0xF<br>in the WDTOSCCTRL register  | [2][3] | -   | 1700   | -   | kHz  |

[1] Typical ratings are not guaranteed. The values listed are at nominal supply voltages.

All information provided in this document is subject to legal disclaimers. © NXP B.V. 2014. All rights reserved.

### 32-bit ARM Cortex-M0 microcontroller

# 10.7 USB interface

### Table 17. Dynamic characteristics: USB pins (full-speed)

$C_L = 50 \ pF; \ R_{pu} = 1.5 \ k\Omega \ on \ D+ \ to \ V_{DD}; \ 3.0 \ V \le V_{DD} \le 3.6 \ V.$

| Symbol             | Parameter                                                   | Conditions                                  | Min   | Тур | Max   | Unit |

|--------------------|-------------------------------------------------------------|---------------------------------------------|-------|-----|-------|------|

| t <sub>r</sub>     | rise time                                                   | 10 % to 90 %                                | 8.5   | -   | 13.8  | ns   |

| t <sub>f</sub>     | fall time                                                   | 10 % to 90 %                                | 7.7   | -   | 13.7  | ns   |

| t <sub>FRFM</sub>  | differential rise and fall time matching                    | t <sub>r</sub> / t <sub>f</sub>             | -     | -   | 109   | %    |

| V <sub>CRS</sub>   | output signal crossover voltage                             |                                             | 1.3   | -   | 2.0   | V    |

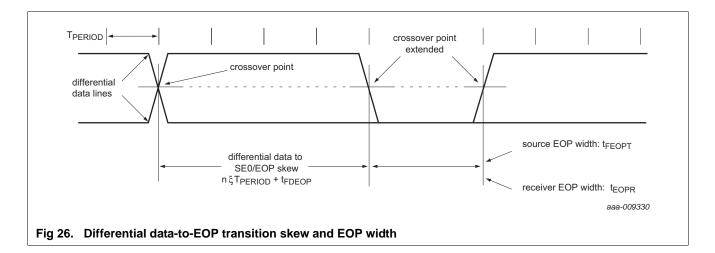

| t <sub>FEOPT</sub> | source SE0 interval of EOP                                  | see Figure 26                               | 160   | -   | 175   | ns   |

| t <sub>FDEOP</sub> | source jitter for differential transition to SE0 transition | see Figure 26                               | -2    | -   | +5    | ns   |

| t <sub>JR1</sub>   | receiver jitter to next transition                          |                                             | -18.5 | -   | +18.5 | ns   |

| t <sub>JR2</sub>   | receiver jitter for paired transitions                      | 10 % to 90 %                                | -9    | -   | +9    | ns   |

| t <sub>EOPR</sub>  | EOP width at receiver                                       | must accept as [1]<br>EOP; see<br>Figure 26 | 82    | -   | -     | ns   |

[1] Characterized but not implemented as production test. Guaranteed by design.

### 32-bit ARM Cortex-M0 microcontroller

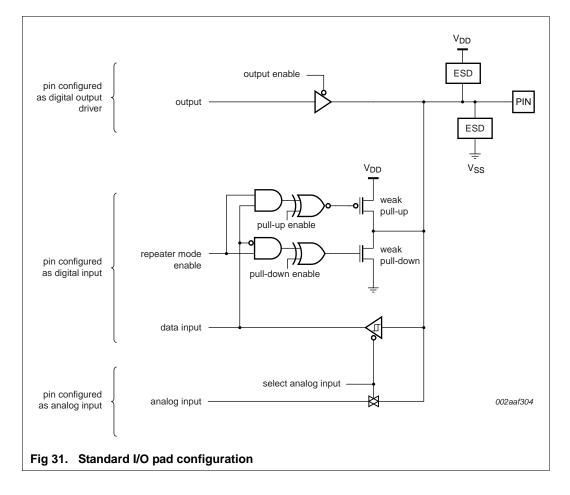

# 11.4 Standard I/O pad configuration

Figure 31 shows the possible pin modes for standard I/O pins with analog input function:

- Digital output driver

- Digital input: Pull-up enabled/disabled

- Digital input: Pull-down enabled/disabled

- Digital input: Repeater mode enabled/disabled

- Analog input

LPC11U2X

56 of 74

32-bit ARM Cortex-M0 microcontroller

# 14. Abbreviations

| Table 20. Abbreviations |                                                         |

|-------------------------|---------------------------------------------------------|

| Acronym                 | Description                                             |

| A/D                     | Analog-to-Digital                                       |

| ADC                     | Analog-to-Digital Converter                             |

| AHB                     | Advanced High-performance Bus                           |

| APB                     | Advanced Peripheral Bus                                 |

| BOD                     | BrownOut Detection                                      |

| GPIO                    | General Purpose Input/Output                            |

| JTAG                    | Joint Test Action Group                                 |

| PLL                     | Phase-Locked Loop                                       |

| RC                      | Resistor-Capacitor                                      |

| SPI                     | Serial Peripheral Interface                             |

| SSI                     | Serial Synchronous Interface                            |

| SSP                     | Synchronous Serial Port                                 |

| TAP                     | Test Access Port                                        |

| USART                   | Universal Synchronous Asynchronous Receiver/Transmitter |

# 15. References

- [1] LPC11U2x User manual UM10462: http://www.nxp.com/documents/user\_manual/UM10462.pdf

- [2] LPC11U2x Errata sheet: http://www.nxp.com/documents/errata\_sheet/ES\_LPC11U2X.pdf