Welcome to **E-XFL.COM**

What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded - Microcontrollers</u>"

| Details                    |                                                                            |

|----------------------------|----------------------------------------------------------------------------|

| Product Status             | Active                                                                     |

| Core Processor             | ARM® Cortex®-M0                                                            |

| Core Size                  | 32-Bit Single-Core                                                         |

| Speed                      | 50MHz                                                                      |

| Connectivity               | I <sup>2</sup> C, Microwire, SPI, SSI, SSP, UART/USART, USB                |

| Peripherals                | Brown-out Detect/Reset, POR, WDT                                           |

| Number of I/O              | 26                                                                         |

| Program Memory Size        | 32KB (32K x 8)                                                             |

| Program Memory Type        | FLASH                                                                      |

| EEPROM Size                | 2K x 8                                                                     |

| RAM Size                   | 8K x 8                                                                     |

| Voltage - Supply (Vcc/Vdd) | 1.8V ~ 3.6V                                                                |

| Data Converters            | A/D 8x10b                                                                  |

| Oscillator Type            | Internal                                                                   |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                          |

| Mounting Type              | Surface Mount                                                              |

| Package / Case             | 32-VFQFN Exposed Pad                                                       |

| Supplier Device Package    | 33-HVQFN (5x5)                                                             |

| Purchase URL               | https://www.e-xfl.com/product-detail/nxp-semiconductors/lpc11u24fhi33-301y |

#### 32-bit ARM Cortex-M0 microcontroller

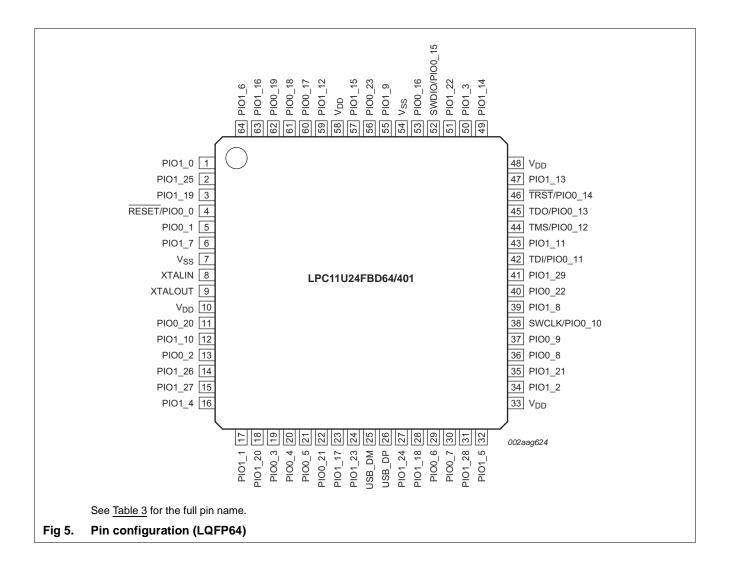

# 6.2 Pin description

Table 3 shows all pins and their assigned digital or analog functions in order of the GPIO port number. The default function after reset is listed first. All port pins have internal pull-up resistors enabled after reset except for the true open-drain pins PIO0\_4 and PIO0\_5.

Every port pin has a corresponding IOCON register for programming the digital or analog function, the pull-up/pull-down configuration, the repeater, and the open-drain modes.

The USART, counter/timer, and SSP functions are available on more than one port pin.

Table 3. Pin description

| Symbol Symbol                                 | Pin HVQFN33                                                                                                                                                                  | Pin TFBGA48 | Pin LQFP48                                                                                                                                                                                                                                                                                                                                                                       | Pin LQFP64 |     | Reset state [1] | Туре | Description                                                                                                                                                                                                        |

|-----------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------|-----|-----------------|------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| RESET/PIO0_0                                  | 2 C1 3 4 [2] I; PU I RESET — External reset A LOW-going pulse as sh resets the device, causing take on their default state to begin at address 0. Th debug select input. LOW |             | RESET — External reset input with 20 ns glitch filter. A LOW-going pulse as short as 50 ns on this pin resets the device, causing I/O ports and peripherals to take on their default states, and processor execution to begin at address 0. This pin also serves as the debug select input. LOW level selects the JTAG boundary scan. HIGH level selects the ARM SWD debug mode. |            |     |                 |      |                                                                                                                                                                                                                    |

|                                               |                                                                                                                                                                              |             |                                                                                                                                                                                                                                                                                                                                                                                  |            |     |                 |      | In deep power-down mode, this pin must be pulled HIGH externally. The RESET pin can be left unconnected or be used as a GPIO pin if an external RESET function is not needed and Deep power-down mode is not used. |

|                                               |                                                                                                                                                                              |             |                                                                                                                                                                                                                                                                                                                                                                                  |            |     | -               | I/O  | PIO0_0 — General purpose digital input/output pin.                                                                                                                                                                 |

| PIO0_1/CLKOUT/<br>CT32B0_MAT2/<br>USB_FTOGGLE | 3                                                                                                                                                                            | C2          | 4                                                                                                                                                                                                                                                                                                                                                                                | 5          | [3] | I; PU           | I/O  | PIO0_1 — General purpose digital input/output pin. A LOW level on this pin during reset starts the ISP command handler or the USB device enumeration.                                                              |

|                                               |                                                                                                                                                                              |             |                                                                                                                                                                                                                                                                                                                                                                                  |            |     | -               | 0    | CLKOUT — Clockout pin.                                                                                                                                                                                             |

|                                               |                                                                                                                                                                              |             |                                                                                                                                                                                                                                                                                                                                                                                  |            |     | -               | 0    | CT32B0_MAT2 — Match output 2 for 32-bit timer 0.                                                                                                                                                                   |

|                                               |                                                                                                                                                                              |             |                                                                                                                                                                                                                                                                                                                                                                                  |            |     | -               | 0    | USB_FTOGGLE — USB 1 ms Start-of-Frame signal.                                                                                                                                                                      |

| PIO0_2/SSEL0/                                 | 8                                                                                                                                                                            | F1          | 10                                                                                                                                                                                                                                                                                                                                                                               | 13         | [3] | I; PU           | I/O  | PIO0_2 — General purpose digital input/output pin.                                                                                                                                                                 |

| CT16B0_CAP0                                   |                                                                                                                                                                              |             |                                                                                                                                                                                                                                                                                                                                                                                  |            |     | -               | I/O  | SSEL0 — Slave select for SSP0.                                                                                                                                                                                     |

|                                               |                                                                                                                                                                              |             |                                                                                                                                                                                                                                                                                                                                                                                  |            |     | -               | I    | CT16B0_CAP0 — Capture input 0 for 16-bit timer 0.                                                                                                                                                                  |

| PIO0_3/USB_VBUS                               | 9                                                                                                                                                                            | H2          | 14                                                                                                                                                                                                                                                                                                                                                                               | 19         | [3] | I; PU           | I/O  | PIO0_3 — General purpose digital input/output pin. A LOW level on this pin during reset starts the ISP command handler. A HIGH level during reset starts the USB device enumeration.                               |

|                                               |                                                                                                                                                                              |             |                                                                                                                                                                                                                                                                                                                                                                                  |            |     | -               | I    | USB_VBUS — Monitors the presence of USB bus power.                                                                                                                                                                 |

| PIO0_4/SCL                                    | 10                                                                                                                                                                           | G3          | 15                                                                                                                                                                                                                                                                                                                                                                               | 20         | [4] | I; IA           | I/O  | PIO0_4 — General purpose digital input/output pin (open-drain).                                                                                                                                                    |

|                                               |                                                                                                                                                                              |             |                                                                                                                                                                                                                                                                                                                                                                                  |            |     | -               | I/O  | <b>SCL</b> — I <sup>2</sup> C-bus clock input/output (open-drain). High-current sink only if I <sup>2</sup> C Fast-mode Plus is selected in the I/O configuration register.                                        |

Table 3. Pin description

| Symbol                             | Pin HVQFN33 | Pin TFBGA48 | Pin LQFP48 | Pin LQFP64 |            | Reset<br>state<br>[1] | Туре | Description                                                                                                                                                         |

|------------------------------------|-------------|-------------|------------|------------|------------|-----------------------|------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| PIO0_5/SDA                         | 11          | НЗ          | 16         | 21         | <u>[4]</u> | I; IA                 | I/O  | PIO0_5 — General purpose digital input/output pin (open-drain).                                                                                                     |

|                                    |             |             |            |            |            | -                     | I/O  | SDA — I <sup>2</sup> C-bus data input/output (open-drain). High-current sink only if I <sup>2</sup> C Fast-mode Plus is selected in the I/O configuration register. |

| PIO0_6/USB_CONNECT/                | 15          | H6          | 22         | 29         | [3]        | I; PU                 | I/O  | PIO0_6 — General purpose digital input/output pin.                                                                                                                  |

| SCK0                               |             |             |            |            |            | -                     | 0    | USB_CONNECT — Signal used to switch an external 1.5 kΩ resistor under software control. Used with the SoftConnect USB feature.                                      |

|                                    |             |             |            |            |            | -                     | I/O  | SCK0 — Serial clock for SSP0.                                                                                                                                       |

| PIO0_7/CTS                         | 16          | G7          | 23         | 30         | [5]        | I; PU                 | I/O  | PIO0_7 — General purpose digital input/output pin (high-current output driver).                                                                                     |

|                                    |             |             |            |            |            | -                     | I    | CTS — Clear To Send input for USART.                                                                                                                                |

| PIO0_8/MISO0/                      | 17          | F8          | 27         | 36         | [3]        | I; PU                 | I/O  | PIO0_8 — General purpose digital input/output pin.                                                                                                                  |

| CT16B0_MAT0                        |             |             |            |            |            | -                     | I/O  | MISO0 — Master In Slave Out for SSP0.                                                                                                                               |

|                                    |             |             |            |            |            | -                     | 0    | CT16B0_MAT0 — Match output 0 for 16-bit timer 0.                                                                                                                    |

| PIO0_9/MOSI0/                      | 18          | F7          | 28         | 37         | [3]        | I; PU                 | I/O  | PIO0_9 — General purpose digital input/output pin.                                                                                                                  |

| CT16B0_MAT1                        |             |             |            |            |            | -                     | I/O  | MOSI0 — Master Out Slave In for SSP0.                                                                                                                               |

|                                    |             |             |            |            |            | -                     | 0    | CT16B0_MAT1 — Match output 1 for 16-bit timer 0.                                                                                                                    |

| SWCLK/PIO0_10/SCK0/<br>CT16B0_MAT2 | 19          | E7          | 29         | 38         | [3]        | I; PU                 | I    | <b>SWCLK</b> — Serial wire clock and test clock TCK for JTAG interface.                                                                                             |

|                                    |             |             |            |            |            | -                     | I/O  | PIO0_10 — General purpose digital input/output pin.                                                                                                                 |

|                                    |             |             |            |            |            | -                     | 0    | SCK0 — Serial clock for SSP0.                                                                                                                                       |

|                                    |             |             |            |            |            | -                     | 0    | CT16B0_MAT2 — Match output 2 for 16-bit timer 0.                                                                                                                    |

| TDI/PIO0_11/AD0/                   | 21          | D8          | 32         | 42         | [6]        | I; PU                 | I    | TDI — Test Data In for JTAG interface.                                                                                                                              |

| CT32B0_MAT3                        |             |             |            |            |            | -                     | I/O  | PIO0_11 — General purpose digital input/output pin.                                                                                                                 |

|                                    |             |             |            |            |            | -                     | I    | AD0 — A/D converter, input 0.                                                                                                                                       |

|                                    |             |             |            |            |            | -                     | 0    | CT32B0_MAT3 — Match output 3 for 32-bit timer 0.                                                                                                                    |

| TMS/PIO0_12/AD1/                   | 22          | C7          | 33         | 44         | [6]        | I; PU                 | I    | TMS — Test Mode Select for JTAG interface.                                                                                                                          |

| CT32B1_CAP0                        |             |             |            |            |            | -                     | I/O  | PIO_12 — General purpose digital input/output pin.                                                                                                                  |

|                                    |             |             |            |            |            | -                     | I    | AD1 — A/D converter, input 1.                                                                                                                                       |

|                                    | L           | L           | L          |            |            | -                     | I    | CT32B1_CAP0 — Capture input 0 for 32-bit timer 1.                                                                                                                   |

| TDO/PIO0_13/AD2/                   | 23          | C8          | 34         | 45         | [6]        | I; PU                 | 0    | TDO — Test Data Out for JTAG interface.                                                                                                                             |

| CT32B1_MAT0                        |             |             |            |            |            | -                     | I/O  | PIO0_13 — General purpose digital input/output pin.                                                                                                                 |

|                                    |             |             |            |            |            | -                     | I    | AD2 — A/D converter, input 2.                                                                                                                                       |

|                                    |             |             |            |            |            | -                     | 0    | CT32B1_MAT0 — Match output 0 for 32-bit timer 1.                                                                                                                    |

#### 32-bit ARM Cortex-M0 microcontroller

### **7.3 SRAM**

The LPC11U2x contain a total of 8 kB or 10 kB on-chip static RAM memory.

# 7.4 On-chip ROM

The on-chip ROM contains the boot loader and the following Application Programming Interfaces (APIs):

- In-System Programming (ISP) and In-Application Programming (IAP) support for flash

- IAP support for EEPROM

- USB API

- Power profiles for configuring power consumption and PLL settings

- 32-bit integer division routines

## 7.5 Memory map

The LPC11U2x incorporates several distinct memory regions, shown in the following figures. Figure 6 shows the overall map of the entire address space from the user program viewpoint following reset. The interrupt vector area supports address remapping.

The AHB (Advanced High-performance Bus) peripheral area is 2 MB in size and is divided to allow for up to 128 peripherals. The APB (Advanced Peripheral Bus) peripheral area is 512 kB in size and is divided to allow for up to 32 peripherals. Each peripheral of either type is allocated 16 kB of space. This addressing scheme allows simplifying the address decoding for each peripheral.

#### 32-bit ARM Cortex-M0 microcontroller

- Four programmable interrupt priority levels, with hardware priority level masking.

- Software interrupt generation.

## 7.6.2 Interrupt sources

Each peripheral device has one interrupt line connected to the NVIC but can have several interrupt flags. Individual interrupt flags can also represent more than one interrupt source.

#### 7.7 IOCON block

The IOCON block allows selected pins of the microcontroller to have more than one function. Configuration registers control the multiplexers to allow connection between the pin and the on-chip peripherals.

Connect peripherals to the appropriate pins before activating the peripheral and before enabling any related interrupt. Activity of any enabled peripheral function that is not mapped to a related pin is treated as undefined.

#### 7.7.1 Features

- Programmable pull-up, pull-down, or repeater mode.

- All GPIO pins (except PIO0\_4 and PIO0\_5) are pulled up to 3.3 V (V<sub>DD</sub> = 3.3 V) if their pull-up resistor is enabled.

- Programmable pseudo open-drain mode.

- Programmable 10 ns glitch filter on pins PIO0\_22, PIO0\_23, and PIO0\_11 to PIO0\_16. The glitch filter is turned on by default.

- Programmable hysteresis.

- Programmable input inverter.

## 7.8 General-Purpose Input/Output GPIO

The GPIO registers control device pin functions that are not connected to a specific peripheral function. Pins can be dynamically configured as inputs or outputs. Multiple outputs can be set or cleared in one write operation.

LPC11U2x use accelerated GPIO functions:

- GPIO registers are a dedicated AHB peripheral so that the fastest possible I/O timing can be achieved.

- Entire port value can be written in one instruction.

Any GPIO pin providing a digital function can be programmed to generate an interrupt on a level, a rising or falling edge, or both.

The GPIO block consists of three parts:

- 1. The GPIO ports.

- 2. The GPIO pin interrupt block to control eight GPIO pins selected as pin interrupts.

- Two GPIO group interrupt blocks to control two combined interrupts from all GPIO pins.

#### 32-bit ARM Cortex-M0 microcontroller

#### 7.12.1 Features

- The I<sup>2</sup>C-interface is an I<sup>2</sup>C-bus compliant interface with open-drain pins. The I<sup>2</sup>C-bus interface supports Fast-mode Plus with bit rates up to 1 Mbit/s.

- Easy to configure as master, slave, or master/slave.

- Programmable clocks allow versatile rate control.

- Bidirectional data transfer between masters and slaves.

- Multi-master bus (no central master).

- Arbitration between simultaneously transmitting masters without corruption of serial data on the bus.

- Serial clock synchronization allows devices with different bit rates to communicate via one serial bus.

- Serial clock synchronization can be used as a handshake mechanism to suspend and resume serial transfer.

- The I<sup>2</sup>C-bus can be used for test and diagnostic purposes.

- The I<sup>2</sup>C-bus controller supports multiple address recognition and a bus monitor mode.

#### 7.13 10-bit ADC

The LPC11U2x contains one ADC. It is a single 10-bit successive approximation ADC with eight channels.

#### 7.13.1 Features

- 10-bit successive approximation ADC.

- Input multiplexing among 8 pins.

- Power-down mode.

- Measurement range 0 V to V<sub>DD</sub>.

- 10-bit conversion time ≥ 2.44 µs (up to 400 kSamples/s).

- Burst conversion mode for single or multiple inputs.

- Optional conversion on transition of input pin or timer match signal.

- Individual result registers for each ADC channel to reduce interrupt overhead.

## 7.14 General purpose external event counter/timers

The LPC11U2x includes two 32-bit counter/timers and two 16-bit counter/timers. The counter/timer is designed to count cycles of the system derived clock. It can optionally generate interrupts or perform other actions at specified timer values, based on four match registers. Each counter/timer also includes one capture input to trap the timer value when an input signal transitions, optionally generating an interrupt.

## 7.14.1 Features

- A 32-bit/16-bit timer/counter with a programmable 32-bit/16-bit prescaler.

- Counter or timer operation.

- One capture channel per timer, that can take a snapshot of the timer value when an input signal transitions. A capture event can also generate an interrupt.

LPC11U2X

#### 32-bit ARM Cortex-M0 microcontroller

consumption by eliminating all dynamic power use in any peripherals that are not required for the application. Selected peripherals have their own clock divider which provides even better power control.

## 7.17.5.1 Power profiles

The power consumption in Active and Sleep modes can be optimized for the application through simple calls to the power profile. The power configuration routine configures the LPC11U2x for one of the following power modes:

- Default mode corresponding to power configuration after reset.

- CPU performance mode corresponding to optimized processing capability.

- Efficiency mode corresponding to optimized balance of current consumption and CPU performance.

- Low-current mode corresponding to lowest power consumption.

In addition, the power profile includes routines to select the optimal PLL settings for a given system clock and PLL input clock.

Remark: When using the USB, configure the LPC11U2x in Default mode.

#### 7.17.5.2 Sleep mode

When Sleep mode is entered, the clock to the core is stopped. Resumption from the Sleep mode does not need any special sequence but re-enabling the clock to the ARM core.

In Sleep mode, execution of instructions is suspended until either a reset or interrupt occurs. Peripheral functions continue operation during Sleep mode and can generate interrupts to cause the processor to resume execution. Sleep mode eliminates dynamic power used by the processor itself, by memory systems and related controllers, and by internal buses.

### 7.17.5.3 Deep-sleep mode

In Deep-sleep mode, the LPC11U2x is in Sleep-mode and all peripheral clocks and all clock sources are off except for the IRC. The IRC output is disabled unless the IRC is selected as input to the watchdog timer. In addition all analog blocks are shut down and the flash is in stand-by mode. In Deep-sleep mode, the application can keep the watchdog oscillator and the BOD circuit running for self-timed wake-up and BOD protection.

The LPC11U2x can wake up from Deep-sleep mode via reset, selected GPIO pins, a watchdog timer interrupt, or an interrupt generating USB port activity.

Deep-sleep mode saves power and allows for short wake-up times.

#### 7.17.5.4 Power-down mode

In Power-down mode, the LPC11U2x is in Sleep-mode and all peripheral clocks and all clock sources are off except for watchdog oscillator if selected. In addition all analog blocks and the flash are shut down. In Power-down mode, the application can keep the BOD circuit running for BOD protection.

The LPC11U2x can wake up from Power-down mode via reset, selected GPIO pins, a watchdog timer interrupt, or an interrupt generating USB port activity.

## 32-bit ARM Cortex-M0 microcontroller

# 9. Static characteristics

Table 5. Static characteristics

$T_{amb} = -40$  °C to +85 °C, unless otherwise specified.

| Symbol           | Parameter                               | Conditions                                                                |        | Min                | Typ[1] | Max                | Unit |

|------------------|-----------------------------------------|---------------------------------------------------------------------------|--------|--------------------|--------|--------------------|------|

| $V_{DD}$         | supply voltage (core and external rail) |                                                                           | [2]    | 1.8                | 3.3    | 3.6                | V    |

| I <sub>DD</sub>  | supply current                          | $ \begin{array}{c ccccccccccccccccccccccccccccccccccc$                    |        |                    |        |                    |      |

|                  |                                         |                                                                           |        |                    |        |                    |      |

|                  |                                         | executed from flash;                                                      |        |                    |        |                    |      |

|                  |                                         | system clock = 12 MHz                                                     |        | -                  | 2      | -                  | mA   |

|                  |                                         | system clock = 50 MHz                                                     |        | -                  | 7      | -                  | mA   |

|                  |                                         | $V_{DD} = 3.3 \text{ V}; T_{amb} = 25 ^{\circ}\text{C};$                  |        | -                  | 1      | -                  | mA   |

|                  |                                         | Deep-sleep mode; V <sub>DD</sub> = 3.3 V;                                 | [4][7] | -                  | 360    | -                  | μΑ   |

|                  |                                         | Power-down mode; V <sub>DD</sub> = 3.3 V;                                 |        | -                  | 2      | -                  | μΑ   |

|                  |                                         |                                                                           | [10]   | -                  | 220    | -                  | nA   |

| Standard         | d port pins, RESET                      |                                                                           |        |                    |        |                    |      |

| I <sub>IL</sub>  | LOW-level input current                 | 1 -                                                                       |        | -                  | 0.5    | 10                 | nA   |

| I <sub>IH</sub>  | HIGH-level input current                |                                                                           |        | -                  | 0.5    | 10                 | nA   |

| I <sub>OZ</sub>  | OFF-state output current                |                                                                           |        | -                  | 0.5    | 10                 | nA   |

| VI               | input voltage                           |                                                                           |        | 0                  | -      | 5.0                | V    |

| Vo               | output voltage                          | output active                                                             |        | 0                  | -      | $V_{DD}$           | V    |

| V <sub>IH</sub>  | HIGH-level input voltage                |                                                                           |        | 0.7V <sub>DD</sub> | -      | -                  | V    |

| $V_{IL}$         | LOW-level input voltage                 |                                                                           |        | -                  | -      | 0.3V <sub>DD</sub> | V    |

| V <sub>hys</sub> | hysteresis voltage                      |                                                                           |        | -                  | 0.4    | -                  | V    |

| V <sub>OH</sub>  | HIGH-level output                       | $2.0 \text{ V} \le V_{DD} \le 3.6 \text{ V}; I_{OH} = -4 \text{ mA}$      |        | $V_{DD}-0.4$       | -      | -                  | V    |

|                  | voltage                                 | $1.8 \text{ V} \le \text{V}_{DD} < 2.0 \text{ V}; I_{OH} = -3 \text{ mA}$ |        | $V_{DD} - 0.4$     | -      | -                  | V    |

| $V_{OL}$         | LOW-level output                        |                                                                           |        | -                  | -      | 0.4                | V    |

|                  | voltage                                 | $1.8 \text{ V} \le \text{V}_{DD} < 2.0 \text{ V}; I_{OL} = 3 \text{ mA}$  |        | -                  | -      | 0.4                | V    |

| I <sub>OH</sub>  | HIGH-level output current               |                                                                           |        | -4                 | -      | -                  | mA   |

|                  |                                         | 1.8 V ≤ V <sub>DD</sub> < 2.0 V                                           |        | -3                 | -      | -                  | mA   |

#### 32-bit ARM Cortex-M0 microcontroller

Table 6. ADC static characteristics

$T_{amb} = -40$  °C to +85 °C unless otherwise specified; ADC frequency 4.5 MHz,  $V_{DD} = 2.5$  V to 3.6 V.

| Symbol              | Parameter                           | Conditions | Min | Тур | Max      | Unit |

|---------------------|-------------------------------------|------------|-----|-----|----------|------|

| V <sub>IA</sub>     | analog input voltage                |            | 0   | -   | $V_{DD}$ | V    |

| C <sub>ia</sub>     | analog input capacitance            |            | -   | -   | 1        | pF   |

| E <sub>D</sub>      | differential linearity error        | [1][2]     | -   | -   | ±1       | LSB  |

| E <sub>L(adj)</sub> | integral non-linearity              | [3]        | -   | -   | ±1.5     | LSB  |

| Eo                  | offset error                        | [4]        | -   | -   | ±3.5     | LSB  |

| E <sub>G</sub>      | gain error                          | <u>[5]</u> | -   | -   | 0.6      | %    |

| E <sub>T</sub>      | absolute error                      | [6]        | -   | -   | ±4       | LSB  |

| R <sub>vsi</sub>    | voltage source interface resistance |            | -   | -   | 40       | kΩ   |

| Ri                  | input resistance                    | [7][8]     | -   | -   | 2.5      | МΩ   |

- [1] The ADC is monotonic, there are no missing codes.

- [2] The differential linearity error (ED) is the difference between the actual step width and the ideal step width. See Figure 8.

- [3] The integral non-linearity (E<sub>L(adj)</sub>) is the peak difference between the center of the steps of the actual and the ideal transfer curve after appropriate adjustment of gain and offset errors. See <u>Figure 8</u>.

- [4] The offset error (E<sub>O</sub>) is the absolute difference between the straight line which fits the actual curve and the straight line which fits the ideal curve. See Figure 8.

- [5] The gain error (E<sub>G</sub>) is the relative difference in percent between the straight line fitting the actual transfer curve after removing offset error, and the straight line which fits the ideal transfer curve. See Figure 8.

- [6] The absolute error (E<sub>T</sub>) is the maximum difference between the center of the steps of the actual transfer curve of the non-calibrated ADC and the ideal transfer curve. See <u>Figure 8</u>.

- [7]  $T_{amb} = 25$  °C; maximum sampling frequency  $f_s = 400$  kSamples/s and analog input capacitance  $C_{ia} = 1$  pF.

- [8] Input resistance  $R_i$  depends on the sampling frequency fs:  $R_i = 1 / (f_s \times C_{ia})$ .

## 32-bit ARM Cortex-M0 microcontroller

## 9.1 BOD static characteristics

Table 7. BOD static characteristics [1]  $T_{amb} = 25$  °C.

| Symbol   | Parameter         | Conditions        | Min | Тур  | Max | Unit |

|----------|-------------------|-------------------|-----|------|-----|------|

| $V_{th}$ | threshold voltage | interrupt level 1 |     |      |     |      |

|          |                   | assertion         | -   | 2.22 | -   | V    |

|          |                   | de-assertion      | -   | 2.35 | -   | V    |

|          |                   | interrupt level 2 |     |      |     |      |

|          |                   | assertion         | -   | 2.52 | -   | V    |

|          |                   | de-assertion      | -   | 2.66 | -   | V    |

|          |                   | interrupt level 3 |     |      |     |      |

|          |                   | assertion         | -   | 2.80 | -   | V    |

|          |                   | de-assertion      | -   | 2.90 | -   | V    |

|          |                   | reset level 0     |     |      |     |      |

|          |                   | assertion         | -   | 1.46 | -   | V    |

|          |                   | de-assertion      | -   | 1.63 | -   | V    |

|          |                   | reset level 1     |     |      |     |      |

|          |                   | assertion         | -   | 2.06 | -   | V    |

|          |                   | de-assertion      | -   | 2.15 | -   | V    |

|          |                   | reset level 2     |     |      |     |      |

|          |                   | assertion         | -   | 2.35 | -   | V    |

|          |                   | de-assertion      | -   | 2.43 | -   | V    |

|          |                   | reset level 3     |     |      |     |      |

|          |                   | assertion         | -   | 2.63 | -   | V    |

|          |                   | de-assertion      | -   | 2.71 | -   | V    |

<sup>[1]</sup> Interrupt levels are selected by writing the level value to the BOD control register BODCTRL, see the LPC11Uxx user manual.

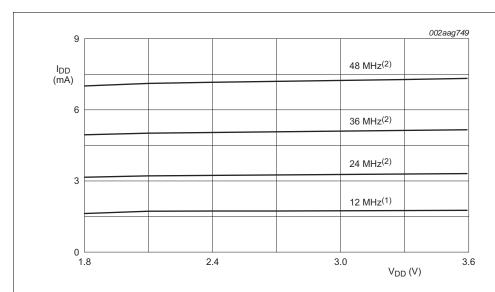

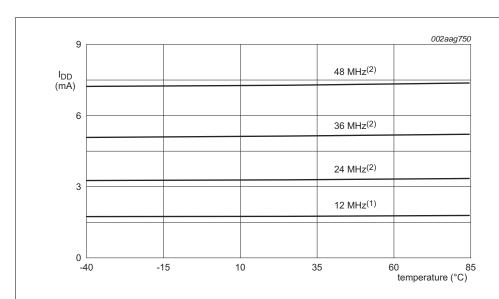

# 9.2 Power consumption

Power measurements in Active, Sleep, and Deep-sleep modes were performed under the following conditions (see the *LPC11Uxx user manual*):

- Configure all pins as GPIO with pull-up resistor disabled in the IOCON block.

- Configure GPIO pins as outputs using the GPIOnDIR registers.

- Write 0 to all GPIOnDATA registers to drive the outputs LOW.

#### 32-bit ARM Cortex-M0 microcontroller

Conditions:  $T_{amb} = 25$  °C; Active mode entered executing code while(1){} from flash; internal pull-up resistors disabled; BOD disabled; all peripherals disabled in the SYSAHBCLKCTRL register; all peripheral clocks disabled; low-current mode; USB\_DP and USB\_DM pulled LOW externally.

- (1) System oscillator and system PLL disabled; IRC enabled.

- (2) System oscillator and system PLL enabled; IRC disabled.

Fig 9. Typical supply current versus regulator supply voltage V<sub>DD</sub> in active mode

Conditions:  $V_{DD} = 3.3 \text{ V}$ ; Active mode entered executing code while(1) {} from flash; internal pull-up resistors disabled; BOD disabled; all peripherals disabled in the SYSAHBCLKCTRL register; all peripheral clocks disabled; low-current mode; USB\_DP and USB\_DM pulled LOW externally.

- (1) System oscillator and system PLL disabled; IRC enabled.

- (2) System oscillator and system PLL enabled; IRC disabled.

Fig 10. Typical supply current versus temperature in Active mode

#### 32-bit ARM Cortex-M0 microcontroller

# 10. Dynamic characteristics

## 10.1 Flash memory

Table 9. Flash characteristics

$T_{amb} = -40$  °C to +85 °C, unless otherwise specified.

| Symbol            | Parameter        | Conditions                             |     | Min   | Тур    | Max  | Unit   |

|-------------------|------------------|----------------------------------------|-----|-------|--------|------|--------|

| N <sub>endu</sub> | endurance        |                                        | [1] | 10000 | 100000 | -    | cycles |

| t <sub>ret</sub>  | retention time   | powered                                |     | 10    | -      | -    | years  |

|                   |                  | unpowered                              |     | 20    | -      | -    | years  |

| t <sub>er</sub>   | erase time       | sector or multiple consecutive sectors |     | 95    | 100    | 105  | ms     |

| t <sub>prog</sub> | programming time |                                        | [2] | 0.95  | 1      | 1.05 | ms     |

<sup>[1]</sup> Number of program/erase cycles.

#### Table 10. EEPROM characteristics

$T_{amb} = -40$  °C to +85 °C;  $V_{DD} = 2.7$  V to 3.6 V. Based on JEDEC NVM qualification. Failure rate < 10 ppm for parts as specified below.

| Symbol            | Parameter        | Conditions | Min    | Тур     | Max | Unit   |

|-------------------|------------------|------------|--------|---------|-----|--------|

| N <sub>endu</sub> | endurance        |            | 100000 | 1000000 | -   | cycles |

| t <sub>ret</sub>  | retention time   | powered    | 100    | 200     | -   | years  |

|                   |                  | unpowered  | 150    | 300     | -   | years  |

| t <sub>prog</sub> | programming time | 64 bytes   | -      | 2.9     | -   | ms     |

## 10.2 External clock

Table 11. Dynamic characteristic: external clock

$T_{amb} = -40 \, ^{\circ}\text{C}$  to +85  $^{\circ}\text{C}$ ;  $V_{DD}$  over specified ranges.[1]

| Symbol               | Parameter            | Conditions | Min                      | Typ[2] | Max  | Unit |

|----------------------|----------------------|------------|--------------------------|--------|------|------|

| f <sub>osc</sub>     | oscillator frequency |            | 1                        | -      | 25   | MHz  |

| T <sub>cy(clk)</sub> | clock cycle time     |            | 40                       | -      | 1000 | ns   |

| t <sub>CHCX</sub>    | clock HIGH time      |            | $T_{cy(clk)} \times 0.4$ | -      | -    | ns   |

| t <sub>CLCX</sub>    | clock LOW time       |            | $T_{cy(clk)} \times 0.4$ | -      | -    | ns   |

| t <sub>CLCH</sub>    | clock rise time      |            | -                        | -      | 5    | ns   |

| t <sub>CHCL</sub>    | clock fall time      |            | -                        | -      | 5    | ns   |

<sup>[1]</sup> Parameters are valid over operating temperature range unless otherwise specified.

<sup>[2]</sup> Programming times are given for writing 256 bytes from RAM to the flash. Data must be written to the flash in blocks of 256 bytes.

<sup>[2]</sup> Typical ratings are not guaranteed. The values listed are at room temperature (25  $^{\circ}$ C), nominal supply voltages.

### 32-bit ARM Cortex-M0 microcontroller

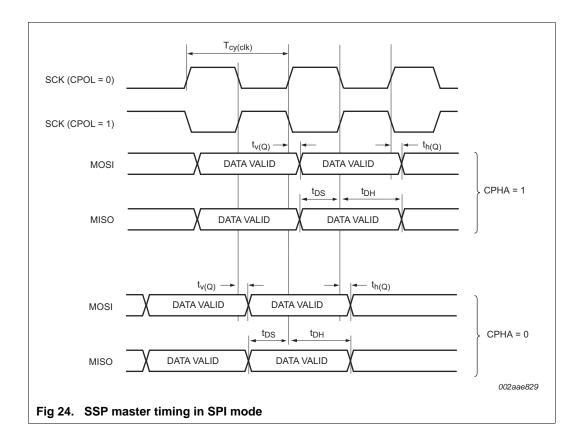

## 10.6 SSP interface

Table 16. Dynamic characteristics of SPI pins in SPI mode

| Symbol                | Parameter                      | Conditions                                        |        | Min                         | Тур | Max                            | Unit |

|-----------------------|--------------------------------|---------------------------------------------------|--------|-----------------------------|-----|--------------------------------|------|

| SPI maste             | er (in SPI mode)               |                                                   |        |                             |     |                                |      |

| T <sub>cy(clk)</sub>  | clock cycle time               | full-duplex mode                                  | [1]    | 50                          | -   | -                              | ns   |

|                       |                                | when only transmitting                            | [1]    | 40                          |     |                                | ns   |

| t <sub>DS</sub>       | data set-up time               | in SPI mode                                       | [2]    | 15                          | -   | -                              | ns   |

|                       | $2.4~V \leq V_{DD} \leq 3.6~V$ |                                                   |        |                             |     |                                |      |

|                       |                                | $2.0 \text{ V} \le \text{V}_{DD} < 2.4 \text{ V}$ | [2]    | 20                          |     |                                | ns   |

|                       |                                | $1.8 \text{ V} \le \text{V}_{DD} < 2.0 \text{ V}$ | [2]    | 24                          | -   | -                              | ns   |

| t <sub>DH</sub>       | data hold time                 | in SPI mode                                       | [2]    | 0                           | -   | -                              | ns   |

| t <sub>v(Q)</sub>     | data output valid time         | in SPI mode                                       | [2]    | -                           | -   | 10                             | ns   |

| t <sub>h(Q)</sub>     | data output hold time          | in SPI mode                                       | [2]    | 0                           | -   | -                              | ns   |

| SPI slave             | (in SPI mode)                  |                                                   |        |                             | -   | -                              |      |

| T <sub>cy(PCLK)</sub> | PCLK cycle time                |                                                   |        | 20                          | -   | -                              | ns   |

| t <sub>DS</sub>       | data set-up time               | in SPI mode                                       | [3][4] | 0                           | -   | -                              | ns   |

| t <sub>DH</sub>       | data hold time                 | in SPI mode                                       | [3][4] | $3 \times T_{cy(PCLK)} + 4$ | -   | -                              | ns   |

| t <sub>v(Q)</sub>     | data output valid time         | in SPI mode                                       | [3][4] | -                           | -   | 3 × T <sub>cy(PCLK)</sub> + 11 | ns   |

| t <sub>h(Q)</sub>     | data output hold time          | in SPI mode                                       | [3][4] | -                           | -   | 2 × T <sub>cy(PCLK)</sub> + 5  | ns   |

<sup>[1]</sup>  $T_{cy(clk)} = (SSPCLKDIV \times (1 + SCR) \times CPSDVSR) / f_{main}$ . The clock cycle time derived from the SPI bit rate  $T_{cy(clk)}$  is a function of the main clock frequency  $f_{main}$ , the SPI peripheral clock divider (SSPCLKDIV), the SPI SCR parameter (specified in the SSP0CR0 register), and the SPI CPSDVSR parameter (specified in the SPI clock prescale register).

<sup>[2]</sup>  $T_{amb} = -40 \,^{\circ}\text{C}$  to 85  $^{\circ}\text{C}$ .

<sup>[3]</sup>  $T_{cy(clk)} = 12 \times T_{cy(PCLK)}$ .

<sup>[4]</sup>  $T_{amb} = 25$  °C; for normal voltage supply range:  $V_{DD} = 3.3$  V.

#### 32-bit ARM Cortex-M0 microcontroller

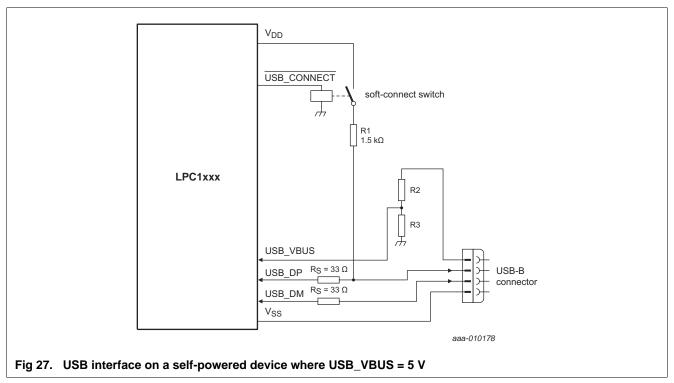

# 11. Application information

## 11.1 Suggested USB interface solutions

The USB device can be connected to the USB as self-powered device (see <u>Figure 27</u>) or bus-powered device (see <u>Figure 28</u>).

On the LPC11U2x, the PIO0\_3/USB\_VBUS pin is 5 V tolerant only when  $V_{DD}$  is applied and at operating voltage level. Therefore, if the USB\_VBUS function is connected to the USB connector and the device is self-powered, the USB\_VBUS pin must be protected for situations when  $V_{DD} = 0$  V.

If  $V_{DD}$  is always at operating level while VBUS = 5 V, the USB\_VBUS pin can be connected directly to the VBUS pin on the USB connector.

For systems where  $V_{DD}$  can be 0 V and VBUS is directly applied to the VBUS pin, precautions must be taken to reduce the voltage to below 3.6 V, which is the maximum allowable voltage on the USB\_VBUS pin in this case.

One method is to use a voltage divider to connect the USB\_VBUS pin to the VBUS on the USB connector. The voltage divider ratio should be such that the USB\_VBUS pin will be greater than  $0.7V_{DD}$  to indicate a logic HIGH while below the 3.6~V allowable maximum voltage.

For the following operating conditions

$$VBUS_{max} = 5.25 V$$

$V_{DD} = 3.6 V$ ,

the voltage divider should provide a reduction of 3.6 V/5.25 V or ~0.686 V.

LPC11U2X

## 32-bit ARM Cortex-M0 microcontroller

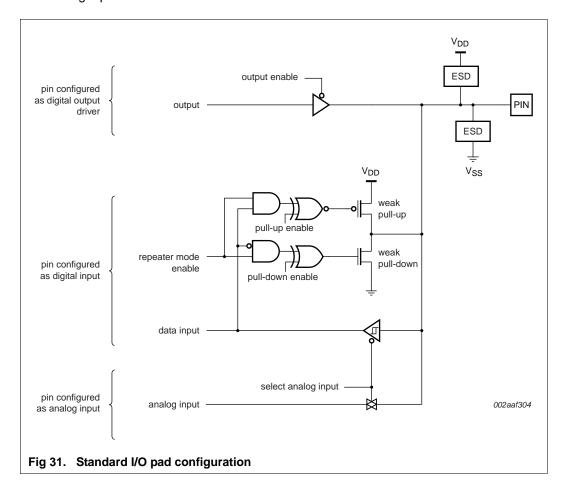

# 11.4 Standard I/O pad configuration

Figure 31 shows the possible pin modes for standard I/O pins with analog input function:

- Digital output driver

- Digital input: Pull-up enabled/disabled

- Digital input: Pull-down enabled/disabled

- · Digital input: Repeater mode enabled/disabled

- Analog input

#### 32-bit ARM Cortex-M0 microcontroller

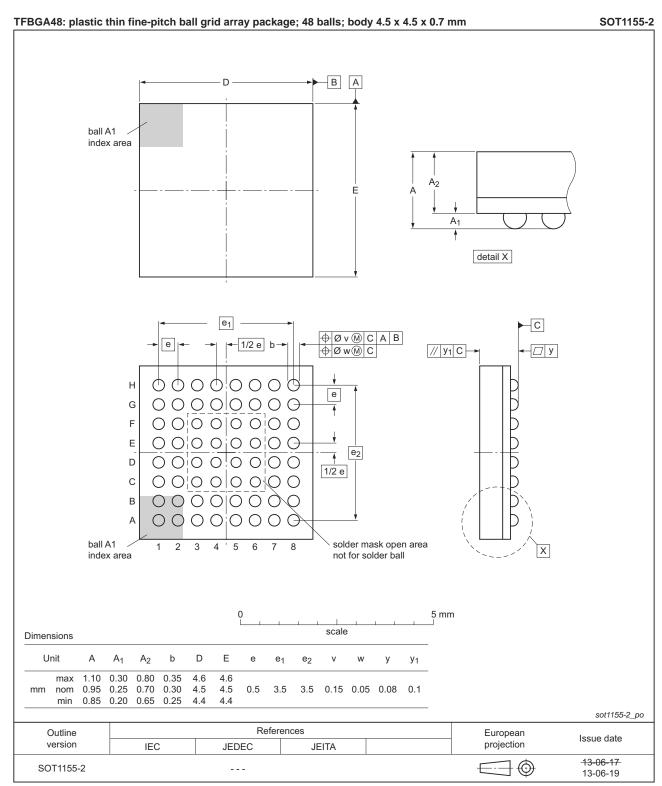

Fig 38. Package outline TFBGA48 (SOT1155-2)

LPC11U2X

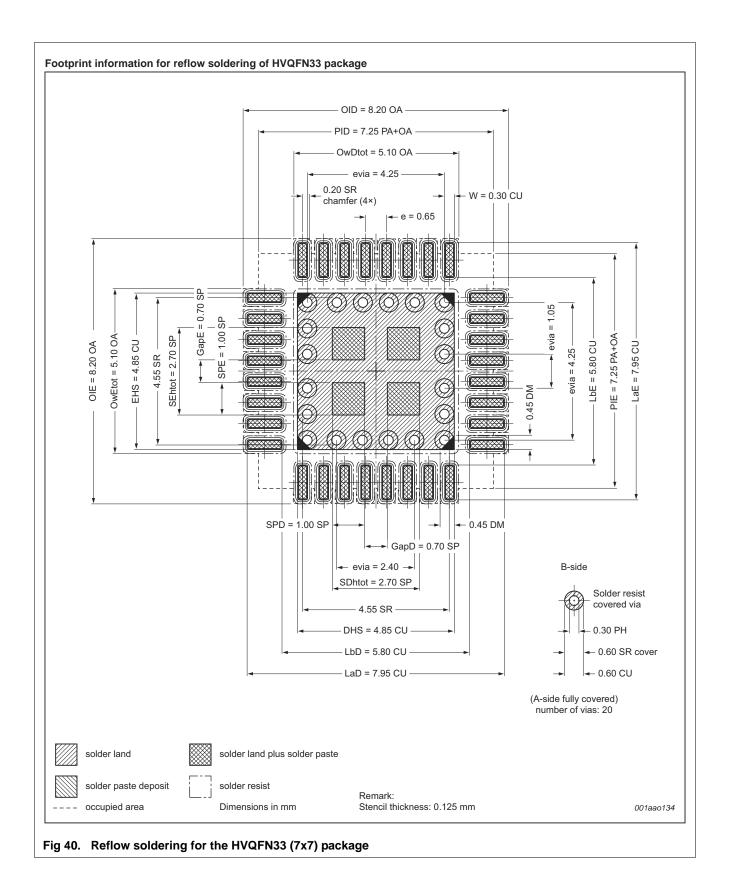

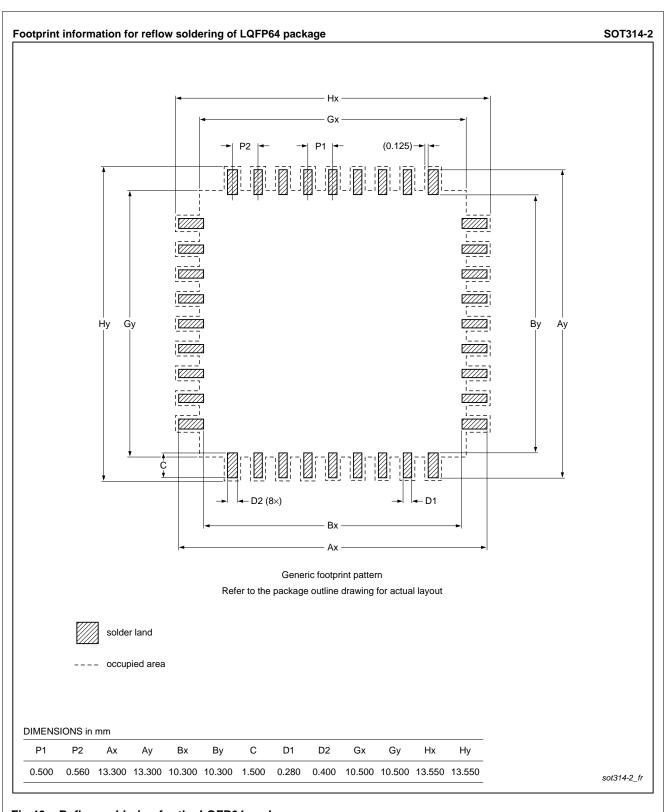

Fig 43. Reflow soldering for the LQFP64 package

## 32-bit ARM Cortex-M0 microcontroller

# 19. Contents

| 1               | General description                        | . 1 | 7.17.5               | Power control                           |    |

|-----------------|--------------------------------------------|-----|----------------------|-----------------------------------------|----|

| 2               | Features and benefits                      | . 1 | 7.17.5.1             |                                         |    |

| 3               | Applications                               | . 3 | 7.17.5.2             |                                         |    |

| 4               | Ordering information                       | . 3 | 7.17.5.3             | ·                                       |    |

| 4.1             | Ordering options                           |     | 7.17.5.4             |                                         |    |

| 5               | Block diagram                              |     | 7.17.5.5             |                                         |    |

| 6               |                                            |     | 7.17.6               | System control                          |    |

| -               | Pinning information                        |     | 7.17.6.1<br>7.17.6.2 |                                         |    |

| 6.1             | Pinning                                    |     | 7.17.6.2             |                                         |    |

| 6.2<br><b>7</b> | Pin description                            |     | 7.17.6.3             |                                         |    |

|                 | Functional description                     |     | 7.17.6.5             |                                         |    |

| 7.1             | On-chip flash programming memory           |     | 7.17.6.6             |                                         |    |

| 7.2             | EEPROM                                     |     | 7.18                 | Emulation and debugging                 |    |

| 7.3             | SRAM                                       |     | 8                    | Limiting values                         |    |

| 7.4<br>7.5      | On-chip ROM                                |     | 9                    | Static characteristics                  |    |

| 7.5<br>7.6      | Memory map                                 |     | _                    | BOD static characteristics              |    |

| 7.6.1           | Features                                   |     | 9.1<br>9.2           |                                         |    |

| 7.6.2           | Interrupt sources                          |     |                      | Power consumption                       |    |

| 7.0.2           | IOCON block                                |     | 9.3                  | Peripheral power consumption            |    |

| 7.7.1           | Features                                   |     | 9.4                  | Electrical pin characteristics          |    |

| 7.7.1           | General-Purpose Input/Output GPIO          |     | 10                   | Dynamic characteristics                 |    |

| 7.8.1           | Features                                   |     | 10.1                 | Flash memory                            |    |

| 7.0.1           | USB interface                              |     | 10.2                 | External clock                          |    |

| 7.9.1           | Full-speed USB device controller           |     | 10.3                 | Internal oscillators                    |    |

| 7.9.1.1         | Features                                   |     | 10.4                 | I/O pins                                |    |

| 7.10            | USART                                      |     | 10.5                 | I <sup>2</sup> C-bus                    |    |

| 7.10.1          | Features                                   |     | 10.6                 | SSP interface                           |    |

| 7.11            | SSP serial I/O controller                  |     | 10.7                 | USB interface                           |    |

| 7.11.1          | Features                                   |     | 11                   | Application information                 |    |

| 7.12            | I <sup>2</sup> C-bus serial I/O controller |     | 11.1                 | Suggested USB interface solutions       |    |

| 7.12.1          | Features                                   |     | 11.2                 | XTAL input                              | 53 |

| 7.13            | 10-bit ADC                                 |     | 11.3                 | XTAL Printed-Circuit Board (PCB) layout |    |

| 7.13.1          | Features                                   |     |                      | guidelines                              |    |

| 7.14            | General purpose external event             |     | 11.4                 | Standard I/O pad configuration          |    |

|                 | counter/timers                             | 20  | 11.5                 | Reset pad configuration                 |    |

| 7.14.1          | Features                                   |     | 11.6                 | ADC effective input impedance           |    |

| 7.15            | System tick timer                          |     | 11.7                 | ADC usage notes                         | 58 |

| 7.16            | Windowed WatchDog Timer (WWDT)             |     | 12                   | Package outline                         | 59 |

| 7.16.1          | Features                                   |     | 13                   | Soldering                               | 64 |

| 7.17            | Clocking and power control                 |     | 14                   | Abbreviations                           |    |

| 7.17.1          | Integrated oscillators                     |     | 15                   |                                         |    |

| 7.17.1.1        |                                            |     | _                    | References                              |    |

| 7.17.1.2        |                                            |     | 16                   | Revision history                        |    |

| 7.17.1.3        |                                            |     | 17                   | Legal information                       |    |

| 7.17.2          | System PLL and USB PLL                     |     | 17.1                 | Data sheet status                       |    |

| 7.17.3          | Clock output                               |     | 17.2                 | Definitions                             |    |

| 7.17.4          | Wake-up process                            |     | 17.3                 | Disclaimers                             | 71 |

continued >>