# E·XFL

Welcome to E-XFL.COM

#### Understanding <u>Embedded - FPGAs (Field</u> <u>Programmable Gate Array)</u>

Embedded - FPGAs, or Field Programmable Gate Arrays, are advanced integrated circuits that offer unparalleled flexibility and performance for digital systems. Unlike traditional fixed-function logic devices, FPGAs can be programmed and reprogrammed to execute a wide array of logical operations, enabling customized functionality tailored to specific applications. This reprogrammability allows developers to iterate designs quickly and implement complex functions without the need for custom hardware.

#### **Applications of Embedded - FPGAs**

The versatility of Embedded - FPGAs makes them indispensable in numerous fields. In telecommunications.

| Details                        |                                                                 |

|--------------------------------|-----------------------------------------------------------------|

| Product Status                 | Obsolete                                                        |

| Number of LABs/CLBs            | -                                                               |

| Number of Logic Elements/Cells | -                                                               |

| Total RAM Bits                 | 2560                                                            |

| Number of I/O                  | 202                                                             |

| Number of Gates                | 54000                                                           |

| Voltage - Supply               | 3V ~ 3.6V, 4.5V ~ 5.5V                                          |

| Mounting Type                  | Surface Mount                                                   |

| Operating Temperature          | -40°C ~ 85°C (TA)                                               |

| Package / Case                 | 240-BFQFP                                                       |

| Supplier Device Package        | 240-PQFP (32x32)                                                |

| Purchase URL                   | https://www.e-xfl.com/product-detail/microsemi/a42mx36-1pqg240i |

|                                |                                                                 |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

Power Matters."

Microsemi Corporate Headquarters One Enterprise, Aliso Viejo, CA 92656 USA Within the USA: +1 (800) 713-4113 Outside the USA: +1 (949) 380-6100 Fax: +1 (949) 215-4996 Email: sales.support@microsemi.com www.microsemi.com

© 2016 Microsemi Corporation. All rights reserved. Microsemi and the Microsemi logo are trademarks of Microsemi Corporation. All other trademarks and service marks are the property of their respective owners. Microsemi makes no warranty, representation, or guarantee regarding the information contained herein or the suitability of its products and services for any particular purpose, nor does Microsemi assume any liability whatsoever arising out of the application or use of any product or circuit. The products sold hereunder and any other products sold by Microsemi have been subject to limited testing and should not be used in conjunction with mission-critical equipment or applications. Any performance specifications are believed to be reliable but are not verified, and Buyer must conduct and complete all performance and other testing of the products, alone and together with, or installed in, any end-products. Buyer shall not rely on any data and performance specifications or parameters provided by Microsemi. It is the Buyer's responsibility to independently determine suitability of any products and to test and verify the same. The information provided by Microsemi hereunder is provided "as is, where is" and with all faults, and the entire risk associated with such information is entirely with the Buyer. Microsemi does not grant, explicitly or implicitly, to any party any patent rights, licenses, or any other IP rights, whether with regard to such information itself or anything described by such information. Information provided in this document or to any products and services at any time without notice.

#### About Microsemi

Microsemi Corporation (Nasdaq: MSCC) offers a comprehensive portfolio of semiconductor and system solutions for aerospace & defense, communications, data center and industrial markets. Products include high-performance and radiation-hardened analog mixed-signal integrated circuits, FPGAs, SoCs and ASICs; power management products; timing and synchronization devices and precise time solutions, setting the world's standard for time; voice processing devices; RF solutions; discrete components; enterprise storage and communication solutions, security technologies and scalable anti-tamper products; Ethernet solutions; Power-over-Ethernet ICs and midspans; as well as custom design capabilities and services. Microsemi is headquartered in Aliso Viejo, California, and has approximately 4,800 employees globally. Learn more at www.microsemi.com.

| Figure 51 | BG272 |

|-----------|-------|

| Figure 52 | PG132 |

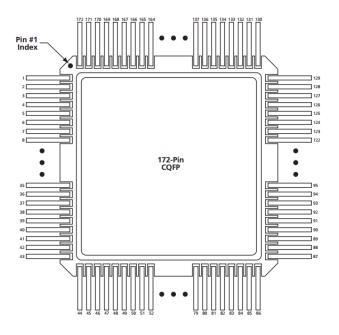

| Figure 53 | CQ172 |

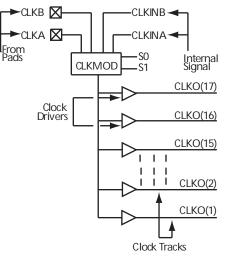

#### Figure 8 • Clock Networks of 42MX Devices

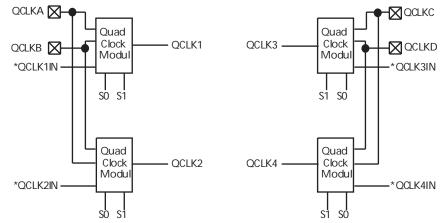

#### Figure 9 • Quadrant Clock Network of A42MX36 Devices

Note: \*QCLK1IN, QCLK2IN, QCLK3IN, and QCLK4IN are internally-generated signals.

## 3.2.5 MultiPlex I/O Modules

42MX devices feature Multiplex I/Os and support 5.0 V, 3.3 V, and mixed 3.3 V/5.0 V operations.

The MultiPlex I/O modules provide the interface between the device pins and the logic array. Figure 10, page 12 is a block diagram of the 42MX I/O module. A variety of user functions, determined by a library macro selection, can be implemented in the module. (See the *Antifuse Macro Library Guide* for more information.) All 42MX I/O modules contain tristate buffers, with input and output latches that can be configured for input, output, or bidirectional operation.

All 42MX devices contain flexible I/O structures, where each output pin has a dedicated output-enable control (Figure 10, page 12). The I/O module can be used to latch input or output data, or both, providing fast set-up time. In addition, the Designer software tools can build a D-type flip-flop using a C-module combined with an I/O module to register input and output signals. See the *Antifuse Macro Library Guide* for more details.

A42MX24 and A42MX36 devices also offer selectable PCI output drives, enabling 100% compliance with version 2.1 of the PCI specification. For low-power systems, all inputs and outputs are turned off to reduce current consumption to below 500  $\mu$ A.

To achieve 5.0 V or 3.3 V PCI-compliant output drives on A42MX24 and A42MX36 devices, a chip-wide PCI fuse is programmed via the Device Selection Wizard in the Designer software (Figure 11, page 12). When the PCI fuse is not programmed, the output drive is standard.

Silicon Sculptor programs devices independently to achieve the fastest programming times possible. After being programmed, each fuse is verified to insure that it has been programmed correctly. Furthermore, at the end of programming, there are integrity tests that are run to ensure no extra fuses have been programmed. Not only does it test fuses (both programmed and non-programmed), Silicon Sculptor also allows self-test to verify its own hardware extensively.

The procedure for programming an MX device using Silicon Sculptor is as follows:

- 1. Load the \*.AFM file

- 2. Select the device to be programmed

- 3. Begin programming

When the design is ready to go to production, Microsemi offers device volume-programming services either through distribution partners or via In-House Programming from the factory.

For more details on programming MX devices, see the *AC225: Programming Antifuse Devices* application note and the *Silicon Sculptor 3 Programmers User Guide*.

### 3.3.4 Power Supply

MX devices are designed to operate in both 5.0V and 3.3V environments. In particular, 42MX devices can operate in mixed 5.0 V/3.3 V systems. The following table describes the voltage support of MX devices.

| Device | VCC   | VCCA  | VCCI  | Maximum Input Tolerance | Nominal Output Voltage |

|--------|-------|-------|-------|-------------------------|------------------------|

| 40MX   | 5.0 V | -     | -     | 5.5 V                   | 5.0 V                  |

|        | 3.3 V | _     | -     | 3.6 V                   | 3.3 V                  |

| 42MX   | _     | 5.0 V | 5.0 V | 5.5 V                   | 5.0 V                  |

|        | _     | 3.3 V | 3.3 V | 3.6 V                   | 3.3 V                  |

|        | _     | 5.0 V | 3.3 V | 5.5 V                   | 3.3 V                  |

|        |       |       |       |                         |                        |

#### Table 6 • Voltage Support of MX Devices

For A42MX24 and A42MX36 devices the VCCA supply has to be monotonic during power up in order for the POR to issue reset to the JTAG state machine correctly. For more information, see the AC291: 42MX Family Devices Power-Up Behavior.

## 3.3.5 Power-Up/Down in Mixed-Voltage Mode

When powering up 42MX in mixed voltage mode (VCCA = 5.0 V and VCCI = 3.3 V), VCCA must be greater than or equal to VCCI throughout the power-up sequence. If VCCI exceeds VCCA during power-up, one of two things will happen:

- The input protection diode on the I/Os will be forward biased

- The I/Os will be at logical High

In either case, ICC rises to high levels. For power-down, any sequence with VCCA and VCCI can be implemented.

## 3.3.6 Transient Current

Due to the simultaneous random logic switching activity during power-up, a transient current may appear on the core supply (VCC). Customers must use a regulator for the VCC supply that can source a minimum of 100 mA for transient current during power-up. Failure to provide enough power can prevent the system from powering up properly and result in functional failure. However, there are no reliability concerns, since transient current is distributed across the die instead of confined to a localized spot.

Since the transient current is not due to I/O switching, its value and duration are independent of the VCCI.

## 3.3.7 Low Power Mode

42MX devices have been designed with a Low Power Mode. This feature, activated with setting the special LP pin to HIGH for a period longer than 800 ns, is particularly useful for battery-operated systems where battery life is a primary concern. In this mode, the core of the device is turned off and the device consumes minimal power with low standby current. In addition, all input buffers are turned off, and all outputs and bidirectional buffers are tristated. Since the core of the device is turned off, the states of the registers are lost. The device must be re-initialized when exiting Low Power Mode. I/Os can be driven during LP mode, and clock pins should be driven HIGH or LOW and should not float to avoid drawing current. To exit LP mode, the LP pin must be pulled LOW for over 200 µs to allow for charge pumps to power up, and device initialization will begin.

## 3.4 **Power Dissipation**

The general power consumption of MX devices is made up of static and dynamic power and can be expressed with the following equation.

## 3.4.1 General Power Equation

P = [ICCstandby + ICCactive]\*VCCI + IOL\*VOL\*N + IOH\*(VCCI - VOH)\*M

EQ 1

where:

- ICCstandby is the current flowing when no inputs or outputs are changing.

- ICCactive is the current flowing due to CMOS switching.

- IOL, IOH are TTL sink/source currents.

- VOL, VOH are TTL level output voltages.

- N equals the number of outputs driving TTL loads to VOL.

- M equals the number of outputs driving TTL loads to VOH.

Accurate values for N and M are difficult to determine because they depend on the family type, on design details, and on the system I/O. The power can be divided into two components: static and active.

## 3.4.2 Static Power Component

The static power due to standby current is typically a small component of the overall power consumption. Standby power is calculated for commercial, worst-case conditions. The static power dissipation by TTL loads depends on the number of outputs driving, and on the DC load current. For instance, a 32-bit bus sinking 4mA at 0.33V will generate 42mW with all outputs driving LOW, and 140mW with all outputs driving HIGH. The actual dissipation will average somewhere in between, as I/Os switch states with time.

## 3.4.3 Active Power Component

Power dissipation in CMOS devices is usually dominated by the dynamic power dissipation. Dynamic power consumption is frequency-dependent and is a function of the logic and the external I/O. Active power dissipation results from charging internal chip capacitances of the interconnect, unprogrammed antifuses, module inputs, and module outputs, plus external capacitances due to PC board traces and load device inputs. An additional component of the active power dissipation is the totem pole current in the CMOS transistor pairs. The net effect can be associated with an equivalent capacitance that can be combined with frequency and voltage to represent active power dissipation.

The power dissipated by a CMOS circuit can be expressed by the equation:

$$Power(\mu W) = C_{EO}^* VCCA2^* F(1)$$

where:

C<sub>EQ</sub> = Equivalent capacitance expressed in picofarads (pF)

EQ 2

$f_{\alpha 2}$  = Average second routed array clock rate in MHz)

| Device Type | r1 routed_Clk1 | r2 routed_Clk2 |

|-------------|----------------|----------------|

| A40MX02     | 41.4           | N/A            |

| A40MX04     | 68.6           | N/A            |

| A42MX09     | 118            | 118            |

| A42MX16     | 165            | 165            |

| A42MX24     | 185            | 185            |

| A42MX36     | 220            | 220            |

Table 7 •

Fixed Capacitance Values for MX FPGAs (pF)

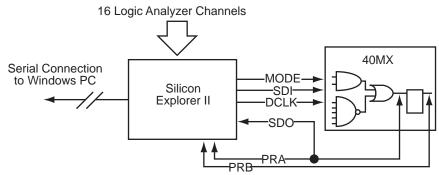

## 3.4.6 Test Circuitry and Silicon Explorer II Probe

MX devices contain probing circuitry that provides built-in access to every node in a design, via the use of Silicon Explorer II. Silicon Explorer II is an integrated hardware and software solution that, in conjunction with the Designer software, allow users to examine any of the internal nets of the device while it is operating in a prototyping or a production system. The user can probe into an MX device without changing the placement and routing of the design and without using any additional resources. Silicon Explorer II's noninvasive method does not alter timing or loading effects, thus shortening the debug cycle and providing a true representation of the device under actual functional situations.

Silicon Explorer II samples data at 100 MHz (asynchronous) or 66 MHz (synchronous). Silicon Explorer II attaches to a PC's standard COM port, turning the PC into a fully functional 18-channel logic analyzer. Silicon Explorer II allows designers to complete the design verification process at their desks and reduces verification time from several hours per cycle to a few seconds.

Silicon Explorer II is used to control the MODE, DCLK, SDI and SDO pins in MX devices to select the desired nets for debugging. The user simply assigns the selected internal nets in the Silicon Explorer II software to the PRA/PRB output pins for observation. Probing functionality is activated when the MODE pin is held HIGH.

Figure 12, page 16 illustrates the interconnection between Silicon Explorer II and 40MX devices, while Figure 13, page 17 illustrates the interconnection between Silicon Explorer II and 42MX devices

To allow for probing capabilities, the security fuses must not be programmed. (See User Security, page 12 for the security fuses of 40MX and 42MX devices). Table 8, page 17 summarizes the possible device configurations for probing.

PRA and PRB pins are dual-purpose pins. When the "Reserve Probe Pin" is checked in the Designer software, PRA and PRB pins are reserved as dedicated outputs for probing. If PRA and PRB pins are required as user I/Os to achieve successful layout and "Reserve Probe Pin" is checked, the layout tool will override the option and place user I/Os on PRA and PRB pins.

#### Figure 12 • Silicon Explorer II Setup with 40MX

3. All outputs unloaded. All inputs = VCC/VCCI or GND

## 3.8 3.3 V Operating Conditions

The following table shows 3.3 V operating conditions.

#### Table 16 • Absolute Maximum Ratings for 40MX Devices\*

| Symbol           | Parameter           | Limits            | Units<br>V |  |  |

|------------------|---------------------|-------------------|------------|--|--|

| VCC              | DC Supply Voltage   | -0.5 to +7.0      |            |  |  |

| VI               | Input Voltage       | -0.5 to VCC + 0.5 | V          |  |  |

| VO               | Output Voltage      | -0.5 to VCC + 0.5 | V          |  |  |

| t <sub>STG</sub> | Storage Temperature | -65 to + 150      | °C         |  |  |

**Note:** \*Stresses beyond those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. Exposure to absolute maximum rated conditions for extended periods may affect device reliability. Devices should not be operated outside the recommended operating conditions.

#### Table 17 • Absolute Maximum Ratings for 42MX Devices\*

| Symbol           | Parameter                   | Limits           | Units |

|------------------|-----------------------------|------------------|-------|

| VCCI             | DC Supply Voltage for I/Os  | -0.5 to +7.0     | V     |

| VCCA             | DC Supply Voltage for Array | -0.5 to +7.0     | V     |

| VI               | Input Voltage               | -0.5 to VCCI+0.5 | V     |

| VO               | Output Voltage              | -0.5 to VCCI+0.5 | V     |

| t <sub>STG</sub> | Storage Temperature         | -65 to +150      | °C    |

**Note:** \*Stresses beyond those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. Exposure to absolute maximum rated conditions for extended periods may affect device reliability. Devices should not be operated outside the recommended operating conditions.

#### Table 18 • Recommended Operating Conditions

| Parameter          | Commercial | Industrial | Military    | Units |

|--------------------|------------|------------|-------------|-------|

| Temperature Range* | 0 to +70   | -40 to +85 | -55 to +125 | °C    |

| VCC (40MX)         | 3.0 to 3.6 | 3.0 to 3.6 | 3.0 to 3.6  | V     |

| VCCA (42MX)        | 3.0 to 3.6 | 3.0 to 3.6 | 3.0 to 3.6  | V     |

| VCCI (42MX)        | 3.0 to 3.6 | 3.0 to 3.6 | 3.0 to 3.6  | V     |

**Note:** \*Ambient temperature (T<sub>A</sub>) is used for commercial and industrial grades; case temperature (T<sub>C</sub>) is used for military grades.

All the following tables show various specifications and operating conditions of 40MX and 42MX FPGAs.

#### **3.3 V LVTTL Electrical Specifications** 3.8.1

#### Table 19 • 3.3V LVTTL Electrical Specifications

|                                        |                      | Commercial |             | Com      | nercial -F   | Indus  | trial        | Milita  | ry             |       |

|----------------------------------------|----------------------|------------|-------------|----------|--------------|--------|--------------|---------|----------------|-------|

| Symbol                                 | Parameter            | Min.       | Max.        | Min.     | Max.         | Min.   | Max.         | Min.    | Max.           | Units |

| VOH <sup>1</sup>                       | IOH = -4 mA          | 2.15       |             | 2.15     |              | 2.4    |              | 2.4     |                | V     |

| VOL <sup>1</sup>                       | IOL = 6 mA           |            | 0.4         |          | 0.4          |        | 0.48         |         | 0.48           | V     |

| VIL                                    |                      | -0.3       | 0.8         | -0.3     | 0.8          | -0.3   | 0.8          | -0.3    | 0.8            | V     |

| VIH (40MX)                             |                      | 2.0        | VCC + 0.3   | 2.0      | VCC + 0.3    | 2.0    | VCC + 0.3    | 2.0     | VCC + 0.3      | V     |

| VIH (42MX)                             |                      | 2.0        | VCCI + 0.3  | 2.0      | VCCI + 0.3   | 2.0    | VCCI + 0.3   | 2.0     | VCCI + 0.3     | V     |

| IIL                                    |                      |            | -10         |          | -10          |        | -10          |         | -10            | μA    |

| IIH                                    |                      |            | -10         |          | -10          |        | -10          |         | -10            | μA    |

| Input Transition Time, $T_R$ and $T_F$ |                      |            | 500         |          | 500          |        | 500          |         | 500            | ns    |

| C <sub>IO</sub> I/O<br>Capacitance     |                      |            | 10          |          | 10           |        | 10           |         | 10             | pF    |

| Standby<br>Current, ICC <sup>2</sup>   | A40MX02,<br>A40MX04  |            | 3           |          | 25           |        | 10           |         | 25             | mA    |

|                                        | A42MX09              |            | 5           | 25       |              | 25     |              | 25      |                | mA    |

|                                        | A42MX16              |            | 6           |          | 25           |        | 25           |         | 25             | mA    |

|                                        | A42MX24,<br>A42MX36  |            | 15          |          | 25           |        | 25           |         | 25             | mA    |

| Low-Power<br>Mode Standby<br>Current   | 42MX<br>devices only |            | 0.5         |          | ICC - 5.0    |        | ICC - 5.0    |         | ICC - 5.0      | mA    |

| IIO, I/O source                        | Can be derive        | ed from    | the IBIS mo | del (htt | p://www.micr | osemi. | com/soc/tech | ndocs/n | nodels/ibis.ht | ml)   |

sink current

Only one output tested at a time. VCC/VCCI = min. 1.

All outputs unloaded. All inputs = VCC/VCCI or GND. 2.

#### Mixed 5.0 V / 3.3 V Operating Conditions (for 42MX 3.9 **Devices Only)**

#### Table 20 • Absolute Maximum Ratings\*

| Symbol           | Parameter                   | Limits             | Units |

|------------------|-----------------------------|--------------------|-------|

| VCCI             | DC Supply Voltage for I/Os  | –0.5 to +7.0       | V     |

| VCCA             | DC Supply Voltage for Array | -0.5 to +7.0       | V     |

| VI               | Input Voltage               | -0.5 to VCCA +0.5  | V     |

| VO               | Output Voltage              | -0.5 to VCCI + 0.5 | V     |

| t <sub>STG</sub> | Storage Temperature         | -65 to +150        | °C    |

Note: \*Stresses beyond those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. Exposure to absolute maximum rated conditions for extended periods may affect device

#### Table 33 • Timing Parameters for 33 MHz PCI

|                      |                                         | PCI                 |      | A42N | IX24 | A42N |      |       |

|----------------------|-----------------------------------------|---------------------|------|------|------|------|------|-------|

| Symbol               | Parameter                               | Min.                | Max. | Min. | Max. | Min. | Max. | Units |

| t <sub>SU(PTP)</sub> | Input Set-Up Time to CLK—Point-to-Point | 10, 12 <sup>2</sup> | _    | 1.5  | -    | 1.5  | -    | ns    |

| t <sub>H</sub>       | Input Hold to CLK                       | 0                   | _    | 0    | -    | 0    | -    | ns    |

1. TOFF is system dependent. MX PCI devices have 7.4 ns turn-off time, reflection is typically an additional 10 ns.

2. REQ# and GNT# are point-to-point signals and have different output valid delay and input setup times than do bussed signals. GNT# has a setup of 10; REW# has a setup of 12.

### 3.11.6.1 Timing Characteristics

The following tables list the timing characteristics.

## Table 34 •A40MX02 Timing Characteristics (Nominal 5.0 V Operation)<br/>(Worst-Case Commercial Conditions, VCC = 4.75 V, T<sub>J</sub> = 70°C)

|                              |                                                 | -3 Sp            | beed | –2 Sp | beed | –1 Sp | beed | Std S | peed | –F Sp | beed |       |

|------------------------------|-------------------------------------------------|------------------|------|-------|------|-------|------|-------|------|-------|------|-------|

| Parame                       | eter / Description                              | Min.             | Max. | Min.  | Max. | Min.  | Max. | Min.  | Max. | Min.  | Max. | Units |

| Logic N                      | Iodule Propagation Delays                       |                  |      |       |      |       |      |       |      |       |      |       |

| t <sub>PD1</sub>             | Single Module                                   |                  | 1.2  |       | 1.4  |       | 1.6  |       | 1.9  |       | 2.7  | ns    |

| t <sub>PD2</sub>             | Dual-Module Macros                              |                  | 2.7  |       | 3.1  |       | 3.5  |       | 4.1  |       | 5.7  | ns    |

| t <sub>CO</sub>              | Sequential Clock-to-Q                           |                  | 1.2  |       | 1.4  |       | 1.6  |       | 1.9  |       | 2.7  | ns    |

| t <sub>GO</sub>              | Latch G-to-Q                                    |                  | 1.2  |       | 1.4  |       | 1.6  |       | 1.9  |       | 2.7  | ns    |

| t <sub>RS</sub>              | Flip-Flop (Latch) Reset-to-Q                    |                  | 1.2  |       | 1.4  |       | 1.6  |       | 1.9  |       | 2.7  | ns    |

| Logic N                      | Nodule Predicted Routing Del                    | ays <sup>1</sup> |      |       |      |       |      |       |      |       |      |       |

| t <sub>RD1</sub>             | FO = 1 Routing Delay                            |                  | 1.3  |       | 1.5  |       | 1.7  |       | 2.0  |       | 2.8  | ns    |

| t <sub>RD2</sub>             | FO = 2 Routing Delay                            |                  | 1.8  |       | 2.1  |       | 2.4  |       | 2.8  |       | 3.9  | ns    |

| t <sub>RD3</sub>             | FO = 3 Routing Delay                            |                  | 2.3  |       | 2.7  |       | 3.0  |       | 3.6  |       | 5.0  | ns    |

| t <sub>RD4</sub>             | FO = 4 Routing Delay                            |                  | 2.9  |       | 3.3  |       | 3.7  |       | 4.4  |       | 6.1  | ns    |

| t <sub>RD8</sub>             | FO = 8 Routing Delay                            |                  | 4.9  |       | 5.7  |       | 6.5  |       | 7.6  |       | 10.6 | ns    |

| Logic N                      | Iodule Sequential Timing <sup>2</sup>           |                  |      |       |      |       |      |       |      |       |      |       |

| t <sub>SUD</sub>             | Flip-Flop (Latch)<br>Data Input Set-Up          | 3.1              |      | 3.5   |      | 4.0   |      | 4.7   |      | 6.6   |      | ns    |

| t <sub>HD</sub> <sup>3</sup> | Flip-Flop (Latch)<br>Data Input Hold            | 0.0              |      | 0.0   |      | 0.0   |      | 0.0   |      | 0.0   |      | ns    |

| t <sub>SUENA</sub>           | Flip-Flop (Latch)<br>Enable Set-Up              | 3.1              |      | 3.5   |      | 4.0   |      | 4.7   |      | 6.6   |      | ns    |

| t <sub>HENA</sub>            | Flip-Flop (Latch) Enable Hold                   | 0.0              |      | 0.0   |      | 0.0   |      | 0.0   |      | 0.0   |      | ns    |

| t <sub>WCLKA</sub>           | Flip-Flop (Latch)<br>Clock Active Pulse Width   | 3.3              |      | 3.8   |      | 4.3   |      | 5.0   |      | 7.0   |      | ns    |

| t <sub>WASYN</sub>           | Flip-Flop (Latch)<br>Asynchronous Pulse Width   | 3.3              |      | 3.8   |      | 4.3   |      | 5.0   |      | 7.0   |      | ns    |

| t <sub>A</sub>               | Flip-Flop Clock Input Period                    | 4.8              |      | 5.6   |      | 6.3   |      | 7.5   |      | 10.4  |      | ns    |

| f <sub>MAX</sub>             | Flip-Flop (Latch) Clock<br>Frequency (FO = 128) |                  | 181  |       | 168  |       | 154  |       | 134  |       | 80   | MHz   |

# Table 37 • A40MX04 Timing Characteristics (Nominal 3.3 V Operation) (continued)(Worst-Case Commercial Conditions, VCC = 3.0 V, T<sub>J</sub> = 70°C)

|                    |                                                    | –3 SI | beed | –2 S | beed | –1 Sp | eed  | Std S | Speed | –F S | peed |       |

|--------------------|----------------------------------------------------|-------|------|------|------|-------|------|-------|-------|------|------|-------|

| Paramet            | er / Description                                   | Min.  | Max. | Min. | Max. | Min.  | Max. | Min.  | Max.  | Min. | Max. | Units |

| t <sub>WCLKA</sub> | Flip-Flop (Latch)<br>Clock Active Pulse Width      | 4.6   |      | 5.3  |      | 5.6   |      | 7.0   |       | 9.8  |      | ns    |

| t <sub>WASYN</sub> | Flip-Flop (Latch)<br>Asynchronous Pulse Width      | 4.6   |      | 5.3  |      | 5.6   |      | 7.0   |       | 9.8  |      | ns    |

| t <sub>A</sub>     | Flip-Flop Clock Input Period                       | 6.8   |      | 7.8  |      | 8.9   |      | 10.4  |       | 14.6 |      | ns    |

| f <sub>MAX</sub>   | Flip-Flop (Latch) Clock<br>Frequency<br>(FO = 128) |       | 109  |      | 101  |       | 92   |       | 80    |      | 48   | MHz   |

| Input Mo           | odule Propagation Delays                           |       |      |      |      |       |      |       |       |      |      |       |

| t <sub>INYH</sub>  | Pad-to-Y HIGH                                      |       | 1.0  |      | 1.1  |       | 1.3  |       | 1.5   |      | 2.1  | ns    |

| t <sub>INYL</sub>  | Pad-to-Y LOW                                       |       | 0.9  |      | 1.0  |       | 1.1  |       | 1.3   |      | 1.9  | ns    |

## Table 40 •A42MX16 Timing Characteristics (Nominal 5.0 V Operation) (continued) (Worst-Case Commercial<br/>Conditions, VCCA = 4.75 V, T<sub>J</sub> = 70°C)

|                    |                                               | –3 S       | peed       | –2 S       | peed       | –1 S       | beed       | Std S      | speed      | –F Sp      | beed       |          |

|--------------------|-----------------------------------------------|------------|------------|------------|------------|------------|------------|------------|------------|------------|------------|----------|

| Parame             | ter / Description                             | Min.       | Max.       | Units    |

| t <sub>RD3</sub>   | FO = 3 Routing Delay                          |            | 1.3        |            | 1.4        |            | 1.6        |            | 1.9        |            | 2.7        | ns       |

| t <sub>RD4</sub>   | FO = 4 Routing Delay                          |            | 1.6        |            | 1.7        |            | 2.0        |            | 2.3        |            | 3.2        | ns       |

| t <sub>RD8</sub>   | FO = 8 Routing Delay                          |            | 2.6        |            | 2.9        |            | 3.2        |            | 3.8        |            | 5.3        | ns       |

| Logic M            | odule Sequential Timing <sup>3,4</sup>        |            |            |            |            |            |            |            |            |            |            |          |

| t <sub>SUD</sub>   | Flip-Flop (Latch)<br>Data Input Set-Up        | 0.3        |            | 0.4        |            | 0.4        |            | 0.5        |            | 0.7        |            | ns       |

| t <sub>HD</sub>    | Flip-Flop (Latch) Data Input Hold             | 0.0        |            | 0.0        |            | 0.0        |            | 0.0        |            | 0.0        |            | ns       |

| t <sub>SUENA</sub> | Flip-Flop (Latch) Enable Set-Up               | 0.7        |            | 0.8        |            | 0.9        |            | 1.0        |            | 1.4        |            | ns       |

| t <sub>HENA</sub>  | Flip-Flop (Latch) Enable Hold                 | 0.0        |            | 0.0        |            | 0.0        |            | 0.0        |            | 0.0        |            | ns       |

| t <sub>WCLKA</sub> | Flip-Flop (Latch)<br>Clock Active Pulse Width | 3.4        |            | 3.8        |            | 4.3        |            | 5.0        |            | 7.1        |            | ns       |

| t <sub>WASYN</sub> | Flip-Flop (Latch)<br>Asynchronous Pulse Width | 4.5        |            | 5.0        |            | 5.6        |            | 6.6        |            | 9.2        |            | ns       |

| t <sub>A</sub>     | Flip-Flop Clock Input Period                  | 6.8        |            | 7.6        |            | 8.6        |            | 10.1       |            | 14.1       |            | ns       |

| t <sub>INH</sub>   | Input Buffer Latch Hold                       | 0.0        |            | 0.0        |            | 0.0        |            | 0.0        |            | 0.0        |            | ns       |

| t <sub>INSU</sub>  | Input Buffer Latch Set-Up                     | 0.5        |            | 0.5        |            | 0.6        |            | 0.7        |            | 1.0        |            | ns       |

| t <sub>OUTH</sub>  | Output Buffer Latch Hold                      | 0.0        |            | 0.0        |            | 0.0        |            | 0.0        |            | 0.0        |            | ns       |

| t <sub>OUTSU</sub> | Output Buffer Latch Set-Up                    | 0.5        |            | 0.5        |            | 0.6        |            | 0.7        |            | 1.0        |            | ns       |

| f <sub>MAX</sub>   | Flip-Flop (Latch) Clock Frequency             | /          | 215        |            | 195        |            | 179        |            | 156        |            | 94         | MHz      |

| Input M            | odule Propagation Delays                      |            |            |            |            |            |            |            |            |            |            |          |

| t <sub>INYH</sub>  | Pad-to-Y HIGH                                 |            | 1.1        |            | 1.2        |            | 1.3        |            | 1.6        |            | 2.2        | ns       |

| t <sub>INYL</sub>  | Pad-to-Y LOW                                  |            | 0.8        |            | 0.9        |            | 1.0        |            | 1.2        |            | 1.7        | ns       |

| t <sub>INGH</sub>  | G to Y HIGH                                   |            | 1.4        |            | 1.6        |            | 1.8        |            | 2.1        |            | 2.9        | ns       |

| t <sub>INGL</sub>  | G to Y LOW                                    |            | 1.4        |            | 1.6        |            | 1.8        |            | 2.1        |            | 2.9        | ns       |

| Input M            | odule Predicted Routing Delays <sup>2</sup>   |            |            |            |            |            |            |            |            |            |            |          |

| t <sub>IRD1</sub>  | FO = 1 Routing Delay                          |            | 1.8        |            | 2.0        |            | 2.3        |            | 2.7        |            | 4.0        | ns       |

| t <sub>IRD2</sub>  | FO = 2 Routing Delay                          |            | 2.1        |            | 2.3        |            | 2.6        |            | 3.1        |            | 4.3        | ns       |

| t <sub>IRD3</sub>  | FO = 3 Routing Delay                          |            | 2.3        |            | 2.6        |            | 3.0        |            | 3.5        |            | 4.9        | ns       |

| t <sub>IRD4</sub>  | FO = 4 Routing Delay                          |            | 2.6        |            | 3.0        |            | 3.3        |            | 3.9        |            | 5.4        | ns       |

| t <sub>IRD8</sub>  | FO = 8 Routing Delay                          |            | 3.6        |            | 4.0        |            | 4.6        |            | 5.4        |            | 7.5        | ns       |

| Global (           | Clock Network                                 |            |            |            |            |            |            |            |            |            |            |          |

| t <sub>CKH</sub>   | Input LOW to HIGH FO = 32<br>FO = 384         |            | 2.6<br>2.9 |            | 2.9<br>3.2 |            | 3.3<br>3.6 |            | 3.9<br>4.3 |            | 5.4<br>6.0 | ns<br>ns |

| t <sub>CKL</sub>   | Input HIGH to LOW FO = 32<br>FO = 384         |            | 3.8<br>4.5 |            | 4.2<br>5.0 |            | 4.8<br>5.6 |            | 5.6<br>6.6 |            | 7.8<br>9.2 | ns<br>ns |

| t <sub>PWH</sub>   | Minimum Pulse Width FO = 32<br>HIGH FO = 384  | 3.2<br>3.7 |            | 3.5<br>4.1 |            | 4.0<br>4.6 |            | 4.7<br>5.4 |            | 6.6<br>7.6 |            | ns<br>ns |

## Table 42 • A42MX24 Timing Characteristics (Nominal 5.0 V Operation) (continued) (Worst-Case Commercial Conditions, VCCA = 4.75 V, T<sub>J</sub> = 70°C)

|                    |                                         |                     | –3 S       | peed       | -2 Sp      | beed       | –1 S       | peed       | Std S      | Speed      | –F S         | peed       |          |

|--------------------|-----------------------------------------|---------------------|------------|------------|------------|------------|------------|------------|------------|------------|--------------|------------|----------|

| Paramet            | ter / Description                       |                     | Min.       | Max.       | Min.       | Max.       | Min.       | Max.       | Min.       | Max.       | Min.         | Max.       | Units    |

| Input Mo           | odule Predicted Routing                 | Delays <sup>2</sup> |            |            |            |            |            |            |            |            |              |            |          |

| t <sub>IRD1</sub>  | FO = 1 Routing Delay                    |                     |            | 1.8        |            | 2.0        |            | 2.3        |            | 2.7        |              | 3.8        | ns       |

| t <sub>IRD2</sub>  | FO = 2 Routing Delay                    |                     |            | 2.1        |            | 2.3        |            | 2.6        |            | 3.1        |              | 4.3        | ns       |

| t <sub>IRD3</sub>  | FO = 3 Routing Delay                    |                     |            | 2.3        |            | 2.5        |            | 2.9        |            | 3.4        |              | 4.8        | ns       |

| t <sub>IRD4</sub>  | FO = 4 Routing Delay                    |                     |            | 2.5        |            | 2.8        |            | 3.2        |            | 3.7        |              | 5.2        | ns       |

| t <sub>IRD8</sub>  | FO = 8 Routing Delay                    |                     |            | 3.4        |            | 3.8        |            | 4.3        |            | 5.1        |              | 7.1        | ns       |

| Global C           | Clock Network                           |                     |            |            |            |            |            |            |            |            |              |            |          |

| t <sub>СКН</sub>   | Input LOW to HIGH                       | FO = 32<br>FO = 486 |            | 2.6<br>2.9 |            | 2.9<br>3.2 |            | 3.3<br>3.6 |            | 3.9<br>4.3 |              | 5.4<br>5.9 | ns<br>ns |

| t <sub>CKL</sub>   | Input HIGH to LOW                       | FO = 32<br>FO = 486 |            | 3.7<br>4.3 |            | 4.1<br>4.7 |            | 4.6<br>5.4 |            | 5.4<br>6.3 |              | 7.6<br>8.8 | ns<br>ns |

| t <sub>PWH</sub>   | Minimum Pulse<br>Width HIGH             | FO = 32<br>FO = 486 | 2.2<br>2.4 |            | 2.4<br>2.6 |            | 2.7<br>3.0 |            | 3.2<br>3.5 |            | 4.5<br>4.9   |            | ns<br>ns |

| t <sub>PWL</sub>   | Minimum Pulse<br>Width LOW              | FO = 32<br>FO = 486 | 2.2<br>2.4 |            | 2.4<br>2.6 |            | 2.7<br>3.0 |            | 3.2<br>3.5 |            | 4.5<br>4.9   |            | ns<br>ns |

| t <sub>CKSW</sub>  | Maximum Skew                            | FO = 32<br>FO = 486 |            | 0.5<br>0.5 |            | 0.6<br>0.6 |            | 0.7<br>0.7 |            | 0.8<br>0.8 |              | 1.1<br>1.1 | ns<br>ns |

| t <sub>SUEXT</sub> | Input Latch External<br>Set-Up          | FO = 32<br>FO = 486 | 0.0<br>0.0 |            | 0.0<br>0.0 |            | 0.0<br>0.0 |            | 0.0<br>0.0 |            | 0.0<br>0.0   |            | ns<br>ns |

| t <sub>HEXT</sub>  | Input Latch External<br>Hold            | FO = 32<br>FO = 486 | 2.8<br>3.3 |            | 3.1<br>3.7 |            | 3.5<br>4.2 |            | 4.1<br>4.9 |            | 5.7<br>6.9   |            | ns<br>ns |

| t <sub>P</sub>     | Minimum Period<br>(1/f <sub>MAX</sub> ) | FO = 32<br>FO = 486 | 4.7<br>5.1 |            | 5.2<br>5.7 |            | 5.7<br>6.2 |            | 6.5<br>7.1 |            | 10.9<br>11.9 |            | ns<br>ns |

# Table 43 •A42MX24 Timing Characteristics (Nominal 3.3 V Operation) (continued) (Worst-Case Commercial<br/>Conditions, VCCA = 3.0 V, T<sub>J</sub> = 70°C)

|                    |                                |                     | –3 Speed –2 |            | –2 Sp      | beed       | –1 S       | peed       | Std Speed  |            | -F Speed   |              |          |

|--------------------|--------------------------------|---------------------|-------------|------------|------------|------------|------------|------------|------------|------------|------------|--------------|----------|

| Paramet            | ter / Description              |                     | Min.        | Max.       | Min.       | Max.       | Min.       | Max.       | Min.       | Max.       | Min.       | Max.         | Units    |

| Input Mo           | odule Predicted Routing        | Delays <sup>2</sup> |             |            |            |            |            |            |            |            |            |              |          |

| t <sub>IRD1</sub>  | FO = 1 Routing Delay           |                     |             | 2.6        |            | 2.9        |            | 3.2        |            | 3.8        |            | 5.3          | ns       |

| t <sub>IRD2</sub>  | FO = 2 Routing Delay           |                     |             | 2.9        |            | 3.2        |            | 3.6        |            | 4.3        |            | 6.0          | ns       |

| t <sub>IRD3</sub>  | FO = 3 Routing Delay           |                     |             | 3.2        |            | 3.6        |            | 4.0        |            | 4.8        |            | 6.6          | ns       |

| t <sub>IRD4</sub>  | FO = 4 Routing Delay           |                     |             | 3.5        |            | 3.9        |            | 4.4        |            | 5.2        |            | 7.3          | ns       |

| t <sub>IRD8</sub>  | FO = 8 Routing Delay           |                     |             | 4.8        |            | 5.3        |            | 6.1        |            | 7.1        |            | 10.0         | ns       |

| Global C           | Clock Network                  |                     |             |            |            |            |            |            |            |            |            |              |          |

| t <sub>CKH</sub>   | Input LOW to HIGH              | FO = 32<br>FO = 486 |             | 4.4<br>4.8 |            | 4.8<br>5.3 |            | 5.5<br>6.0 |            | 6.5<br>7.1 |            | 9.1<br>10.0  | ns<br>ns |

| t <sub>CKL</sub>   | Input HIGH to LOW              | FO = 32<br>FO = 486 |             | 5.1<br>6.0 |            | 5.7<br>6.6 |            | 6.4<br>7.5 |            | 7.6<br>8.8 |            | 10.6<br>12.4 | ns<br>ns |

| t <sub>PWH</sub>   | Minimum Pulse<br>Width HIGH    | FO = 32<br>FO = 486 | 3.0<br>3.3  |            | 3.3<br>3.7 |            | 3.8<br>4.2 |            | 4.5<br>4.9 |            | 6.3<br>6.9 |              | ns<br>ns |

| t <sub>PWL</sub>   | Minimum Pulse<br>Width LOW     | FO = 32<br>FO = 486 | 3.0<br>3.3  |            | 3.4<br>3.7 |            | 3.8<br>4.2 |            | 4.5<br>4.9 |            | 6.3<br>6.9 |              | ns<br>ns |

| t <sub>CKSW</sub>  | Maximum Skew                   | FO = 32<br>FO = 486 |             | 0.8<br>0.8 |            | 0.8<br>0.8 |            | 1.0<br>1.0 |            | 1.1<br>1.1 |            | 1.6<br>1.6   | ns<br>ns |

| t <sub>SUEXT</sub> | Input Latch External<br>Set-Up | FO = 32<br>FO = 486 | 0.0<br>0.0  |            | 0.0<br>0.0 |            | 0.0<br>0.0 |            | 0.0<br>0.0 |            | 0.0<br>0.0 |              | ns<br>ns |

| TTL Out            | put Module Timing <sup>5</sup> |                     |             |            |            |            |            |            |            |            |            |              |          |

| t <sub>DLH</sub>   | Data-to-Pad HIGH               |                     |             | 3.4        |            | 3.8        |            | 4.3        |            | 5.0        |            | 7.1          | ns       |

| t <sub>DHL</sub>   | Data-to-Pad LOW                |                     |             | 4.0        |            | 4.4        |            | 5.0        |            | 5.9        |            | 8.3          | ns       |

| t <sub>ENZH</sub>  | Enable Pad Z to HIGH           |                     |             | 3.6        |            | 4.0        |            | 4.5        |            | 5.3        |            | 7.4          | ns       |

| t <sub>ENZL</sub>  | Enable Pad Z to LOW            |                     |             | 3.9        |            | 4.4        |            | 5.0        |            | 5.8        |            | 8.2          | ns       |

| t <sub>ENHZ</sub>  | Enable Pad HIGH to Z           |                     |             | 7.2        |            | 8.0        |            | 9.1        |            | 10.7       |            | 14.9         | ns       |

| t <sub>ENLZ</sub>  | Enable Pad LOW to Z            |                     |             | 6.7        |            | 7.5        |            | 8.5        |            | 9.9        |            | 13.9         | ns       |

| t <sub>GLH</sub>   | G-to-Pad HIGH                  |                     |             | 4.8        |            | 5.3        |            | 6.0        |            | 7.2        |            | 10.0         | ns       |

| t <sub>GHL</sub>   | G-to-Pad LOW                   |                     |             | 4.8        |            | 5.3        |            | 6.0        |            | 7.2        |            | 10.0         | ns       |

| t <sub>LSU</sub>   | I/O Latch Output Set-U         | lр                  | 0.7         |            | 0.7        |            | 0.8        |            | 1.0        |            | 1.4        |              | ns       |

#### Table 57 • TQ176

| TQ176      |                  |                  |                  |

|------------|------------------|------------------|------------------|

| Pin Number | A42MX09 Function | A42MX16 Function | A42MX24 Function |

| 84         | I/O              | I/O              | WD, I/O          |

| 85         | I/O              | I/O              | WD, I/O          |

| 86         | NC               | I/O              | I/O              |

| 87         | SDO, I/O         | SDO, I/O         | SDO, TDO, I/O    |

| 88         | I/O              | I/O              | I/O              |

| 89         | GND              | GND              | GND              |

| 90         | I/O              | I/O              | I/O              |

| 91         | I/O              | I/O              | I/O              |

| 92         | I/O              | I/O              | I/O              |

| 93         | I/O              | I/O              | I/O              |

| 94         | I/O              | I/O              | I/O              |

| 95         | I/O              | I/O              | I/O              |

| 96         | NC               | I/O              | I/O              |

| 97         | NC               | I/O              | I/O              |

| 98         | I/O              | I/O              | I/O              |

| 99         | I/O              | I/O              | I/O              |

| 100        | I/O              | I/O              | I/O              |

| 101        | NC               | NC               | I/O              |

| 102        | I/O              | I/O              | I/O              |

| 103        | NC               | I/O              | I/O              |

| 104        | I/O              | I/O              | I/O              |

| 105        | I/O              | I/O              | I/O              |

| 106        | GND              | GND              | GND              |

| 107        | NC               | I/O              | I/O              |

| 108        | NC               | I/O              | TCK, I/O         |

| 109        | LP               | LP               | LP               |

| 110        | VCCA             | VCCA             | VCCA             |

| 111        | GND              | GND              | GND              |

| 112        | VCCI             | VCCI             | VCCI             |

| 113        | VCCA             | VCCA             | VCCA             |

| 114        | NC               | I/O              | I/O              |

| 115        | NC               | I/O              | I/O              |

| 116        | NC               | VCCA             | VCCA             |

| 117        | I/O              | I/O              | I/O              |

| 118        | I/O              | I/O              | I/O              |

| 119        | I/O              | I/O              | I/O              |

| 120        | I/O              | I/O              | I/O              |

#### Table 57 • TQ176

| TQ176      |                  |                  |                  |

|------------|------------------|------------------|------------------|

| Pin Number | A42MX09 Function | A42MX16 Function | A42MX24 Function |

| 121        | NC               | NC               | I/O              |

| 122        | I/O              | I/O              | I/O              |

| 123        | I/O              | I/O              | I/O              |

| 124        | NC               | I/O              | I/O              |

| 125        | NC               | I/O              | I/O              |

| 126        | NC               | NC               | I/O              |

| 127        | I/O              | I/O              | I/O              |

| 128        | I/O              | I/O              | I/O              |

| 129        | I/O              | I/O              | I/O              |

| 130        | I/O              | I/O              | I/O              |

| 131        | I/O              | I/O              | I/O              |

| 132        | I/O              | I/O              | I/O              |

| 133        | GND              | GND              | GND              |

| 134        | I/O              | I/O              | I/O              |

| 135        | SDI, I/O         | SDI, I/O         | SDI, I/O         |

| 136        | NC               | I/O              | I/O              |

| 137        | I/O              | I/O              | WD, I/O          |

| 138        | I/O              | I/O              | WD, I/O          |

| 139        | I/O              | I/O              | I/O              |

| 140        | NC               | VCCI             | VCCI             |

| 141        | I/O              | I/O              | I/O              |

| 142        | I/O              | I/O              | I/O              |

| 143        | NC               | I/O              | I/O              |

| 144        | NC               | I/O              | WD, I/O          |

| 145        | NC               | NC               | WD, I/O          |

| 146        | I/O              | I/O              | I/O              |

| 147        | NC               | I/O              | I/O              |

| 148        | I/O              | I/O              | I/O              |

| 149        | I/O              | I/O              | I/O              |

| 150        | I/O              | I/O              | WD, I/O          |

| 151        | NC               | I/O              | WD, I/O          |

| 152        | PRA, I/O         | PRA, I/O         | PRA, I/O         |

| 153        | I/O              | I/O              | I/O              |

| 154        | CLKA, I/O        | CLKA, I/O        | CLKA, I/O        |

| 155        | VCCA             | VCCA             | VCCA             |

| 156        | GND              | GND              | GND              |

| 157        | I/O              | I/O              | I/O              |

| CQ208      |                  |

|------------|------------------|

| Pin Number | A42MX36 Function |

| 37         | I/O              |

| 38         | I/O              |

| 39         | I/O              |

| 40         | I/O              |

| 41         | I/O              |

| 42         | I/O              |

| 43         | I/O              |

| 44         | I/O              |

| 45         | I/O              |

| 46         | I/O              |

| 47         | I/O              |

| 48         | I/O              |

| 49         | I/O              |

| 50         | I/O              |

| 51         | I/O              |

| 52         | GND              |

| 53         | GND              |

| 54         | TMS, I/O         |

| 55         | TDI, I/O         |

| 56         | I/O              |

| 57         | WD, I/O          |

| 58         | WD, I/O          |

| 59         | I/O              |

| 60         | VCCI             |

| 61         | I/O              |

| 62         | I/O              |

| 63         | I/O              |

| 64         | I/O              |

| 65         | QCLKA, I/O       |

| 66         | WD, I/O          |

| 67         | WD, I/O          |

| 68         | I/O              |

| 69         | I/O              |

| 70         | WD, I/O          |

| 71         | WD, I/O          |

| 72         | I/O              |

| 73         | I/O              |

| CQ208      |                  |

|------------|------------------|

| Pin Number | A42MX36 Function |

| 74         | I/O              |

| 75         | I/O              |

| 76         | I/O              |

| 77         | I/O              |

| 78         | GND              |

| 79         | VCCA             |

| 80         | VCCI             |

| 81         | I/O              |

| 32         | I/O              |

| 83         | I/O              |

| 84         | I/O              |

| 35         | WD, I/O          |

| 36         | WD, I/O          |

| 87         | I/O              |

| 88         | I/O              |

| 89         | I/O              |

| 90         | I/O              |

| 91         | QCLKB, I/O       |

| 92         | I/O              |

| 93         | WD, I/O          |

| 94         | WD, I/O          |

| 95         | I/O              |

| 96         | I/O              |

| 97         | I/O              |

| 98         | VCCI             |

| 99         | I/O              |

| 100        | WD, I/O          |

| 101        | WD, I/O          |

| 102        | I/O              |

| 103        | TDO, I/O         |

| 104        | I/O              |

| 105        | GND              |

| 106        | VCCA             |

| 107        | I/O              |

| 108        | I/O              |

| 109        | I/O              |

| 110        | I/O              |

| Table 60 • BG | 272              |

|---------------|------------------|

| BG272         |                  |

| Pin Number    | A42MX36 Function |

| D20           | I/O              |

| E1            | I/O              |

| E2            | I/O              |

| E3            | I/O              |

| E4            | VCCA             |

| E17           | VCCI             |

| E18           | I/O              |

| E19           | I/O              |

| E20           | I/O              |

| F1            | I/O              |

| F2            | I/O              |

| F3            | I/O              |

| F4            | VCCI             |

| F17           | I/O              |

| F18           | I/O              |

| F19           | I/O              |

| F20           | I/O              |

| G1            | I/O              |

| G2            | I/O              |

| G3            | I/O              |

| G4            | VCCI             |

| G17           | VCCI             |

| G18           | I/O              |

| G19           | I/O              |

| G20           | I/O              |

| H1            | I/O              |

| H2            | I/O              |

| H3            | I/O              |

| H4            | VCCA             |

| H17           | I/O              |

| H18           | I/O              |

| H19           | I/O              |

| H20           | I/O              |

| J1            | I/O              |

| J2            | I/O              |

| J3            | I/O              |

| J4            | VCCI             |

### Figure 53 • CQ172

| CQ172      |                     |  |

|------------|---------------------|--|

| Pin Number | A42MX16<br>Function |  |

| 1          | MODE                |  |

| 2          | I/O                 |  |

| 3          | I/O                 |  |

| 4          | I/O                 |  |

| 5          | I/O                 |  |

| 6          | I/O                 |  |

| 7          | GND                 |  |

| 8          | I/O                 |  |

| 9          | I/O                 |  |

| 10         | I/O                 |  |

| 11         | I/O                 |  |

| 12         | VCC                 |  |

| 13         | I/O                 |  |

| 14         | I/O                 |  |

| 15         | I/O                 |  |

| 16         | I/O                 |  |

| 17         | GND                 |  |

| 18         | I/O                 |  |

| 19         | I/O                 |  |

| 20         | I/O                 |  |

|            |                     |  |

| <i>Table 62</i> • CQ172 |       |

|-------------------------|-------|

| 138                     | I/O   |

| 139                     | I/O   |

| 140                     | I/O   |

| 141                     | GND   |

| 142                     | I/O   |

| 143                     | I/O   |

| 144                     | I/O   |

| 145                     | I/O   |

| 146                     | I/O   |

| 147                     | I/O   |

| 148                     | PROBA |

| 149                     | I/O   |

| 150                     | CLKA  |

| 151                     | VCC   |

| 152                     | GND   |

| 153                     | I/O   |

| 154                     | CLKB  |

| 155                     | I/O   |

| 156                     | PROBB |

| 157                     | I/O   |

| 158                     | I/O   |

| 159                     | I/O   |

| 160                     | I/O   |

| 161                     | GND   |

| 162                     | I/O   |

| 163                     | I/O   |

| 164                     | I/O   |

| 165                     | I/O   |

| 166                     | VCCI  |

| 167                     | I/O   |

| 168                     | I/O   |

| 169                     | I/O   |

| 170                     | I/O   |

| 171                     | DCLK  |

|                         |       |