# E·XFL

#### Welcome to E-XFL.COM

#### Understanding Embedded - Microprocessors

Embedded microprocessors are specialized computing chips designed to perform specific tasks within an embedded system. Unlike general-purpose microprocessors found in personal computers, embedded microprocessors are tailored for dedicated functions within larger systems, offering optimized performance, efficiency, and reliability. These microprocessors are integral to the operation of countless electronic devices, providing the computational power necessary for controlling processes, handling data, and managing communications.

#### Applications of **Embedded - Microprocessors**

Embedded microprocessors are utilized across a broad spectrum of applications, making them indispensable in

#### Details

| Product Status                  | Active                                                                |

|---------------------------------|-----------------------------------------------------------------------|

| Core Processor                  | ARM1136JF-S                                                           |

| Number of Cores/Bus Width       | 1 Core, 32-Bit                                                        |

| Speed                           | 532MHz                                                                |

| Co-Processors/DSP               | Multimedia; GPU, IPU, VFP                                             |

| RAM Controllers                 | LPDDR, DDR2                                                           |

| Graphics Acceleration           | Yes                                                                   |

| Display & Interface Controllers | Keypad, KPP, LCD                                                      |

| Ethernet                        | 10/100Mbps (1)                                                        |

| SATA                            | -                                                                     |

| USB                             | USB 2.0 + PHY (2)                                                     |

| Voltage - I/O                   | 1.8V, 2.0V, 2.5V, 2.7V, 3.0V, 3.3V                                    |

| Operating Temperature           | -40°C ~ 85°C (TA)                                                     |

| Security Features               | Secure Fusebox, Secure JTAG, Tamper Detection                         |

| Package / Case                  | 400-LFBGA                                                             |

| Supplier Device Package         | 400-LFBGA (17x17)                                                     |

| Purchase URL                    | https://www.e-xfl.com/product-detail/nxp-semiconductors/mcimx353cjq5c |

|                                 |                                                                       |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

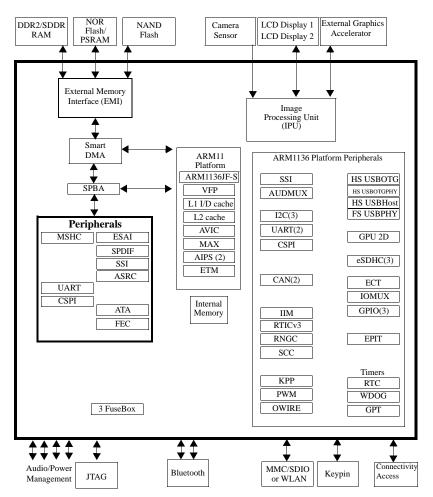

## 1.3 Block Diagram

Figure 1 is the i.MX35 simplified interface block diagram.

Figure 1. i.MX35 Simplified Interface Block Diagram

## 2 Functional Description and Application Information

The i.MX35 consists of the following major subsystems:

- ARM1136 Platform—AP domain

- SDMA Platform and EMI—Shared domain

## 2.1 Application Processor Domain Overview

The applications processor (AP) and its domain are responsible for running the operating system and applications software, providing the user interface, and supplying access to integrated and external peripherals. The AP domain is built around an ARM1136JF-S core with 16-Kbyte instruction and data L1 caches, an MMU, a 128-Kbyte L2 cache, a multiported crossbar switch, and advanced debug and trace interfaces.

| Block<br>Mnemonic | Block Name                                        | Domain <sup>1</sup> | Subsystem                       | Brief Description                                                                                                                                                                                                                                                                                                                                                                                                                       |

|-------------------|---------------------------------------------------|---------------------|---------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| ATA               | ATA module                                        | SDMA                | Connectivity peripherals        | The ATA block is an AT attachment host interface. Its main use is to interface with IDE hard disk drives and ATAPI optical disk drives. It interfaces with the ATA device over a number of ATA signals.                                                                                                                                                                                                                                 |

| AUDMUX            | Digital audio<br>mux                              | ARM                 | Multimedia<br>peripherals       | The AUDMUX is a programmable interconnect for voice, audio, and<br>synchronous data routing between host serial interfaces (SSIs) and<br>peripheral serial interfaces (audio codecs). The AUDMUX has two<br>sets of interfaces: internal ports to on-chip peripherals and external<br>ports to off-chip audio devices. Data is routed by configuring the<br>appropriate internal and external ports.                                    |

| CAN(2)            | CAN module                                        | ARM                 | Connectivity peripherals        | The CAN protocol is primarily designed to be used as a vehicle serial data bus running at 1 Mbps.                                                                                                                                                                                                                                                                                                                                       |

| ССМ               | Clock control<br>module                           | ARM                 | Clocks                          | This block generates all clocks for the peripherals in the SDMA platform. The CCM also manages ARM1136 platform low-power modes (WAIT, STOP), disabling peripheral clocks appropriately for power conservation, and provides alternate clock sources for the ARM1136 and SDMA platforms.                                                                                                                                                |

| CSPI(2)           | Configurable<br>serial<br>peripheral<br>interface | SDMA,<br>ARM        | Connectivity<br>peripherals     | This module is a serial interface equipped with data FIFOs; each master/slave-configurable SPI module is capable of interfacing to both serial port interface master and slave devices. The CSPI ready (SPI_RDY) and slave select (SS) control signals enable fast data communication with fewer software interrupts.                                                                                                                   |

| ECT               | Embedded<br>cross trigger                         | SDMA,<br>ARM        | Debug                           | ECT (embedded cross trigger) is an IP for real-time debug<br>purposes. It is a programmable matrix allowing several subsystems<br>to interact with each other. ECT receives signals required for<br>debugging purposes (from cores, peripherals, buses, external<br>inputs, and so on) and propagates them (propagation programmed<br>through software) to the different debug resources available within<br>the SoC.                   |

| EMI               | External<br>memory<br>interface                   | SDMA                | External<br>memory<br>interface | The EMI module provides access to external memory for the ARM<br>and other masters. It is composed of the following main<br>submodules:<br>M3IF—provides arbitration between multiple masters requesting<br>access to the external memory.<br>SDRAM CTRL—interfaces to mDDR, DDR2 (4-bank architecture<br>type), and SDR interfaces.<br>NANDFC—provides an interface to NAND Flash memories.<br>WEIM—interfaces to NOR Flash and PSRAM. |

| EPIT(2)           | Enhanced<br>periodic<br>interrupt timer           | ARM                 | Timer<br>peripherals            | Each EPIT is a 32-bit "set-and-forget" timer that starts counting after<br>the EPIT is enabled by software. It is capable of providing precise<br>interrupts at regular intervals with minimal processor intervention. It<br>has a 12-bit prescaler to adjust the input clock frequency to the<br>required time setting for the interrupts, and the counter value can be<br>programmed on the fly.                                      |

| Block<br>Mnemonic | Block Name                                    | Domain <sup>1</sup> | Subsystem                   | Brief Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

|-------------------|-----------------------------------------------|---------------------|-----------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| ESAI              | Enhanced<br>serial audio<br>interface         | SDMA                | Connectivity peripherals    | The enhanced serial audio interface (ESAI) provides a full-duplex<br>serial port for serial communication with a variety of serial devices,<br>including industry-standard codecs, SPDIF transceivers, and other<br>DSPs. The ESAI consists of independent transmitter and receiver<br>sections, each section with its own clock generator.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| eSDHCv2<br>(3)    | Enhanced<br>secure digital<br>host controller | ARM                 | Connectivity<br>peripherals | The eSDHCv2 consists of four main modules: CE-ATA, MMC, SD<br>and SDIO. CE-ATA is a hard drive interface that is optimized for<br>embedded applications of storage. The MultiMediaCard (MMC) is a<br>universal, low-cost, data storage and communication media to<br>applications such as electronic toys, organizers, PDAs, and smart<br>phones. The secure digital (SD) card is an evolution of MMC and is<br>specifically designed to meet the security, capacity, performance,<br>and environment requirements inherent in emerging audio and<br>video consumer electronic devices. SD cards are categorized into<br>Memory and I/O. A memory card enables a copyright protection<br>mechanism that complies with the SDMI security standard. SDIO<br>cards provide high-speed data I/O (such as wireless LAN via SDIO<br>interface) with low power consumption.<br><b>Note:</b> CE-ATA is not available for the MCIMX351. |

| FEC               | Ethernet                                      | SDMA                | Connectivity peripherals    | The Ethernet media access controller (MAC) is designed to support<br>both 10 and 100 Mbps Ethernet/IEEE 802.3 networks. An external<br>transceiver interface and transceiver function are required to<br>complete the interface to the media                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| GPIO(3)           | General<br>purpose I/O<br>modules             | ARM                 | Pins                        | Used for general purpose input/output to external ICs. Each GPIO module supports 32 bits of I/O.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| GPT               | General<br>purpose timers                     | ARM                 | Timer<br>peripherals        | Each GPT is a 32-bit free-running or set-and-forget mode timer with<br>a programmable prescaler and compare and capture registers. A<br>timer counter value can be captured using an external event and can<br>be configured to trigger a capture event on either the leading or<br>trailing edges of an input pulse. When the timer is configured to<br>operate in set-and-forget mode, it is capable of providing precise<br>interrupts at regular intervals with minimal processor intervention.<br>The counter has output compare logic to provide the status and<br>interrupt at comparison. This timer can be configured to run either<br>on an external clock or on an internal clock.                                                                                                                                                                                                                                  |

| GPU2D             | Graphics<br>processing unit<br>2Dv1           | ARM                 | Multimedia<br>peripherals   | This module accelerates OpenVG and GDI graphics.<br>Note: Not available for the MCIMX351.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

Table 4. Digital and Analog Modules (continued)

Table 26. AC Electrical Characteristics of DDR Type IO Pins in SDRAM Mode Max Drive (1.8 V)

| Parameter                                      | Symbol | Test Condition | Min.<br>Rise/Fall      | Тур.                   | Max.<br>Rise/Fall      | Units |

|------------------------------------------------|--------|----------------|------------------------|------------------------|------------------------|-------|

| Clock frequency                                | f      | _              | 125                    | _                      | —                      | MHz   |

| Output pin slew rate (max. drive) <sup>1</sup> | tps    | 25 pF<br>50 pF | 2.83/2.68<br>1.59/1.49 | 1.84/1.85<br>1.03/1.05 | 1.21/1.40<br>0.70/0.75 | V/ns  |

| Output pin di/dt (max. drive) <sup>2</sup>     | didt   | 25 pF<br>50 pF | 89<br>95               | 202<br>213             | 435<br>456             | mA/ns |

| Input pin transition times <sup>3</sup>        | trfi   | 1.0 pF         | 0.07/0.08              | 0.11/0.12              | 0.16/0.20              | ns    |

| Input pin propagation delay, 50%–50%           | tpi    | 1.0 pF         | 0.35/1.17              | 0.63/1.53              | 1.16/2.04              | ns    |

| Input pin propagation delay, 40%-60%           | tpi    | 1.0 pF         | 1.18/1.99              | 1.45/2.35              | 1.97/2.85              | ns    |

<sup>1</sup> Min. condition for tps: wcs model, 1.1 V, IO 1.65 V, and 105 °C. tps is measured between VIL to VIH for rising edge and between VIH to VIL for falling edge.

$^2\,$  Max. condition for tdit: bcs model, 1.3 V, IO 1.95 V, and –40 °C.

<sup>3</sup> Max. condition for tpi and trfi: wcs model, 1.1 V, IO 1.65 V and 105 °C. Min. condition for tpi and trfi: bcs model, 1.3 V, IO 1.95 V and -40 °C. Input transition time from pad is 5 ns (20%–80%).

## 4.9 Module-Level AC Electrical Specifications

This section contains the AC electrical information (including timing specifications) for the modules of the i.MX35. The modules are listed in alphabetical order.

## 4.9.1 AUDMUX Electrical Specifications

The AUDMUX provides a programmable interconnect logic for voice, audio and data routing between internal serial interfaces (SSI) and external serial interfaces (audio and voice codecs). The AC timing of AUDMUX external pins is hence governed by the SSI module. See the electrical specification for SSI.

## 4.9.2 CSPI AC Electrical Specifications

The i.MX35 provides two CSPI modules. CSPI ports are multiplexed in the i.MX35 with other pins. See the "External Signals and Multiplexing" chapter of the reference manual for more details.

| ID   | Parameter           | Symbol | Timing<br>T = NFC Clock Cycle <sup>2</sup> |      | Example Timing for NFC Clock $\approx$ 33 MHz T = 30 ns |      | Unit |

|------|---------------------|--------|--------------------------------------------|------|---------------------------------------------------------|------|------|

|      |                     |        | Min.                                       | Max. | Min.                                                    | Max. |      |

| NF5  | NF_WP pulse width   | tWP    | T – 1.0 n                                  | IS   | 2                                                       | 29   | ns   |

| NF6  | NFALE setup time    | tALS   | T – 4.0 ns                                 | —    | 26                                                      | —    | ns   |

| NF7  | NFALE hold time     | tALH   | T – 4.5 ns                                 | _    | 25.5                                                    | _    | ns   |

| NF8  | Data setup time     | tDS    | T – 2.0 ns                                 | _    | 28                                                      | _    | ns   |

| NF9  | Data hold time      | tDH    | T – 5.0 ns                                 | _    | 25                                                      | _    | ns   |

| NF10 | Write cycle time    | tWC    | 2T – 3.0 ns                                |      | 57                                                      |      | ns   |

| NF11 | NFWE hold time      | tWH    | T – 5.0 ns 25                              |      | 25                                                      | ns   |      |

| NF12 | Ready to NFRE low   | tRR    | 6T                                         | —    | 180                                                     | —    | ns   |

| NF13 | NFRE pulse width    | tRP    | 1.5T – 1.0 ns                              | -    | 44                                                      | -    | ns   |

| NF14 | READ cycle time     | tRC    | 2T – 5.5 ns                                | -    | 54.5                                                    | -    | ns   |

| NF15 | NFRE high hold time | tREH   | 0.5T – 4.0 ns                              |      | 11                                                      | —    | ns   |

| NF16 | Data setup on READ  | tDSR   | N/A                                        |      | 9                                                       | —    | ns   |

| NF17 | Data hold on READ   | tDHR   | N/A                                        |      | 0                                                       |      | ns   |

Table 32. NFC Timing Parameters<sup>1</sup> (continued)

<sup>1</sup> The flash clock maximum frequency is 50 MHz.

<sup>2</sup> Subject to DPLL jitter specification listed in Table 28, "DPLL Specifications," on page 31.

#### NOTE

High is defined as 80% of signal value and low is defined as 20% of signal value.

Timing for HCLK is 133 MHz and internal NFC clock (flash clock) is approximately 33 MHz (30 ns). All timings are listed according to this NFC clock frequency (multiples of NFC clock phases), except NF16 and NF17, which are not NFC clock related.

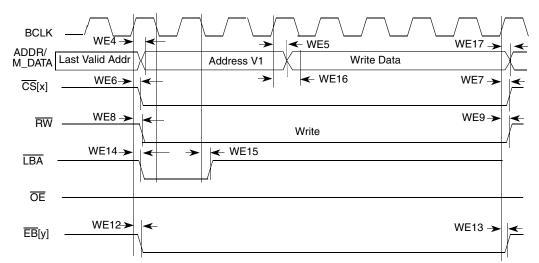

### 4.9.5.2 Wireless External Interface Module (WEIM)

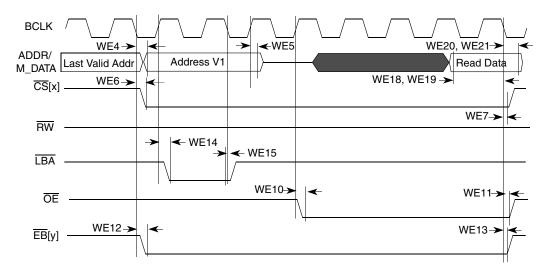

All WEIM output control signals may be asserted and deasserted by internal clocks related to the BCLK rising edge or falling edge according to the corresponding assertion or negation control fields. The address always begins related to BCLK falling edge but may be ended both on rising and falling edge in muxed mode according to control register configuration. Output data begins related to BCLK rising edge except in muxed mode where both rising and falling edge may be used according to control register configuration.

Figure 21. Muxed A/D Mode Timing Diagram for Synchronous Read Access-WSC = 7, LBA = 1, LBN = 1, LAH = 1, OEA = 7

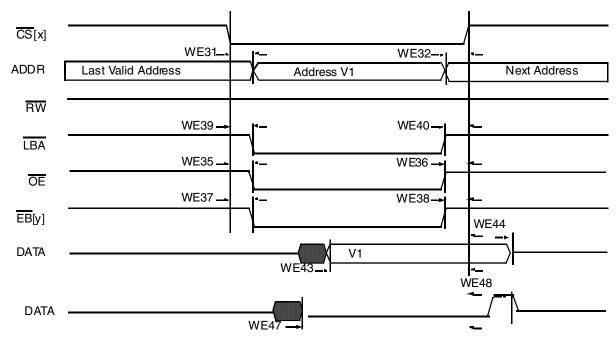

Figure 26. DTACK Read Access

| Ref No.                 | Parameter                                              | Determination By<br>Synchronous Measured<br>Parameters <sup>1</sup> | Min                                            | Max<br>(If 133 MHz is<br>supported by SoC)    | Unit |

|-------------------------|--------------------------------------------------------|---------------------------------------------------------------------|------------------------------------------------|-----------------------------------------------|------|

| WE31                    | CS[x] valid to Address valid                           | WE4 – WE6 – CSA <sup>2</sup>                                        | _                                              | 3 – CSA                                       | ns   |

| WE32                    | Address invalid to $\overline{CS}[x]$ invalid          | WE7 – WE5 – CSN <sup>3</sup>                                        | _                                              | 3 – CSN                                       | ns   |

| WE32A(<br>muxed<br>A/D  | CS[x] valid to address invalid                         | WE4 – WE7 + (LBN + LBA + 1<br>– CSA <sup>2</sup> )                  | -3+(LBN+LBA+<br>1-CSA)                         | _                                             | ns   |

| WE33                    | $\overline{CS}[x]$ valid to $\overline{WE}$ valid      | WE8 – WE6 + (WEA – CSA)                                             | _                                              | 3 + (WEA – CSA)                               | ns   |

| WE34                    | $\overline{WE}$ invalid to $\overline{CS}[x]$ invalid  | WE7 – WE9 + (WEN – CSN)                                             | _                                              | 3 – (WEN_CSN)                                 | ns   |

| WE35                    | $\overline{CS}[x]$ valid to $\overline{OE}$ valid      | WE10 – WE6 + (OEA – CSA)                                            | _                                              | 3 + (OEA – CSA)                               | ns   |

| WE35A<br>(muxed<br>A/D) | $\overline{CS}[x]$ valid to $\overline{OE}$ valid      | WE10 – WE6 + (OEA + RLBN<br>+ RLBA + ADH + 1 – CSA)                 | -3 + (OEA +<br>RLBN + RLBA +<br>ADH + 1 – CSA) | 3 + (OEA + RLBN +<br>RLBA + ADH + 1 –<br>CSA) | ns   |

| WE36                    | $\overline{OE}$ invalid to $\overline{CS}[x]$ invalid  | WE7 – WE11 + (OEN – CSN)                                            | _                                              | 3 – (OEN – CSN)                               | ns   |

| WE37                    | CS[x] valid to BE[y] valid (read access)               | WE12 – WE6 + (RBEA – CSA)                                           | _                                              | 3 + (RBEA <sup>4</sup> – CSA)                 | ns   |

| WE38                    | BE[y] invalid to CS[x] invalid (read access)           | WE7 – WE13 + (RBEN – CSN)                                           | —                                              | 3 – (RBEN <sup>5</sup> – CSN)                 | ns   |

| WE39                    | CS[x] valid to LBA valid                               | WE14 – WE6 + (LBA – CSA)                                            | —                                              | 3 + (LBA – CSA)                               | ns   |

| WE40                    | $\overline{LBA}$ invalid to $\overline{CS}[x]$ invalid | WE7 – WE15 – CSN                                                    |                                                | 3 – CSN                                       | ns   |

| Ref No.                 | Parameter                                            | Determination By<br>Synchronous Measured<br>Parameters <sup>1</sup> | Min                                                                  | Max<br>(If 133 MHz is<br>supported by SoC) | Unit |

|-------------------------|------------------------------------------------------|---------------------------------------------------------------------|----------------------------------------------------------------------|--------------------------------------------|------|

| WE40A<br>(muxed<br>A/D) | CS[x] valid to LBA invalid                           | WE14 – WE6 + (LBN + LBA + 1<br>– CSA)                               | –3 + (LBN + LBA +<br>1 – CSA)                                        | 3 + (LBN + LBA + 1 –<br>CSA)               | ns   |

| WE41                    | $\overline{CS}[x]$ valid to Output Data valid        | WE16 – WE6 – WCSA                                                   | —                                                                    | 3 – WCSA                                   | ns   |

| WE41A<br>(muxed<br>A/D) | CS[x] valid to Output Data valid                     | WE16 – WE6 + (WLBN +<br>WLBA + ADH + 1 – WCSA)                      | _                                                                    | 3 + (WLBN + WLBA +<br>ADH + 1 – WCSA)      | ns   |

| WE42                    | Output Data invalid to $\overline{CS}[x]$<br>Invalid | WE17 – WE7 – CSN                                                    | _                                                                    | 3 – CSN                                    | ns   |

| WE43                    | Input Data valid to $\overline{CS}[x]$ invalid       | MAXCO – MAXCSO + MAXDI                                              | MAXCO <sup>6 –</sup><br>MAXCSO <sup>7</sup> +<br>MAXDI <sup>8</sup>  | _                                          | ns   |

| WE44                    | CS[x] invalid to Input Data<br>invalid               | 0                                                                   | 0                                                                    | _                                          | ns   |

| WE45                    | CS[x] valid to BE[y] valid (write access)            | WE12 – WE6 + (WBEA – CSA)                                           | _                                                                    | 3 + (WBEA – CSA)                           | ns   |

| WE46                    | BE[y] invalid to CS[x] invalid (write access)        | WE7 – WE13 + (WBEN – CSN)                                           | _                                                                    | -3 + (WBEN - CSN)                          | ns   |

| WE47                    | DTACK valid to CS[x] invalid                         | MAXCO – MAXCSO + MAXDTI                                             | MAXCO <sup>6</sup> –<br>MAXCSO <sup>7</sup> +<br>MAXDTI <sup>9</sup> | —                                          | ns   |

| WE48                    | CS[x] Invalid to DTACK invalid                       | 0                                                                   | 0                                                                    |                                            | ns   |

#### Table 34. WEIM Asynchronous Timing Parameters Relative Chip Select Table (continued)

<sup>1</sup> For the value of parameters WE4–WE21, see column BCD = 0 in Table 33.

<sup>2</sup>  $\overline{\text{CS}}$  Assertion. This bit field determines when the  $\overline{\text{CS}}$  signal is asserted during read/write cycles.

<sup>3</sup>  $\overline{\text{CS}}$  Negation. This bit field determines when the  $\overline{\text{CS}}$  signal is negated during read/write cycles.

<sup>4</sup>  $\overline{\text{BE}}$  Assertion. This bit field determines when the  $\overline{\text{BE}}$  signal is asserted during read cycles.

<sup>5</sup>  $\overline{\text{BE}}$  Negation. This bit field determines when the  $\overline{\text{BE}}$  signal is negated during read cycles.

<sup>6</sup> Output maximum delay from internal driving ADDR/control FFs to chip outputs.

<sup>7</sup> Output maximum delay from  $\overline{CS}[x]$  internal driving FFs to  $\overline{CS}[x]$  out.

<sup>8</sup> DATA maximum delay from chip input data to its internal FF.

<sup>9</sup> DTACK maximum delay from chip dtack input to its internal FF.

Note: All configuration parameters (CSA, CSN, WBEA, WBEN, LBA, LBN, OEN, OEA, RBEA, and RBEN) are in cycle units.

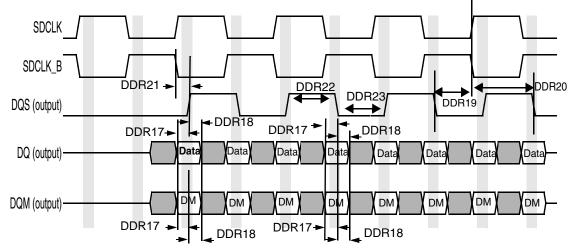

Figure 32. DDR2 SDRAM Write Cycle Timing Diagram

| ID    |                                                           | Quarte e l    | DDR2-400 |      | 11   |

|-------|-----------------------------------------------------------|---------------|----------|------|------|

|       | PARAMETER                                                 | Symbol        | Min      | Max  | Unit |

| DDR17 | DQ and DQM setup time to DQS (single-ended strobe)        | tDS1(base)    | 0.5      | —    | ns   |

| DDR18 | DQ and DQM hold time to DQS (single-ended strobe)         | tDH1(base)    | 0.5      | —    | ns   |

| DDR19 | Write cycle DQS falling edge to SDCLK output setup time.  | tDSS          | 0.2      | —    | tCK  |

| DDR20 | Write cycle DQS falling edge to SDCLK output hold time.   | <b>t</b> DSH  | 0.2      | —    | tCK  |

| DDR21 | DQS latching rising transitions to associated clock edges | tDQSS         | -0.25    | 0.25 | tCK  |

| DDR22 | DQS high level width                                      | <b>t</b> DQSH | 0.35     | —    | tCK  |

| DDR23 | DQS low level width                                       | tDQSL         | 0.35     | —    | tCK  |

#### Table 41. DDR2 SDRAM Write Cycle Parameters

#### NOTE

These values are for DQ/DM slew rate of 1 V/ns and DQS slew rate of 1 V/ns. For different values use the derating table.

| ID    | PARAMETER                                                                    | Symbol         | DDR2-400 |      | Unit |

|-------|------------------------------------------------------------------------------|----------------|----------|------|------|

|       | ID PARAMETER                                                                 |                | Min      | Max  |      |

| DDR24 | DQS – DQ Skew (defines the Data valid window in read cycles related to DQS). | tDQSQ          | —        | 0.35 | ns   |

| DDR25 | DQS DQ in HOLD time from DQS <sup>1</sup>                                    | tqн            | 2.925    | —    | ns   |

| DDR26 | DQS output access time from SDCLK posedge                                    | <b>t</b> DQSCK | -0.5     | 0.5  | ns   |

#### Table 43. DDR2 SDRAM Read Cycle Parameter Table

<sup>1</sup>The value was calculated for an SDCLK frequency of 133 MHz by the formula  $tQH = tHP - tQHS = min (tCL, tCH) - tQHS = 0.45 \times tCK - tQHS = 0.45 \times 7.5 - 0.45 = 2.925 ns.$

#### NOTE

SDRAM CLK and DQS-related parameters are measured from the 50% point—that is, "high" is defined as 50% of signal value and "low" is defined as 50% of signal value. DDR SDRAM CLK parameters are measured at the crossing point of SDCLK and SDCLK (inverted clock).

Test conditions are: Capacitance 15 pF for DDR PADS. Recommended drive strength is Medium for SDCLK and High for Address and controls.

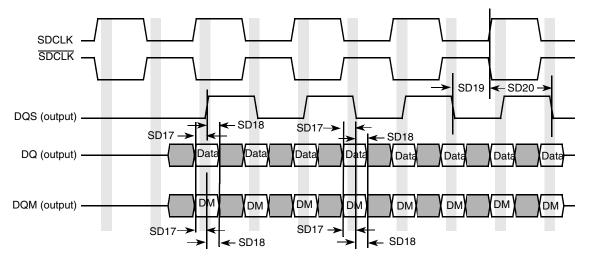

| Figure 34. Mobile DDR SDRAM Write | Cycle Timing Diagram |

|-----------------------------------|----------------------|

|-----------------------------------|----------------------|

| ID   | Parameter                                                | Symbol | Min. | Max. | Unit |

|------|----------------------------------------------------------|--------|------|------|------|

| SD17 | DQ and DQM setup time to DQS                             | tDS    | 0.95 | _    | ns   |

| SD18 | DQ and DQM hold time to DQS                              | tDH    | 0.95 | _    | ns   |

| SD19 | Write cycle DQS falling edge to SDCLK output delay time. | tDSS   | 1.8  | _    | ns   |

| SD20 | Write cycle DQS falling edge to SDCLK output hold time.  | tDSH   | 1.8  | _    | ns   |

<sup>1</sup> Test condition: Measured using delay line 5 programmed as follows: ESDCDLY5[15:0] = 0x0703.

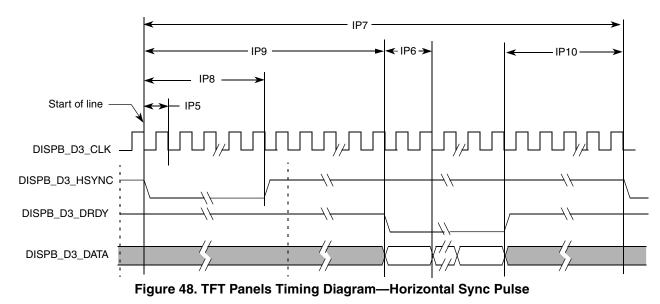

of the DISPB\_D3\_CLK signal and active-low polarity of the DISPB\_D3\_HSYNC, DISPB\_D3\_VSYNC and DISPB\_D3\_DRDY signals.

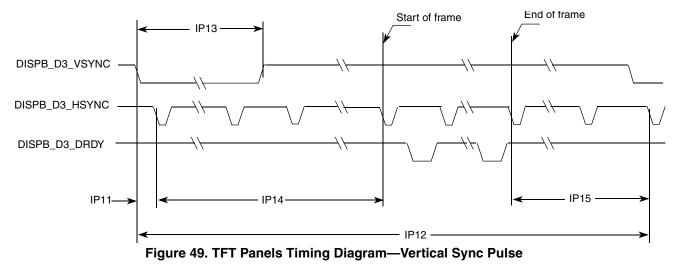

Figure 49 depicts the vertical timing (timing of one frame). All figure parameters shown are programmable.

Table 55 shows timing parameters of signals presented in Figure 48 and Figure 49.

#### Table 55. Synchronous Display Interface Timing Parameters—Pixel Level

| ID  | Parameter                      | Symbol | Value                            | Units |

|-----|--------------------------------|--------|----------------------------------|-------|

| IP5 | Display interface clock period | Tdicp  | Tdicp <sup>1</sup>               | ns    |

| IP6 | Display pixel clock period     | Tdpcp  | (DISP3_IF_CLK_CNT_D + 1) × Tdicp | ns    |

| IP7 | Screen width                   | Tsw    | (SCREEN_WIDTH + 1) × Tdpcp       | ns    |

| IP8 | HSYNC width                    | Thsw   | (H_SYNC_WIDTH + 1) × Tdpcp       | ns    |

### 4.9.13.3 Synchronous Interface to Dual-Port Smart Displays

Functionality and electrical characteristics of the synchronous interface to dual-port smart displays are identical to parameters of the synchronous interface. See Section 4.9.13.1.5, "Interface to Active Matrix TFT LCD Panels, Electrical Characteristics."

### 4.9.13.3.6 Interface to a TV Encoder—Functional Description

The interface has an 8-bit data bus, transferring a single 8-bit value (Y/U/V) in each cycle. The bits D7–D0 of the value are mapped to bits LD17–LD10 of the data bus, respectively. Figure 52 depicts the interface timing.

- The frequency of the clock DISPB\_D3\_CLK is 27 MHz.

- The DISPB\_D3\_HSYNC, DISPB\_D3\_VSYNC and DISPB\_D3\_DRDY signals are active low.

- The transition to the next row is marked by the negative edge of the DISPB\_D3\_HSYNC signal. It remains low for a single clock cycle.

- The transition to the next field/frame is marked by the negative edge of the DISPB\_D3\_VSYNC signal. It remains low for at least one clock cycle.

- At a transition to an odd field (of the next frame), the negative edges of DISPB\_D3\_VSYNC and DISPB\_D3\_HSYNC coincide.

- At a transition to an even field (of the same frame), they do not coincide.

- The active intervals—during which data is transferred—are marked by the DISPB\_D3\_HSYNC signal being high.

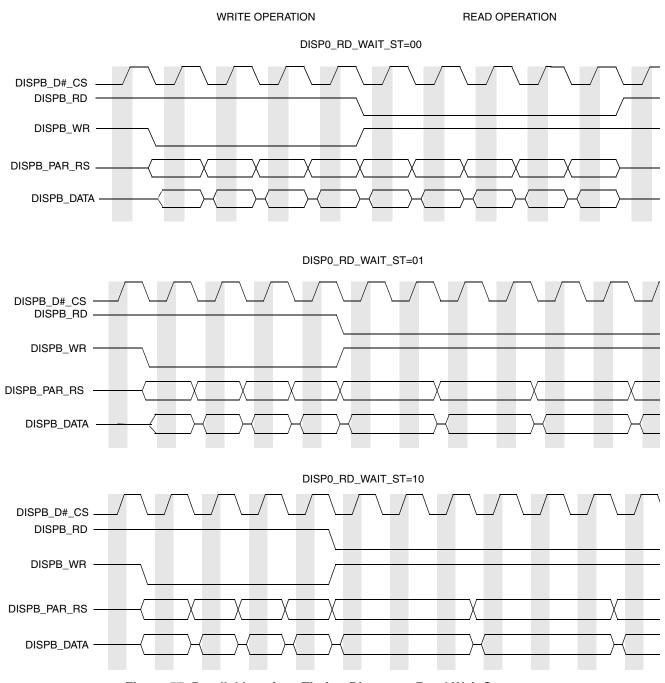

DI\_DISP $n_TIME_CONF_3$  registers (n = 0,1,2). Figure 57 shows the timing of the parallel interface with read wait states.

Figure 57. Parallel Interface Timing Diagram—Read Wait States

#### 4.9.13.4.9 Parallel Interfaces, Electrical Characteristics

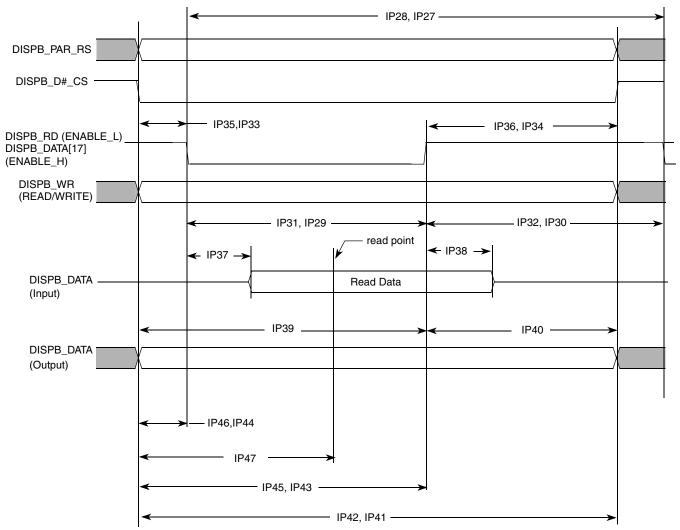

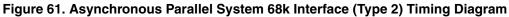

Figure 58, Figure 60, Figure 59, and Figure 61 depict timing of asynchronous parallel interfaces based on the system 80 and system 68k interfaces. Table 58 lists the timing parameters at display access level. All

| ID   | Parameter                    | Symbol | Min.                              | Typ. <sup>1</sup>                            | Max.                              | Units |

|------|------------------------------|--------|-----------------------------------|----------------------------------------------|-----------------------------------|-------|

| IP27 | Read system cycle time       | Tcycr  | Tdicpr – 1.5                      | Tdicpr <sup>2</sup>                          | Tdicpr + 1.5                      | ns    |

| IP28 | Write system cycle time      | Tcycw  | Tdicpw – 1.5                      | Tdicpw <sup>3</sup>                          | Tdicpw + 1.5                      | ns    |

| IP29 | Read low pulse width         | Trl    | Tdicdr – Tdicur – 1.5             | Tdicdr <sup>4</sup> – Tdicur <sup>5</sup>    | Tdicdr – Tdicur + 1.5             | ns    |

| IP30 | Read high pulse width        | Trh    | Tdicpr – Tdicdr +<br>Tdicur – 1.5 | Tdicpr – Tdicdr +<br>Tdicur                  | Tdicpr – Tdicdr + Tdicur<br>+ 1.5 | ns    |

| IP31 | Write low pulse width        | Twl    | Tdicdw – Tdicuw<br>– 1.5          | Tdicdw <sup>6</sup> –<br>Tdicuw <sup>7</sup> | Tdicdw – Tdicuw + 1.5             | ns    |

| IP32 | Write high pulse width       | Twh    | Tdicpw – Tdicdw +<br>Tdicuw – 1.5 | Tdicpw – Tdicdw<br>+ Tdicuw                  | Tdicpw – Tdicdw +<br>Tdicuw + 1.5 | ns    |

| IP33 | Controls setup time for read | Tdcsr  | Tdicur – 1.5                      | Tdicur                                       | —                                 | ns    |

| IP34 | Controls hold time for read  | Tdchr  | Tdicpr – Tdicdr – 1.5             | Tdicpr – Tdicdr                              | _                                 | ns    |

| ID   | Parameter                                | Symbol | Min.                          | Typ. <sup>1</sup> | Max.                                                     | Units |

|------|------------------------------------------|--------|-------------------------------|-------------------|----------------------------------------------------------|-------|

| IP35 | Controls setup time for write            | Tdcsw  | Tdicuw – 1.5                  | Tdicuw            | —                                                        | ns    |

| IP36 | Controls hold time for write             | Tdchw  | Tdicpw – Tdicdw – 1.5         | Tdicpw – Tdicdw   | —                                                        | ns    |

| IP37 | Slave device data delay <sup>8</sup>     | Tracc  | 0                             | -                 | Tdrp <sup>9</sup> – Tlbd <sup>10</sup> – Tdicur –<br>1.5 | ns    |

| IP38 | Slave device data hold time <sup>8</sup> | Troh   | Tdrp – Tlbd – Tdicdr<br>+ 1.5 | -                 | Tdicpr – Tdicdr – 1.5                                    | ns    |

| IP39 | Write data setup time                    | Tds    | Tdicdw – 1.5                  | Tdicdw            | —                                                        | ns    |

| IP40 | Write data hold time                     | Tdh    | Tdicpw – Tdicdw – 1.5         | Tdicpw – Tdicdw   | —                                                        | ns    |

| IP41 | Read period <sup>2</sup>                 | Tdicpr | Tdicpr – 1.5                  | Tdicpr            | Tdicpr + 1.5                                             | ns    |

| IP42 | Write period <sup>3</sup>                | Tdicpw | Tdicpw – 1.5                  | Tdicpw            | Tdicpw + 1.5                                             | ns    |

| IP43 | Read down time <sup>4</sup>              | Tdicdr | Tdicdr – 1.5                  | Tdicdr            | Tdicdr + 1.5                                             | ns    |

| IP44 | Read up time <sup>5</sup>                | Tdicur | Tdicur – 1.5                  | Tdicur            | Tdicur + 1.5                                             | ns    |

| IP45 | Write down time <sup>6</sup>             | Tdicdw | Tdicdw – 1.5                  | Tdicdw            | Tdicdw + 1.5                                             | ns    |

| IP46 | Write up time <sup>7</sup>               | Tdicuw | Tdicuw – 1.5                  | Tdicuw            | Tdicuw + 1.5                                             | ns    |

| IP47 | Read time point <sup>9</sup>             | Tdrp   | Tdrp – 1.5                    | Tdrp              | Tdrp + 1.5                                               | ns    |

Table 58. Asynchronous Parallel Interface Timing Parameters—Access Level (continued)

<sup>1</sup>The exact conditions have not been finalized, but will likely match the current customer requirement for their specific display. These conditions may be device-specific.

<sup>2</sup> Display interface clock period value for read:

$Tdicpr = T_{HSP\_CLK} \cdot ceil \left[ \frac{DISP\#\_IF\_CLK\_PER\_RD}{HSP\_CLK\_PERIOD} \right]$

<sup>3</sup> Display interface clock period value for write:

$Tdicpw = T_{HSP\_CLK} \cdot ceil \left[ \frac{DISP\#\_IF\_CLK\_PER\_WR}{HSP\_CLK\_PERIOD} \right]$

<sup>4</sup> Display interface clock down time for read:

$Tdicdr = \frac{1}{2}T_{HSP\_CLK} \cdot ceil \left[\frac{2 \cdot DISP\#\_IF\_CLK\_DOWN\_RD}{HSP\_CLK\_PERIOD}\right]$

<sup>5</sup> Display interface clock up time for read:  $Tdicur = \frac{1}{2}T_{HSP\_CLK} \cdot ceil \left[\frac{2 \cdot DISP\#\_IF\_CLK\_UP\_RD}{HSP\_CLK\_PERIOD}\right]$

<sup>6</sup> Display interface clock down time for write:  $Tdicdw = \frac{1}{2}T_{HSP\_CLK} \cdot ceil \left[\frac{2 \cdot DISP\#\_IF\_CLK\_DOWn\_WR}{HSP\_CLK\_PERIOD}\right]$

<sup>7</sup> Display interface clock up time for write:

$Tdicuw = \frac{1}{2}T_{HSP\_CLK} \cdot ceil \left[\frac{2 \cdot DISP\#\_IF\_CLK\_UP\_WR}{HSP\_CLK\_PERIOD}\right]$

<sup>8</sup> This parameter is a requirement to the display connected to the IPU

Figure 64 depicts timing of the 5-wire serial interface (Type 1). For this interface, a separate RS line is added. When a burst is transmitted within a single active chip select interval, the RS can be changed at boundaries of words.

Figure 64. 5-Wire Serial Interface (Type 1) Timing Diagram

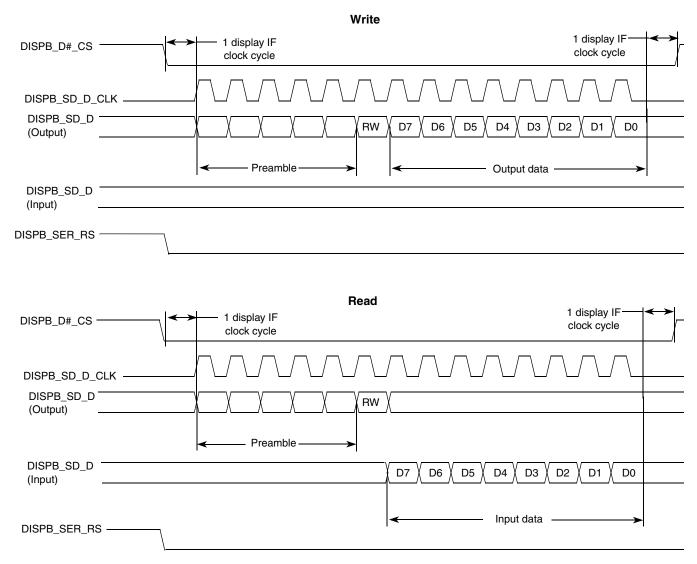

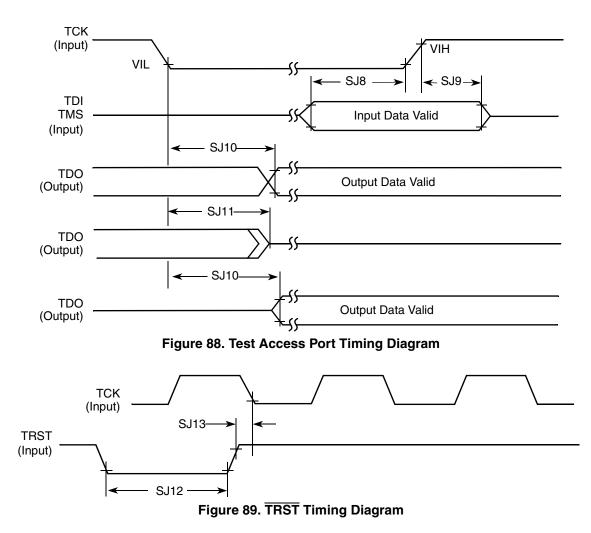

| Table | 76. SJC | Timing | Parameters |

|-------|---------|--------|------------|

|-------|---------|--------|------------|

| ID   | Parameter                                 | All Freq         | Unit |    |  |

|------|-------------------------------------------|------------------|------|----|--|

|      | Falameter                                 | Min.             | Max. |    |  |

| SJ1  | TCK cycle time                            | 100 <sup>1</sup> | _    | ns |  |

| SJ2  | TCK clock pulse width measured at $V_M^2$ | 40               | _    | ns |  |

| SJ3  | TCK rise and fall times                   | —                | 3    | ns |  |

| SJ4  | Boundary scan input data set-up time      | 10               | _    | ns |  |

| SJ5  | Boundary scan input data hold time        | 50               | _    | ns |  |

| SJ6  | TCK low to output data valid              | —                | 50   | ns |  |

| SJ7  | TCK low to output high impedance          | —                | 50   | ns |  |

| SJ8  | TMS, TDI data set-up time                 | 10               | _    | ns |  |

| SJ9  | TMS, TDI data hold time                   | 50               | _    | ns |  |

| SJ10 | TCK low to TDO data valid                 |                  | 44   | ns |  |

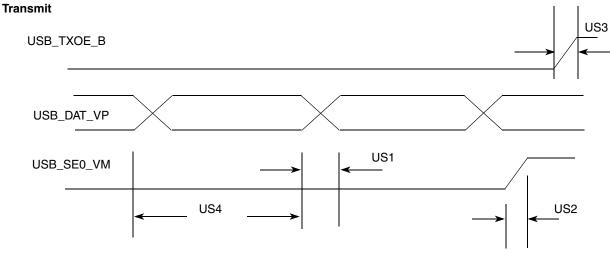

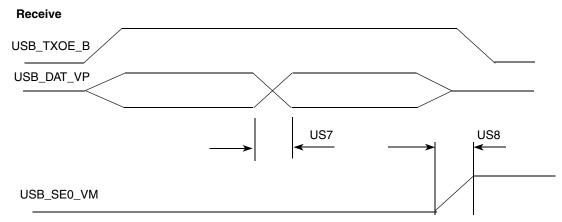

## 4.9.24.1 DAT\_SE0 Bidirectional Mode

Table 86 defines the signals for DAT\_SE0 bidirectional mode. Figure 100 and Figure 101 show the transmit and receive waveforms respectively.

| Name       | Direction | Signal Description                                                             |

|------------|-----------|--------------------------------------------------------------------------------|

| USB_TXOE_B | Out       | Transmit enable, active low                                                    |

| USB_DAT_VP | Out<br>In | Tx data when USB_TXOE_B is low<br>Differential Rx data when USB_TXOE_B is high |

| USB_SE0_VM | Out<br>In | SE0 drive when USB_TXOE_B is low<br>SE0 Rx indicator when USB_TXOE_B is high   |

Figure 100. USB Transmit Waveform in DAT\_SE0 Bidirectional Mode

Figure 101. USB Receive Waveform in DAT\_SE0 Bidirectional Mode

|   | 1                  | 2                  | 3                  | 4                  | 5                       | 6                   | 7                      | 8                         | 9                      | 10                     | 11               | 12                | 13                | 14                | 15                 | 16                | 17                              | 18                                | 19                        | 20                                |   |

|---|--------------------|--------------------|--------------------|--------------------|-------------------------|---------------------|------------------------|---------------------------|------------------------|------------------------|------------------|-------------------|-------------------|-------------------|--------------------|-------------------|---------------------------------|-----------------------------------|---------------------------|-----------------------------------|---|

| Ρ | FEC<br>_MDI<br>O   | FEC<br>_RD<br>ATA0 | FEC<br>_CO<br>L    | FEC<br>_TX_<br>CLK | FEC<br>_TDA<br>TA0      | NVC<br>C_AT<br>A    | NVC<br>C_AT<br>A       | NVC<br>C_AT<br>A          | GND                    | GND                    | MVD<br>D         | PHY<br>2_VS<br>S  | FUS<br>E_V<br>DD  | NVC<br>C_S<br>DIO | TDI                | NVC<br>C_JT<br>AG | USB<br>PHY<br>1_UP<br>LLVD<br>D | USB<br>PHY<br>1_VB<br>US          | USB<br>PHY<br>1_DP        | PHY<br>1_VS<br>SA                 | Ρ |

| R | FEC<br>_MD<br>C    | FEC<br>_RX_<br>CLK | CTS<br>1           | ATA_<br>DA0        | ata_<br>Da2             | TXD<br>1            | VDD<br>3               | VDD<br>3                  | NVC<br>C_C<br>RM       | NVC<br>C_M<br>LB       | NVC<br>C_C<br>SI | VDD<br>4          | PHY<br>2_VD<br>D  | SD1_<br>DATA<br>0 | TDO                | TMS               | тск                             | USB<br>PHY<br>1_VS<br>SA_<br>BIAS | USB<br>PHY<br>1_R<br>REF  | USB<br>PHY<br>1_VD<br>DA_<br>BIAS | R |

| т | FEC<br>_TX_<br>EN  | FEC<br>_RX_<br>DV  | ATA_<br>DMA<br>RQ  | ATA_<br>DATA<br>15 | ATA_<br>BUF<br>F_E<br>N | ATA_<br>RES<br>ET_B | ATA_<br>CS1            | CSPI<br>1_SP<br>I_RD<br>Y | VST<br>BY              | CLK_<br>MOD<br>E1      | GPIO<br>1_0      | COM<br>PAR<br>E   | SD2_<br>DATA<br>1 | CSI_<br>VSY<br>NC | CSI_<br>D11        | TRS<br>TB         | GND                             | OSC<br>24M_<br>VSS                | OSC<br>24M_<br>VDD        | EXTA<br>L24M                      | Т |

| U | RTS<br>1           | RXD<br>1           | ATA_<br>DATA<br>12 | ATA_<br>DATA<br>8  | ATA_<br>DATA<br>3       | ATA_<br>IORD<br>Y   | USB<br>OTG<br>_OC      | CSPI<br>1_SS<br>1         | BOO<br>T_M<br>ODE<br>1 | RES<br>ET_I<br>N_B     | GPIO<br>2_0      | SD2_<br>DATA<br>3 | SD2_<br>CMD       | CSI_<br>D14       | CSI_<br>D8         | SD1_<br>DATA<br>1 | SJC_<br>MOD                     | RTC<br>K                          | OSC<br>_AU<br>DIO_<br>VSS | XTAL<br>24M                       | U |

| V | ATA_<br>DA1        | ATA_<br>INTR<br>Q  | ATA_<br>DATA<br>10 | ATA_<br>DATA<br>6  | ATA_<br>DATA<br>2       | ATA_<br>DMA<br>CK   | ATA_<br>CS0            | EXT_<br>ARM<br>CLK        | CSPI<br>1_MI<br>SO     | CLK<br>O               | GPIO<br>3_0      | CAP<br>TUR<br>E   | SD2_<br>DATA<br>0 | CSI_<br>HSY<br>NC | CSI_<br>D13        | CSI_<br>D10       | SD1_<br>DATA<br>3               | SD1_<br>CLK                       | xtal<br>_au<br>Dio        | OSC<br>_AU<br>DIO_<br>VDD         | V |

| W | ATA_<br>DATA<br>14 | ATA_<br>DATA<br>13 | ATA_<br>DATA<br>9  | ATA_<br>DATA<br>5  | ATA_<br>DATA<br>1       | ATA_<br>DIO<br>W    | USB<br>OTG<br>_PW<br>R | CSPI<br>1_SC<br>LK        | CSPI<br>1_M<br>OSI     | BOO<br>T_M<br>ODE<br>0 | POR<br>_B        | MLB<br>_SIG       | MLB<br>_CLK       | SD2_<br>CLK       | CSI_<br>MCL<br>K   | CSI_<br>D12       | CSI_<br>D9                      | SD1_<br>DATA<br>2                 | DE_<br>B                  | EXTA<br>L_AU<br>DIO               | W |

| Y | GND                | ATA_<br>DATA<br>11 | ATA_<br>DATA<br>7  | ATA_<br>DATA<br>4  | ATA_<br>DATA<br>0       | ATA_<br>DIOR        | TES<br>T_M<br>ODE      | CSPI<br>1_SS<br>0         | POW<br>ER_<br>FAIL     | CLK_<br>MOD<br>E0      | GPIO<br>1_1      | WDO<br>G_R<br>ST  | MLB<br>_DAT       | SD2_<br>DATA<br>2 | CSI_<br>PIXC<br>LK | CSI_<br>D15       | USB<br>PHY<br>2_D<br>M          | USB<br>PHY<br>2_DP                | SD1_<br>CMD               | GND                               | Y |

|   | 1                  | 2                  | 3                  | 4                  | 5                       | 6                   | 7                      | 8                         | 9                      | 10                     | 11               | 12                | 13                | 14                | 15                 | 16                | 17                              | 18                                | 19                        | 20                                |   |

Table 97. Silicon Revision 2.1 Ball Map—17 x 17, 0.8 mm Pitch (continued)

## 6 Product Documentation

All related product documentation for the i.MX35 processor is located at http://www.freescale.com/imx.

## 7 Revision History

Table 98 shows the revision history of this document. Note: There were no revisions of this document between revision 1 and revision 4 or between revision 6 and revision 7.

| Revision<br>Number | Date       | Substantive Change(s)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

|--------------------|------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 10                 | 06/2012    | <ul> <li>In Table 2, "Functional Differences in the i.MX35 Parts," on page 3, added two columns for part numbers MCIMX353 and MCIMX357.</li> <li>Added Table 29, "Clock Input Tolerance," on page 31 in Section 4.9.3, "DPLL Electrical Specifications."</li> <li>Updated Table 39, "DDR2 SDRAM Timing Parameter Table," on page 50 for DDR2-400 values.</li> <li>Updated Table 41, "DDR2 SDRAM Write Cycle Parameters," on page 52 for DDR2-400 values.</li> <li>Added Table 15, "AC Requirements of I/O Pins," on page 24.</li> <li>Updated WE4 parameter in Table 33, "WEIM Bus Timing Parameters," on page 37.</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| 9                  | 08/2010    | <ul> <li>Updated Table 32, "NFC Timing Parameters."</li> <li>Updated Table 33, "WEIM Bus Timing Parameters."</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| 8                  | 04/2010    | Updated Table 14, "I/O Pin DC Electrical Characteristics."                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| 7                  | 12/18/2009 | Updated Table 1, "Ordering Information."                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| 6                  | 10/21/2009 | <ul> <li>Added information for silicon rev. 2.1</li> <li>Updated Table 1, "Ordering Information."</li> <li>Added Table 95, "Silicon Revision 2.1 Signal Ball Map Locations."</li> <li>Added Table 97, "Silicon Revision 2.1 Ball Map—17 x 17, 0.8 mm Pitch."</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| 5                  | 08/06/2009 | <ul> <li>Added a line for T<sub>A</sub> = -40 to 85 °C in Table 14, "I/O Pin DC Electrical Characteristics"</li> <li>Filled in TBDs in Table 14.</li> <li>Revised Figure 15 and Table 33 by removing FCE = 0 and FCE = 1. Added footnote 3 to the table.</li> <li>Added Table 26, "AC Electrical Characteristics of DDR Type IO Pins in SDRAM Mode Max Drive (1.8 V)."</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| 4                  | 04/30/2009 | <ul> <li>Note: There were no revisions of this document between revision 1 and revision 4.</li> <li>In Section 4.3.1, "Powering Up," reverse positions of steps 5 and 6.</li> <li>Updated values in Table 10, "i.MX35 Power Modes."</li> <li>Added Section 4.4, "Reset Timing."</li> <li>In Section 4.8.2, "AC Electrical Characteristics for DDR Pins (DDR2, Mobile DDR, and SDRAM Modes)," removed Slow Slew rate tables, relabeled Table 24, "AC Electrical Characteristics of DDR Type IO Pins in mDDR Mode," and Table 25, "AC Electrical Characteristics of DDR Type IO Pins in mDDR Mode," and Table 25, "AC Electrical Characteristics of DDR Type IO Pins in SDRAM Mode," to exclude mention of slew rate.</li> <li>In Section 4.9.5.2, "Wireless External Interface Module (WEIM)," modified Figure 16, "Synchronous Memory Timing Diagram for Read Access—WSC = 1," through Figure 21, "Muxed A/D Mode Timing Diagram for Synchronous Read Access—WSC = 7, LBA = 1, LBN = 1, LAH = 1, OEA = 7."</li> <li>In Section 4.9.6, "Enhanced Serial Audio Interface (ESAI) Timing Specifications," modified Figure 36, "ESAI Transmitter Timing," and Figure 37, "ESAI Receiver Timing," to remove extraneous signals. Removed a note from Figure 36, "ESAI Transmitter Timing."</li> </ul> |

| 3                  | 03/2009    | In Section 4.3.1, "Powering Up," reverse positions of steps 5 and 6.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| 2                  | 02/2009    | <ul> <li>Added the following parts to Table 1, "Ordering Information": PCIMX357CVM5B,<br/>MCIMX353CVM5B, MCIMX353DVM5B, MCIMX357CVM5B, and MCIMX357DVM5B. Throughout<br/>consumer data sheet: Removed or updated information related to Media Local Bus<br/>interface.Updated Section 4.3.1, "Powering Up."</li> <li>Updated values in Table 10, "i.MX35 Power Modes."</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

#### Table 98. i.MX35 Data Sheet Revision History