# E·XFL

#### Welcome to E-XFL.COM

#### Understanding Embedded - Microprocessors

Embedded microprocessors are specialized computing chips designed to perform specific tasks within an embedded system. Unlike general-purpose microprocessors found in personal computers, embedded microprocessors are tailored for dedicated functions within larger systems, offering optimized performance, efficiency, and reliability. These microprocessors are integral to the operation of countless electronic devices, providing the computational power necessary for controlling processes, handling data, and managing communications.

#### Applications of **Embedded - Microprocessors**

Embedded microprocessors are utilized across a broad spectrum of applications, making them indispensable in

#### Details

| Product Status                  | Active                                                                |

|---------------------------------|-----------------------------------------------------------------------|

| Core Processor                  | ARM1136JF-S                                                           |

| Number of Cores/Bus Width       | 1 Core, 32-Bit                                                        |

| Speed                           | 532MHz                                                                |

| Co-Processors/DSP               | Multimedia; GPU, IPU, VFP                                             |

| RAM Controllers                 | LPDDR, DDR2                                                           |

| Graphics Acceleration           | Yes                                                                   |

| Display & Interface Controllers | Keypad, KPP, LCD                                                      |

| Ethernet                        | 10/100Mbps (1)                                                        |

| SATA                            | -                                                                     |

| USB                             | USB 2.0 + PHY (2)                                                     |

| Voltage - I/O                   | 1.8V, 2.0V, 2.5V, 2.7V, 3.0V, 3.3V                                    |

| Operating Temperature           | -20°C ~ 70°C (TA)                                                     |

| Security Features               | Secure Fusebox, Secure JTAG, Tamper Detection                         |

| Package / Case                  | 400-LFBGA                                                             |

| Supplier Device Package         | 400-LFBGA (17x17)                                                     |

| Purchase URL                    | https://www.e-xfl.com/product-detail/nxp-semiconductors/mcimx353djq5c |

|                                 |                                                                       |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

- PWM

- SPDIF transceiver

- 3 UART (up to 4.0 Mbps each)

# 1.2 Ordering Information

Table 1 provides the ordering information for the i.MX35 processors for consumer and industrial applications.

| Description | Part Number   | Silicon<br>Revision | Package <sup>1</sup> | Speed   | Operating<br>Temperature<br>Range (°C) | Signal Ball<br>Map<br>Locations | Ball Map |

|-------------|---------------|---------------------|----------------------|---------|----------------------------------------|---------------------------------|----------|

| i.MX353     | MCIMX353CVM5B | 2.0                 | 5284                 | 532 MHz | -40 to 85                              | Table 94                        | Table 96 |

| i.MX353     | MCIMX353DVM5B | 2.0                 | 5284                 | 532 MHz | -20 to 70                              | Table 94                        | Table 96 |

| i.MX357     | MCIMX357CVM5B | 2.0                 | 5284                 | 532 MHz | -40 to 85                              | Table 94                        | Table 96 |

| i.MX357     | MCIMX357DVM5B | 2.0                 | 5284                 | 532 MHz | -20 to 70                              | Table 94                        | Table 96 |

| i.MX353     | MCIMX353CJQ5C | 2.1                 | 5284                 | 532MHz  | -40 to 85                              | Table 95                        | Table 97 |

| i.MX353     | MCIMX353DJQ5C | 2.1                 | 5284                 | 532MHz  | -20 to 70                              | Table 95                        | Table 97 |

| i.MX357     | MCIMX357CJQ5C | 2.1                 | 5284                 | 532MHz  | -40 to 85                              | Table 95                        | Table 97 |

| i.MX357     | MCIMX357DJQ5C | 2.1                 | 5284                 | 532MHz  | -20 to 70                              | Table 95                        | Table 97 |

Table 1. Ordering Information

<sup>1</sup> Case 5284 is RoHS-compliant, lead-free, MSL = 3, 1.

The ball map for silicon revision 2.1 is different than the ballmap for silicon revision 2.0. The layout for each revision is not compatible, so it is important that the correct ballmap be used to implement the layout. See Section 5, "Package Information and Pinout."

Table 2 shows the functional differences between the different parts in the i.MX35 family.

| Module      | MCIMX351 | MCIMX353 | MCIMX355 | MCIMX356 | MCIMX357 |

|-------------|----------|----------|----------|----------|----------|

| I2C (3)     | Yes      | Yes      | Yes      | Yes      | Yes      |

| CSPI (2)    | Yes      | Yes      | Yes      | Yes      | Yes      |

| SSI/I2S (2) | Yes      | Yes      | Yes      | Yes      | Yes      |

| ESAI        | Yes      | Yes      | Yes      | Yes      | Yes      |

| SPDIF I/O   | Yes      | Yes      | Yes      | Yes      | Yes      |

| USB HS Host | Yes      | Yes      | Yes      | Yes      | Yes      |

| USB OTG     | Yes      | Yes      | Yes      | Yes      | Yes      |

| FlexCAN (2) | Yes      | Yes      | Yes      | Yes      | Yes      |

| MLB         | Yes      | Yes      | Yes      | Yes      | Yes      |

Table 2. Functional Differences in the i.MX35 Parts

| Block<br>Mnemonic | Block Name                                    | Domain <sup>1</sup> | Subsystem                   | Brief Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

|-------------------|-----------------------------------------------|---------------------|-----------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| ESAI              | Enhanced<br>serial audio<br>interface         | SDMA                | Connectivity peripherals    | The enhanced serial audio interface (ESAI) provides a full-duplex<br>serial port for serial communication with a variety of serial devices,<br>including industry-standard codecs, SPDIF transceivers, and other<br>DSPs. The ESAI consists of independent transmitter and receiver<br>sections, each section with its own clock generator.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| eSDHCv2<br>(3)    | Enhanced<br>secure digital<br>host controller | ARM                 | Connectivity<br>peripherals | The eSDHCv2 consists of four main modules: CE-ATA, MMC, SD<br>and SDIO. CE-ATA is a hard drive interface that is optimized for<br>embedded applications of storage. The MultiMediaCard (MMC) is a<br>universal, low-cost, data storage and communication media to<br>applications such as electronic toys, organizers, PDAs, and smart<br>phones. The secure digital (SD) card is an evolution of MMC and is<br>specifically designed to meet the security, capacity, performance,<br>and environment requirements inherent in emerging audio and<br>video consumer electronic devices. SD cards are categorized into<br>Memory and I/O. A memory card enables a copyright protection<br>mechanism that complies with the SDMI security standard. SDIO<br>cards provide high-speed data I/O (such as wireless LAN via SDIO<br>interface) with low power consumption.<br><b>Note:</b> CE-ATA is not available for the MCIMX351. |

| FEC               | Ethernet                                      | SDMA                | Connectivity peripherals    | The Ethernet media access controller (MAC) is designed to support<br>both 10 and 100 Mbps Ethernet/IEEE 802.3 networks. An external<br>transceiver interface and transceiver function are required to<br>complete the interface to the media                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| GPIO(3)           | General<br>purpose I/O<br>modules             | ARM                 | Pins                        | Used for general purpose input/output to external ICs. Each GPIO module supports 32 bits of I/O.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| GPT               | General<br>purpose timers                     | ARM                 | Timer<br>peripherals        | Each GPT is a 32-bit free-running or set-and-forget mode timer with<br>a programmable prescaler and compare and capture registers. A<br>timer counter value can be captured using an external event and can<br>be configured to trigger a capture event on either the leading or<br>trailing edges of an input pulse. When the timer is configured to<br>operate in set-and-forget mode, it is capable of providing precise<br>interrupts at regular intervals with minimal processor intervention.<br>The counter has output compare logic to provide the status and<br>interrupt at comparison. This timer can be configured to run either<br>on an external clock or on an internal clock.                                                                                                                                                                                                                                  |

| GPU2D             | Graphics<br>processing unit<br>2Dv1           | ARM                 | Multimedia<br>peripherals   | This module accelerates OpenVG and GDI graphics.<br>Note: Not available for the MCIMX351.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

Table 4. Digital and Analog Modules (continued)

| Block<br>Mnemonic   | Block Name                                  | Domain <sup>1</sup> | Subsystem                          | Brief Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

|---------------------|---------------------------------------------|---------------------|------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| l <sup>2</sup> C(3) | I <sup>2</sup> C module                     | ARM                 | ARM1136<br>platform<br>peripherals | Inter-integrated circuit (I <sup>2</sup> C) is an industry-standard, bidirectional serial bus that provides a simple, efficient method of data exchange, minimizing the interconnection between devices. I <sup>2</sup> C is suitable for applications requiring occasional communications over a short distance among many devices. The interface operates at up to 100 kbps with maximum bus loading and timing. The I <sup>2</sup> C system is a true multiple-master bus, with arbitration and collision detection that prevent data corruption if multiple devices attempt to control the bus simultaneously. This feature supports complex applications with multiprocessor control and can be used for rapid testing and alignment of end products through external connections to an assembly-line computer. |

| IIM                 | IC<br>identification<br>module              | ARM                 | Security<br>modules                | The IIM provides the primary user-visible mechanism for interfacing<br>with on-chip fuse elements. Among the uses for the fuses are<br>unique chip identifiers, mask revision numbers, cryptographic keys,<br>and various control signals requiring a fixed value.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| IOMUX               | External<br>signals and pin<br>multiplexing | ARM                 | Pins                               | <ul> <li>Each I/O multiplexer provides a flexible, scalable multiplexing solution with the following features:</li> <li>Up to eight output sources multiplexed per pin</li> <li>Up to four destinations for each input pin</li> <li>Unselected input paths held at constant levels for reduced power consumption</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| IPUv1               | Image<br>processing unit                    | ARM                 | Multimedia<br>peripherals          | <ul> <li>The IPU supports video and graphics processing functions. It also provides the interface for image sensors and displays. The IPU performs the following main functions:</li> <li>Preprocessing of data from the sensor or from the external system memory</li> <li>Postprocessing of data from the external system memory</li> <li>Post-filtering of data from the system memory with support of the MPEG-4 (both deblocking and deringing) and H.264 post-filtering algorithms</li> <li>Displaying video and graphics on a synchronous (dumb or memory-less) display</li> <li>Displaying video and graphics on an asynchronous (smart) display</li> <li>Transferring data between IPU sub-modules and to/from the system memory with flexible pixel reformatting</li> </ul>                                |

| KPP                 | Keypin port                                 | ARM                 | Connectivity peripherals           | Can be used for either keypin matrix scanning or general purpose I/O.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| OSCAUD              | OSC audio<br>reference<br>oscillator        | Analog              | Clock                              | The OSCAUDIO oscillator provides a stable frequency reference for<br>the PLLs. This oscillator is designed to work in conjunction with an<br>external 24.576-MHz crystal.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| OSC24M              | OSC24M<br>24-MHz<br>reference<br>oscillator | Analog              | Clock                              | The signal from the external 24-MHz crystal is the source of the CLK24M signal fed into USB PHY as the reference clock and to the real time clock (RTC).                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

### Table 4. Digital and Analog Modules (continued)

| Parameter                             | Symbol | Test<br>Condition       | Min.<br>Rise/Fall                   | Тур.                                | Max.<br>Rise/Fall | Units | Notes |

|---------------------------------------|--------|-------------------------|-------------------------------------|-------------------------------------|-------------------|-------|-------|

| Duty cycle                            | Fduty  | —                       | 40                                  | —                                   | 60                | %     | _     |

| Output pin slew rate (max. drive)     | tps    | 25 pF<br>40 pF<br>50 pF | 0.84/1.10<br>0.68/0.83<br>0.58/0.72 | 1.14/1.34                           | 1.88/2.06         | V/ns  | 2     |

| Output pin slew rate (high drive)     | tps    | 25 pF<br>40 pF<br>50 pF | 0.69/0.96<br>0.55/0.69<br>0.40/0.59 | 0.92/1.10                           |                   | V/ns  |       |

| Output pin slew rate (standard drive) | tps    | 25 pF<br>40 pF<br>50 pF | 0.37/0.47                           | 0.80/1.00<br>0.62/0.76<br>0.45/0.65 |                   | V/ns  |       |

| Output pin di/dt (max. drive)         | tdit   | 25 pF<br>50 pF          | 46<br>49                            | 124<br>131                          | 310<br>324        | mA/ns | 3     |

| Output pin di/dt (high drive)         | tdit   | 25 pF<br>50 pF          | 33<br>35                            | 89<br>94                            | 290<br>304        | mA/ns |       |

| Output pin di/dt (standard<br>drive)  | tdit   | 25 pF<br>50 pF          | 28<br>29                            | 75<br>79                            | 188<br>198        | mA/ns |       |

# Table 21. AC Electrical Characteristics of GPIO Pins in Fast Slew Rate Mode [NVCC = 2.25 V–2.75 V]

# 4.8.2 AC Electrical Characteristics for DDR Pins (DDR2, Mobile DDR, and SDRAM Modes)

### Table 22. AC Electrical Characteristics of DDR Type IO Pins in DDR2 Mode

| Parameter            | Symbol | Test Condition | Min.<br>Rise/Fall     | Тур.                  | Max.<br>Rise/Fall      | Units |

|----------------------|--------|----------------|-----------------------|-----------------------|------------------------|-------|

| Duty cycle           | Fduty  | —              | 45                    | 50                    | 55                     | %     |

| Clock frequency      | f      | —              | _                     | 133                   | —                      | MHz   |

| Output pin slew rate | tps    | 25 pF<br>50 pF | 0.86/0.98<br>0.46/054 | 1.35/1.5<br>0.72/0.81 | 2.15/2.19<br>1.12/1.16 | V/ns  |

| Output pin di/dt     | tdit   | 25 pF<br>50 pF | 65<br>70              | 157<br>167            | 373<br>396             | mA/ns |

### Table 23. AC Requirements of DDR2 Pins

| Parameter <sup>1</sup>                                      | Symbol  | Min.             | Max.             | Units |

|-------------------------------------------------------------|---------|------------------|------------------|-------|

| AC input logic high                                         | VIH(ac) | NVCC ÷ 2 + 0.25  | NVCC + 0.3       | V     |

| AC input logic low                                          | VIL(ac) | -0.3             | NVCC ÷ 2 – 0.25  | V     |

| AC differential cross point voltage for output <sup>2</sup> | Vox(ac) | NVCC ÷ 2 – 0.125 | NVCC ÷ 2 + 0.125 | V     |

<sup>1</sup> The Jedec SSTL\_18 specification (JESD8-15a) for an SSTL interface for class II operation supersedes any specification in this document.

<sup>2</sup> The typical value of Vox(ac) is expected to be about  $0.5 \times$  NVCC and Vox(ac) is expected to track variation in NVCC. Vox(ac) indicates the voltage at which the differential output signal must cross. Cload = 25 pF.

| Parameter                             | Symbol | Test Condition | Min.<br>Rise/Fall      | Тур.                   | Max.<br>Rise/Fall      | Units |

|---------------------------------------|--------|----------------|------------------------|------------------------|------------------------|-------|

| Duty cycle                            | Fduty  | —              | 45                     | 50                     | 55                     | %     |

| Clock frequency                       | f      | —              | _                      | 133                    | —                      | MHz   |

| Output pin slew rate (max. drive)     | tps    | 25 pF<br>50 pF | 0.80/0.92<br>0.43/0.50 | 1.35/1.50<br>0.72/0.81 | 2.23/2.27<br>1.66/1.68 | V/ns  |

| Output pin slew rate (high drive)     | tps    | 25 pF<br>50 pF | 0.37/0.43<br>0.19/0.23 | 0.62/0.70<br>0.33/0.37 | 1.03/1.05<br>0.75/0.77 | V/ns  |

| Output pin slew rate (standard drive) | tps    | 25 pF<br>50 pF | 0.18/0.22<br>0.10/0.12 | 0.31/0.35<br>0.16/0.18 | 0.51/0.53<br>0.38/0.39 | V/ns  |

| Output pin di/dt (max. drive)         | tdit   | 25 pF<br>50 pF | 64<br>69               | 171<br>183             | 407<br>432             | mA/ns |

| Output pin di/dt (high drive)         | tdit   | 25 pF<br>50 pF | 37<br>39               | 100<br>106             | 232<br>246             | mA/ns |

| Output pin di/dt (standard drive)     | tdit   | 25 pF<br>50 pF | 18<br>20               | 50<br>52               | 116<br>123             | mA/ns |

Table 24. AC Electrical Characteristics of DDR Type IO Pins in mDDR Mode

### Table 25. AC Electrical Characteristics of DDR Type IO Pins in SDRAM Mode

| Parameter                             | Symbol | Test Condition | Min.<br>Rise/Fall      | Min. Clock<br>Frequency | Max.<br>Rise/Fall      | Units |

|---------------------------------------|--------|----------------|------------------------|-------------------------|------------------------|-------|

| Clock frequency                       | f      | —              | _                      | 125                     | _                      | MHz   |

| Output pin slew rate (max. drive)     | tps    | 25 pF<br>50 pF | 1.11/1.20<br>0.97/0.65 | 1.74/1.75<br>0.92/0.94  | 2.42/2.46<br>1.39/1.30 | V/ns  |

| Output pin slew rate (high drive)     | tps    | 25 pF<br>50 pF | 0.76/0.80<br>0.40/0.43 | 1.16/1.19<br>0.61/0.63  | 1.76/1.66<br>0.93/0.87 | V/ns  |

| Output pin slew rate (standard drive) | tps    | 25 pF<br>50 pF | 0.38/0.41<br>0.20/0.22 | 0.59/0.60<br>0.31/0.32  | 0.89/0.82<br>0.47/0.43 | V/ns  |

| Output pin di/dt (max. drive)         | tdit   | 25 pF<br>50 pF | 89<br>94               | 198<br>209              | 398<br>421             | mA/ns |

| Output pin di/dt (high drive)         | tdit   | 25 pF<br>50 pF | 59<br>62               | 132<br>139              | 265<br>279             | mA/ns |

| Output pin di/dt (standard drive)     | tdit   | 25 pF<br>50 pF | 29<br>31               | 65<br>69                | 132<br>139             | mA/ns |

# 4.9.4 Embedded Trace Macrocell (ETM) Electrical Specifications

ETM is an ARM protocol. The timing specifications in this section are given as a guide for a test point access (TPA) that supports TRACECLK frequencies up to 133 MHz.

Figure 9 depicts the TRACECLK timings of ETM, and Table 30 lists the timing parameters.

### Figure 9. ETM TRACECLK Timing Diagram

### Table 30. ETM TRACECLK Timing Parameters

| ID               | Parameter                | Min.                | Max. | Unit |

|------------------|--------------------------|---------------------|------|------|

| T <sub>cyc</sub> | Clock period             | Frequency dependent | _    | ns   |

| T <sub>wl</sub>  | Low pulse width          | 2                   | _    | ns   |

| T <sub>wh</sub>  | High pulse width         | 2                   | _    | ns   |

| T <sub>r</sub>   | Clock and data rise time | —                   | 3    | ns   |

| T <sub>f</sub>   | Clock and data fall time | _                   | 3    | ns   |

Figure 10 depicts the setup and hold requirements of the trace data pins with respect to TRACECLK, and Table 31 lists the timing parameters.

### Figure 10. Trace Data Timing Diagram

### Table 31. ETM Trace Data Timing Parameters

| ID             | Parameter  | Min. | Max. | Unit |

|----------------|------------|------|------|------|

| T <sub>s</sub> | Data setup | 2    | —    | ns   |

| T <sub>h</sub> | Data hold  | 1    | —    | ns   |

## 4.9.4.1 Half-Rate Clocking Mode

When half-rate clocking is used, the trace data signals are sampled by the TPA on both the rising and falling edges of TRACECLK, where TRACECLK is half the frequency of the clock shown in Figure 10. The same  $T_s$  and  $T_h$  parameters from Table 31 still apply with respect to the falling edge of the TRACECLK signal.

| ID   | PARAMETER                       | Symbol           | DDR2-4 | 00  | Unit |

|------|---------------------------------|------------------|--------|-----|------|

|      |                                 |                  | Min    | Max | Omt  |

| DDR5 | CS, RAS, CAS, CKE, WE hold time | tıH1             | 1.25   | _   | ns   |

| DDR6 | Address output setup time       | tis <sup>1</sup> | 1.5    | _   | ns   |

| DDR7 | Address output hold time        | tıн <sup>1</sup> | 1.5    | _   | ns   |

### Table 39. DDR2 SDRAM Timing Parameter Table

### NOTE

These values are for command/address slew rate of 1 V/ns and SDCLK, SDCLK\_B differential slew rate of 2 V/ns. For different values, use the derating table.

Table 40. Derating Values for DDR2-400, DDR2-533

# 4.9.6 Enhanced Serial Audio Interface (ESAI) Timing Specifications

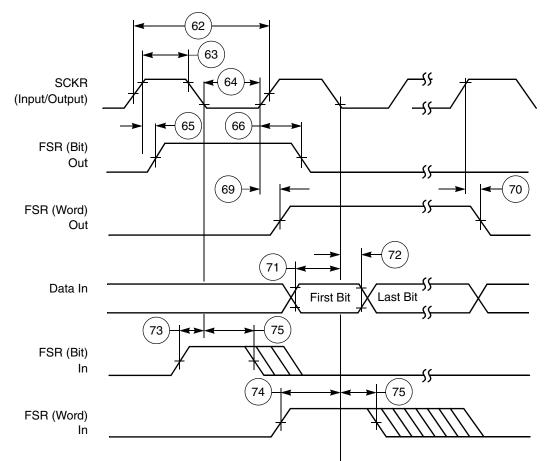

The ESAI consists of independent transmitter and receiver sections, each section with its own clock generator. Table 46 shows the interface timing values. The number field in the table refers to timing signals found in Figure 36 and Figure 37.

| No. | Characteristics <sup>1,2</sup>                                        | Symbol             | Expression <sup>2</sup>          | Min.         | Max.         | Condition <sup>3</sup> | Unit |

|-----|-----------------------------------------------------------------------|--------------------|----------------------------------|--------------|--------------|------------------------|------|

| 62  | Clock cycle <sup>4</sup>                                              | t <sub>SSICC</sub> | $4 \times T_c$<br>$4 \times T_c$ | 30.0<br>30.0 | _            | i ck<br>i ck           | ns   |

| 63  | Clock high period<br>• For internal clock                             | _                  | $2 \times T_{C} - 9.0$           | 6            | _            | _                      | ns   |

|     | For external clock                                                    | —                  | $2 \times T_{C}$                 | 15           | _            | —                      |      |

| 64  | Clock low period<br>• For internal clock                              | _                  | $2 \times T_{C} - 9.0$           | 6            |              | _                      | ns   |

|     | For external clock                                                    | _                  | $2 \times T_{C}$                 | 15           | _            | —                      |      |

| 65  | SCKR rising edge to FSR out (bl) high                                 |                    | _                                |              | 17.0<br>7.0  | x ck<br>i ck a         | ns   |

| 66  | SCKR rising edge to FSR out (bl) low                                  | -                  |                                  |              | 17.0<br>7.0  | x ck<br>i ck a         | ns   |

| 67  | SCKR rising edge to FSR out (wr) high <sup>5</sup>                    | _                  | _                                |              | 19.0<br>9.0  | x ck<br>i ck a         | ns   |

| 68  | SCKR rising edge to FSR out (wr) low <sup>5</sup>                     |                    | —                                |              | 19.0<br>9.0  | x ck<br>i ck a         | ns   |

| 69  | SCKR rising edge to FSR out (wl) high                                 |                    |                                  |              | 16.0<br>6.0  | x ck<br>i ck a         | ns   |

| 70  | SCKR rising edge to FSR out (wl) low                                  |                    | —                                |              | 17.0<br>7.0  | x ck<br>i ck a         | ns   |

| 71  | Data in setup time before SCKR (SCK in synchronous mode) falling edge | —                  | —                                | 12.0<br>19.0 | _            | x ck<br>i ck           | ns   |

| 72  | Data in hold time after SCKR falling edge                             |                    | —                                | 3.5<br>9.0   | _            | x ck<br>i ck           | ns   |

| 73  | FSR input (bl, wr) high before SCKR falling edge <sup>5</sup>         |                    | —                                | 2.0<br>12.0  | _            | x ck<br>i ck a         | ns   |

| 74  | FSR input (wl) high before SCKR falling edge                          |                    | —                                | 2.0<br>12.0  | _            | x ck<br>i ck a         | ns   |

| 75  | FSR input hold time after SCKR falling edge                           |                    | —                                | 2.5<br>8.5   | _            | x ck<br>i ck a         | ns   |

| 78  | SCKT rising edge to FST out (bl) high                                 |                    | —                                |              | 18.0<br>8.0  | x ck<br>i ck           | ns   |

| 79  | SCKT rising edge to FST out (bl) low                                  |                    |                                  |              | 20.0<br>10.0 | x ck<br>i ck           | ns   |

### Table 46. Enhanced Serial Audio Interface Timing

Figure 37. ESAI Receiver Timing

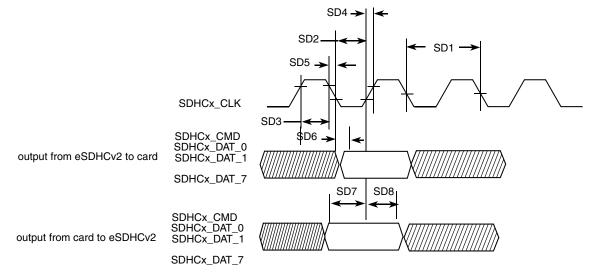

# 4.9.7 eSDHCv2 AC Electrical Specifications

Figure 38 depicts the timing of eSDHCv2, and Table 47 lists the eSDHCv2 timing characteristics. The following definitions apply to values and signals described in Table 47:

- LS: low-speed mode. Low-speed card can tolerate a clock up to 400 kHz.

- FS: full-speed mode. For a full-speed MMC card, the card clock can reach 20 MHz; a full-speed SD/SDIO card can reach 25 MHz.

- HS: high-speed mode. For a high-speed MMC card, the card clock can reach 52 MHz; SD/SDIO can reach 50 MHz.

### Figure 38. eSDHCv2 Timing

### Table 47. eSDHCv2 Interface Timing Specification

| ID   | Parameter                                         | Symbols                      | Min. | Max.  | Unit |

|------|---------------------------------------------------|------------------------------|------|-------|------|

| Card | Input Clock                                       | 1                            | 1    | 1     | 1    |

| SD1  | Clock frequency (Low Speed)                       | f <sub>PP</sub> <sup>1</sup> | 0    | 400   | kHz  |

|      | Clock frequency (SD/SDIO Full Speed/High Speed)   | f <sub>PP</sub> <sup>2</sup> | 0    | 25/50 | MHz  |

|      | Clock frequency (MMC Full Speed/High Speed)       | f <sub>PP</sub> <sup>3</sup> | 0    | 20/52 | MHz  |

|      | Clock frequency (Identification Mode)             | f <sub>OD</sub>              | 100  | 400   | kHz  |

| SD2  | Clock Low time                                    | t <sub>WL</sub>              | 7    | —     | ns   |

| SD3  | Clock high time                                   | t <sub>WH</sub>              | 7    | —     | ns   |

| SD4  | Clock rise time                                   | t <sub>TLH</sub>             | —    | 3     | ns   |

| SD5  | Clock fall time                                   | t <sub>THL</sub>             | —    | 3     | ns   |

| eSDł | IC Output/Card Inputs CMD, DAT (Reference to CLK) |                              |      |       |      |

| SD6  | eSDHC output delay                                | t <sub>OD</sub>              | -3   | 3     | ns   |

| eSDł | IC Input/Card Outputs CMD, DAT (Reference to CLK) |                              | •    |       | •    |

| SD7  | eSDHC input setup time                            | t <sub>ISU</sub>             | 5    |       | ns   |

| SD8  | eSDHC input hold time                             | t <sub>IH</sub> 4            | 2.5  | —     | ns   |

|      |                                                   |                              |      | •     |      |

<sup>1</sup> In low-speed mode, the card clock must be lower than 400 kHz, voltage ranges from 2.7 to 3.6 V.

<sup>2</sup> In normal-speed mode for the SD/SDIO card, clock frequency can be any value between 0–25 MHz. In high-speed mode, clock frequency can be any value between 0–50 MHz.

<sup>3</sup> In normal-speed mode for MMC card, clock frequency can be any value between 0 and 20 MHz. In high-speed mode, clock frequency can be any value between 0–52 MHz.

<sup>4</sup> To satisfy hold timing, the delay difference between clock input and cmd/data input must not exceed 2 ns.

# 4.9.13.3 Synchronous Interface to Dual-Port Smart Displays

Functionality and electrical characteristics of the synchronous interface to dual-port smart displays are identical to parameters of the synchronous interface. See Section 4.9.13.1.5, "Interface to Active Matrix TFT LCD Panels, Electrical Characteristics."

## 4.9.13.3.6 Interface to a TV Encoder—Functional Description

The interface has an 8-bit data bus, transferring a single 8-bit value (Y/U/V) in each cycle. The bits D7–D0 of the value are mapped to bits LD17–LD10 of the data bus, respectively. Figure 52 depicts the interface timing.

- The frequency of the clock DISPB\_D3\_CLK is 27 MHz.

- The DISPB\_D3\_HSYNC, DISPB\_D3\_VSYNC and DISPB\_D3\_DRDY signals are active low.

- The transition to the next row is marked by the negative edge of the DISPB\_D3\_HSYNC signal. It remains low for a single clock cycle.

- The transition to the next field/frame is marked by the negative edge of the DISPB\_D3\_VSYNC signal. It remains low for at least one clock cycle.

- At a transition to an odd field (of the next frame), the negative edges of DISPB\_D3\_VSYNC and DISPB\_D3\_HSYNC coincide.

- At a transition to an even field (of the same frame), they do not coincide.

- The active intervals—during which data is transferred—are marked by the DISPB\_D3\_HSYNC signal being high.

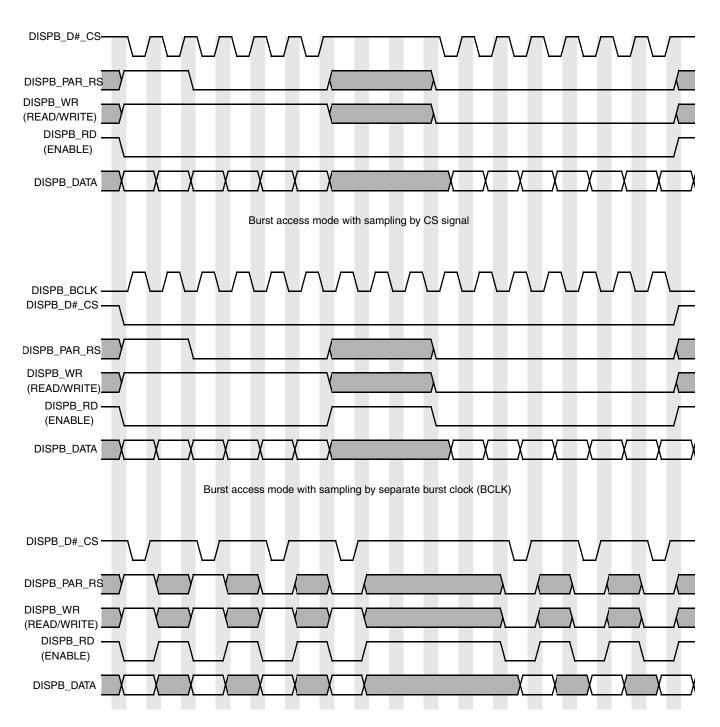

Single access mode (all control signals are not active for one display interface clock after each display access)

### Figure 55. Asynchronous Parallel System 68k Interface (Type 1) Burst Mode Timing Diagram

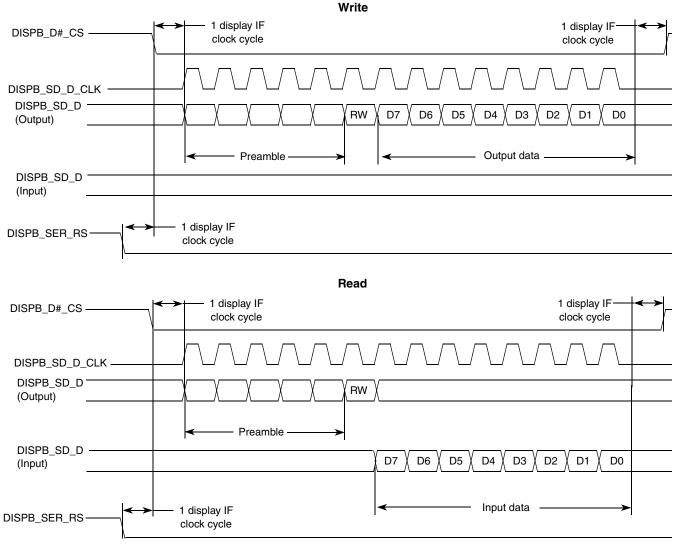

Figure 65 depicts timing of the 5-wire serial interface (Type 2). For this interface, a separate RS line is added. When a burst is transmitted within a single active chip select interval, the RS can be changed at boundaries of words.

Figure 65. 5-Wire Serial Interface (Type 2) Timing Diagram

### 4.9.13.5.10 Serial Interfaces, Electrical Characteristics

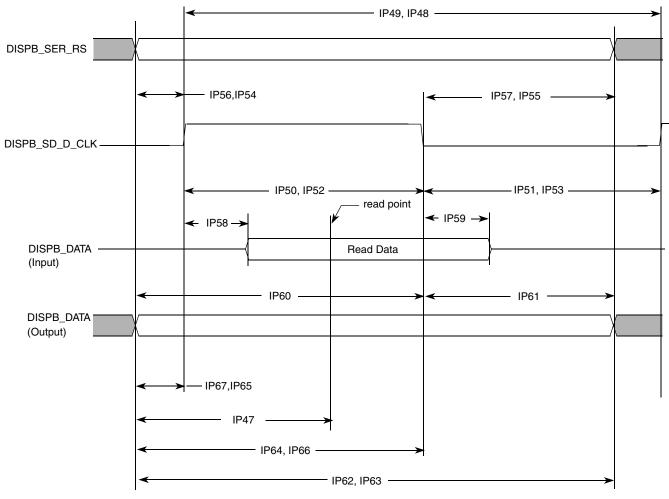

Figure 66 depicts timing of the serial interface. Table 59 lists the timing parameters at display access level.

Figure 66. Asynchronous Serial Interface Timing Diagram

| Table 50 Act  |            | Covial | Interfees | T:     | Devenetere  | A       |       |

|---------------|------------|--------|-----------|--------|-------------|---------|-------|

| Table 59. Asy | ynchronous | Serial | Interface | IIming | Parameters- | -Access | Levei |

| ID   | Parameter                    | Symbol | Min.                              | Typ. <sup>1</sup>                            | Max.                              | Units |

|------|------------------------------|--------|-----------------------------------|----------------------------------------------|-----------------------------------|-------|

| IP48 | Read system cycle time       | Tcycr  | Tdicpr – 1.5                      | Tdicpr <sup>2</sup>                          | Tdicpr + 1.5                      | ns    |

| IP49 | Write system cycle time      | Tcycw  | Tdicpw – 1.5                      | Tdicpw <sup>3</sup>                          | Tdicpw + 1.5                      | ns    |

| IP50 | Read clock low pulse width   | Trl    | Tdicdr – Tdicur – 1.5             | Tdicdr <sup>4</sup> – Tdicur <sup>5</sup>    | Tdicdr – Tdicur + 1.5             | ns    |

| IP51 | Read clock high pulse width  | Trh    | Tdicpr – Tdicdr + Tdicur<br>– 1.5 | Tdicpr – Tdicdr +<br>Tdicur                  | Tdicpr – Tdicdr + Tdicur<br>+ 1.5 | ns    |

| IP52 | Write clock low pulse width  | Twl    | Tdicdw – Tdicuw – 1.5             | Tdicdw <sup>6</sup> –<br>Tdicuw <sup>7</sup> | Tdicdw – Tdicuw + 1.5             | ns    |

| IP53 | Write clock high pulse width | Twh    | Tdicpw – Tdicdw +<br>Tdicuw – 1.5 | Tdicpw – Tdicdw<br>+ Tdicuw                  | Tdicpw – Tdicdw +<br>Tdicuw + 1.5 | ns    |

| IP54 | Controls setup time for read | Tdcsr  | Tdicur – 1.5                      | Tdicur                                       | _                                 | ns    |

| ID   | Parameter                                | Symbol | Min.                          | Typ. <sup>1</sup> | Max.                                                     | Units |

|------|------------------------------------------|--------|-------------------------------|-------------------|----------------------------------------------------------|-------|

| IP55 | Controls hold time for read              | Tdchr  | Tdicpr – Tdicdr – 1.5         | Tdicpr – Tdicdr   | —                                                        | ns    |

| IP56 | Controls setup time for write            | Tdcsw  | Tdicuw – 1.5                  | Tdicuw            | —                                                        | ns    |

| IP57 | Controls hold time for write             | Tdchw  | Tdicpw – Tdicdw – 1.5         | Tdicpw – Tdicdw   | —                                                        | ns    |

| IP58 | Slave device data delay <sup>8</sup>     | Tracc  | 0                             | _                 | Tdrp <sup>9</sup> – Tlbd <sup>10</sup> – Tdicur<br>– 1.5 | ns    |

| IP59 | Slave device data hold time <sup>8</sup> | Troh   | Tdrp – Tlbd – Tdicdr<br>+ 1.5 | _                 | Tdicpr – Tdicdr – 1.5                                    | ns    |

| IP60 | Write data setup time                    | Tds    | Tdicdw – 1.5                  | Tdicdw            | —                                                        | ns    |

| IP61 | Write data hold time                     | Tdh    | Tdicpw – Tdicdw – 1.5         | Tdicpw – Tdicdw   | —                                                        | ns    |

| IP62 | Read period <sup>2</sup>                 | Tdicpr | Tdicpr – 1.5                  | Tdicpr            | Tdicpr + 1.5                                             | ns    |

| IP63 | Write period <sup>3</sup>                | Tdicpw | Tdicpw – 1.5                  | Tdicpw            | Tdicpw + 1.5                                             | ns    |

| IP64 | Read down time <sup>4</sup>              | Tdicdr | Tdicdr – 1.5                  | Tdicdr            | Tdicdr + 1.5                                             | ns    |

| IP65 | Read up time <sup>5</sup>                | Tdicur | Tdicur – 1.5                  | Tdicur            | Tdicur + 1.5                                             | ns    |

| IP66 | Write down time <sup>6</sup>             | Tdicdw | Tdicdw – 1.5                  | Tdicdw            | Tdicdw + 1.5                                             | ns    |

| IP67 | Write up time <sup>7</sup>               | Tdicuw | Tdicuw – 1.5                  | Tdicuw            | Tdicuw + 1.5                                             | ns    |

| IP68 | Read time point <sup>9</sup>             | Tdrp   | Tdrp – 1.5                    | Tdrp              | Tdrp + 1.5                                               | ns    |

Table 59. Asynchronous Serial Interface Timing Parameters—Access Level (continued)

<sup>1</sup> The exact conditions have not been finalized, but will likely match the current customer requirement for their specific display. These conditions may be device specific.

<sup>2</sup> Display interface clock period value for read:

$Tdicpr = T_{HSP\_CLK} \cdot ceil \left[\frac{DISP\#\_IF\_CLK\_PER\_RD}{HSP\_CLK\_PERIOD}\right]$

<sup>3</sup> Display interface clock period value for write:

$Tdicpw = T_{HSP\_CLK} \cdot ceil \left[ \frac{DISP\#\_IF\_CLK\_PER\_WR}{HSP\_CLK\_PERIOD} \right]$

<sup>4</sup> Display interface clock down time for read:

$Tdicdr = \frac{1}{2}T_{HSP\_CLK} \cdot ceil \left[\frac{2 \cdot DISP\#\_IF\_CLK\_DOWN\_RD}{HSP\_CLK\_PERIOD}\right]$

<sup>5</sup> Display interface clock up time for read:

$Tdicur = \frac{1}{2}T_{HSP\_CLK} \cdot ceil \left[\frac{2 \cdot DISP\#\_IF\_CLK\_UP\_RD}{HSP\_CLK\_PERIOD}\right]$

<sup>6</sup> Display interface clock down time for write:

$Tdicdw = \frac{1}{2}T_{HSP\_CLK} \cdot ceil \left[\frac{2 \cdot DISP\#\_IF\_CLK\_DOWN\_WR}{HSP\_CLK\_PERIOD}\right]$

<sup>7</sup> Display interface clock up time for write:

$Tdicuw = \frac{1}{2}T_{HSP\_CLK} \cdot ceil \left[\frac{2 \cdot DISP\#\_IF\_CLK\_UP\_WR}{HSP\_CLK\_PERIOD}\right]$

<sup>8</sup> This parameter is a requirement to the display connected to the IPU.

| Signal    | Parameter         | Symbol | Stan | dards | Unit |  |

|-----------|-------------------|--------|------|-------|------|--|

| Signal    | Falameter         | Symbol | Min. | Max.  | onne |  |

| MSHC_DATA | Setup time        | tDsu   | 5    | —     | ns   |  |

|           | Hold time         | tDh    | 5    | —     | ns   |  |

|           | Output delay time | tDd    | —    | 15    | ns   |  |

Table 60. Serial Interface Timing Parameters<sup>1</sup> (continued)

<sup>1</sup> Timing is guaranteed for NVCC from 2.7 V through 3.1 V and up to a maximum overdrive NVCC of 3.3 V. See NVCC restrictions described in Table 61.

| Signal    | Parameter         | Symbol  | Stand | ards | Unit |

|-----------|-------------------|---------|-------|------|------|

| Signal    | Parameter Symbol  |         | Min.  | Max. | Unit |

| MSHC_SCLK | Cycle             | tSCLKc  | 25    | _    | ns   |

|           | H pulse length    | tSCLKwh | 5     | _    | ns   |

|           | L pulse length    | tSCLKwl | 5     |      | ns   |

|           | Rise time         | tSCLKr  | —     | 10   | ns   |

|           | Fall time         | tSCLKf  | —     | 10   | ns   |

| MSHC_BS   | Setup time        | tBSsu   | 8     |      | ns   |

|           | Hold time         | tBSh    | 1     |      | ns   |

| MSHC_DATA | Setup time        | tDsu    | 8     | _    | ns   |

|           | Hold time         | tDh     | 1     | _    | ns   |

|           | Output delay time | tDd     | —     | 15   | ns   |

### Table 61. Parallel Interface Timing Parameters<sup>1</sup>

<sup>1</sup> Timing is guaranteed for NVCC from 2.7 V through 3.1 V and up to a maximum overdrive NVCC of 3.3 V. See the NVCC restrictions described in Table 8.

# 4.9.15 MediaLB Controller Electrical Specifications

This section describes the electrical information of the MediaLB Controller module.

Table 62. MLB 256/512 Fs Timing Parameters

| Parameter                               | Symbol            | Min    | Тур              | Max               | Units | Comment                                                                                                                                                                           |

|-----------------------------------------|-------------------|--------|------------------|-------------------|-------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| MLBCLK operating frequency <sup>1</sup> | f <sub>mck</sub>  | 11.264 | 12.288<br>24.576 | 24.6272<br>25.600 | MHz   | Min: $256 \times$ Fs at 44.0 kHz<br>Typ: $256 \times$ Fs at 48.0 kHz<br>Typ: $512 \times$ Fs at 48.0 kHz<br>Max: $512 \times$ Fs at 48.1 kHz<br>Max: $512 \times$ Fs PLL unlocked |

| MLBCLK rise time                        | t <sub>mckr</sub> | _      | —                | 3                 | ns    | V <sub>IL</sub> TO V <sub>IH</sub>                                                                                                                                                |

| Parameter                                           | Symbol             | Min        | Тур          | Мах               | Units | Comment           |

|-----------------------------------------------------|--------------------|------------|--------------|-------------------|-------|-------------------|

| MLBCLK high time                                    | t <sub>mckh</sub>  | 9.7<br>9.3 | 10.6<br>10.2 |                   | ns    | PLL unlocked      |

| MLBCLK pulse width variation                        | t <sub>mpwv</sub>  |            | —            | 0.7               | ns pp | Note <sup>2</sup> |

| MLBSIG/MLBDAT input valid<br>to MLBCLK falling      | t <sub>dsmcf</sub> | 1          | —            | —                 | ns    | _                 |

| MLBSIG/MLBDAT input hold<br>from MLBCLK low         | t <sub>dhmcf</sub> | 0          | —            | —                 | ns    | _                 |

| MLBSIG/MLBDAT output high impedance from MLBCLK low | t <sub>mcfdz</sub> | 0          | _            | t <sub>mckl</sub> | ns    | _                 |

| Bus Hold Time                                       | t <sub>mdzh</sub>  | 2          | —            | _                 | ns    | Note <sup>3</sup> |

Table 63. MLB Device 1024Fs Timing Parameters (continued)

<sup>1</sup> The MLB Controller can shut off MLBCLK to place MediaLB in a low-power state.

<sup>2</sup> Pulse width variation is measured at 1.25 V by triggering on one edge of MLBCLK and measuring the spread on the other edge, measured in ns peak-to-peak (pp)

<sup>3</sup> The board must be designed to insure that the high-impedance bus does not leave the logic state of the final driven bit for this time period. Therefore, coupling must be minimized while meeting the maximum capacitive load listed.

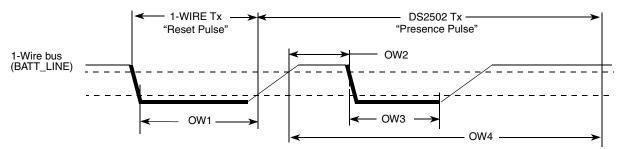

# 4.9.16 1-Wire Timing Specifications

Figure 70 depicts the RPP timing, and Table 64 lists the RPP timing parameters.

Figure 70. Reset and Presence Pulses (RPP) Timing Diagram

| ID  | Parameters           | Symbol            | Min. | Тур. | Max. | Units |

|-----|----------------------|-------------------|------|------|------|-------|

| OW1 | Reset time low       | t <sub>RSTL</sub> | 480  | 511  | _    | μs    |

| OW2 | Presence detect high | t <sub>PDH</sub>  | 15   |      | 60   | μs    |

| OW3 | Presence detect low  | t <sub>PDL</sub>  | 60   |      | 240  | μs    |

| OW4 | Reset time high      | t <sub>RSTH</sub> | 480  | 512  | _    | μs    |

### Figure 81. UDMA-In Device Terminates Transfer Timing Diagram

| ATA<br>Parameter | Parameters<br>from<br>Figure 79,<br>Figure 80,<br>Figure 81 | Description                                                                                          | Controlling Variable                         |

|------------------|-------------------------------------------------------------|------------------------------------------------------------------------------------------------------|----------------------------------------------|

| tack             | tack                                                        | tack (min.) = (time_ack × T) – (tskew1 + tskew2)                                                     | time_ack                                     |

| tenv             | tenv                                                        | tenv (min.) = (time_env × T) – (tskew1 + tskew2)<br>tenv (max.) = (time_env × T) + (tskew1 + tskew2) | time_env                                     |

| tds              | tds1                                                        | $tds - (tskew3) - ti_ds > 0$                                                                         | tskew3, ti_ds, ti_dh<br>should be low enough |

| tdh              | tdh1                                                        | $tdh - (tskew3) - ti_dh > 0$                                                                         |                                              |

| tcyc             | tc1                                                         | (tcyc – tskew > T                                                                                    | T big enough                                 |

| trp              | trp                                                         | trp (min.) = time_rp × T – (tskew1 + tskew2 + tskew6)                                                | time_rp                                      |

| _                | tx1 <sup>1</sup>                                            | $(time\_rp \times T) - (tco + tsu + 3T + 2 \times tbuf + 2 \times tcable2) > trfs (drive)$           | time_rp                                      |

| tmli             | tmli1                                                       | tmli1 (min.) = (time_mlix + 0.4) × T                                                                 | time_mlix                                    |

| tzah             | tzah                                                        | tzah (min.) = (time_zah + 0.4) $\times$ T                                                            | time_zah                                     |

| tdzfs            | tdzfs                                                       | $tdzfs = (time_dzfs \times T) - (tskew1 + tskew2)$                                                   | time_dzfs                                    |

| tcvh             | tcvh                                                        | $tcvh = (time_cvh \times T) - (tskew1 + tskew2)$                                                     | time_cvh                                     |

| _                | ton<br>toff                                                 | $ton = time_on \times T - tskew1$<br>toff = time_off $\times T - tskew1$                             | _                                            |

### Table 72. UDMA-In Burst Timing Parameters

<sup>1</sup> There is a special timing requirement in the ATA host that requires the internal DIOW to go high three clocks after the last active edge on the DSTROBE signal. The equation given on this line tries to capture this constraint.

2. Make ton and toff large enough to avoid bus contention.

| Signal ID   | Ball Location |

|-------------|---------------|

| CTS2        | G5            |

| D0          | A2            |

| D1          | D4            |

| D10         | D2            |

| D11         | E6            |

| D12         | E3            |

| D13         | F5            |

| D14         | D1            |

| D15         | E2            |

| D2          | B2            |

| D3          | E5            |

| D3_CLS      | L17           |

| D3_DRDY     | L20           |

| D3_FPSHIFT  | L15           |

| D3_HSYNC    | L18           |

| D3_REV      | M17           |

| D3_SPL      | M18           |

| D3_VSYNC    | M19           |

| D4          | C3            |

| D5          | B1            |

| D6          | D3            |

| D7          | C2            |

| D8          | C1            |

| D9          | E4            |

| DE_B        | W19           |

| DQM0        | B19           |

| SDCKE1      | D17           |

| DQM2        | D16           |

| DQM3        | C18           |

| EB0         | F18           |

| EB1         | F16           |

| ECB         | D19           |

| EXT_ARMCLK  | V8            |

| EXTAL_AUDIO | W20           |

| EXTAL24M    | T20           |

| FEC_COL     | P3            |

| FEC_CRS     | N5            |

| FEC_MDC     | R1            |

| FEC_MDIO    | P1            |

| FEC_RDATA0  | P2            |

| FEC_RDATA1  | N2            |

| FEC_RDATA2  | M3            |

| FEC_RDATA3  | N1            |

| FEC_RX_CLK  | R2            |

| FEC_RX_DV   | T2            |

| FEC_RX_ERR  | N3            |

|             |               |

| Signal IDBall LocationFEC_TDATA0P5FEC_TDATA1M4FEC_TDATA2M5FEC_TDATA3L6FEC_TX_CLKP4FEC_TX_ENT1FEC_TX_ERN4FSRK5FSTJ1FUSE_VDDP13FUSE_VSSM11 |  |

|------------------------------------------------------------------------------------------------------------------------------------------|--|

| FEC_TDATA1M4FEC_TDATA2M5FEC_TDATA3L6FEC_TX_CLKP4FEC_TX_ENT1FEC_TX_ERRN4FSRK5FSTJ1FUSE_VDDP13                                             |  |

| FEC_TDATA2M5FEC_TDATA3L6FEC_TX_CLKP4FEC_TX_ENT1FEC_TX_ERRN4FSRK5FSTJ1FUSE_VDDP13                                                         |  |

| FEC_TDATA3L6FEC_TX_CLKP4FEC_TX_ENT1FEC_TX_ERRN4FSRK5FSTJ1FUSE_VDDP13                                                                     |  |

| FEC_TX_CLKP4FEC_TX_ENT1FEC_TX_ERRN4FSRK5FSTJ1FUSE_VDDP13                                                                                 |  |

| FEC_TX_ENT1FEC_TX_ERRN4FSRK5FSTJ1FUSE_VDDP13                                                                                             |  |

| FEC_TX_ERRN4FSRK5FSTJ1FUSE_VDDP13                                                                                                        |  |

| FSR K5<br>FST J1<br>FUSE_VDD P13                                                                                                         |  |

| FUSE_VDD P13                                                                                                                             |  |

| FUSE_VDD P13                                                                                                                             |  |

| FUSE VSS M11                                                                                                                             |  |

|                                                                                                                                          |  |

| GPIO1_0 T11                                                                                                                              |  |

| GPIO1_1 Y11                                                                                                                              |  |

| GPIO2_0 U11                                                                                                                              |  |

| GPIO3_0 V11                                                                                                                              |  |

| HCKR K2                                                                                                                                  |  |

| HCKT J5                                                                                                                                  |  |

| I2C1_CLK M20                                                                                                                             |  |

| I2C1_DAT N17                                                                                                                             |  |

| I2C2_CLK L3                                                                                                                              |  |

| I2C2_DAT M1                                                                                                                              |  |

| LBA D20                                                                                                                                  |  |

| LD0 F20                                                                                                                                  |  |

| LD1 G18                                                                                                                                  |  |

| LD10 H20                                                                                                                                 |  |

| LD11 J18                                                                                                                                 |  |

| LD12 J16                                                                                                                                 |  |

| LD13 J19                                                                                                                                 |  |

| LD14 J17                                                                                                                                 |  |

| LD15 J20                                                                                                                                 |  |

| LD16 K14                                                                                                                                 |  |

| LD17 K19                                                                                                                                 |  |

| LD18 K18                                                                                                                                 |  |

| LD19 K20                                                                                                                                 |  |

| LD2 G17                                                                                                                                  |  |

| LD20 K16                                                                                                                                 |  |

| LD21 K17                                                                                                                                 |  |

| LD22 K15                                                                                                                                 |  |

| LD23 L19                                                                                                                                 |  |

| LD3 G16                                                                                                                                  |  |

| LD4 G19                                                                                                                                  |  |

| LD5 H16                                                                                                                                  |  |

| LD6 H18                                                                                                                                  |  |

| LD7 G20                                                                                                                                  |  |

| LD8 H17                                                                                                                                  |  |

| LD9 H19                                                                                                                                  |  |

### Table 95. Silicon Revision 2.1 Signal Ball Map Locations (continued)

#### How to Reach Us:

Home Page: www.freescale.com

Web Support: http://www.freescale.com/support

#### **USA/Europe or Locations Not Listed:**

Freescale Semiconductor, Inc. Technical Information Center, EL516 2100 East Elliot Road Tempe, Arizona 85284 1-800-521-6274 or +1-480-768-2130 www.freescale.com/support

#### Europe, Middle East, and Africa:

Freescale Halbleiter Deutschland GmbH Technical Information Center Schatzbogen 7 81829 Muenchen, Germany +44 1296 380 456 (English) +46 8 52200080 (English) +49 89 92103 559 (German) +33 1 69 35 48 48 (French) www.freescale.com/support

#### Japan:

Freescale Semiconductor Japan Ltd. Headquarters ARCO Tower 15F 1-8-1, Shimo-Meguro, Meguro-ku Tokyo 153-0064 Japan 0120 191014 or +81 3 5437 9125 support.japan@freescale.com

#### Asia/Pacific:

Freescale Semiconductor China Ltd. Exchange Building 23F No. 118 Jianguo Road Chaoyang District Beijing 100022 China +86 10 5879 8000 support.asia@freescale.com

#### For Literature Requests Only:

Freescale Semiconductor Literature Distribution Center P.O. Box 5405 Denver, Colorado 80217 1-800 441-2447 or +1-303-675-2140 Fax: +1-303-675-2150 LDCForFreescaleSemiconductor @hibbertgroup.com

Document Number: MCIMX35SR2CEC Rev. 10 06/2012 Information in this document is provided solely to enable system and software implementers to use Freescale Semiconductor products. There are no express or implied copyright licenses granted hereunder to design or fabricate any integrated circuits or integrated circuits based on the information in this document.

Freescale Semiconductor reserves the right to make changes without further notice to any products herein. Freescale Semiconductor makes no warranty, representation or guarantee regarding the suitability of its products for any particular purpose, nor does Freescale Semiconductor assume any liability arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without limitation consequential or incidental damages. "Typical" parameters that may be provided in Freescale Semiconductor data sheets and/or specifications can and do vary in different applications and actual performance may vary over time. All operating parameters, including "Typicals", must be validated for each customer application by customer's technical experts. Freescale Semiconductor does not convey any license under its patent rights nor the rights of others. Freescale Semiconductor products are not designed, intended, or authorized for use as components in systems intended for surgical implant into the body, or other applications intended to support or sustain life, or for any other application in which the failure of the Freescale Semiconductor product could create a situation where personal injury or death may occur. Should Buyer purchase or use Freescale Semiconductor products for any such unintended or unauthorized application, Buyer shall indemnify and hold Freescale Semiconductor and its officers, employees, subsidiaries, affiliates, and distributors harmless against all claims, costs, damages, and expenses, and reasonable attorney fees arising out of, directly or indirectly, any claim of personal injury or death associated with such unintended or unauthorized use, even if such claim alleges that Freescale Semiconductor was negligent regarding the design or manufacture of the part.

RoHS-compliant and/or Pb-free versions of Freescale products have the functionality and electrical characteristics as their non-RoHS-compliant and/or non-Pb-free counterparts. For further information, see http://www.freescale.com or contact your Freescale sales representative.

For information on Freescale's Environmental Products program, go to http://www.freescale.com/epp.

Freescale and the Freescale logo are trademarks of Freescale Semiconductor, Inc., Reg. U.S. Pat. & Tm. Off. All other product or service names are the property of their respective owners. ARM is the registered trademark of ARM Limited. ARM1136JF-S is the trademark of ARM Limited.

© 2012 Freescale Semiconductor, Inc.