Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFI

| Details                    |                                                              |

|----------------------------|--------------------------------------------------------------|

| Product Status             | Active                                                       |

| Core Processor             | Coldfire V2                                                  |

| Core Size                  | 32-Bit Single-Core                                           |

| Speed                      | 66MHz                                                        |

| Connectivity               | CANbus, EBI/EMI, Ethernet, I <sup>2</sup> C, SPI, UART/USART |

| Peripherals                | DMA, LVD, POR, PWM, WDT                                      |

| Number of I/O              | 142                                                          |

| Program Memory Size        | ·                                                            |

| Program Memory Type        | ROMIess                                                      |

| EEPROM Size                | ·                                                            |

| RAM Size                   | 64K x 8                                                      |

| Voltage - Supply (Vcc/Vdd) | 2.7V ~ 3.6V                                                  |

| Data Converters            | A/D 8x10b                                                    |

| Oscillator Type            | External                                                     |

| Operating Temperature      | -40°C ~ 85°C (TA)                                            |

| Mounting Type              | Surface Mount                                                |

| Package / Case             | 256-LBGA                                                     |

| Supplier Device Package    | 256-MAPBGA (17x17)                                           |

| Purchase URL               | https://www.e-xfl.com/pro/item?MUrl=&PartUrl=mcf5280cvf66    |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

Overview

٠

- Toggle-on-overflow feature for pulse-width modulator (PWM) generation

- One dual-mode pulse accumulation channel per timer

- Four periodic interrupt timers (PITs)

- 16-bit counter

- Selectable as free running or count down

- Software watchdog timer

- 16-bit counter

- Low-power mode support

- Phase locked loop (PLL)

- Crystal or external oscillator reference

- 2- to 10-MHz reference frequency for normal PLL mode

- 33- to 80-MHz (66 MHz for MCF5214/16) oscillator reference frequency for 1:1 mode

- Low-power modes supported

- Separate clock output pin

- Two interrupt controllers

- Support for up to 63 interrupt sources per interrupt controller (a total of 126), organized as follows:

- 56 fully-programmable interrupt sources

- 7 fixed-level interrupt sources

- Seven external interrupt signals

- Unique vector number for each interrupt source

- Ability to mask any individual interrupt source or all interrupt sources (global mask-all)

- Support for hardware and software interrupt acknowledge (IACK) cycles

- Combinatorial path to provide wake-up from low-power modes

- DMA controller

- Four fully programmable channels

- Dual-address transfer support with 8-, 16- and 32-bit data capability along with support for 16-byte (4 x 32-bit) burst transfers

- Source/destination address pointers that can increment or remain constant

- 24-bit byte transfer counter per channel

- Auto-alignment transfers supported for efficient block movement

- Bursting and cycle steal support

- Software-programmable connections between the 11 DMA requesters in the UARTs (3), 32-bit timers (4) plus external logic (4) and the four DMA channels

- External bus interface

- Glueless connections to external memory devices (e.g., SRAM, Flash, ROM, etc.)

- SDRAM controller supports 8-, 16-, and 32-bit wide memory devices

- Glueless interface to SRAM devices with or without byte strobe inputs

- Programmable wait state generator

- 32-bit bidirectional data bus

- 24-bit address bus

- Up to seven chip selects available

- Byte/write enables (byte strobes)

base address register (RAMBAR), and system control registers that include low-power and core watchdog timer control.

## 1.1.3 External Interface Module (EIM)

The external interface module handles the transfer of information between the internal core and memory, peripherals, or other processing elements in the external address space.

Programmable chip-select outputs provide signals to enable external memory and peripheral circuits, providing all handshaking and timing signals for automatic wait-state insertion and data bus sizing.

Base memory address and block size are programmable, with some restrictions. For example, the starting address must be on a boundary that is a multiple of the block size. Each chip select can be configured to provide read and write enable signals suitable for use with most popular static RAMs and peripherals. Data bus width (8-bit, 16-bit, or 32-bit) is programmable on all chip selects, and further decoding is available for protection from user mode access or read-only access.

## 1.1.4 Chip Select

Programmable chip select outputs provide a glueless connection to external memory and peripheral circuits, providing all handshaking and timing signals for automatic wait-state insertion and data bus sizing.

## 1.1.5 **Power Management**

The MCF5282 incorporates several low-power modes of operation which are entered under program control and exited by several external trigger events. An integrated Power-On Reset (POR) circuit monitors the input supply and forces an MCU reset as the supply voltage rises. The Low Voltage Detect (LVD) section monitors the supply voltage and is configurable to force a reset or interrupt condition if it falls below the LVD trip point. The RAM standby switch provides power to RAM when the supply voltage is higher than the standby voltage. If the supply voltage to chip falls below the standby battery voltage, the RAM is switched over to the standby supply.

## 1.1.6 General Input/Output Ports

All of the pins associated with the external bus interface may be used for several different functions. Their primary function is to provide an external memory interface to access off-chip resources. When not used for this function, all of the pins may be used as general-purpose digital I/O pins. In some cases, the pin function is set by the operating mode, and the alternate pin functions are not supported.

The digital I/O pins on the MCF5282 are grouped into 8-bit ports. Some ports do not use all eight bits. Each port has registers that configure, monitor, and control the port pins.

# 1.1.7 Interrupt Controllers (INTC0/INTC1)

There are two interrupt controllers on the MCF5282, each of which can support up to 63 interrupt sources for a total of 126. Each interrupt controller is organized as 7 levels with 9 interrupt sources per level. Each interrupt source has a unique interrupt vector, and 56 of the 63 sources of a given controller provide a programmable level [1-7] and priority within the level.

ColdFire Core

| BDM <sup>1</sup> | Register                                       | Width<br>(bits) | Access    | Reset Value                            | Written with<br>MOVEC | Section/Page |

|------------------|------------------------------------------------|-----------------|-----------|----------------------------------------|-----------------------|--------------|

| 0x80F            | Program Counter (PC)                           | 32              | R/W       | Contents of<br>location<br>0x0000_0004 | No                    | 2.2.5/2-7    |

|                  | Supervisor Acco                                | ess Only        | / Registe | rs                                     | I                     |              |

| 0x002            | Cache Control Register (CACR)                  | 32              | R/W       | 0x0000_0000                            | Yes                   | 2.2.6/2-7    |

| 0x004–5          | Access Control Register 0–1 (ACR0–1)           | 32              | R/W       | See Section                            | Yes                   | 2.2.7/2-7    |

| 0x800            | User/Supervisor A7 Stack Pointer<br>(OTHER_A7) | 32              | R/W       | Contents of<br>location<br>0x0000_0000 | No                    | 2.2.3/2-5    |

| 0x801            | Vector Base Register (VBR)                     | 32              | R/W       | 0x0000_0000                            | Yes                   | 2.2.8/2-7    |

| 0x80E            | Status Register (SR)                           | 16              | R/W       | 0x27                                   | No                    | 2.2.9/2-8    |

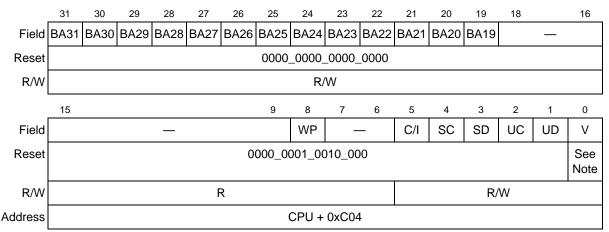

| 0xC04            | Flash Base Address Register<br>(FLASHBAR)      | 32              | R/W       | 0x0000_0000                            | Yes                   | 2.2.10/2-8   |

| 0xC05            | RAM Base Address Register (RAMBAR)             | 32              | R/W       | See Section                            | Yes                   | 2.2.10/2-8   |

### Table 2-1. ColdFire Core Programming Model (continued)

<sup>1</sup> The values listed in this column represent the Rc field used when accessing the core registers via the BDM port. For more information see Chapter 30, "Debug Support".

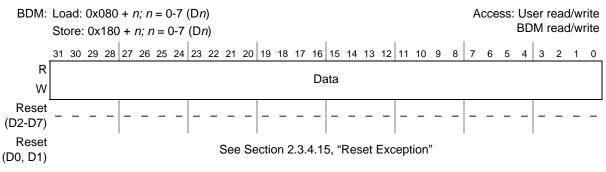

# 2.2.1 Data Registers (D0–D7)

D0–D7 data registers are for bit (1-bit), byte (8-bit), word (16-bit) and longword (32-bit) operations; they can also be used as index registers.

### NOTE

Registers D0 and D1 contain hardware configuration details after reset. See Section 2.3.4.15, "Reset Exception" for more details.

Figure 2-2. Data Registers (D0–D7)

# 2.2.2 Address Registers (A0–A6)

These registers can be used as software stack pointers, index registers, or base address registers. They can also be used for word and longword operations.

## NOTE

Flash accesses (reads/writes) by a bus master other than the core, (DMA controller or Fast Ethernet Controller), or writes to Flash by the core during programming must use the backdoor Flash address of IPSBAR plus an offset of 0x0400\_0000. For example, for a DMA transfer from the first location of Flash when IPSBAR is still at its default location of 0x4000\_0000, the source register would be loaded with 0x4400\_0000. Backdoor access to Flash for reads can be made by the bus master, but it takes 2 cycles longer than a direct read of the Flash if using its FLASHBAR address.

## NOTE

The Flash is marked as valid on reset based on the RCON (reset configuration) pin state. Flash space is valid on reset when booting in single chip mode (RCON pin asserted and D[26]/D[17]/D[16] set to 110), or when booting internally in master mode (RCON asserted and D[26]/D[17]/D[16] are set to 111 and D[18] and D[19] are set to 00). See Chapter 27, "Chip Configuration Module (CCM)" for more details. When the default reset configuration is not overriden, the device (by default) boots in single chip mode and the Flash space will be marked as valid at address 0x0. The Flash configuration field is checked during the reset sequence to see if the Flash is secured. If it is the part will always boot from internal Flash, since it will be marked as valid, regardless of what is done for chip configuration.

**Note:** The reset value for the valid bit is determined by the chip mode selected at reset (see Chapter 27, "Chip Configuration Module (CCM)").

### Figure 6-3. Flash Base Address Register (FLASHBAR)

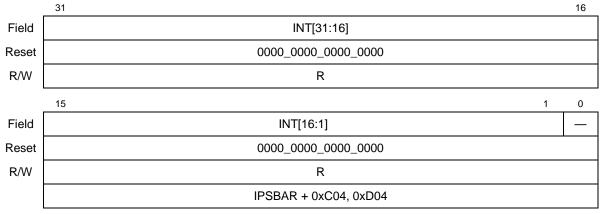

#### Table 10-4. IPRHn Field Descriptions

| Bits | Name | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

|------|------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 31–0 | INT  | Interrupt pending. Each bit corresponds to an interrupt source. The corresponding IMRH <i>n</i> bit determines whether an interrupt condition can generate an interrupt. At every system clock, the IPRH <i>n</i> samples the signal generated by the interrupting source. The corresponding IPRH <i>n</i> bit reflects the state of the interrupt signal even if the corresponding IMRH <i>n</i> bit is set.<br>0 The corresponding interrupt source does not have an interrupt pending<br>1 The corresponding interrupt source has an interrupt pending |

#### Figure 10-2. Interrupt Pending Register Low (IPRLn)

#### Table 10-5. IPRLn Field Descriptions

| Bits | Name | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

|------|------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 31–1 | INT  | Interrupt Pending. Each bit corresponds to an interrupt source. The corresponding IMRL <i>n</i> bit determines whether an interrupt condition can generate an interrupt. At every system clock, the IPRL <i>n</i> samples the signal generated by the interrupting source. The corresponding IPRL <i>n</i> bit reflects the state of the interrupt signal even if the corresponding IMRL <i>n</i> bit is set.<br>0 The corresponding interrupt source does not have an interrupt pending<br>1 The corresponding interrupt source has an interrupt pending |

| 0    | _    | Reserved, should be cleared.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

## 10.3.2 Interrupt Mask Register (IMRHn, IMRLn)

The IMRH*n* and IMRL*n* registers are each 32 bits in size and provide a bit map for each interrupt to allow the request to be disabled (1 = disable the request, 0 = enable the request). The IMR*n* is set to all ones by reset, disabling all interrupt requests. The IMR*n* can be read and written. A write that sets bit 0 of the IMR forces the other 63 bits to be set, disabling all interrupt sources, and providing a global mask-all capability.

# 14.2.5 External Interrupt Signals

## 14.2.5.1 External Interrupts (IRQ[7:1])

These inputs are the external interrupt sources. See Chapter 11, "Edge Port Module (EPORT)" for more information on these interrupt sources and their corresponding registers.

These pins are configured as GPIO PNQ[7:1] in single-chip mode.

## 14.2.6 Ethernet Module Signals

The following signals are used by the Ethernet module for data and clock signals.

### NOTE

These signals are not available on the MCF5214 and MCF5216.

## 14.2.6.1 Management Data (EMDIO)

The bidirectional EMDIO signal transfers control information between the external PHY and the media-access controller. Data is synchronous to EMDC and applies to MII mode operation. This signal is an input after reset. When the FEC is operated in 10 Mbps 7-wire interface mode, this signal should be connected to VSS.

This pin can also be configured as GPIO PAS5 or URXD2.

## 14.2.6.2 Management Data Clock (EMDC)

EMDC is an output clock which provides a timing reference to the PHY for data transfers on the EMDIO signal and applies to MII mode operation.

This pin can also be configured as GPIO PAS4 or UTXD2.

## 14.2.6.3 Transmit Clock (ETXCLK)

This is an input clock which provides a timing reference for ETXEN, ETXD[3:0] and ETXER.

This pin can also be configured as GPIO PEH7.

## 14.2.6.4 Transmit Enable (ETXEN)

The transmit enable (ETXEN) output indicates when valid nibbles are present on the MII. This signal is asserted with the first nibble of a preamble and is negated before the first ETXCLK following the final nibble of the frame.

This pin can also be configured as GPIO PEH6.

## 14.2.6.5 Transmit Data 0 (ETXD0)

ETXD0 is the serial output Ethernet data and is only valid during the assertion of ETXEN. This signal is used for 10 Mbps Ethernet data. This signal is also used for MII mode data in conjunction with ETXD[3:1].

This pin can also be configured as GPIO PEH5.

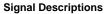

### Figure 15-2. DRAM Control Register (DCR)

Table 15-4 describes DCR fields.

| Table 15-4. | DCR Field | d Descriptions |

|-------------|-----------|----------------|

|-------------|-----------|----------------|

| Bits  | Name | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

|-------|------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 15-14 | —    | Reserved, should be cleared.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| 13    | NAM  | No address multiplexing. Some implementations require external multiplexing. For example, when linear addressing is required, the SDRAM should not multiplex addresses on SDRAM accesses.<br>0 The SDRAM controller multiplexes the external address bus to provide column addresses.<br>1 The SDRAM controller does not multiplex the external address bus to provide column addresses.                                                                                                                                                                                                                                                         |

| 12    | COC  | <ul> <li>Command on SDRAM clock enable (SCKE). Implementations that use external multiplexing (NAM = 1) must support command information to be multiplexed onto the SDRAM address bus.</li> <li>0 SCKE functions as a clock enable; self-refresh is initiated by the SDRAM controller through DCR[IS].</li> <li>1 SCKE drives command information. Because SCKE is not a clock enable, self-refresh cannot be used (setting DCR[IS]). Thus, external logic must be used if this functionality is desired. External multiplexing is also responsible for putting the command information on the proper address bit.</li> </ul>                    |

| 11    | IS   | <ul> <li>Initiate self-refresh command.</li> <li>Take no action or issue a SELFX command to exit self refresh.</li> <li>If DCR[COC] = 0, the SDRAM controller sends a SELF command to both SDRAM blocks to put them in low-power, self-refresh state where they remain until IS is cleared. When IS is cleared, the controller sends a SELFX command for the SDRAMs to exit self-refresh. The refresh counter is suspended while the SDRAMs are in self-refresh; the SDRAM controls the refresh period.</li> </ul>                                                                                                                               |

| 10–9  | RTIM | Refresh timing. Determines the timing operation of auto-refresh in the SDRAM controller. Specifically, it determines the number of bus clocks inserted between a REF command and the next possible ACTV command. This same timing is used for both memory blocks controlled by the SDRAM controller. This corresponds to t <sub>RC</sub> in the SDRAM specifications.<br>00 3 clocks<br>01 6 clocks<br>1x 9 clocks                                                                                                                                                                                                                               |

| 8–0   | RC   | Refresh count. Controls refresh frequency. The number of bus clocks between refresh cycles is $(RC + 1) \times 16$ . Refresh can range from 16–8192 bus clocks to accommodate both standard and low-power SDRAMs with bus clock operation from less than 2 MHz to greater than 50 MHz. The following example calculates RC for an auto-refresh period for 4096 rows to receive 64 ms of refresh every 15.625 µs for each row (1031 bus clocks at 66 MHz). This operation is the same as in asynchronous mode.<br># of bus clocks = 1031 = (RC field + 1) × 16<br>RC = (1031 bus clocks/16) -1 = 63.44, which rounds to 63; therefore, RC = 0x3F. |

| 31–16 | _     | Reserved. Should be cleared.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

|-------|-------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 15–0  | DMACn | <ul> <li>DMA Channel <i>n</i>. Each four bit field defines the logical connection between the DMA requestors and that DMA channel. There are seven possible requesters (4 DMA Timers and 3 UARTs). Any request can be routed to any of the DMA channels. Effectively, the DMAREQC provides a software-controlled routing matrix of the 7 DMA request signals to the 4 channels of the DMA module. DMAC3 controls DMA channel 3. DMAC2 controls DMA channel 2. DMAC1 controls DMA channel 1. DMAC0 controls DMA channel 0.</li> <li>1000 UART0.</li> <li>1001 UART1.</li> <li>1010 UART2.</li> <li>0100 DMA Timer 0.</li> <li>0111 DMA Timer 3.</li> <li>All other values are reserved and will not generate a DMA request.</li> </ul> |

| Bits | Name | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

|------|------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 15   | AT   | <ul> <li>AT is available only if MPARK[BCR24BIT] = 1.</li> <li>DMA acknowledge type. Controls whether acknowledge information is provided for the entire transfer or only the final transfer.</li> <li>0 Entire transfer. DMA acknowledge information is displayed anytime the channel is selected as the result of an external request.</li> <li>1 Final transfer (when BCR reaches zero). For dual-address transfer, the acknowledge information is displayed for both the read and write cycles.</li> </ul> |

| 14–0 |      | Reserved, should be cleared.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

#### Table 16-3. DCRn Field Descriptions (continued)

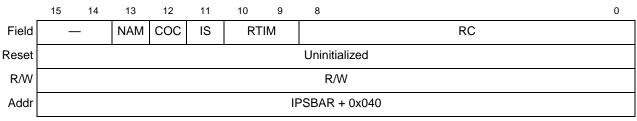

# 16.4.5 DMA Status Registers (DSR0–DSR3)

In response to an event, the DMA controller writes to the appropriate DSRn bit, Figure 16-9. Only a write to DSRn[DONE] results in action.

Figure 16-9. DMA Status Registers (DSRn)

Table 16-4 describes DSR*n* fields.

Table 16-4. DSR*n* Field Descriptions

| Bits | Name | Description                                                                                                                                                                                                                                                                                             |

|------|------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7    | _    | Reserved, should be cleared.                                                                                                                                                                                                                                                                            |

| 6    | CE   | Configuration error. Occurs when BCR, SAR, or DAR does not match the requested transfer size,<br>or if BCR = 0 when the DMA receives a start condition. CE is cleared at hardware reset or by writing<br>a 1 to DSR[DONE].<br>0 No configuration error exists.<br>1 A configuration error has occurred. |

| 5    | BES  | Bus error on source<br>0 No bus error occurred.<br>1 The DMA channel terminated with a bus error during the read portion of a transfer.                                                                                                                                                                 |

| 4    | BED  | Bus error on destination<br>0 No bus error occurred.<br>1 The DMA channel terminated with a bus error during the write portion of a transfer.                                                                                                                                                           |

| 3    | _    | Reserved, should be cleared.                                                                                                                                                                                                                                                                            |

| 2    | REQ  | <ul> <li>Request</li> <li>0 No request is pending or the channel is currently active. Cleared when the channel is selected.</li> <li>1 The DMA channel has a transfer remaining and the channel is not selected.</li> </ul>                                                                             |

Fast Ethernet Controller (FEC)

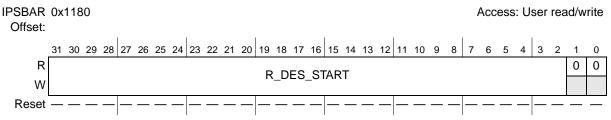

### Figure 17-22. Ethernet Receive Descriptor Ring Start Register (ERDSR)

Table 17-26. ERDSR Field Descriptions

| Field               | Description                                          |

|---------------------|------------------------------------------------------|

| 31–2<br>R_DES_START | Pointer to start of receive buffer descriptor queue. |

| 1–0                 | Reserved, must be cleared.                           |

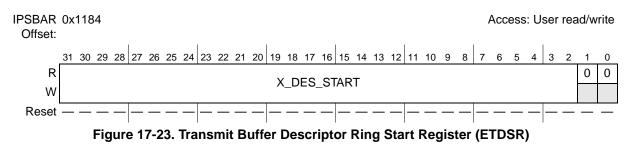

# 17.4.23 Transmit Buffer Descriptor Ring Start Registers (ETSDR)

ETSDR provides a pointer to the start of the circular transmit buffer descriptor queue in external memory. This pointer must be 32-bit aligned; however, it is recommended it be made 128-bit aligned (evenly divisible by 16). You should write zeros to bits 1 and 0. Hardware ignores non-zero values in these two bit positions.

This register is undefined at reset and must be initialized prior to operation.

| Field               | Description                                           |  |

|---------------------|-------------------------------------------------------|--|

| 31–2<br>X_DES_START | Pointer to start of transmit buffer descriptor queue. |  |

| 1–0                 | Reserved, must be cleared.                            |  |

# 17.4.24 Receive Buffer Size Register (EMRBR)

The EMRBR is a user-programmable register that dictates the maximum size of all receive buffers. This value should take into consideration that the receive CRC is always written into the last receive buffer. To allow one maximum size frame per buffer, EMRBR must be set to RCR[MAX\_FL] or larger. To properly align the buffer, EMRBR must be evenly divisible by 16. To ensure this, bits 3–0 are forced low.

#### Fast Ethernet Controller (FEC)

group address is determined by the I/G bit in the destination address field. A flowchart for address recognition on received frames appears in the figures below.

Address recognition is accomplished through the use of the receive block and microcode running on the microcontroller. The flowchart shown in Figure 17-27 illustrates the address recognition decisions made by the receive block, while Figure 17-28 illustrates the decisions made by the microcontroller.

If the DA is a broadcast address and broadcast reject (RCR[BC\_REJ]) is cleared, then the frame is accepted unconditionally, as shown in Figure 17-27. Otherwise, if the DA is not a broadcast address, then the microcontroller runs the address recognition subroutine, as shown in Figure 17-28.

If the DA is a group (multicast) address and flow control is disabled, then the microcontroller performs a group hash table lookup using the 64-entry hash table programmed in GAUR and GALR. If a hash match occurs, the receiver accepts the frame.

If flow control is enabled, the microcontroller does an exact address match check between the DA and the designated PAUSE DA (01:80:C2:00:00:01). If the receive block determines the received frame is a valid PAUSE frame, the frame is rejected. The receiver detects a PAUSE frame with the DA field set to the designated PAUSE DA or the unicast physical address.

If the DA is the individual (unicast) address, the microcontroller performs an individual exact match comparison between the DA and 48-bit physical address that you program in the PALR and PAUR registers. If an exact match occurs, the frame is accepted; otherwise, the microcontroller does an individual hash table lookup using the 64-entry hash table programmed in registers, IAUR and IALR. In the case of an individual hash match, the frame is accepted. Again, the receiver accepts or rejects the frame based on PAUSE frame detection, shown in Figure 17-27.

If neither a hash match (group or individual) nor an exact match (group or individual) occur, and if promiscuous mode is enabled (RCR[PROM] set), the frame is accepted and the MISS bit in the receive buffer descriptor is set; otherwise, the frame is rejected.

Similarly, if the DA is a broadcast address, broadcast reject (RCR[BC\_REJ]) is asserted, and promiscuous mode is enabled, the frame is accepted and the MISS bit in the receive buffer descriptor is set; otherwise, the frame is rejected.

In general, when a frame is rejected, it is flushed from the FIFO.

• Start/end break interrupt/status

# 23.2 External Signal Description

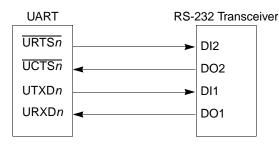

Table 23-1 briefly describes the UART module signals.

| Signal | Description                                                                                                                                                                                                                                                                                 |  |  |  |

|--------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| UTXDn  | Transmitter Serial Data Output. UTXD <i>n</i> is held high (mark condition) when the transmitter is disabled, idle, or operating in the local loopback mode. Data is shifted out on UTXD <i>n</i> on the falling edge of the clock source, with the least significant bit (lsb) sent first. |  |  |  |

| URXDn  | Receiver Serial Data Input. Data received on URXD <i>n</i> is sampled on the rising edge of the clock source, with the lsb received first.                                                                                                                                                  |  |  |  |

| UCTSn  | Clear-to- Send. This input can generate an interrupt on a change of state.                                                                                                                                                                                                                  |  |  |  |

| URTSn  | Request-to-Send. This output can be programmed to be negated or asserted automatically by the receiver or the transmitter. When connected to a transmitter's UCTS <i>n</i> , URTS <i>n</i> can control serial data flow.                                                                    |  |  |  |

Figure 23-2 shows a signal configuration for a UART/RS-232 interface.

Figure 23-2. UART/RS-232 Interface

# 23.3 Memory Map/Register Definition

This section contains a detailed description of each register and its specific function. Flowcharts in Section 23.5, "Initialization/Application Information," describe basic UART module programming. Writing control bytes into the appropriate registers controls the operation of the UART module.

## NOTE

UART registers are accessible only as bytes.

### NOTE

Interrupt can mean an interrupt request asserted to the CPU or a DMA request.

#### General Purpose I/O Module

| Table 26-1. | Ports | External | Signals |

|-------------|-------|----------|---------|

|             |       |          |         |

| Primary<br>Function<br>(Pin Name) <sup>1</sup> | GPIO<br>(Default<br>Function) | Alternate<br>Function 1 | Alternate<br>Function 2 | Description                                                                            |  |

|------------------------------------------------|-------------------------------|-------------------------|-------------------------|----------------------------------------------------------------------------------------|--|

| D[31:0] <sup>2</sup>                           | PA, PB,<br>PC, PD             | _                       | _                       | External data bus / Ports A, B, C, D                                                   |  |

| OE <sup>1</sup>                                | PE[7]                         |                         | —                       | Output enable for external reads / Port E[7]                                           |  |

| TA <sup>1</sup>                                | PE[6]                         | _                       | —                       | Transfer acknowledge for external data transfer / Port E[6]                            |  |

| TEA <sup>1</sup>                               | PE[5]                         | —                       | —                       | Transfer error acknowledge for external data transfer / Port E[5]                      |  |

| R/W <sup>1</sup>                               | PE[4]                         | —                       | —                       | Read/Write indication for external data transfer / Port E[4]                           |  |

| SIZ1 <sup>1</sup>                              | PE[3]                         | SYNCA                   | —                       | Size of the external data transfer / Port E[3] / Timer A sync                          |  |

| SIZ0 <sup>1</sup>                              | PE[2]                         | SYNCB                   | —                       | Size of the external data transfer / Port E[3:2] / Timer B sync                        |  |

| TS <sup>1</sup>                                | PE[1]                         | SYNCA                   | —                       | Transfer start indication for external data transfer / Port E[1] / Timer A sync        |  |

| TIP <sup>1</sup>                               | PE[0]                         | SYNCB                   | —                       | Transfer in progress indication for external data transfer / Port E[0] / Timer B sync  |  |

| A[23:21] <sup>1</sup>                          | PF[7:5]                       | <u>CS</u> [6:4]         | —                       | External address bus [23:21] / Port F[7:5] / Chip selects 6-4                          |  |

| A[20:0] <sup>1</sup>                           | PF[4:0],<br>PG, PH            | _                       | _                       | External address bus [20:0] / Ports F[4:0], G, H                                       |  |

| BS[3:0] <sup>1</sup>                           | PJ[7:4]                       | —                       | —                       | Byte strobes for external data transfer / Port J[7:4] / SDRAM column address strobes   |  |

| CS[3:0] <sup>1</sup>                           | PJ[3:0]                       | _                       | —                       | Chip selects 3 - 0 / Port J[3:0]                                                       |  |

| DDATA[3:0]                                     | PDD[7:4]                      | —                       | —                       | Debug data / Port DD[7:4]                                                              |  |

| PST[3:0]                                       | PDD[7:4]                      | —                       | —                       | Processor status / Port DD[3:0]                                                        |  |

| CANRX                                          | PAS[3]                        | URXD2                   | —                       | FlexCAN receive data / Port AS[3] / URXD2                                              |  |

| CANTX                                          | PAS[2]                        | UTXD2                   | —                       | FlexCAN transmit data / Port AS[2] / UTXD2                                             |  |

| SDA                                            | PAS[1]                        | URXD2                   | —                       | I <sup>2</sup> C serial data / Port AS[1] / URXD2                                      |  |

| SCL                                            | PAS[0]                        | UTXD2                   | —                       | I <sup>2</sup> C serial clock / Port AS[0] / UTXD2                                     |  |

| IRQ[7:1] <sup>3</sup>                          | PNQ[7:1]                      | —                       | —                       | Edge Port external interrupt pins / Port NQ[7:1]                                       |  |

| AN[56:55:53:52]                                | PQA<br>[4:3:1:0]              | ETRIG[2:1],<br>MA[1:0]  | —                       | QADC analog inputs / Port QA[4:3:1:0] / external triggers / external multiplex control |  |

| AN[3:0] <sup>2</sup>                           | PQB[3:0]                      | ANZ, ANY,<br>ANX, ANW   | _                       | QADC analog inputs / Port QB[3:0] / multiplexed analog inputs                          |  |

| QSPI_CS<br>[3:0]                               | PQS[6:3]                      |                         | _                       | QSPI synchronous peripheral chip selects / Port QS[3:6]                                |  |

| QSPI_CLK                                       | PQS[2]                        | —                       | —                       | QSPI serial clock / Port QS[2]                                                         |  |

| QSPI_DIN                                       | PQS[1]                        | —                       | —                       | QSPI serial data input / Port QS[1]                                                    |  |

| QSPI_DOUT                                      | PQS[0]                        | —                       | —                       | QSPI serial data output / Port QS[0]                                                   |  |

| SRAS                                           | PSD[5]                        | —                       | —                       | SDRAM synchronous row address strobe / Port SD[5]                                      |  |

# 26.3.2 Register Descriptions

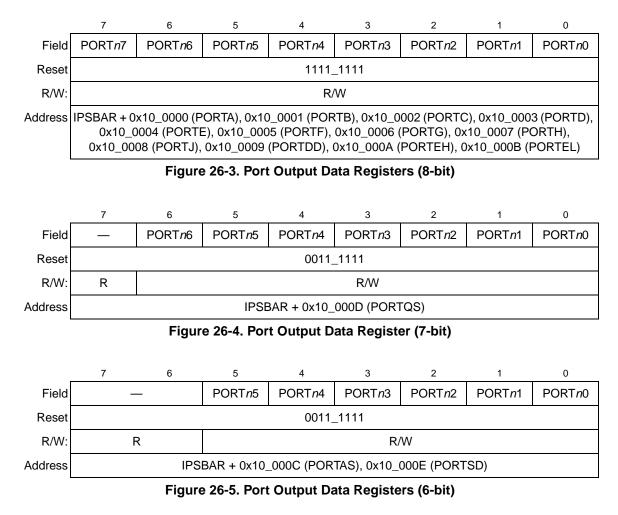

## 26.3.2.1 Port Output Data Registers (PORTn)

The PORTn registers store the data to be driven on the corresponding port n pins when the pins are configured for digital output.

Most PORT*n* registers have a full 8-bit implementation, as shown in Figure 26-3. The remaining PORT*n* registers use fewer than eight bits. Their bit definitions are shown in Figure 26-4, Figure 26-5, and Figure 26-6.

At reset, all bits in the PORT*n* registers are set.

Reading a PORT*n* register returns the current values in the register, not the port *n* pin values.

PORT*n* bits can be set by setting the PORT*n* register, or by setting the corresponding bits in the PORT*n*P/SET*n* register. They can be cleared by clearing the PORT*n* register, or by clearing the corresponding bits in the CLR*n* register.

Chip Configuration Module (CCM)

| Pin(s) Affected  | Default<br>Configuration    | Override Pins<br>in Reset <sup>2,34</sup> | Function                                                     |

|------------------|-----------------------------|-------------------------------------------|--------------------------------------------------------------|

| CS0              | RCON[4:3] = 00<br>RCON2 = 0 | D[19:18]                                  | Boot Device                                                  |

|                  |                             | 00                                        | Internal with 32-bit port <sup>5</sup>                       |

|                  |                             | 10                                        | External with 8-bit port                                     |

|                  |                             | 01                                        | External with 16-bit port                                    |

|                  |                             | 11                                        | External with 32-bit port                                    |

| All output pins  | RCON5 = 1                   | D21                                       | Output Pad Drive Strength                                    |

|                  |                             | 0                                         | Partial strength                                             |

|                  |                             | 1                                         | Full strength <sup>5</sup>                                   |

| Clock mode       | N/A                         | CLKMOD1, CLKMOD0                          | Clock Mode                                                   |

|                  |                             | 00                                        | External clock mode (PLL disabled)                           |

|                  |                             | 01                                        | 1:1 PLL mode                                                 |

|                  |                             | 10                                        | Normal PLL mode with external<br>clock reference             |

|                  |                             | 11                                        | Normal PLL mode w/crystal reference                          |

| A[23:21]/CS[6:4] | RCON[9:8] = 00              | D[25:24]                                  | Chip Select Configuration                                    |

|                  |                             | 00                                        | PF[7:5] = A[23:21] <sup>5</sup>                              |

|                  |                             | 10                                        | $PF[7] = \overline{CS6} / PF[6:5] = A[22:21]$                |

|                  |                             | 01                                        | $PF[7:6] = \overline{CS6}, \ \overline{CS5} / PF[5] = A[21]$ |

|                  |                             | 11                                        | $PF[7:6] = \overline{CS6},  \overline{CS5},  \overline{CS4}$ |

| Table 27-8. Configuration Duri | ng Reset <sup>1</sup> (continued) |

|--------------------------------|-----------------------------------|

|--------------------------------|-----------------------------------|

<sup>1</sup> Modifying the default configurations is possible only if the external RCON pin is asserted.

<sup>2</sup> The D[31:27, 23:22, 20, 15:0] pins do not affect reset configuration.

<sup>3</sup> The external reset override circuitry drives the data bus pins with the override values while RSTO is asserted. It must stop driving the data bus pins within one CLKOUT cycle after RSTO is negated. To prevent contention with the external reset override circuitry, the reset override pins are forced to inputs during reset and do not become outputs until at least one CLKOUT cycle after RSTO is negated.

- <sup>4</sup> RCON[0] has higher priority than RCON[3:2]. When RCON[0] is configured to boot the chip in single chip mode, the part will boot internally with a 32-bit port overriding any configuration set by RCON[3:2].

- <sup>5</sup> Default configuration

## 27.6.2 Chip Mode Selection

The chip mode is selected during reset and reflected in the MODE field of the chip configuration register (CCR). See Section 27.5.3.1, "Chip Configuration Register (CCR)." Once reset is exited, the operating mode cannot be changed. Table 27-9 shows the mode selection during reset configuration.

I

<sup>1</sup> All channels not listed are reserved or unimplemented and return undefined results.

## 28.6.8 Result Registers

The result word table is a 64 half-word (128 byte) long by 10-bit wide RAM. An entry is written by the QADC after completing an analog conversion specified by the corresponding CCW table entry.

### 28.6.8.1 Right-Justified Unsigned Result Register (RJURR)

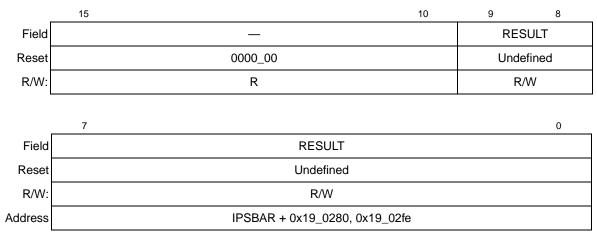

Figure 28-15. Right-Justified Unsigned Result Register (RJURR)

#### Table 28-18. RJURR Field Descriptions

| Bit(s) | Name   | Description                                              |  |  |

|--------|--------|----------------------------------------------------------|--|--|

| 15–10  | —      | Reserved, should be cleared.                             |  |  |

| 9–0    | RESULT | The conversion result is unsigned, right-justified data. |  |  |

## 28.6.8.2 Left-Justified Signed Result Register (LJSRR)

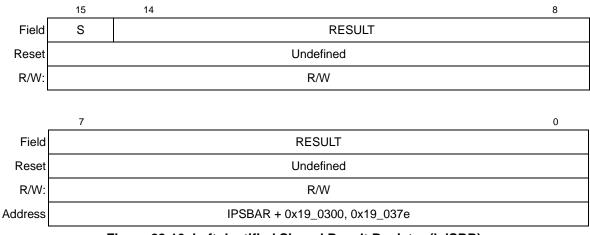

### Figure 28-16. Left-Justified Signed Result Register (LJSRR)

# 28.9.4 Analog Supply Filtering and Grounding

Two important factors influencing performance in analog integrated circuits are supply filtering and grounding. Generally, digital circuits use bypass capacitors on every  $V_{DD}/V_{SS}$  signal pair. This applies to analog subsystems and submodules also. Equally important as bypassing is the distribution of power and ground.

Analog supplies should be isolated from digital supplies as much as possible. This necessity stems from the higher performance requirements often associated with analog circuits. Therefore, deriving an analog supply from a local digital supply is not recommended. However, if for cost reasons digital and analog power are derived from a common regulator, filtering of the analog power is recommended in addition to the bypassing of the supplies already mentioned. For example, an RC low pass filter could be used to isolate the digital and analog supplies when generated by a common regulator. If multiple high precision analog circuits are locally employed (for example, two A/D converters), the analog supplies should be isolated from each other as sharing supplies introduces the potential for interference between analog circuits.

Grounding is the most important factor influencing analog circuit performance in mixed signal systems (or in standalone analog systems). Close attention must be paid not to introduce additional sources of noise into the analog circuitry. Common sources of noise include ground loops, inductive coupling, and combining digital and analog grounds together inappropriately.

The problem of how and when to combine digital and analog grounds arises from the large transients which the digital ground must handle. If the digital ground is not able to handle the large transients, the associated current can return to ground through the analog ground. It is this excess current overflowing into the analog ground which causes performance degradation by developing a differential voltage between the true analog ground and the microcontroller's ground pins. The end result is that the ground observed by the analog circuit is no longer true ground and thus skews converter performance.

Two similar approaches to improving or eliminating the problems associated with grounding excess transient currents involve star-point ground systems. One approach is to star-point the different grounds at the power supply origin, thus keeping the ground isolated. Refer to Figure 28-49.

Another approach is to star-point the different grounds near the analog ground signal on the microcontroller by using small traces for connecting the non-analog grounds to the analog ground. The small traces are meant only to accommodate dc differences, not ac transients.

### NOTE

This star-point scheme still requires adequate grounding for digital and analog subsystems in addition to the star-point ground.

| Address        | Name                                                | Mnemonic | Size |

|----------------|-----------------------------------------------------|----------|------|

| IPSBAR + 0xC18 | Interrupt Level Request Register 0                  | ILRR0    | 8    |

| IPSBAR + 0XC19 | Interrupt Acknowledge Level and Priority Register 0 | IACKLPR0 | 8    |

| IPSBAR + 0xC41 | Interrupt Control Register 0-01                     | ICR001   | 8    |

| IPSBAR + 0xC42 | Interrupt Control Register 0-02                     | ICR002   | 8    |

| IPSBAR + 0xC43 | Interrupt Control Register 0-03                     | ICR003   | 8    |

| IPSBAR + 0xC44 | Interrupt Control Register 0-04                     | ICR004   | 8    |

| IPSBAR + 0xC45 | Interrupt Control Register 0-05                     | ICR005   | 8    |

| IPSBAR + 0xC46 | Interrupt Control Register 0-06                     | ICR006   | 8    |

| IPSBAR + 0xC47 | Interrupt Control Register 0-07                     | ICR007   | 8    |

| IPSBAR + 0xC48 | Interrupt Control Register 0-08                     | ICR008   | 8    |

| IPSBAR + 0xC49 | Interrupt Control Register 0-09                     | ICR009   | 8    |

| IPSBAR + 0xC4A | Interrupt Control Register 0-10                     | ICR010   | 8    |

| IPSBAR + 0xC4B | Interrupt Control Register 0-11                     | ICR011   | 8    |

| IPSBAR + 0xC4C | Interrupt Control Register 0-12                     | ICR012   | 8    |

| IPSBAR + 0xC4D | Interrupt Control Register 0-13                     | ICR013   | 8    |

| IPSBAR + 0xC4E | Interrupt Control Register 0-14                     | ICR014   | 8    |

| IPSBAR + 0xC4F | Interrupt Control Register 0-15                     | ICR015   | 8    |

| IPSBAR + 0xC51 | Interrupt Control Register 0-17                     | ICR017   | 8    |

| IPSBAR + 0xC52 | Interrupt Control Register 0-18                     | ICR018   | 8    |

| IPSBAR +0xC53  | Interrupt Control Register 0-19                     | ICR019   | 8    |

| IPSBAR + 0xC54 | Interrupt Control Register 0-20                     | ICR020   | 8    |

| IPSBAR + 0xC55 | Interrupt Control Register 0-21                     | ICR021   | 8    |

| IPSBAR + 0xC56 | Interrupt Control Register 0-22                     | ICR022   | 8    |

| IPSBAR + 0xC57 | Interrupt Control Register 0-23                     | ICR023   | 8    |

| IPSBAR + 0xC58 | Interrupt Control Register 0-24                     | ICR024   | 8    |

| IPSBAR + 0xC59 | Interrupt Control Register 0-25                     | ICR025   | 8    |

| IPSBAR + 0xC5A | Interrupt Control Register 0-26                     | ICR026   | 8    |

| IPSBAR + 0xC5B | Interrupt Control Register 0-27                     | ICR027   | 8    |

| IPSBAR + 0xC5C | Interrupt Control Register 0-28                     | ICR028   | 8    |

| IPSBAR + 0xC5D | Interrupt Control Register 0-29                     | ICR029   | 8    |

| IPSBAR + 0xC5E | Interrupt Control Register 0-30                     | ICR030   | 8    |

| IPSBAR + 0xC5F | Interrupt Control Register 0-31                     | ICR031   | 8    |

| IPSBAR + 0xC60 | Interrupt Control Register 0-32                     | ICR032   | 8    |

### Table A-3. Register Memory Map (continued)

reads 6-17 setting CFMCLKD 6-17 stop mode 6-21 verify 6-18 writes 6-17 registers clock divider (CFMCLKD) 6-9 setting 6-17 command (CFMCMD) 6-16 configuration (CFMCR) 6-8 data access (CFMDACC) 6-14 FLASHBAR 6-5 protection (CFMPROT) 6-12 security (CFMSEC) 6-10 supervisor access (CFMSACC) 6-13 user status (CFMUSTAT) 6-15 reset 6-23 security back door access 6-23 erase verify check 6-23 Collision handling 17-42 Core block diagram 2-1 low-power modes 7-6 registers address (An) 2-4 condition code (CCR) 2-6 data (Dn) 2-4 program counter (PC) 2-7 stack pointer (A7) 2-5 status register (SR) 2-8 vector base (VBR) 2-7 Cyclic redundancy check error (CRCERR) bit 25-26

### D

DC characteristics 33-3 Debug see BDM breakpoint functions 30-7 operation 30-37 data 30-39 electrical characteristics AC timing specifications 33-27 emulator mode 30-38 interrupt 30-37 low-power modes 7-13 operation 30-37 overview 30-1 processor status 30-2, 30-39 programming model 30-5 registers

address attribute trigger (AATR) 30-7 address breakpoint (ABLR, ABHR) 30-9 configuration/status (CSR) 30-10 data breakpoint/mask (DBR, DBMR) 30-12 program counter breakpoint/mask (PBR, PBMR) 30-13 trigger definition (TDR) 30-14 support, real-time 30-37 taken branch 30-4 trace, real-time 30-2 Debug interrupt 30-37 DMA controller channel prioritization 16-12 data transfer auto alignment 16-13 bandwidth control 16-14 dual-address 16-12 overview 16-4 requests 16-11 termination 16-14 functional description 16-11 low-power modes 7-7 overview 16-1 programming 16-12 registers byte count (BCRn) 16-7 control (DCRn) 16-7 destination address (DARn) 16-6 request control (DMAREQC) 16-2 source address (SARn) 16-5 status (DSRn) 16-10 signal diagram 16-1 **DMA** timers electrical characteristics AC timing specifications 33-24 operation low-power modes 7-8 Doze mode 7-6

## Ε

Electrical characteristics bus external output timing specifications 33-12 processor input timing specifications 33-11 ColdFire Flash module module life characteristics 33-11 program and erase characteristics 33-10 DC specifications 33-3 debug AC timing specifications 33-27 DMA timer AC timing specifications 33-24 FEC AC timing specifications 33-21 GPIO timing 33-18 I<sup>2</sup>C input timing between SCL and SDA 33-20

set-and-forget 19-6 registers control and status (PCSR) 19-3 count (PCNTR) 19-5 modulus (PMR) 19-5 timeout 19-7 watchdog, see watchdog timer 18-2 Timing diagrams debug BDM serial port AC timing 33-28 real-time trace AC timing 33-28 Ethernet MII async input signal 33-23 general input timing requirements 33-12 GPIO 33-19 digital input 26-28 digital output 26-28  $I^2C$ input/output timing 33-21 JTAG BKPT timing 33-27 boundary scan 33-26 test access port 33-26 test clock input timing 33-26 TRST timing 33-27 OADC bypass mode conversion timing 28-33 conversion in external positive edge trigger mode 28-59 conversion in gated mode, continuous scan 28-60 conversion in gated mode, single scan 28-60 conversion timing 28-33 QSPI timing 33-25 reset controller RSTI and configuration override timing 33-20 SDRAM controller read cycle 33-17 write cycle 33-18 SRAM bus cycle terminated by  $\overline{TA}$  33-15 bus cycle terminated by TEA 33-16 Transmit bit error (BITERR) 25-26

### U

UART modules clock select registers (UCSR*n*) 23-9 clock source baud rates 23-17 divider 23-17 external 23-18 command registers (UCR*n*) 23-9 core interrupts 23-26 DMA service 23-27 FIFO stack 23-21 initialization 23-29 input port change (UIPCRn) 23-12 memory map 23-3 operation looping modes automatic echo 23-23 local loop-back 23-23 remote loop-back 23-23 low-power modes 7-8 multidrop mode 23-24 receiver 23-20 transmitter 23-18 registers auxiliary control (UACRn) 23-13 baud rate generator (UBG1n/UBG2n) 23-15 input port (UIPn) 23-15 interrupt status/mask (UISRn/UIMRn) 23-13 mode 1 (UMR1n) 23-5 mode 2 (UMR2n) 23-6 output port command (UOP1n/UOP0n) 23-16 receive buffers (URBn) 23-11 status (USRn) 23-8 transmit buffers (UTBn) 23-12

### V

Variant address 30-4

### W

Wait mode 7-6 Wake interrupt (WAKEINT) 25-16, 25-27 Watchdog timer block diagram 18-2 memory map 18-2 operation low-power 7-10, 18-1 overview 18-1 registers control (WCR) 18-3 count (WCNTR) 18-5 modulus (WMR) 18-4 service (WSR) 18-5 WDDATA execution 30-3