Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Details                    |                                                              |

|----------------------------|--------------------------------------------------------------|

| Product Status             | Obsolete                                                     |

| Core Processor             | Coldfire V2                                                  |

| Core Size                  | 32-Bit Single-Core                                           |

| Speed                      | 66MHz                                                        |

| Connectivity               | CANbus, EBI/EMI, Ethernet, I <sup>2</sup> C, SPI, UART/USART |

| Peripherals                | DMA, LVD, POR, PWM, WDT                                      |

| Number of I/O              | 150                                                          |

| Program Memory Size        | -                                                            |

| Program Memory Type        | ROMIess                                                      |

| EEPROM Size                | -                                                            |

| RAM Size                   | 64K x 8                                                      |

| Voltage - Supply (Vcc/Vdd) | 2.7V ~ 3.6V                                                  |

| Data Converters            | A/D 8x10b                                                    |

| Oscillator Type            | External                                                     |

| Operating Temperature      | -40°C ~ 85°C (TA)                                            |

| Mounting Type              | Surface Mount                                                |

| Package / Case             | 256-LBGA                                                     |

| Supplier Device Package    | 256-MAPBGA (17x17)                                           |

| Purchase URL               | https://www.e-xfl.com/pro/item?MUrl=&PartUrl=mcf5280cvf66j   |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

byte, word, longword or 16-byte burst line transfers. These transfers are triggered by software, explicitly setting a DCR*n*[START] bit or the occurrence of a hardware event from one of the on-chip peripheral devices, such as a capture event or an output reference event in a DMA timer (DTIM*n*) for each channel. The DMA controller supports dual-address mode to on-chip devices.

## 1.1.17 Reset

The reset controller is provided to determine the cause of reset, assert the appropriate reset signals to the system, and keep track of what caused the last reset. The power management registers for the internal low-voltage detect (LVD) circuit are implemented in the reset module. There are seven sources of reset:

- External

- Power-on reset (POR)

- Watchdog timer

- Phase-locked loop (PLL) loss of lock

- PLL loss of clock

- Software

- Low-voltage detection (LVD) reset

External reset on the  $\overline{\text{RSTO}}$  pin is software-assertable independent of chip reset state. There are also software-readable status flags indicating the cause of the last reset, and LVD control and status bits for setup and use of LVD reset or interrupt.

# 1.2 MCF5282-Specific Features

# **1.2.1 Fast Ethernet Controller (FEC)**

The MCF5282's integrated Fast Ethernet Controller (FEC) performs the full set of IEEE 802.3/Ethernet CSMA/CD media access control and channel interface functions. The FEC supports connection and functionality for the 10/100 Mbps 802.3 media independent interface (MII). It requires an external transceiver (PHY) to complete the interface to the media.

### NOTE

The MCF5214 and MCF5216 devices do not contain an FEC module.

# 1.2.2 FlexCAN

The FlexCAN module is a communication controller implementing the CAN protocol. The CAN protocol can be used as an industrial control serial data bus, meeting the specific requirements of real-time processing, reliable operation in a harsh EMI environment, cost-effectiveness, and required bandwidth. FlexCAN contains 16 message buffers.

# 1.2.3 I<sup>2</sup>C Bus

The I<sup>2</sup>C bus is a two-wire, bidirectional serial bus that provides a simple, efficient method of data exchange, minimizing the interconnection between devices. This bus is suitable for applications requiring occasional communications over a short distance between many devices.

execution until all previous operations, including all pending write operations, are complete. If any previous write terminates with an access error, it is guaranteed to be reported on the NOP instruction.

## 2.3.4.2 Address Error Exception

Any attempted execution transferring control to an odd instruction address (if bit 0 of the target address is set) results in an address error exception.

Any attempted use of a word-sized index register (Xn.w) or a scale factor of eight on an indexed effective addressing mode generates an address error, as does an attempted execution of a full-format indexed addressing mode, which is defined by bit 8 of extension word 1 being set.

If an address error occurs on a JSR instruction, the Version 2 ColdFire processor calculates the target address then the return address is pushed onto the stack. If an address error occurs on an RTS instruction, the Version 2 ColdFire processor overwrites the faulting return PC with the address error stack frame.

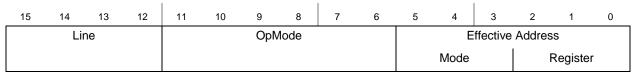

## 2.3.4.3 Illegal Instruction Exception

The ColdFire variable-length instruction set architecture supports three instruction sizes: 16, 32, or 48 bits. The first instruction word is known as the operation word (or opword), while the optional words are known as extension word 1 and extension word 2. The opword is further subdivided into three sections: the upper four bits segment the entire ISA into 16 instruction lines, the next 6 bits define the operation mode (opmode), and the low-order 6 bits define the effective address. See Figure 2-17. The opword line definition is shown in Table 2-8.

Figure 2-17. ColdFire Instruction Operation Word (Opword) Format

| Opword[Line] | Instruction Class                                                                                                     |

|--------------|-----------------------------------------------------------------------------------------------------------------------|

| 0x0          | Bit manipulation, Arithmetic and Logical Immediate                                                                    |

| 0x1          | Move Byte                                                                                                             |

| 0x2          | Move Long                                                                                                             |

| 0x3          | Move Word                                                                                                             |

| 0x4          | Miscellaneous                                                                                                         |

| 0x5          | Add (ADDQ) and Subtract Quick (SUBQ), Set according to Condition Codes (Scc)                                          |

| 0x6          | PC-relative change-of-flow instructions<br>Conditional (Bcc) and unconditional (BRA) branches, subroutine calls (BSR) |

| 0x7          | Move Quick (MOVEQ), Move with sign extension (MVS) and zero fill (MVZ)                                                |

| 0x8          | Logical OR (OR)                                                                                                       |

| 0x9          | Subtract (SUB), Subtract Extended (SUBX)                                                                              |

### Table 2-8. ColdFire Opword Line Definition

| Table 10-7. IMRLn Field Desc | riptions |

|------------------------------|----------|

|------------------------------|----------|

| Bits | Name     | Description                                                                                                                                                                                                                                                                                                                                                                                                                                   |

|------|----------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 31–1 | INT_MASK | <ul> <li>Interrupt mask. Each bit corresponds to an interrupt source. The corresponding IMRL<i>n</i> bit determines whether an interrupt condition can generate an interrupt. The corresponding IPRL<i>n</i> bit reflects the state of the interrupt signal even if the corresponding IMRL<i>n</i> bit is set.</li> <li>0 The corresponding interrupt source is not masked</li> <li>1 The corresponding interrupt source is masked</li> </ul> |

| 0    | MASKALL  | Mask all interrupts. Setting this bit will force the other 63 bits of the IMRH <i>n</i> and IMRL <i>n</i> to ones, disabling all interrupt sources, and providing a global mask-all capability.                                                                                                                                                                                                                                               |

### NOTE

If an interrupt source is being masked in the interrupt controller mask register (IMR) or a module's interrupt mask register while the interrupt mask in the status register (SR[I]) is set to a value lower than the interrupt's level, a spurious interrupt may occur. This is because by the time the status register acknowledges this interrupt, the interrupt has been masked. A spurious interrupt is generated because the CPU cannot determine the interrupt source. To avoid this situation for interrupts sources with levels 1-6, first write a higher level interrupt mask to the status register, before setting the mask in the IMR or the module's interrupt mask register to its previous value. Since level seven interrupts cannot be disabled in the status register to disable level seven interrupts is not recommended.

## 10.3.3 Interrupt Force Registers (INTFRCHn, INTFRCLn)

The INTFRCH*n* and INTFRCL*n* registers are each 32 bits in size and provide a mechanism to allow software generation of interrupts for each possible source for functional or debug purposes. The system design may reserve one or more sources to allow software to self-schedule interrupts by forcing one or more of these bits (1 = force request, 0 = negate request) in the appropriate INTFRC*n* register. The assertion of an interrupt request via the INTFRC*n* register is not affected by the interrupt mask register. The INTFRC*n* register is cleared by reset.

| Processor<br>Pins | A15 | A14 | A13 | A12 | A11 | A10 | A9 | A17 | A19 | A21 | A23 |

|-------------------|-----|-----|-----|-----|-----|-----|----|-----|-----|-----|-----|

| Row               | 15  | 14  | 13  | 12  | 11  | 10  | 9  | 17  | 19  | 21  | 23  |

| Column            | 2   | 3   | 4   | 5   | 6   | 7   | 8  | 16  | 18  | 20  | 22  |

| SDRAM<br>Pins     | A0  | A1  | A2  | A3  | A4  | A5  | A6 | A7  | A8  | A9  | A10 |

Table 15-23. Processor to SDRAM Interface (32-Bit Port, 12-Column Address Lines)

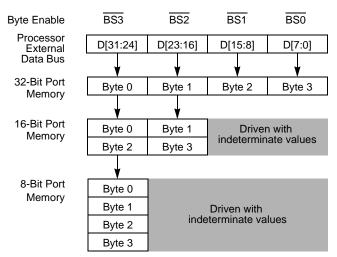

### 15.2.3.2 SDRAM Byte Strobe Connections

Figure 15-5 shows SDRAM connections for port sizes of 32, 16, or 8 bits.

Figure 15-5. Connections for External Memory Port Sizes

### 15.2.3.3 Interfacing Example

The tables in the previous section can be used to configure the interface in the following example. To interface one 2M x 32-bit x 4 bank SDRAM component (8 columns), use the connections shown in Table 15-24.

Table 15-24.

SDRAM Hardware Connections

| SDRAM Pins     | A0  | A1  | A2  | A3  | A4  | A5  | A6 | A7  | A8  | A9  | A10 = CMD | BA0 | BA1 |

|----------------|-----|-----|-----|-----|-----|-----|----|-----|-----|-----|-----------|-----|-----|

| Processor Pins | A15 | A14 | A13 | A12 | A11 | A10 | A9 | A17 | A18 | A19 | A20       | A21 | A22 |

### 15.2.3.4 Burst Page Mode

SDRAM can efficiently provide data when an SDRAM page is opened. As soon as SCAS is issued, the SDRAM accepts a new address and asserts SCAS every CLKOUT for as long as accesses occur in that page. In burst page mode, there are multiple read or write operations for every ACTV command in the SDRAM if the requested transfer size exceeds the port size of the associated SDRAM. The primary cycle of the transfer generates the ACTV and READ or WRITE commands; secondary cycles generate only READ or WRITE commands. As soon as the transfer completes, the PALL command is generated to prepare for the next access.

#### Fast Ethernet Controller (FEC)

| Signal Description              | EMAC pin     |

|---------------------------------|--------------|

| Collision                       | FEC_COL      |

| Carrier Sense                   | FEC_CRS      |

| Receive Clock                   | FEC_RXCLK    |

| Receive Data Valid              | FEC_RXDV     |

| Receive Data                    | FEC_RXD[3:0] |

| Receive Error                   | FEC_RXER     |

| Management Data Clock           | FEC_MDC      |

| Management Data<br>Input/Output | FEC_MDIO     |

The 7-wire serial mode interface (RCR[MII\_MODE] cleared) is generally referred to as AMD mode. Table 17-36 shows the 7-wire mode connections to the external transceiver.

| Signal description | EMAC Pin   |

|--------------------|------------|

| Transmit Clock     | FEC_TXCLK  |

| Transmit Enable    | FEC_TXEN   |

| Transmit Data      | FEC_TXD[0] |

| Collision          | FEC_COL    |

| Receive Clock      | FEC_RXCLK  |

| Receive Data Valid | FEC_RXDV   |

| Receive Data       | FEC_RXD[0] |

Table 17-36. 7-Wire Mode Configuration

## 17.5.7 FEC Frame Transmission

The Ethernet transmitter is designed to work with almost no intervention from software. After ECR[ETHER\_EN] is set and data appears in the transmit FIFO, the Ethernet MAC can transmit onto the network. The Ethernet controller transmits bytes least significant bit (lsb) first.

When the transmit FIFO fills to the watermark (defined by TFWR), MAC transmit logic asserts FEC\_TXEN and starts transmitting the preamble (PA) sequence, the start frame delimiter (SFD), and then the frame information from the FIFO. However, the controller defers the transmission if the network is busy (FEC\_CRS is asserted). Before transmitting, the controller waits for carrier sense to become inactive, then determines if carrier sense stays inactive for 60 bit times. If so, transmission begins after waiting an additional 36 bit times (96 bit times after carrier sense originally became inactive). See Section 17.5.15.1, "Transmission Errors," for more details.

#### General Purpose Timer Modules (GPTA and GPTB)

The PORTTn data direction register controls the data direction of an input capture pin. External pin conditions trigger input captures on input capture pins configured as inputs.

To configure a pin for input capture:

- 1. Clear the pin's IOS bit in GPTIOS.

- 2. Clear the pin's DDR bit in PORTT*n*DDR.

- 3. Write to GPTCTL2 to select the input edge to detect.

PORTT*n*DDR does not affect the data direction of an output compare pin. The output compare function overrides the data direction register but does not affect the state of the data direction register.

To configure a pin for output compare:

- 1. Set the pin's IOS bit in GPTIOS.

- 2. Write the output compare value to GPTC*n*.

- 3. Clear the pin's DDR bit in PORTT*n*DDR.

- 4. Write to the OMn/OLn bits in GPTCTL1 to select the output action.

Table 20-23 shows how various timer settings affect pin functionality.

Table 20-23. GPT Settings and Pin Functions

| GPTE<br>N | DDR <sup>1</sup> | GPTIOS         | EDGx<br>[B:A]          | OMx/<br>OLx <sup>2</sup> | OC3Mx<br>3 | Pin<br>Data<br>Dir. | Pin<br>Driven<br>by | Pin<br>Function      | Comments                                                                                               |

|-----------|------------------|----------------|------------------------|--------------------------|------------|---------------------|---------------------|----------------------|--------------------------------------------------------------------------------------------------------|

| 0         | 0                | X <sup>4</sup> | Х                      | Х                        | Х          | In                  | Ext.                | Digital input        | GPT disabled by GPTEN = 0                                                                              |

| 0         | 1                | Х              | Х                      | Х                        | Х          | Out                 | Data reg.           | Digital output       | GPT disabled by GPTEN = 0                                                                              |

| 1         | 0                | 0 (IC)         | 0 (IC<br>disable<br>d) | Х                        | 0          | In                  | Ext.                | Digital input        | Input capture disabled by EDG <i>n</i> setting                                                         |

| 1         | 1                | 0              | 0                      | Х                        | 0          | Out                 | Data reg.           | Digital output       | Input capture disabled by EDG <i>n</i> setting                                                         |

| 1         | 0                | 0              | <> 0                   | Х                        | 0          | In                  | Ext.                | IC and digital input | Normal settings for input capture                                                                      |

| 1         | 1                | 0              | <> 0                   | Х                        | 0          | Out                 | Data reg.           | Digital output       | Input capture of data driven to output pin by CPU                                                      |

| 1         | 0                | 0              | <> 0                   | Х                        | 1          | In                  | Ext.                | IC and digital input | OC3M setting has no effect because<br>IOS = 0                                                          |

| 1         | 1                | 0              | <> 0                   | Х                        | 1          | Out                 | Data reg.           | Digital output       | OC3M setting has no effect because<br>IOS = 0; input capture of data driven<br>to output pin by CPU    |

| 1         | 0                | 1 (OC)         | X <sup>(3)</sup>       | 0 <sup>5</sup>           | 0          | In                  | Ext.                | Digital input        | Output compare takes place but does not affect the pin because of the OM <i>n</i> /OL <i>n</i> setting |

| 1         | 1                | 1              | Х                      | 0                        | 0          | Out                 | Data reg.           | Digital output       | Output compare takes place but does not affect the pin because of the OM <i>n</i> /OL <i>n</i> setting |

| 1         | 0                | 1              | Х                      | <> 0                     | 0          | Out                 | OC action           | Output compare       | Pin readable only if DDR = $0^{(5)}$                                                                   |

| 1         | 1                | 1              | Х                      | <> 0                     | 0          | Out                 | OC action           | Output compare       | Pin driven by OC action <sup>(5)</sup>                                                                 |

### Table 23-8. UIPCRn Field Descriptions

| Field    | Description                                                                                                                                                                                                                                                                                                                                                                                    |

|----------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7–5      | Reserved                                                                                                                                                                                                                                                                                                                                                                                       |

| 4<br>COS | <ul> <li>Change of state (high-to-low or low-to-high transition).</li> <li>0 No change-of-state since the CPU last read UIPCR<i>n</i>. Reading UIPCR<i>n</i> clears UISR<i>n</i>[COS].</li> <li>1 A change-of-state longer than 25–50 μs occurred on the UCTS<i>n</i> input. UACR<i>n</i> can be programmed to generate an interrupt to the CPU when a change of state is detected.</li> </ul> |

| 3–1      | Reserved                                                                                                                                                                                                                                                                                                                                                                                       |

| 0<br>CTS | Current state of clear-to-send. Starting two serial clock periods after reset, CTS reflects the state of UCTSn. If         UCTSn is detected asserted at that time, COS is set, which initiates an interrupt if UACRn[IEC] is enabled.         0       The current state of the UCTSn input is asserted.         1       The current state of the UCTSn input is deasserted.                   |

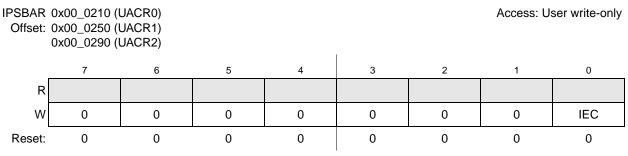

## 23.3.9 UART Auxiliary Control Register (UACR n)

The UACRs control the input enable.

### Figure 23-11. UART Auxiliary Control Registers (UACRn)

### Table 23-9. UACRn Field Descriptions

| Field    | Description                                                                                                                                                                                                                                                                                                                      |

|----------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7–1      | Reserved, must be cleared.                                                                                                                                                                                                                                                                                                       |

| 0<br>IEC | <ul> <li>Input enable control.</li> <li>0 Setting the corresponding UIPCR<i>n</i> bit has no effect on UISR<i>n</i>[COS].</li> <li>1 <u>UISR<i>n</i>[COS]</u> is set and an interrupt is generated when the UIPCR<i>n</i>[COS] is set by an external transition on the UCTS<i>n</i> input (if UIMR<i>n</i>[COS] = 1).</li> </ul> |

## 23.3.10 UART Interrupt Status/Mask Registers (UISR n/UIMR n)

The UISRs provide status for all potential interrupt sources. UISR*n* contents are masked by UIMR*n*. If corresponding UISR*n* and UIMR*n* bits are set, internal interrupt output is asserted. If a UIMR*n* bit is cleared, state of the corresponding UISR*n* bit has no effect on the output.

The UISR*n* and UIMR*n* registers share the same space in memory. Reading this register provides the user with interrupt status, while writing controls the mask bits.

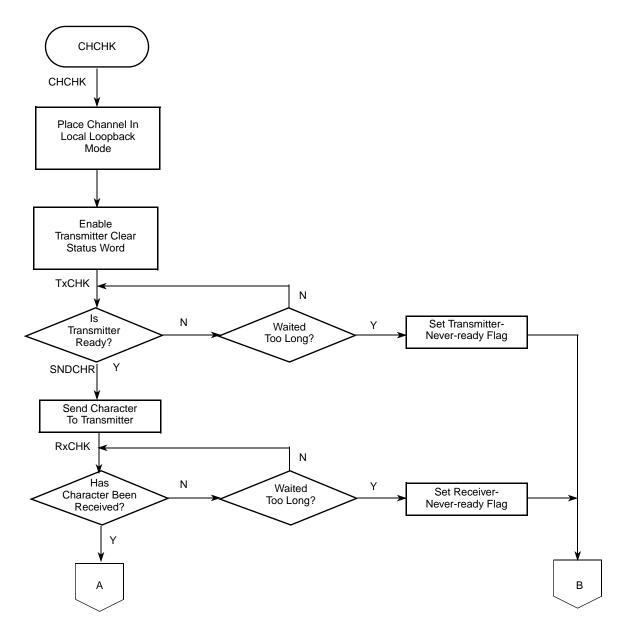

Figure 23-25. UART Mode Programming Flowchart (Sheet 2 of 5)

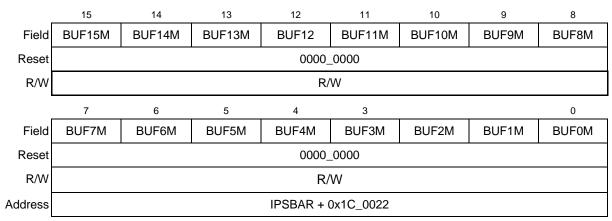

The interrupt mask register contains two 8-bit fields: bits 15-8 (IMASK\_H) and bits 7-0 (IMASK\_L). The register can be accessed by the master as a 16-bit register, or each byte can be accessed individually using an 8-bit (byte) access cycle.

Figure 25-14. Interrupt Mask Register (IMASK)

Table 25-18 describes the IMASK fields.

Table 25-18. IMASK Field Descriptions

| Bits | Name              | Description                                                                                                                                                                                                                                                                                                           |

|------|-------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 15–0 | BUF <i>n</i><br>M | <ul><li>IMASK contains one interrupt mask bit per buffer. It allows the CPU to designate which buffers will generate interrupts after successful transmission/reception.</li><li>0 The interrupt for the corresponding buffer is disabled.</li><li>1 The interrupt for the corresponding buffer is enabled.</li></ul> |

# 25.5.10 Interrupt Flag Register (IFLAG)

IFLAG contains one interrupt flag bit per buffer. Each successful transmission/reception sets the corresponding IFLAG bit and, if the corresponding IMASK bit is set, will generate an interrupt.

This register contains two 8-bit fields: bits 15-8 (IFLAG\_H) and bits 7-0 (IFLAG\_L). The register can be accessed by the master as a 16-bit register, or each byte can be accessed individually using an 8-bit (byte) access cycle.

## 26.3.2.6 Port E Pin Assignment Register (PEPAR)

The PEPAR controls the pin function of port E.

The PEPAR register is read/write.

| _       | 15                 | 14         | 13 | 12         | 11  | 10         | 9 | 8          |

|---------|--------------------|------------|----|------------|-----|------------|---|------------|

| Field   | _                  | PEPA7      | _  | PEPA6      | _   | PEPA5      | _ | PEPA4      |

| Reset   | 0                  | See Note 1 | 0  | See Note 1 | 0   | See Note 1 | 0 | See Note 1 |

| R/W:    | R                  | R/W        | R  | R/W        | R   | R/W        | R | R/W        |

|         |                    |            |    |            |     |            |   |            |

|         | 7                  | 6          | 5  | 4          | 3   | 2          | 1 | 0          |

| Field   |                    | PEPA3      | —  | PEPA2      | PE  | PEPA1      |   | PA0        |

| Reset   | 0                  | See Note 1 | 0  | See Note 1 | See | See Note 1 |   | Note 1     |

| R/W:    | R                  | R/W        | R  | R/W        | F   | R/W        | R | /W         |

| Address | IPSBAR + 0x10_0052 |            |    |            |     |            |   |            |

|         |                    |            |    |            |     |            |   |            |

### Figure 26-20. Port E Pin Assignment Register (PEPAR)

<sup>1</sup> Reset state determined during reset configuration as shown in Table 26-10.

| Table 26-9 | . PEPAR | Field | Descriptions |

|------------|---------|-------|--------------|

|------------|---------|-------|--------------|

| Bits | Name  | Description                                                                                                                                                                                                                                      |

|------|-------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 14   | PEPA7 | Port E pin assignment 7.<br>This bit configures the port E7 pin for its primary function ( $\overline{OE}$ ) or<br>digital I/O.<br>1 Port E7 pin configured for primary function ( $\overline{OE}$ )<br>0 Port E7 pin configured for digital I/O |

| 12   | PEPA6 | Port E pin assignment 6.<br>This bit configures the port E6 pin for its primary function (TA) or<br>digital I/O.<br>1 Port E6 pin configured for primary function (TA)<br>0 Port E6 pin configured for digital I/O                               |

| 10   | PEPA5 | Port E pin assignment 5.<br>This bit configures the port E5 pin for its primary function (TEA) or<br>digital I/O.<br>1 Port E5 pin configured for primary function (TEA)<br>0 Port E5 pin configured for digital I/O                             |

| 8    | PEPA4 | Port E pin assignment 4.<br>This bit configures the port E4 pin for its primary function (R/W) or<br>digital I/O.<br>1 Port E4 pin configured for primary function (R/W)<br>0 Port E4 pin configured for digital I/O                             |

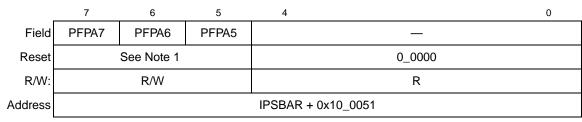

## 26.3.2.7 Port F Pin Assignment Register (PFPAR)

The PFPAR controls the pin function of port F[7:5].

### Figure 26-21. Port F Pin Assignment Register (PFPAR)

<sup>1</sup> Reset state determined during reset configuration. PFPAn = 1 in master mode and 0 in all other modes.

| Bits | Name  | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

|------|-------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7    | PFPA7 | <ul> <li>Port F pin assignment 1. The PFPA7 bit configures the port F7 pin for its primary function (A23), alternate function (CS6), or digital I/O.</li> <li>1 Port F7 pin configured for primary function (A23) or alternate function (CS6), depending on the chip configuration.</li> <li>0 Port F7 pin configured for digital I/O</li> <li>Refer to Chapter 27, "Chip Configuration Module (CCM)" for more information on reset configuration.</li> </ul>                                             |

| 6    | PFPA6 | <ul> <li>Port F pin assignment 6. The PFPA6 bit configures the port F6 pin for its primary function (A22), alternate function (CS5), or digital I/O.</li> <li>Port F6 pin configured for primary function (A22) or alternate function (CS5), depending on the chip configuration.</li> <li>Port F6 pin configured for digital I/O</li> <li>Port F6 pin configured for digital I/O</li> <li>Refer to Chapter 27, "Chip Configuration Module (CCM)" for more information on reset configuration.</li> </ul> |

| 5    | PFPA5 | <ul> <li>Port F pin assignment 5. The PFPAR bit configures the port F5 pin for its primary function (A21), alternate function (CS4), or digital I/O.</li> <li>1 Port F5 pin configured for primary function (A21) or alternate function (CS4), depending on the chip configuration.</li> <li>0 Port F5 pin configured for digital I/O</li> <li>Refer to Chapter 27, "Chip Configuration Module (CCM)" for more information on reset configuration.</li> </ul>                                             |

| 4–0  | _     | Reserved, should be cleared.                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

#### Table 26-11. PFPAR Field Descriptions

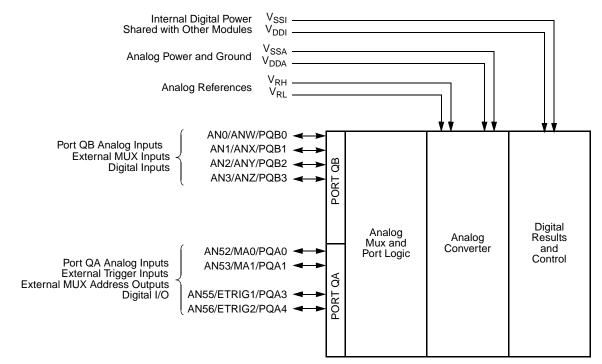

## 28.4.1.1 Port QA Analog Input Signals

When used as analog inputs, the four port QA signals are referred to as AN[56:55, 53:52].

Figure 28-2. QADC Input and Output Signals

### 28.4.1.2 Port QA Digital Input/Output Signals

Port QA signals are referred to as PQA[4:3, 1:0] when used as a bidirectional 4-bit digital input/output port. These four signals may be used for general-purpose digital input or digital output.

Port QA signals are connected to a digital input synchronizer during reads and may be used as general-purpose digital inputs when the applied voltages meet high-voltage input ( $V_{II}$ ) and low-voltage input ( $V_{II}$ ) requirements.

Each port QA signal is configured as an input or output by programming the port data direction register (DDRQA). The digital input signal states are read from the port QA data register (PORTQA) when DDRQA specifies that the signals are inputs. The digital data in PORTQA is driven onto the port QA signals when the corresponding bits in DDRQA specify output. See Section 28.6.4, "Port QA and QB Data Direction Register (DDRQA & DDRQB).

## 28.4.2 Port QB Signal Functions

The four port QB signals can be used as analog inputs or as a 4-bit digital I/O port.

## 28.4.2.1 Port QB Analog Input Signals

When used as analog inputs, the four port QB signals are referred to as AN[3:0].

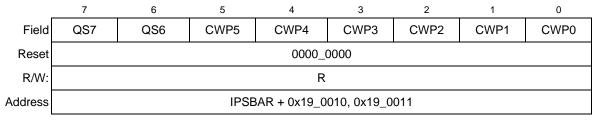

### Figure 28-11. QADC Status Register 0 (QASR0)

### Table 28-10. QASR0 Field Descriptions

| Bit(s) | Name | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

|--------|------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 15, 13 | CFn  | Queue completion flag. Indicates that a queue scan has been completed. CF[1:2] is<br>set by the QADC when the input channel sample requested by the last CCW in the<br>queue is converted, and the result is stored in the result table.<br>When CF <i>n</i> is set and queue completion interrupts are enabled (QACR <i>n</i> [CIE <i>n</i> ] = 1),<br>the QADC requests an interrupt. The interrupt request is cleared when a 0 is written<br>to the CF1 bit after it has been read as a 1. Once set, CF1 can be cleared only by a<br>reset or by writing a 0 to it.<br>CF[1:2] is updated by the QADC regardless of whether the corresponding interrupt is<br>enabled. This allows polled recognition of the queue scan completion.                                                                                                                                                                                                                             |

| 14, 12 | PFn  | <ul> <li>Queue pause flag. Indicates that a queue scan has reached a pause. PF[1:2] is set by the QADC when the current queue 1 CCW has the pause bit set, the selected input channel has been converted, and the result has been stored in the result table. When PF<i>n</i> is set and interrupts are enabled (QACR<i>n</i>[PIE<i>n</i>] = 1), the QADC requests an interrupt. The interrupt request is cleared when a 0 is written to PF<i>n</i>, after it has been read as a 1. Once set, PF<i>n</i> can be cleared only by reset or by writing a 0 to it. PF1:</li> <li>1 Queue 1 has reached a pause or gate closed before end-of-queue in gated mode.</li> <li>0 Queue 1 has not reached a pause or gate has not closed before end-of-queue in gated mode.</li> <li>PF2:</li> <li>1 Queue 2 has reached a pause.</li> <li>0 Queue 2 has not reached a pause.</li> <li>See Table 28-11 for a summary of CCW pause bit response in all scan modes.</li> </ul> |

| 11–10  | TORn | <ul> <li>Queue trigger overrun flag. Indicates that an unexpected trigger event has occurred for queue 1. TOR[1:2] can be set only while the queue is in the active state.</li> <li>Once set, TOR[1:2] is cleared only by a reset or by writing a 0 to it.</li> <li>1 At least one unexpected queue 1 trigger event has occurred or queue 1 reaches an end-of-queue condition for the second time in externally gated continuous scan.</li> <li>0 No unexpected queue 1 trigger events have occurred.</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| IST[1:0] | Input Sample Times                   |

|----------|--------------------------------------|

| 00       | Input sample time = QCLK period × 2  |

| 01       | Input sample time = QCLK period × 4  |

| 10       | Input sample time = QCLK period × 8  |

| 11       | Input sample time = QCLK period × 16 |

#### Table 28-15. Input Sample Times

#### Table 28-16. Non-Multiplexed Channel Assignments and Signal Designations

| Non-Multiplexed Input Signals      |                                      |                                                 |                                  |                                      | Channel Number <sup>1</sup><br>in CCW CHAN Field |  |  |

|------------------------------------|--------------------------------------|-------------------------------------------------|----------------------------------|--------------------------------------|--------------------------------------------------|--|--|

| Port Signal Name                   | Analog Signal Name                   | Other<br>Functions                              | Signal Type                      | Binary                               | Decimal                                          |  |  |

| PQB0<br>PQB1<br>PQB2<br>PQB3       | ANO<br>AN1<br>AN2<br>AN3             |                                                 | Input<br>Input<br>Input<br>Input | 000000<br>000001<br>000010<br>000011 | 0<br>1<br>2<br>3                                 |  |  |

| PQA0<br>PQA1                       | AN52<br>AN53                         | —                                               | Input/Output<br>Input/Output     | 110100<br>110101                     | 52<br>53                                         |  |  |

| PQA3<br>PQA4                       | AN55<br>AN56                         | ETRIG1<br>ETRIG2                                | Input/Output<br>Input/Output     | 110111<br>111000                     | 55<br>56                                         |  |  |

| V <sub>RL</sub><br>V <sub>RH</sub> | Low reference<br>High reference<br>— | —<br>—<br>(V <sub>RH</sub> –V <sub>RL</sub> )/2 | Input<br>Input<br>—              | 111100<br>111101<br>111110           | 60<br>61<br>62                                   |  |  |

| —                                  |                                      | End-of-Queue Code                               | —                                | 111111                               | 63                                               |  |  |

<sup>1</sup> All channels not listed are reserved or unimplemented and return undefined results.

### Table 28-17. Multiplexed Channel Assignments and Signal Designations

|                                    | Multi                                | Channel Number <sup>1</sup><br>in CCW CHAN Field |                                  |                                      |                                                              |

|------------------------------------|--------------------------------------|--------------------------------------------------|----------------------------------|--------------------------------------|--------------------------------------------------------------|

| Port Signal<br>Name                | Analog<br>Signal Name                | Other<br>Functions                               | Signal Type                      | Binary                               | Decimal                                                      |

| PQB0<br>PQB1<br>PQB2<br>PQB3       | ANW<br>ANX<br>ANY<br>ANZ             | <br>                                             | Input<br>Input<br>Input<br>Input | 000XX0<br>000XX1<br>010XX0<br>010XX1 | 0, 2, 4, 6<br>1, 3, 5, 7<br>16, 18, 20, 22<br>17, 19, 21, 23 |

| PQA0<br>PQA1                       |                                      | MA0<br>MA1                                       | Output<br>Output                 | _                                    | 52<br>53                                                     |

| PQA3<br>PQA4                       | AN55<br>AN56                         | ETRIG1<br>ETRIG2                                 | Input/Output<br>Input/Output     | 110111<br>111000                     | 55<br>56                                                     |

| V <sub>RL</sub><br>V <sub>RH</sub> | Low Reference<br>High Reference<br>— | <br>                                             | Input<br>Input<br>—              | 111100<br>111101<br>111110           | 60<br>61<br>62                                               |

|                                    | —                                    | End-of-Queue Code                                | —                                | 111111                               | 63                                                           |

Queued Analog-to-Digital Converter (QADC)

Figure 28-31. CCW Priority Situation 9

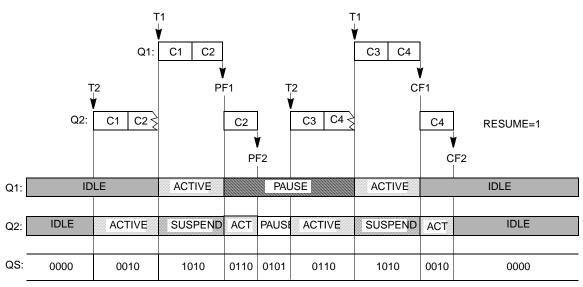

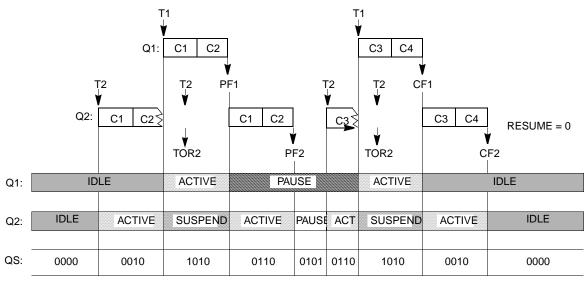

Situations S10 and S11 (Figure 28-32 and Figure 28-33) show that when an additional trigger event is detected for queue 2 while the queue is suspended, the trigger overrun error bit is set, the same as if queue 2 were being executed when a new trigger event occurs. Trigger overrun on queue 2 thus allows the user to know that queue 1 is taking up so much QADC time that queue 2 trigger events are being lost.

Figure 28-32. CCW Priority Situation 10

**Electrical Characteristics**

| Characteristic                                                                                                                                                  | Symbol            | Min        | Max        | Unit |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------|------------|------------|------|

| Load Capacitance <sup>3</sup><br>(50% Partial Drive)<br>(100% Full Drive)                                                                                       | CL                |            | 25<br>50   | pF   |

| Supply Voltage (includes core modules and pads)                                                                                                                 | V <sub>DD</sub>   | 2.7        | 3.6        | V    |

| RAM Memory Standby Supply Voltage<br>Normal Operation: V <sub>DD</sub> > V <sub>STBY</sub> - 0.3 V<br>Standby Mode: V <sub>DD</sub> < V <sub>STBY</sub> - 0.3 V | V <sub>STBY</sub> | 0.0<br>1.8 | 3.6<br>3.6 | V    |

| Flash Memory Supply Voltage<br>(not applicable to MCF5280)                                                                                                      | V <sub>DDF</sub>  | 2.7        | 3.6        | V    |

| Table 33-3. DC Electrical Specifications <sup>1</sup> (continued) |

|-------------------------------------------------------------------|

| $(V_{SS} = V_{SSPLL} = V_{SSF} = V_{SSA} = 0 V_{DC})$             |

<sup>1</sup> Refer to Table 33-8 through Table 33-12 for additional PLL, QADC, and Flash specifications.

<sup>2</sup> This parameter is characterized before qualification rather than 100% tested.

<sup>3</sup> Refer to the chip configuration section for more information. Drivers for the SDRAM pins are at 25pF drive strength.Drivers for the QADC pins are at 50pF drive strength.

# 33.4 Power Consumption Specifications

| Characteristic                                                  | Symbol          | Typical–<br>Master Mode | Typical–<br>Single Chip<br>Mode <sup>1</sup> | Max <sup>2</sup> | Unit |

|-----------------------------------------------------------------|-----------------|-------------------------|----------------------------------------------|------------------|------|

| System clocks disabled (LPCR[STPMD] = 00)                       | I <sub>DD</sub> | 25                      | 7.9                                          | —                | mA   |

| System clocks and CLKOUT disabled (LPCR[STPMD] = 01)            | I <sub>DD</sub> | 7.3                     | 5.6                                          | _                | mA   |

| System clocks, CLKOUT, and PLL disabled (LPCR[STPMD] = 10)      | I <sub>DD</sub> | 4.5                     | 4.7                                          | —                | mA   |

| System clocks, CLKOUT, PLL, and OSC disabled (LPCR[STPMD] = 11) | I <sub>DD</sub> | 400                     | 750                                          | 1000             | μA   |

Single chip mode current measured with all pins in general purpose input mode except for the UART0 and FEC pins that are enabled for their module functionality.

<sup>2</sup> Maximum values can vary depending on the system's state and signal loading.

Figure 33-1 shows typical WAIT/DOZE and RUN mode power consumption for both master and single chip mode as measured on an M5282EVB.

For master mode the RUN mode current was measured executing a continuous loop that performs no operation while running from the on-chip SRAM.

For WAIT/DOZE mode measurements the peripherals on the device are in their default power savings mode, so the WAIT and DOZE power consumption are the same. Some modules can be programmed to shutdown in WAIT and/or DOZE modes. Refer to module chapters for more information.

All single chip mode measurements were taken with all pins in general purpose input mode except for the UARTO and FEC pins that are enabled for their module functionality; however, neither module is being accessed at the time of the current measurement. Single chip RUN mode current was measured executing a continuous loop that performs no operation while running from the on-chip Flash.

| Address                | Name                                                | Mnemonic | Size |  |  |  |

|------------------------|-----------------------------------------------------|----------|------|--|--|--|

| IPSBAR + 0xCEC         | Level 3 Interrupt Acknowledge Register 0            | L3IACKR0 | 8    |  |  |  |

| IPSBAR + 0xCF0         | Level 4 Interrupt Acknowledge Register 0            | L4IACKR0 | 8    |  |  |  |

| IPSBAR + 0xCF4         | Level 5 Interrupt Acknowledge Register 0            | L5IACKR0 | 8    |  |  |  |

| IPSBAR + 0xCF8         | Level 6 Interrupt Acknowledge Register 0            | L6IACKR0 | 8    |  |  |  |

| IPSBAR + 0xCFC         | Level 7 Interrupt Acknowledge Register 0            | L7IACKR0 | 8    |  |  |  |

| Interrupt Controller 1 |                                                     |          |      |  |  |  |

| IPSBAR + 0xD00         | Interrupt Pending Register High 1                   | IPRH1    | 32   |  |  |  |

| IPSBAR + 0xD04         | Interrupt Pending Register Low 1                    | IPRL1    | 32   |  |  |  |

| IPSBAR + 0xD08         | Interrupt Mask Register High 1                      | IMRH1    | 32   |  |  |  |

| IPSBAR + 0xD0C         | Interrupt Mask Register Low 1                       | IMRL1    | 32   |  |  |  |

| IPSBAR + 0xD10         | Interrupt Force Register High 1                     | INTFRCH1 | 32   |  |  |  |

| IPSBAR + 0xD14         | Interrupt Force Register Low 1                      | INTFRCL1 | 32   |  |  |  |

| IPSBAR + 0xD18         | Interrupt Level Request Register 1                  | ILRR1    | 8    |  |  |  |

| IPSBAR + 0xD19         | Interrupt Acknowledge Level and Priority Register 1 | IACKLPR1 | 8    |  |  |  |

| IPSBAR + 0xD48         | Interrupt Control Register 1-08                     | ICR108   | 8    |  |  |  |

| IPSBAR + 0xD49         | Interrupt Control Register 1-09                     | ICR109   | 8    |  |  |  |

| IPSBAR + 0xD4A         | Interrupt Control Register 1-10                     | ICR110   | 8    |  |  |  |

| IPSBAR + 0xD4B         | Interrupt Control Register 1-11                     | ICR111   | 8    |  |  |  |

| IPSBAR + 0xD4C         | Interrupt Control Register 1-12                     | ICR112   | 8    |  |  |  |

| IPSBAR + 0xD4D         | Interrupt Control Register 1-13                     | ICR113   | 8    |  |  |  |

| IPSBAR + 0xD4E         | Interrupt Control Register 1-14                     | ICR114   | 8    |  |  |  |

| IPSBAR + 0xD4F         | Interrupt Control Register 1-15                     | ICR115   | 8    |  |  |  |

| IPSBAR + 0xD50         | Interrupt Control Register 1-16                     | ICR116   | 8    |  |  |  |

| IPSBAR + 0xD51         | Interrupt Control Register 1-17                     | ICR117   | 8    |  |  |  |

| IPSBAR + 0xD52         | Interrupt Control Register 1-18                     | ICR118   | 8    |  |  |  |

| IPSBAR + 0xD53         | Interrupt Control Register 1-19                     | ICR119   | 8    |  |  |  |

| IPSBAR + 0xD54         | Interrupt Control Register 1-20                     | ICR120   | 8    |  |  |  |

| IPSBAR + 0xD55         | Interrupt Control Register 1-21                     | ICR121   | 8    |  |  |  |

| IPSBAR + 0xD56         | Interrupt Control Register 1-22                     | ICR122   | 8    |  |  |  |

| IPSBAR + 0xD57         | Interrupt Control Register 1-23                     | ICR123   | 8    |  |  |  |

| IPSBAR + 0xD58         | Interrupt Control Register 1-24                     | ICR124   | 8    |  |  |  |

| IPSBAR + 0xD59         | Interrupt Control Register 1-25                     | ICR125   | 8    |  |  |  |

### Table A-3. Register Memory Map (continued)

Exceptions access error 2-18 divide-by-zero 2-20 exception stack frame 2-17 format error 2-21 illegal instruction 2-19 overview 2-15 privilege violation 2-20 reset 2-22 trace 2-20 TRAP instruction 2-22 External interface module (EIM), *see*bus EXTEST instruction 31-7

#### F

Fault confinement state (FCS) 25-27 Fault-on-fault 2-22 Fault-on-fault halt 30-17 FEC, see Ethernet Flash, see ColdFire Flash module FlexCAN bit timing 25-12 CAN system overview 25-4 error counters 25-13 features 25-1 format frames 25-5-25-7 IDLE bit 25-27 initialization sequence 25-14 interrupts 25-17 memory map 25-2 message buffers BUSY 25-6 **EMPTY 25-6** FULL 25-6 handling 25-10 locking and releasing 25-11 receive deactivation 25-10 serial message buffers 25-10 transmit deactivation 25-10 NOT ACTIVE 25-6 overload frames 25-12 **OVERRUN 25-6** receive codes 25-6 error status flag (RXWARN) 25-27 pin configuration control (RXMODE) 25-20 remote frames 25-11 self-received frames 25-10 status 25-27 structure 25-4 time stamp 25-12 transmit

codes 25-6 error status flag (TXWARN) 25-26 length 25-6 pin configuration control (TXMODE) 25-20 NOTRDY bit 25-17 operation auto power save mode 25-17 bit timing configuration 25-13 debug mode 25-15 listen-only mode 25-12 low-power modes 7-11, 25-15 overview 25-1 receive process 25-9 registers bit timing 25-12 control 0-2 (CANCTRLn) 25-20-25-22 error and status (ESTAT) 25-25 free running timer (TIMER) 25-23 interrupt flag (IFLAG) 25-28 interrupt mask (IMASK) 25-27 module configuration (CANMCR) 25-18 prescaler divide (PRESDIV) 25-22 receive error counter (RXECTR) 25-29 receive mask (RXGMASK, RXnMASK) 25-24 transmit error counter (TXECTR) 25-30 SAMP bit 25-21 transmit process 25-8 Frame reception, FlexCAN 25-9 Frame transmission, FlexCAN 25-8

### G

General purpose timers block diagram 20-2 features 20-1 functional description 20-17 GPIO ports 20-19 input capture 20-17 interrupts channel flags 20-21 pulse accumulator input 20-22 pulse accumulator overflow 20-22 timer overflow 20-22 low-power modes 7-11 memory map 20-4 operation event counter mode 20-18 gated time accumulation mode 20-19 low-power modes 20-3 output compare 20-18 prescaler 20-17 pulse accumulator event counter mode 20-18

test data input/development serial input (TDI/DSI) 31-3 test data output/development serial output (TDO/DSO) 31-4 test mode select/breakpoint (TMS/BKPT) 31-3 test reset/development serial clock (TRST/DSCLK) 31-3 overview 14-1 power and reference V<sub>DD</sub> 14-32 V<sub>DDA</sub>, V<sub>SSA</sub> 14-32 V<sub>DDF</sub>, V<sub>SSF</sub> 14-32 V<sub>DDH</sub> 14-32 V<sub>DDPLL</sub>, V<sub>SSPLL</sub> 14-32 V<sub>PP</sub> 14-32 V<sub>RH</sub>, <sub>VRL</sub> 14-32 V<sub>SS</sub> 14-32 V<sub>STBY</sub> 14-32 QADC analog input (ANn/ANx) 14-28-14-29 analog power (V<sub>DDA</sub>, V<sub>SSA</sub>) 28-56 analog reference (V<sub>RH</sub>, V<sub>RL</sub>) 28-56 dedicated digital I/O port supply (V<sub>DDH</sub>) 28-6 external trigger input (ETRIG2-1) 28-5 multiplexed address output (MA1-0) 28-5 multiplexed analog input (ANx) 28-5 port QA analog input (AN56-55, 53-52) 28-4 port QA digital input/output (PQA4-3, 1-0) 28-4 port QB analog input (AN3-0) 28-4 port QB digital I/O (PQB3-0) 28-5 **QSPI** chip select (QSPI\_CS3-0) 14-25 serial clock (QSPI\_CLK) 14-25 summary 22-2 synchronous serial data input (QSPI\_DIN) 14-25 synchronous serial data output (QSPI\_DOUT) 14-25 reset controller reset in (RSTI) 14-22, 29-2 reset out (RSTO) 29-2 SDRAM controller bank select (SDRAM\_CS1-0) 14-21 clock enable (SCKE) 14-22 column address strobe (SCAS) 14-21 row address strobe (SRAS) 14-21 summary 15-4 write enable (DRAMW) 14-21 single-chip mode 14-17 TEST 14-31 UART modules clear-to-send (UCTS1-0) 14-26 receive serial data input (URXD2-0) 14-26 request-to-send (URTS1-0) 14-27 transmit serial data output (UTXD2-0) 14-26

cache, interaction 4-7 features 5-1 initialization 5-3 operation low-power modes 7-6 overview 5-1 power management 5-4 programming model 5-1 timing diagrams bus cycle terminated by  $\overline{TA}$  33-15 bus cycle terminated by  $\overline{\text{TEA}}$  33-16 Stack pointer 2-5 Stack pointer registers BDM accesses 30-33 Start-of-frame (SOF) 25-13 STOP instruction 30-4, 30-17 Stop mode 7-6 STUFFERR 25-26 System clock generation 9-11 modes 9-10

### Т

TAP controller 31-6 **TEST\_LEAKAGE 31-8** Time quanta clock 25-12 Time stamp 25-6, 25-12 Timer overflow interrupt 20-22 Timers DTIM capture mode 21-8 code example 21-9 operation general 21-9 output mode 21-9 prescaler 21-8 reference compare 21-8 registers capture (DTCRn) 21-7 counters (DTCNn) 21-8 event (DTERn) 21-5 mode (DTMRn) 21-3 reference (DTRRn) 21-7 time-out values 21-10 general purpose, see general purpose timers PIT block diagram 19-1 interrupts 19-7 memory map 19-2 operation free-running 19-6 low-power modes 19-1

#### SRAM

set-and-forget 19-6 registers control and status (PCSR) 19-3 count (PCNTR) 19-5 modulus (PMR) 19-5 timeout 19-7 watchdog, see watchdog timer 18-2 Timing diagrams debug BDM serial port AC timing 33-28 real-time trace AC timing 33-28 Ethernet MII async input signal 33-23 general input timing requirements 33-12 GPIO 33-19 digital input 26-28 digital output 26-28  $I^2C$ input/output timing 33-21 JTAG BKPT timing 33-27 boundary scan 33-26 test access port 33-26 test clock input timing 33-26 TRST timing 33-27 OADC bypass mode conversion timing 28-33 conversion in external positive edge trigger mode 28-59 conversion in gated mode, continuous scan 28-60 conversion in gated mode, single scan 28-60 conversion timing 28-33 QSPI timing 33-25 reset controller RSTI and configuration override timing 33-20 SDRAM controller read cycle 33-17 write cycle 33-18 SRAM bus cycle terminated by  $\overline{TA}$  33-15 bus cycle terminated by  $\overline{\text{TEA}}$  33-16 Transmit bit error (BITERR) 25-26

### U

UART modules clock select registers (UCSR*n*) 23-9 clock source baud rates 23-17 divider 23-17 external 23-18 command registers (UCR*n*) 23-9 core interrupts 23-26 DMA service 23-27 FIFO stack 23-21 initialization 23-29 input port change (UIPCRn) 23-12 memory map 23-3 operation looping modes automatic echo 23-23 local loop-back 23-23 remote loop-back 23-23 low-power modes 7-8 multidrop mode 23-24 receiver 23-20 transmitter 23-18 registers auxiliary control (UACRn) 23-13 baud rate generator (UBG1n/UBG2n) 23-15 input port (UIPn) 23-15 interrupt status/mask (UISRn/UIMRn) 23-13 mode 1 (UMR1n) 23-5 mode 2 (UMR2n) 23-6 output port command (UOP1n/UOP0n) 23-16 receive buffers (URBn) 23-11 status (USRn) 23-8 transmit buffers (UTBn) 23-12

### V

Variant address 30-4

### W

Wait mode 7-6 Wake interrupt (WAKEINT) 25-16, 25-27 Watchdog timer block diagram 18-2 memory map 18-2 operation low-power 7-10, 18-1 overview 18-1 registers control (WCR) 18-3 count (WCNTR) 18-5 modulus (WMR) 18-4 service (WSR) 18-5 WDDATA execution 30-3