#### Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                                       |

|----------------------------|------------------------------------------------------------------------------|

| Core Processor             | ARM® Cortex®-M0+                                                             |

| Core Size                  | 32-Bit Single-Core                                                           |

| Speed                      | 40MHz                                                                        |

| Connectivity               | CSIO, I <sup>2</sup> C, LINbus, UART/USART, USB                              |

| Peripherals                | LVD, POR, PWM, WDT                                                           |

| Number of I/O              | 24                                                                           |

| Program Memory Size        | 64KB (64K x 8)                                                               |

| Program Memory Type        | FLASH                                                                        |

| EEPROM Size                | -                                                                            |

| RAM Size                   | 12K x 8                                                                      |

| Voltage - Supply (Vcc/Vdd) | 1.65V ~ 3.6V                                                                 |

| Data Converters            | A/D 6x12b                                                                    |

| Oscillator Type            | Internal                                                                     |

| Operating Temperature      | -40°C ~ 105°C (TA)                                                           |

| Mounting Type              | Surface Mount                                                                |

| Package / Case             | 32-WFQFN Exposed Pad                                                         |

| Supplier Device Package    | 32-QFN (5x5)                                                                 |

| Purchase URL               | https://www.e-xfl.com/product-detail/infineon-technologies/s6e1c31b0agn20000 |

|                            |                                                                              |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# FM0+ S6E1C Series

# **Table of Contents**

| Features                                 | 1       |

|------------------------------------------|---------|

| 1. Block Diagram                         | 4       |

| 2. Product Lineup                        | 5       |

| 2.1 Package Dependent Features           | 6       |

| 2.2 Packages                             | 6       |

| 3. Product Features in Detail            | 7       |

| 4. Pin Assignment                        |         |

| 5. List of Pin Functions                 |         |

| 6. I/O Circuit Type                      |         |

| 7. Handling Precautions                  |         |

| 7.1 Precautions for Product Design       |         |

| 7.2 Precautions for Package Mountin      | ng31    |

| 7.3 Precautions for Use Environmen       | t33     |

| 8. Handling Devices                      |         |

| 9. Memory Map                            |         |

| 10. Pin Status in Each CPU State         |         |

| 11. Electrical Characteristics           |         |

| 11.1 Absolute Maximum Ratings            |         |

| 11.2 Recommended Operating Condi         | tions44 |

| 11.3 DC Characteristics                  |         |

| 11.3.1 Current Rating                    |         |

| 11.3.3 Pin Characteristics               |         |

| 11.4 AC Characteristics                  | 51      |

| 11.4.1 Main Clock Input Characteristics. | 51      |

| 11.4.2 Sub Clock Input Characteristics   |         |

|                                          |         |

| 11.4.3 Built-in CR Oscillation Characteristics          | .53 |

|---------------------------------------------------------|-----|

| 11.4.4 Operating Conditions of Main PLL (In the Case of |     |

| Using the Main Clock as the Input Clock of              |     |

| the PLL)                                                | .54 |

| 11.4.5 Operating Conditions of Main PLL (In the Case of |     |

| Using the Built-in High-Speed CR Clock as the Inpu      | ıt  |

| Clock of the Main PLL)                                  | .54 |

| 11.4.6 Reset Input Characteristics                      | .55 |

| 11.4.7 Power-on Reset Timing                            | .55 |

| 11.4.8 Base Timer Input Timing                          | .56 |

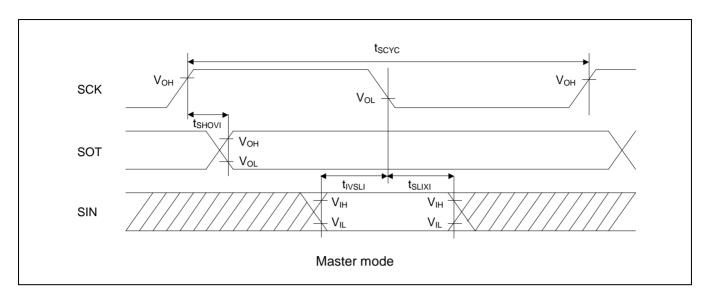

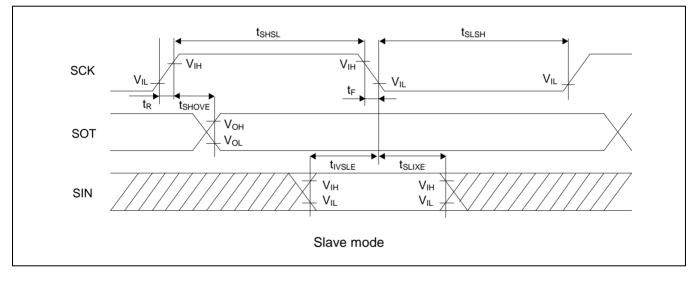

| 11.4.9 CSIO/SPI/UART Timing                             | .57 |

| 11.4.10 External Input Timing                           |     |

| 11.4.11 I <sup>2</sup> C Timing / I2C Slave Timing      | .75 |

| 11.4.12 I <sup>2</sup> S Timing (MFS-I2S Timing)        | .76 |

| 11.4.13 Smart Card Interface Characteristics            | .78 |

| 11.4.14 SW-DP Timing                                    | .79 |

| 11.5 12-bit A/D Converter                               | .80 |

| 11.6 USB Characteristics                                | .83 |

| 11.7 Low-Voltage Detection Characteristics              | .88 |

| 11.7.1 Low-Voltage Detection Reset                      | .88 |

| 11.7.2 Low-Voltage Detection Interrupt                  | .89 |

| 11.8 Flash Memory Write/Erase Characteristics           | .90 |

| 11.9 Return Time from Low-Power Consumption Mode .      |     |

| 11.9.1 Return Factor: Interrupt/WKUP                    |     |

| 11.9.2 Return Factor: Reset                             |     |

| 12. Ordering Information                                |     |

| 13. Acronyms                                            |     |

| 14. Package Dimensions                                  |     |

| 15. Errata                                              |     |

| 15.1 Part Numbers Affected                              |     |

| 15.2 Qualification Status                               | 104 |

| 15.3 Errata Summary                                     |     |

| Document History                                        |     |

| Sales, Solutions, and Legal Information                 | 106 |

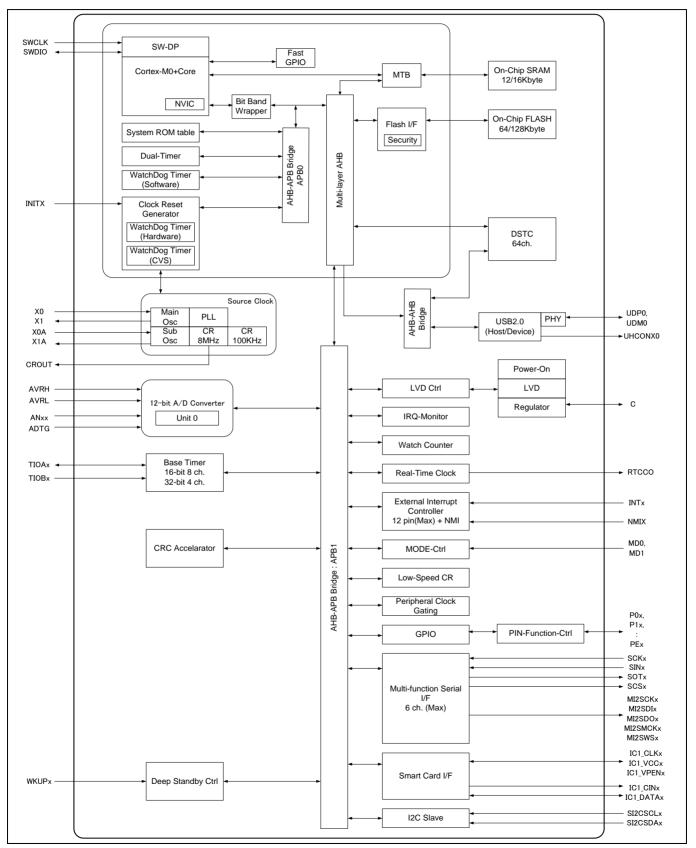

# 1. Block Diagram

# 5. List of Pin Functions

## List of Pin Numbers

The number after the underscore ("\_") in a pin name such as XXX\_1 and XXX\_2 indicates the relocated port number. The channel on such pin has multiple functions, each of which has its own pin name. Use the Extended Port Function Register (EPFR) to select the pin to be used.

|                   | Pin No.           |                   |          |         |            |                 |           |           |                     | <br>I             |

|-------------------|-------------------|-------------------|----------|---------|------------|-----------------|-----------|-----------|---------------------|-------------------|

| LQFP-64<br>QFN-64 | LQFP-48<br>QFN-48 | LQFP-32<br>QFN-32 | Pin Name |         | AI         | ternate Functio | ns        |           | I/O Circuit<br>Type | Pin State<br>Type |

| 1                 | 1                 | 2                 | P50      | SIN3_1  | INT00_0    |                 |           |           | D                   | K                 |

| 2                 | 2                 | 3                 | P51      | SOT3_1  | INT01_0    |                 |           |           | D                   | K                 |

| 3                 | 3                 | 4                 | P52      | SCK3_1  | INT02_0    |                 |           |           | D                   | K                 |

| 4                 | 4                 | -                 | P53      | TIOA1_2 | INT07_2    |                 |           |           | D                   | K                 |

| 5                 | 5                 | -                 | P30      | SCS60_1 | TIOB0_1    | INT03_2         | MI2SWS6_1 |           | D                   | K                 |

| 6                 | 6                 | -                 | P31      | SCK6_1  | SI2CSCL6_1 | INT04_2         | MI2SCK6_1 |           | Н                   | K                 |

| -                 | -                 | 5                 | P31      | SCK6_1  | SI2CSCL6_1 | INT04_2         |           |           | Н                   | K                 |

| 7                 | 7                 | -                 | P32      | SOT6_1  | SI2CSDA6_1 | TIOB2_1         | INT05_2   | MI2SDO6_1 | Н                   | K                 |

| -                 | -                 | 6                 | P32      | SOT6_1  | SI2CSDA6_1 | TIOB2_1         | INT05_2   |           | Н                   | K                 |

| 8                 | 8                 | -                 | P33      | ADTG_6  | SIN6_1     | INT04_0         | MI2SDI6_1 |           | Н                   | K                 |

| -                 | -                 | 7                 | P33      | ADTG_6  | SIN6_1     | INT04_0         |           |           | Н                   | K                 |

| 9                 | -                 | -                 | P34      | SCS61_1 | TIOB4_1    | MI2SMCK6_1      |           |           | D                   | K                 |

| -                 | 9                 | -                 | P34      | SCS61_1 | MI2SMCK6_1 |                 |           |           | D                   | K                 |

| 10                | -                 | -                 | P35      | SCS62_1 | TIOB5_1    | INT08_1         |           |           | D                   | K                 |

| 11                | -                 | -                 | P3A      | TIOA0_1 | INT03_0    | RTCCO_2         | SUBOUT_2  | IC1_CIN_0 | D                   | K                 |

| -                 | 10                | -                 | P3A      | TIOA0_1 | INT03_0    | RTCCO_2         | SUBOUT_2  |           | D                   | K                 |

| 12                | -                 | -                 | P3B      | TIOA1_1 | IC1_DATA_0 |                 |           |           | D                   | K                 |

| -                 | 11                | -                 | P3B      | TIOA1_1 |            |                 |           |           | D                   | K                 |

| 13                | -                 | -                 | P3C      | TIOA2_1 | IC1_RST_0  |                 |           |           | D                   | K                 |

| -                 | 12                | -                 | P3C      | TIOA2_1 |            |                 |           |           | D                   | K                 |

| 14                | -                 | -                 | P3D      | TIOA3_1 | IC1_VPEN_0 |                 |           |           | D                   | K                 |

| 15                | -                 | -                 | P3E      | TIOA4_1 | IC1_VCC_0  |                 |           |           | D                   | K                 |

| 16                | -                 | -                 | P3F      | TIOA5_1 | IC1_CLK_0  |                 |           |           | D                   | K                 |

| 17                | 13                | 8                 | MD0      |         |            |                 |           |           |                     | F                 |

| 18                | 14                | 9                 | PE2      | X0      |            |                 |           |           | Α                   | А                 |

| 19                | 15                | 10                | PE3      | X1      |            |                 |           |           | Α                   | В                 |

| 20                | -                 | -                 | P40      | TIOA0_0 | INT12_1    |                 |           |           | D                   | K                 |

| 21                | -                 | -                 | P41      | TIOA1_0 | INT13_1    |                 |           |           | D                   | K                 |

| 22                | -                 | -                 | P42      | TIOA2_0 |            |                 |           |           | D                   | K                 |

| 23                | -                 | -                 | P43      | ADTG_7  | TIOA3_0    |                 |           |           | D                   | K                 |

| 24                | -                 | -                 | P4C      | SCK7_1  | TIOB3_0    |                 |           |           | D                   | K                 |

| -                 | 16                | -                 | P4C      | SCK7_1  |            |                 |           |           | D                   | K                 |

| 25                | 17                | -                 | P4D      | SOT7_1  |            |                 |           |           | D                   | K                 |

| 26                | 18                | -                 | P4E      | SIN7_1  | INT06_2    |                 |           |           | D                   | К                 |

| 27                | 19                | 11                | VCC      |         |            |                 |           |           | -                   | -                 |

| 28                | 20                | 12                | С        |         |            |                 |           |           | -                   | -                 |

| 29                | 21                | 13                | VSS      |         |            |                 |           |           | -                   | -                 |

| 30                | 22                | 14                | P46      | X0A     |            |                 |           |           | С                   | С                 |

| 31                | 23                | 15                | P47      | X1A     |            |                 |           |           | С                   | D                 |

|                   | Pin No.           |                   |                   |         |            |                |           |         |                     |                   |

|-------------------|-------------------|-------------------|-------------------|---------|------------|----------------|-----------|---------|---------------------|-------------------|

| LQFP-64<br>QFN-64 | LQFP-48<br>QFN-48 | LQFP-32<br>QFN-32 | Pin Name          |         | Alt        | ernate Functio | ons       |         | I/O Circuit<br>Type | Pin State<br>Type |

| 32                | 24                | 16                | INITX             |         |            |                |           |         | В                   | E                 |

| 33                | 25                | 17                | P60               | TIOA2_2 | INT15_1    | CEC1_0         |           |         | Η                   | K                 |

| 34                | -                 | -                 | P1E               | RTS4_1  | MI2SMCK4_1 |                |           |         | D                   | K                 |

| 35                | -                 | -                 | P1D               | CTS4_1  | MI2SWS4_1  |                |           |         | D                   | K                 |

| 36                | -                 | -                 | P1C               | SCK4_1  | MI2SCK4_1  |                |           |         | D                   | K                 |

| 37                | -                 | -                 | P1B               | SOT4_1  | MI2SDO4_1  |                |           |         | D                   | K                 |

| -                 | 26                | -                 | P1B               | SOT4_1  |            |                |           |         | D                   | K                 |

| 38                | -                 | -                 | P1A               | SIN4_1  | INT05_1    | CEC0_0         | MI2SDI4_1 |         | Н                   | K                 |

| -                 | 27                | -                 | P1A               | SIN4_1  | INT05_1    | CEC0_0         |           |         | Н                   | K                 |

| 39                | -                 | -                 | P1F               | ADTG_5  |            |                |           |         | D                   | K                 |

| 40                | 28                | 18                | P10               | AN00    |            |                |           |         | F                   | J                 |

| 41                | 29                | 19                | P11               | AN01    | SIN1_1     | INT02_1        | WKUP1     |         | G                   | J                 |

| 42                | 30                | 20                | P12               | AN02    | SOT1_1     |                |           |         | F                   | J                 |

| 43                | 31                | 21                | P13               | AN03    | SCK1_1     | RTCCO_1        | SUBOUT_1  |         | F                   | J                 |

| 44                | 32                | -                 | P14               | AN04    | SIN0_1     | SCS10_1        | INT03_1   |         | F                   | J                 |

| 45                | 33                | -                 | P15               | AN05    | SOT0_1     | SCS11_1        |           |         | F                   | J                 |

| 46                | 34                | 22                | P23               | AN06    | SCK0_0     | TIOA7_1        |           |         | F                   | J                 |

| 47                | 35                | 23                | P22               | AN07    | TIOB7_1    |                |           |         | F                   | J                 |

| 48                | 36                | 24                | VCC               |         |            |                |           |         | -                   | -                 |

| 49                | 37                | -                 | AVRH <sup>1</sup> |         |            |                |           |         | -                   | -                 |

| 50                | 38                | 25                | AVRL              |         |            |                |           |         | -                   | -                 |

| 51                | 39                | 26                | P21               | INT06_1 | WKUP2      |                |           |         | Е                   | K                 |

| 52                | -                 | -                 | P00               | WKUP4   |            |                |           |         | Е                   | K                 |

| 53                | 40                | 27                | P01               | SWCLK   | SOT0_0     |                |           |         | D                   | K                 |

| 54                | -                 | -                 | P02               | WKUP5   |            |                |           |         | Е                   | K                 |

| 55                | 41                | 28                | P03               | SWDIO   | SIN0_0     | TIOB7_0        |           |         | D                   | K                 |

| 56                | 42                | 29                | P05               | MD1     | TIOA5_2    | INT00_1        | WKUP3     |         | Е                   | K                 |

| 57                | 43                | -                 | VCC               |         |            |                |           |         | -                   | -                 |

| 58                | 44                | 30                | P80               | UDM0    |            |                |           |         | J                   | G                 |

| 59                | 45                | 31                | P81               | UDP0    |            |                |           |         | J                   | G                 |

| 60                | 46                | 32                | VSS               |         |            |                |           |         | -                   | -                 |

| 61                | 47                | -                 | P61               | UHCONX0 | TIOB2_2    |                |           |         | Н                   | K                 |

| 62                | -                 | -                 | P0B               | TIOB6_1 | WKUP6      |                |           |         | Е                   | K                 |

| 63                | -                 | -                 | P0C               | TIOA6_1 | WKUP7      |                |           |         | Е                   | K                 |

| 64                | 48                | 1                 | P0F               | NMIX    | WKUP0      | RTCCO_0        | SUBOUT_0  | CROUT_1 | Е                   | I                 |

$<sup>^{1}\,</sup>$  In a 32-pin package, the AVRH pin is internally connected to the  $V_{CC}$  pin.

|                            |                    |                                                                                                                                                                                                                      | Pin No. |         |         |  |  |  |

|----------------------------|--------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------|---------|---------|--|--|--|

| Pin Function               | Pin Name           | Function Description                                                                                                                                                                                                 | LQFP-64 | LQFP-48 | LQFP-32 |  |  |  |

|                            |                    | Multi-function serial interface ch.1 input                                                                                                                                                                           | QFN-64  | QFN-48  | QFN-32  |  |  |  |

|                            | SIN1_1             | pin                                                                                                                                                                                                                  | 41      | 29      | 19      |  |  |  |

|                            | SOT1_1<br>(SDA1_1) | Multi-function serial interface ch.1 output<br>pin. This pin operates as SOT1 when<br>used as a UART/CSIO/LIN pin (operation<br>mode 0 to 3) and as SDA1 when used as<br>an I <sup>2</sup> C pin (operation mode 4). | 42      | 30      | 20      |  |  |  |

| Multi-function<br>Serial 1 | SCK1_1<br>(SCL1_1) | Multi-function serial interface ch.1 clock I/O pin. This pin operates as SCK1 when used as a CSIO pin (operation mode 2) and as SCL1 when used as an $I^2$ C pin (operation mode 4).                                 | 43      | 31      | 21      |  |  |  |

|                            | SCS10_1            | Multi-function serial interface ch.1 serial chip select 0 input/output pin.                                                                                                                                          | 44      | 32      | -       |  |  |  |

|                            | SCS11_1            | Multi-function serial interface ch.1 serial chip select 1 output pin.                                                                                                                                                | 45      | 33      | -       |  |  |  |

|                            | SIN3_1             | Multi-function serial interface ch.3 input<br>pin                                                                                                                                                                    | 1       | 1       | 2       |  |  |  |

| Multi-function<br>Serial 3 | SOT3_1<br>(SDA3_1) | Multi-function serial interface ch.3 output<br>pin. This pin operates as SOT3 when<br>used as a UART/CSIO/LIN pin (operation<br>mode 0 to 3) and as SDA3 when used as<br>an $I^2C$ pin (operation mode 4).           | 2       | 2       | 3       |  |  |  |

|                            | SCK3_1<br>(SCL3_1) | Multi-function serial interface ch.3 clock I/O pin. This pin operates as SCK3 when used as a CSIO (operation mode 2) and as SCL3 when used as an $I^2$ C pin (operation mode 4).                                     | 3       | 3       | 4       |  |  |  |

|                            | SIN4_1             | Multi-function serial interface ch.4 input<br>pin                                                                                                                                                                    | 38      | 27      | -       |  |  |  |

|                            | SOT4_1<br>(SDA4_1) | Multi-function serial interface ch.4 output<br>pin. This pin operates as SOT4 when<br>used as a UART/CSIO/LIN pin (operation<br>mode 0 to 3) and as SDA4 when used as<br>an $I^2C$ pin (operation mode 4).           | 37      | 26      | -       |  |  |  |

| Multi-function<br>Serial 4 | SCK4_1<br>(SCL4_1) | Multi-function serial interface ch.4 clock I/O pin. This pin operates as SCK4 when used as a CSIO (operation mode 2) and as SCL4 when used as an $I^2$ C pin (operation mode 4).                                     | 36      | -       | -       |  |  |  |

|                            | CTS4_1             | Multi-function serial interface ch4 CTS input pin                                                                                                                                                                    | 35      | -       | -       |  |  |  |

|                            | RTS4_1             | Multi-function serial interface ch4 RTS output pin                                                                                                                                                                   | 34      | -       | -       |  |  |  |

#### Latch-Up

Semiconductor devices are constructed by the formation of P-type and N-type areas on a substrate. When subjected to abnormally high voltages, internal parasitic PNPN junctions (called thyristor structures) may be formed, causing large current levels in excess of several hundred mA to flow continuously at the power supply pin. This condition is called latch-up.

CAUTION: The occurrence of latch-up not only causes loss of reliability in the semiconductor device, but can cause injury or damage from high heat, smoke or flame. To prevent this from happening, do the following:

(1) Be sure that voltages applied to pins do not exceed the absolute maximum ratings. This should include attention to abnormal noise, surge levels, etc.

(2) Be sure that abnormal current flows do not occur during the power-on sequence.

#### **Observance of Safety Regulations and Standards**

Most countries in the world have established standards and regulations regarding safety, protection from electromagnetic interference, etc. Customers are requested to observe applicable regulations and standards in the design of products.

#### Fail-Safe Design

Any semiconductor devices have inherently a certain rate of failure. You must protect against injury, damage or loss from such failures by incorporating safety design measures into your facility and equipment such as redundancy, fire protection, and prevention of over-current levels and other abnormal operating conditions.

#### **Precautions Related to Usage of Devices**

Cypress semiconductor devices are intended for use in standard applications (computers, office automation and other office equipment, industrial, communications, and measurement equipment, personal or household devices, etc.).

CAUTION: Customers considering the use of our products in special applications where failure or abnormal operation may directly affect human lives or cause physical injury or property damage, or where extremely high levels of reliability are demanded (such as aerospace systems, atomic energy controls, sea floor repeaters, vehicle operating controls, medical devices for life support, etc.) are requested to consult with sales representatives before such use. The company will not be responsible for damages arising from such use without prior approval.

#### 7.2 Precautions for Package Mounting

Package mounting may be either lead insertion type or surface mount type. In either case, for heat resistance during soldering, you should mount only under Cypress' recommended conditions. For detailed information about mount conditions, contact your sales representative.

#### Lead Insertion Type

Mounting of lead insertion type packages onto printed circuit boards may be done by two methods: direct soldering on the board, or mounting by using a socket.

Direct mounting onto boards normally involves processes for inserting leads into through-holes on the board and using the flow soldering (wave soldering) method of applying liquid solder. In this case, the soldering process usually causes leads to be subjected to thermal stress in excess of the absolute ratings for storage temperature. Mounting processes should conform to Cypress recommended mounting conditions.

If socket mounting is used, differences in surface treatment of the socket contacts and IC lead surfaces can lead to contact deterioration after long periods. For this reason it is recommended that the surface treatment of socket contacts and IC leads be verified before mounting.

#### Notes on Power-on

Turn power on/off in the following order or at the same time.

Turning on : VCC  $\rightarrow$  AVRH Turning off : AVRH  $\rightarrow$  VCC

#### Serial Communication

There is a possibility to receive wrong data due to the noise or other causes on the serial communication.

Therefore, design a printed circuit board so as to avoid noise.

Consider the case of receiving wrong data due to noise; perform error detection such as by applying a checksum of data at the end. If an error is detected, retransmit the data.

# Differences in Features Among the Products with Different Memory Sizes and Between Flash Memory Products and MASK Products

The electric characteristics including power consumption, ESD, latch-up, noise characteristics, and oscillation characteristics among the products with different memory sizes and between Flash memory products and MASK products are different because chip layout and memory structures are different.

If you are switching to use a different product of the same series, please make sure to evaluate the electric characteristics.

#### Pull-Up Function of 5 V Tolerant I/O

Please do not input the signal more than VCC voltage at the time of Pull-Up function use of 5 V tolerant I/O.

#### Handling when Using Debug Pins

When debug pins (SWDIO/SWCLK) are set to GPIO or other peripheral functions, set them as output only; do not set them as input.

| Tuno | Selected Pin Function   |                                                    |    | CPU State |     |     |     |     |     |     |  |  |  |

|------|-------------------------|----------------------------------------------------|----|-----------|-----|-----|-----|-----|-----|-----|--|--|--|

| Туре | Selected                |                                                    |    |           | (3) | (4) | (5) | (6) | (7) | (8) |  |  |  |

|      |                         | Resource other than above selected                 | -  | -         | PC  | HC  | IS  | GS  | IS  | GS  |  |  |  |

|      |                         | CEC pin selected                                   | -  | -         | CP  | CP  | CP  | CP  | CP  | СР  |  |  |  |

|      |                         | WKUP enable and<br>input selected                  | -  | -         | IP  | IP  | IP  | IP  | IP  | IP  |  |  |  |

|      | Digital I/O<br>selected | I2CSLAVE enable selected                           | -  | -         | PC  | НС  | IP  | GS  | IS  | GS  |  |  |  |

| к    |                         | External interrupt<br>enable and input<br>selected | -  | -         | PC  | НС  | IP  | GS  | IS  | GS  |  |  |  |

|      |                         | GPIO selected                                      | IS | IE        | PC  | HC  | IS  | HS  | IS  | HS  |  |  |  |

|      |                         | Resource other than above selected                 | -  | -         | PC  | HC  | IS  | GS  | IS  | GS  |  |  |  |

Terms in the table above have the following meanings.

#### Туре

This indicates a pin status type that is shown in "pin list table" in "5. List of Pin Functions"

#### **Selected Pin function**

This indicates a pin function that is selected by user program.

#### **CPU** state

This indicates a state of the CPU that is shown below.

- (1) Reset state. CPU is initialized by Power-on reset or a reset due to low Power voltage supply.

- (2) Reset state. CPU is initialized by INITX input signal or system initialization after power on reset.

- (3) Run mode or SLEEP mode state.

- (4) Timer mode, RTC mode or STOP mode state.

- The standby pin level setting bit (SPL) in the Standby Mode Control Register (STB\_CTL) is set to "0".

Timer mode, RTC mode or STOP mode state.

- (5) The standby pin level setting bit (SPL) in the Standby Mode Control Register (STB\_CTL) is set to "1".

- (6) Deep standby STOP mode or Deep standby RTC mode state, The standby pin level setting bit (SPL) in the Standby Mode Control Register (STB\_CTL) is set to "0"

Deep standby STOP mode or Deep standby RTC mode state,

- (7) The standby pin level setting bit (SPL) in the Standby Mode Control Register (STB\_CTL) is set to "1"

Run mode state after returning from Deep Standby mode.

- (8) (I/O state hold function(CONTX) is fixed at 1)

## **11.3 DC Characteristics**

#### 11.3.1 Current Rating

| Symbol        | Conditions                               |                                                                                                            | HCLK                    |                   | lue               | Unit | Remarks    |  |

|---------------|------------------------------------------|------------------------------------------------------------------------------------------------------------|-------------------------|-------------------|-------------------|------|------------|--|

| (Pin Name)    |                                          |                                                                                                            | Frequency <sup>19</sup> | Typ <sup>20</sup> | Max <sup>21</sup> | Unit | Rellians   |  |

|               |                                          | 8 MHz external clock input, PLL ON <sup>22</sup>                                                           | 8 MHz                   | 1.4               | 2.7               |      |            |  |

|               |                                          | NOP code executed                                                                                          | 20 MHz                  | 2.6               | 4.1               | mA   | 23         |  |

|               |                                          | Built-in high speed CR stopped<br>All peripheral clock stopped by CKENx                                    | 40 MHz                  | 3.9               | 5.6               |      |            |  |

|               | Run mode,                                | 8 MHz external clock input, PLL ON <sup>22</sup>                                                           | 8 MHz                   | 1.3               | 2.6               |      |            |  |

|               | code executed                            | Benchmark code executed                                                                                    | 20 MHz                  | 2.3               | 3.8               | mA   | 23         |  |

|               | from Flash                               | Built-in high speed CR stopped<br>PCLK1 stopped                                                            | 40 MHz                  | 3.4               | 5.1               |      |            |  |

|               |                                          | 8 MHz crystal oscillation, PLL ON <sup>22</sup>                                                            | 8 MHz                   | 1.6               | 3.0               |      |            |  |

|               |                                          | NOP code executed                                                                                          | 20 MHz                  | 2.8               | 4.4               | mA   | 23, 24,    |  |

|               |                                          | Built-in high speed CR stopped<br>All peripheral clock stopped by CKENx                                    | 40 MHz                  | 4.1               | 5.9               |      |            |  |

|               | Run mode,                                | 8 MHz external clock input, PLL ON <sup>22</sup>                                                           | 8 MHz                   | 1.0               | 2.1               |      |            |  |

|               | code executed                            | NOP code executed                                                                                          | 20 MHz                  | 1.7               | 2.9               | mA   | 23         |  |

| Icc<br>(VCC)  | from RAM                                 | Built-in high speed CR stopped<br>All peripheral clock stopped by CKENx                                    | 40 MHz                  | 2.7               | 4.0               |      |            |  |

|               | Run mode,<br>code executed<br>from Flash | 8 MHz external clock input, PLL ON<br>NOP code executed<br>Built-in high speed CR stopped<br>PCLK1 stopped | 40 MHz                  | 1.6               | 3.1               | mA   | 23, 25, 26 |  |

|               | Run mode,<br>code executed<br>from Flash | Built-in high speed CR <sup>27</sup><br>NOP code executed<br>All peripheral clock stopped by CKENx         | 8 MHz                   | 1.1               | 2.4               | mA   | 23         |  |

|               |                                          | 32 kHz crystal oscillation<br>NOP code executed<br>All peripheral clock stopped by CKENx                   | 32 kHz                  | 240               | 1264              | μA   | 23         |  |

|               |                                          | Built-in low speed CR<br>NOP code executed<br>All peripheral clock stopped by CKENx                        | 100 kHz                 | 246               | 1271              | μA   | 23         |  |

|               |                                          | $0.0115$ and an all the binnet $D11.001^{22}$                                                              | 8 MHz                   | 0.8               | 1.9               |      |            |  |

|               |                                          | 8 MHz external clock input, PLL ON <sup>22</sup><br>All peripheral clock stopped by CKENx                  | 20 MHz                  | 1.3               | 2.4               | mA   | 23         |  |

|               |                                          |                                                                                                            | 40 MHz                  | 1.8               | 3.0               |      |            |  |

| Iccs<br>(VCC) | Sleep<br>operation                       | Built-in high speed CR <sup>27</sup><br>All peripheral clock stopped by CKENx                              | 8 MHz                   | 0.6               | 1.7               | mA   | 23         |  |

|               | ορειαιιοτι                               | 32 kHz crystal oscillation<br>All peripheral clock stopped by CKENx                                        | 32 kHz                  | 237               | 1261              | μA   | 23         |  |

|               |                                          | Built-in low speed CR<br>All peripheral clock stopped by CKENx                                             | 100 kHz                 | 238               | 1262              | μA   | 23         |  |

<sup>19</sup> PCLK0 is set to divided rate 8.

<sup>20</sup> T<sub>A</sub>=+25°C,V<sub>CC</sub>=3.3 V

<sup>21</sup> T<sub>A</sub>=+105°C,V<sub>CC</sub>=3.6 V

<sup>22</sup> When HCLK=8, PLL is off.

<sup>23</sup> All ports are fixed

<sup>24</sup> When IMAINSEL bit (MOSC\_CTL:IMAINSEL) is "10" (default).

<sup>25</sup> Flash sync down is set to FRWTR.RWT=111 and FSYNDN.SD=1111

<sup>26</sup> VCC=1.65 V

<sup>27</sup> The frequency is act to 8 MHz by trimping

<sup>27</sup> The frequency is set to 8 MHz by trimming

#### 11.3.3 Pin Characteristics

| Parameter                        | Symbol           | Pin Name                        | Conditions                                           |                         | Value |                       | Unit | Remarks |

|----------------------------------|------------------|---------------------------------|------------------------------------------------------|-------------------------|-------|-----------------------|------|---------|

| T di di liotor                   | Cymbol           | · ·····                         |                                                      | Min                     | Тур   | Max                   | 0    | Romanio |

| H level input                    |                  | CMOS<br>hysteresis              | V <sub>CC</sub> ≥ 2.7 V                              | V <sub>CC</sub> × 0.8   | _     | V <sub>CC</sub> +0.3  | V    |         |

| voltage<br>(hysteresis<br>input) | V <sub>IHS</sub> | input pin,<br>MD0               | $V_{CC}$ < 2.7 V                                     | $V_{CC} \times 0.7$     |       |                       |      |         |

|                                  |                  | 5 V tolerant                    | $V_{CC} \ge 2.7 V$                                   | $V_{CC} \times 0.8$     |       | V <sub>SS</sub> +5.5  | V    |         |

|                                  |                  | input pin                       | $V_{CC}$ < 2.7 V                                     | V <sub>CC</sub> × 0.7   | -     | V <sub>SS</sub> +0.0  | v    |         |

| L level input                    |                  | CMOS<br>hysteresis              | V <sub>CC</sub> ≥ 2.7 V                              | V <sub>ss</sub> - 0.3   | -     | V <sub>CC</sub> × 0.2 | V    |         |

| voltage<br>(hysteresis<br>input) | V <sub>ILS</sub> | input pin,<br>MD0               | $V_{CC}$ < 2.7 V                                     |                         |       | $V_{CC} \times 0.3$   |      |         |

|                                  |                  | 5 V tolerant                    | $V_{CC} \ge 2.7 V$                                   |                         | -     | $V_{CC} \times 0.2$   |      |         |

|                                  |                  | input pin                       | V <sub>CC</sub> < 2.7 V                              | - V <sub>SS</sub> - 0.3 | -     | V <sub>CC</sub> × 0.3 | V    |         |

| H level                          | V <sub>OH</sub>  | 4 mA type                       | V <sub>CC</sub> ≥ 2.7 V,<br>I <sub>OH</sub> = - 4 mA | V <sub>CC</sub> - 0.5   | _     | V <sub>cc</sub>       | v    |         |

| output voltage                   | VON              | i nii (typo                     | V <sub>CC</sub> < 2.7 V,<br>I <sub>OH</sub> = - 2 mA | V <sub>CC</sub> - 0.45  |       | VCC                   | v    |         |

| L level<br>output voltage        | V <sub>OL</sub>  | 4 mA type                       | $V_{CC} \ge 2.7 \text{ V},$<br>$I_{OL} 4 \text{ mA}$ | - V <sub>ss</sub>       | -     | 0.4                   | V    |         |

| oulput voltage                   |                  |                                 | V <sub>CC</sub> < 2.7 V,<br>I <sub>OL</sub> =2 mA    |                         |       |                       |      |         |

| Input leak<br>current            | l <sub>IL</sub>  | -                               | -                                                    | - 5                     | -     | + 5                   | μA   |         |

| Pull-up                          |                  |                                 | $V_{CC} \ge 2.7 V$                                   | 21                      | 33    | 48                    |      |         |

| resistance<br>value              | R <sub>PU</sub>  | Pull-up pin                     | V <sub>CC</sub> < 2.7 V                              | -                       | -     | 88                    | kΩ   |         |

| Input<br>capacitance             | C <sub>IN</sub>  | Other than<br>VCC, VSS,<br>AVRH | -                                                    | -                       | 5     | 15                    | pF   |         |

## $(V_{CC} = 1.65 \text{ V to } 3.6 \text{ V}, V_{SS} = 0 \text{ V}, T_{A} = -40^{\circ}\text{C to } +105^{\circ}\text{C})$

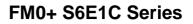

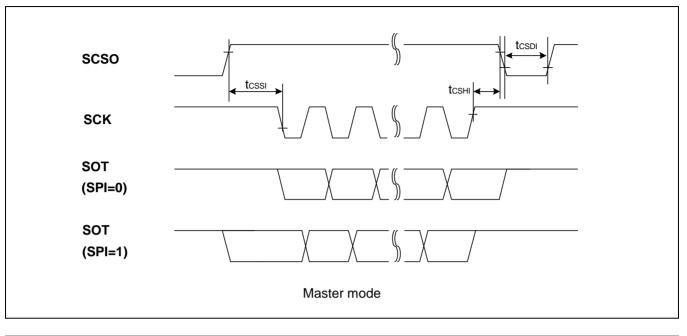

## When Using CSIO/SPI Chip Select (SCINV=1, CSLVL=1)

| 5 1                | ,                 | · · ·       | (V <sub>cc</sub>       | ;= 1.65 V to      | 3.6 V, V <sub>SS</sub> = 0 | V, T <sub>A</sub> =- 40° | C to +1 |

|--------------------|-------------------|-------------|------------------------|-------------------|----------------------------|--------------------------|---------|

| Parameter          | Symbol            | Conditions  | V <sub>cc</sub> < 2    | 2.7 V             | V <sub>cc</sub> ≥ 2        | Unit                     |         |

| Farameter          | Symbol            | Conditions  | Min                    | Max               | Min                        | Max                      |         |

| S↓→SCK↑ setup time | t <sub>CSSI</sub> |             | -50 <sup>46</sup>      | +0 <sup>46</sup>  | -50 <sup>46</sup>          | +0 <sup>46</sup>         | ns      |

| K↓→SCS↑ hold time  | t <sub>CSHI</sub> | Master mode | +047                   | +50 <sup>47</sup> | +047                       | +50 <sup>47</sup>        | ns      |

| S deselect time    | t <sub>CSDI</sub> |             | -50 <sup>48</sup>      | +50 <sup>48</sup> | -50 <sup>48</sup>          | +50 <sup>48</sup>        | ns      |

| S↓→SCK↑ setup time | t <sub>CSSE</sub> |             | 3t <sub>CYCP</sub> +30 | -                 | 3t <sub>CYCP</sub> +30     | -                        | ns      |

| K↓→SCS↑ hold time  | t <sub>CSHE</sub> |             | 0                      | -                 | 0                          | -                        | ns      |

| S deselect time    | t <sub>CSDE</sub> | Slave mode  | 3t <sub>CYCP</sub> +30 | -                 | 3t <sub>CYCP</sub> +30     | -                        | ns      |

| S↓→SOT delay time  | t <sub>DSE</sub>  |             | -                      | 55                | -                          | 40                       | ns      |

| S↑→SOT delay time  | t <sub>DEE</sub>  |             | 0                      | -                 | 0                          | -                        | ns      |

#### Notes:

SCS SCK SCS SCS SCK SCS SCS SCS

- t<sub>CYCP</sub> indicates the APB bus clock cycle time. For the number of the APB bus to which the Base Timer has been connected, see the Peripheral Address Map.

- For information about CSSU, CSHD, CSDS, serial chip select timing operating clock, see "FM0+ Family Peripheral Manual".

- These characteristics guarantee only the same relocate port number. For example, the combination of SCKx\_0 and SCSIx\_1 is not guaranteed.

- When the external load capacitance  $C_L=30$  pF.

CSSU bit value  $\times$  serial chip select timing operating clock cycle. CSHD bit value  $\times$  serial chip select timing operating clock cycle. 46 47

<sup>48</sup>

<sup>&</sup>lt;sup>48</sup> CSDS bit value x serial chip select timing operating clock cycle. Irrespective of CSDS bit setting, 5t<sub>CYCP</sub> or more are required for the period the time when the serial chip select pin becomes inactive to the time when the serial chip select pin becomes active again.

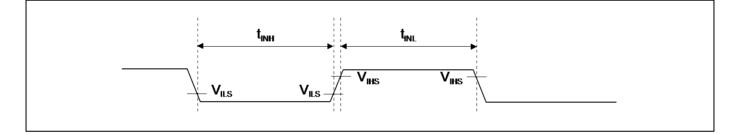

#### 11.4.10 External Input Timing

| Parameter         | Symbol                              | Pin Name                     | Conditions | Value                                  |     | Unit | Remarks                        |

|-------------------|-------------------------------------|------------------------------|------------|----------------------------------------|-----|------|--------------------------------|

| Parameter         | Symbol                              | Pin Name                     | Conditions | Min                                    | Max | Unit | Remarks                        |

| Input pulse width | t <sub>INH</sub> , t <sub>INL</sub> | ADTGx                        | -          | 2 t <sub>CYCP</sub> <sup>55</sup>      | -   | ns   | A/D converter<br>trigger input |

|                   |                                     | INT00 to INT08,              | 56         | 2 t <sub>CYCP</sub> +100 <sup>55</sup> | -   | ns   | External                       |

|                   |                                     | INT12, INT13,<br>INT15, NMIX | 57         | 500                                    | -   | ns   | interrupt, NMI                 |

|                   |                                     | WKUPx                        | 58         | 500                                    | -   | ns   | Deep standby<br>wake up        |

<sup>&</sup>lt;sup>55</sup> t<sub>CYCP</sub> indicates the APB bus clock cycle time. For the number of the APB bus to which the Base Timer has been connected, see the Peripheral Address Map.

<sup>56</sup> In Run mode and Sleep mode

<sup>57</sup> In Timer mode, RTC mode and Stop mode

<sup>58</sup> In Deep Standby RTC mode and Deep Standby Stop mode

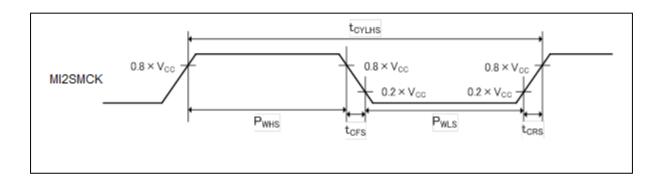

## **MI2SMCK Input Characteristics**

| $(V_{CC} =$ | 1 65 | V | to | 36  | V  | Vee=  | 0 | V  | T_=- | 40°C | to | +105°C) |

|-------------|------|---|----|-----|----|-------|---|----|------|------|----|---------|

| (*00-       | 1.05 | v | ιU | 5.0 | ٧, | v ss- | υ | v, | I A  | 40 0 | ιU | +103 C) |

| Parameter                           | Symbol                               | Pin Name | Conditions                                                                   | Value  |        | Unit         | Remarks                      |

|-------------------------------------|--------------------------------------|----------|------------------------------------------------------------------------------|--------|--------|--------------|------------------------------|

| Falailletei                         |                                      |          | Min                                                                          | in Max |        | i terriar ko |                              |

| Input frequency                     | f <sub>CHS</sub>                     | MI2SMCK  | -                                                                            | -      | 12.288 | MHz          |                              |

| Input clock cycle                   | t <sub>CYLHS</sub>                   | -        | -                                                                            | 81.3   | -      | ns           |                              |

| Input clock pulse width             | -                                    | -        | P <sub>WHS</sub> /t <sub>CYLHS</sub><br>P <sub>WLS</sub> /t <sub>CYLHS</sub> | 45     | 55     | %            | When using<br>external clock |

| Input clock rise time and fall time | t <sub>CFS</sub><br>t <sub>CRS</sub> | -        | -                                                                            | -      | 5      | ns           | When using<br>external clock |

# **MI2SMCK** Output Characteristics

(V\_CC= 1.65 V to 3.6 V, V\_SS= 0 V, T\_A=- 40°C to +105°C)

| Parameter        | Symbol           | Pin Name  | Conditions | Value |     | Unit | Remarks                 |  |

|------------------|------------------|-----------|------------|-------|-----|------|-------------------------|--|

| Falameter        | Symbol           | Fin Name  | Conditions | Min   | Max | Unit | itema ka                |  |

| Output frequency | £                | MIDEMOK   |            | -     | 25  | MHz  | $V_{CC} \ge 2.7 V$      |  |

|                  | t <sub>CHS</sub> | MI2SMCK - | -          | -     | 20  | MHz  | V <sub>CC</sub> < 2.7 V |  |

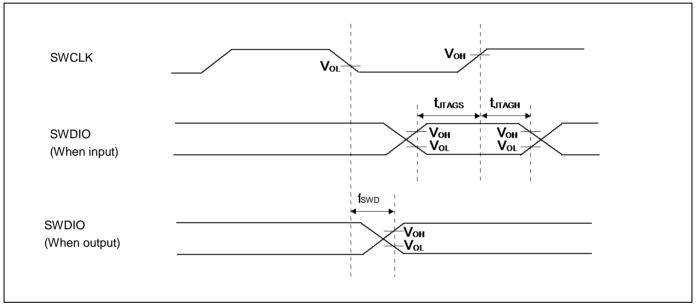

#### 11.4.14 SW-DP Timing

(V<sub>CC</sub>= 1.65 V to 3.6 V, V<sub>SS</sub>= 0 V, T<sub>A</sub>=- 40°C to +105°C)

| Parameter        | Symbol           | Pin Name        | Conditions | Value |     | Unit | Remarks |  |

|------------------|------------------|-----------------|------------|-------|-----|------|---------|--|

| Faranieter       | Symbol           | Fill Maille     | Conditions | Min   | Max | Unit | Remarks |  |

| SWDIO setup time | t <sub>sws</sub> | SWCLK,<br>SWDIO | -          | 15    | -   | ns   |         |  |

| SWDIO hold time  | t <sub>SWH</sub> | SWCLK,<br>SWDIO | -          | 15    | -   | ns   |         |  |

| SWDIO delay time | t <sub>SWD</sub> | SWCLK,<br>SWDIO | -          | -     | 45  | ns   |         |  |

#### Note:

- External load capacitance C<sub>L</sub>=30 pF

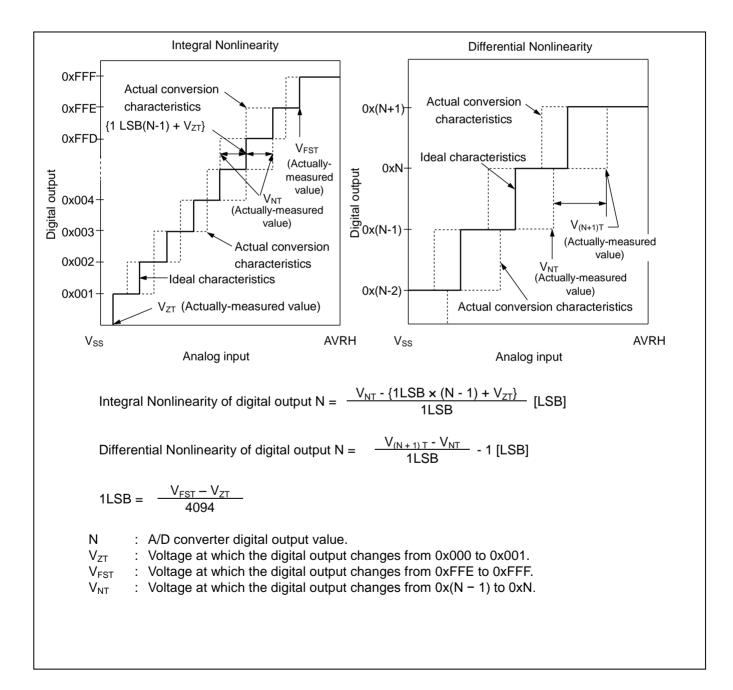

## Definitions of 12-bit A/D Converter Terms

Resolution:

Analog variation that is recognized by an A/D converter.

Deviation of the line between the zero-transition point (0b00000000000  $\leftrightarrow \rightarrow$  0b00000000001) and the ■Integral Nonlinearity: full-scale transition point (0b1111111110  $\leftarrow \rightarrow 0b11111111111$ ) from the actual conversion characteristics.

Differential Nonlinearity: Deviation from the ideal value of the input voltage that is required to change the output code by 1 LSB.

### **11.6 USB Characteristics**

| Parameter                |                                | Symbol        | Pin           |                                          | Value                    |                          | Unit | Schematic |

|--------------------------|--------------------------------|---------------|---------------|------------------------------------------|--------------------------|--------------------------|------|-----------|

|                          |                                | Symbol        | Name          | Conditions                               | Min                      | Max                      | Unit | Reference |

|                          | Input H level voltage          | Vін           |               | -                                        | 2.0                      | V <sub>cc</sub> +<br>0.3 | V    | 1         |

| Input<br>characteristics | Input L level voltage          | VIL           |               | -                                        | V <sub>SS</sub> –<br>0.3 | 0.8                      | V    | 1         |

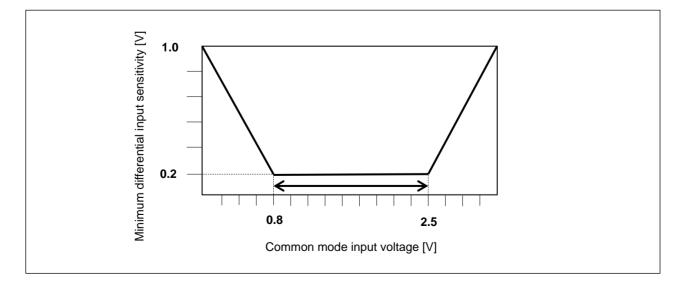

|                          | Differential input sensitivity | Vdi           |               | -                                        | 0.2                      | -                        | V    | 2         |

|                          | Differential common mode range | Vсм           |               | -                                        | 0.8                      | 2.5                      | V    | 2         |

|                          | Output H level voltage         | Vон           | UDP0,<br>UDM0 | External pull-down<br>resistance = 15 kΩ | 2.8                      | 3.6                      | V    | 3         |

|                          | Output L level voltage         | Vol           |               | External pull-up<br>resistance = 1.5 kΩ  | 0.0                      | 0.3                      | V    | 3         |

|                          | Crossover voltage              | VCRS          |               | -                                        | 1.3                      | 2.0                      | V    | 4         |

| Output                   | Rising time                    | tFR           |               | Full-speed                               | 4                        | 20                       | ns   | 5         |

| characteristic           | Falling time                   | tFF           |               | Full-speed                               | 4                        | 20                       | ns   | 5         |

|                          | Rising/Falling time matching   | <b>t</b> FRFM |               | Full-speed                               | 90                       | 111.11                   | %    | 5         |

|                          | Output impedance               | Zdrv          |               | Full-speed                               | 28                       | 44                       | Ω    | 6         |

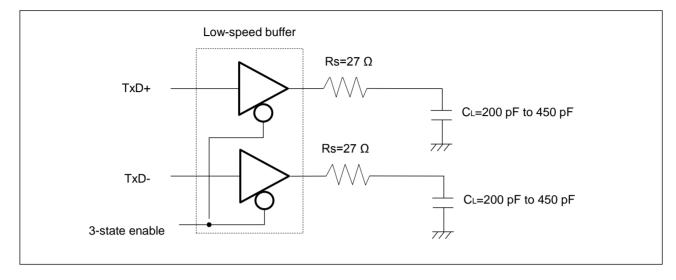

|                          | Rising time                    | tLR           |               | Low-speed                                | 75                       | 300                      | ns   | 7         |

|                          | Falling time                   | tLF           |               | Low-speed                                | 75                       | 300                      | ns   | 7         |

|                          | Rising/Falling time matching   | <b>t</b> LRFM |               | Low-speed                                | 80                       | 125                      | %    | 7         |

#### (V<sub>CC</sub>=3.0 V to 3.6 V, V<sub>SS</sub>=0 V, $T_A$ =- 40°C to +105°C)

1. The switching threshold voltage of single-end-receiver of USB I/O buffer is set as within VIL(Max)=0.8 V, VIH(Min)=2.0 V (TTL input standard).

There is some hysteresis to lower noise sensitivity.

2. Use differential-receiver to receive USB differential data signal.

Differential-receiver has 200 mV of differential input sensitivity when the differential data input is within 0.8 V to 2.5 V to the local ground reference level.

Above voltage range is the common mode input voltage range.

# Low-Speed Load (Compliance Load)

# 15. Errata

This chapter describes the errata for S6E1C product family. Details include errata trigger conditions, scope of impact, available workaround, and silicon revision applicability.

Contact your local Cypress Sales Representative if you have questions.

#### 15.1 Part Numbers Affected

| Part Number                                                                                                         |  |  |  |  |  |  |

|---------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|--|

| S6E1C32D0AGV20000, S6E1C32C0AGV20000, S6E1C32B0AGP20000, S6E1C32D0AGN20000, S6E1C32C0AGN20000, S6E1C32B0AGN20000    |  |  |  |  |  |  |

| S6E1C31D0AGV20000, S6E1C31C0AGV20000, S6E1C31B0AGP20000, S6E1C31D0AGN20000, S6E1C31C0AGN20000, S6E1C31B0AGN20000    |  |  |  |  |  |  |

| S6E1C12D0AGV20000, S6E1C12C0AGV20000, S6E1C12B0AGP20000,<br>S6E1C12D0AGN20000, S6E1C12C0AGN20000, S6E1C12B0AGN20000 |  |  |  |  |  |  |

| S6E1C11D0AGV20000, S6E1C11C0AGV20000, S6E1C11B0AGP20000, S6E1C11D0AGN20000, S6E1C11C0AGN20000, S6E1C11B0AGN20000    |  |  |  |  |  |  |

#### **15.2 Qualification Status**

Product Status: In Production – Qual.

#### 15.3 Errata Summary

This table defines the errata applicability to available devices.

| Items                    | Part Number   | Silicon Revision | Fix Status                        |  |

|--------------------------|---------------|------------------|-----------------------------------|--|

| [1] AHB Bus Matrix issue | Refer to 15.1 | Rev B            | Will be fixed in the next silicon |  |

#### 1. AHB Bus Matrix issue

#### ■ PROBLEM DEFINITION

The AHB Bus Matrix logic has two master interfaces (CPU and DSTC) and four slave interfaces (RAM, FLASH, AHB and APB). When two master interfaces (CPU and DSTC) access the same slave interface at the same time, and when the CPU is in wait cycle, an unnecessary access occurs during the wait cycle and the expected access occurs again after the unnecessary access.

#### ■ PARAMETERS AFFECTED

N/A

# ■TRIGGER CONDITION(S)

CPU and DSTC access the same slave interface at the same time.

SCOPE OF IMPACT DSTC cannot be used.

WORKAROUND DSTC must not use.

FIX STATUS This issue will be fixed in the next silicon revision.