Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

### Details

| Product Status             | Active                                                              |

|----------------------------|---------------------------------------------------------------------|

| Core Processor             | ARM7®                                                               |

| Core Size                  | 16/32-Bit                                                           |

| Speed                      | 41.78MHz                                                            |

| Connectivity               | I <sup>2</sup> C, SPI, UART/USART                                   |

| Peripherals                | PLA, POR, PWM, PSM, Temp Sensor, WDT                                |

| Number of I/O              | 28                                                                  |

| Program Memory Size        | 126KB (63K x 16)                                                    |

| Program Memory Type        | FLASH                                                               |

| EEPROM Size                | -                                                                   |

| RAM Size                   | 2K x 32                                                             |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 3.6V                                                           |

| Data Converters            | A/D 10x12b; D/A 1x10b                                               |

| Oscillator Type            | Internal                                                            |

| Operating Temperature      | -40°C ~ 125°C (TA)                                                  |

| Mounting Type              | Surface Mount                                                       |

| Package / Case             | 64-VFQFN Exposed Pad, CSP                                           |

| Supplier Device Package    | 64-LFCSP-VQ (9x9)                                                   |

| Purchase URL               | https://www.e-xfl.com/product-detail/analog-devices/aduc7128bcpz126 |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

### **SPECIFICATIONS**

Table 1.

$AV_{DD} = IOV_{DD} = 3.0 V$  to 3.6 V,  $V_{REF} = 2.5 V$  internal reference,  $f_{CORE} = 41.78 MHz$ . All specifications  $T_A = T_{MAX}$  to  $T_{MIN}$ , unless otherwise noted.

#### Parameter Min Max Unit **Test Conditions/Comments** Тур ADC CHANNEL SPECIFICATIONS Eight acquisition clocks and fADC/2 ADC Power-Up Time 5 μs DC Accuracy<sup>1, 2</sup> 12 Resolution Bits Integral Nonlinearity<sup>3</sup> LSB 2.5 V internal reference 85°C to 125°C only ±0.7 ±2.0 LSB 2.5 V internal reference -40°C to +85°C ±0.7 ±1.5 ±2.0 LSB 1.0 V external reference Differential Nonlinearity<sup>3</sup> +1/-0.9LSB 2.5 V internal reference ±0.5 ±0.6 LSB 1.0 V external reference DC Code Distribution 1 LSB ADC input is a dc voltage **ENDPOINT ERRORS<sup>4</sup>** Offset Error ±5 LSB Offset Error Match LSB ±1 Gain Error ±5 LSB Gain Error Match ±1 LSB DYNAMIC PERFORMANCE $F_{IN} = 10 \text{ kHz}$ sine wave, $f_{SAMPLE} = 1 \text{ MSPS}$ Signal-to-Noise Ratio (SNR) 69 dB Total Harmonic Distortion (THD) -78 dB Peak Harmonic or Spurious Noise -75 dB Channel-to-Channel Crosstalk dB -80 Crosstalk Between Channel 12 and -60 dB Channel 13 ANALOG INPUT Input Voltage Ranges Differential Mode<sup>5</sup> $V_{CM} \pm V_{REF}/2$ V ٧ Single-Ended Mode 0 to $V_{\text{REF}}$ 85°C to 125°C only Leakage Current ±15 μA -40°C to +85°C ±1 ±3 μΑ Input Capacitance 20 рF **During ADC acquisition ON-CHIP VOLTAGE REFERENCE** 0.47 $\mu$ F from V<sub>REF</sub> to AGND **Output Voltage** 2.5 v Measured at $T_A = 25^{\circ}C$ Accuracy $\pm 2.5$ mV Reference Drop When DAC Enabled 9 mV Reference drop when DAC enabled ppm/°C **Reference Temperature Coefficient** ±40 **Power Supply Rejection Ratio** 80 dB **Output Impedance** 40 Ω Internal V<sub>REF</sub> Power-On Time 1 ms **EXTERNAL REFERENCE INPUT<sup>6</sup>** Input Voltage Range 0.625 AVDD V Input Impedance 38 kΩ DAC CHANNEL SPECIFICATIONS VDAC Output $R_L = 5 \text{ k}\Omega$ , $C_L = 100 \text{ pF}$ Voltage Swing $(0.33 \times V_{REF} \pm$ V<sub>REF</sub> is the internal 2.5 V reference $0.2 \times V_{REF}) \times$ 1.33 7 I/V Output Resistance Ω V mode selected Low-Pass Filter 3 dB Point 1 MHz 2-pole at 1.5 MHz and 2 MHz Bits Resolution 10

| Parameter                                       | Min    | Тур    | Max                      | Unit       | Test Conditions/Comments                                                                                                                                                                                                       |

|-------------------------------------------------|--------|--------|--------------------------|------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Relative Accuracy                               |        | ±2     |                          | LSB        |                                                                                                                                                                                                                                |

| Differential Nonlinearity, +VE                  |        | 0.35   |                          | LSB        |                                                                                                                                                                                                                                |

| Differential Nonlinearity, –VE                  |        | -0.15  |                          | LSB        |                                                                                                                                                                                                                                |

| Offset Error                                    |        |        | -190                     | mV         |                                                                                                                                                                                                                                |

| Gain Error                                      |        |        | +150                     | mV         |                                                                                                                                                                                                                                |

| Voltage Output Settling Time<br>to 0.1%         |        |        | 5                        | μs         |                                                                                                                                                                                                                                |

| Line Driver Output                              |        |        |                          |            | As measured into a range of specified loads<br>(see Figure 2) at LD1TX and LD2TX, unless<br>otherwise noted                                                                                                                    |

| Total Harmonic Distortion                       |        | -52    |                          | dB         | PLM operating at 691.2 kHz                                                                                                                                                                                                     |

| Output Voltage Swing                            |        | ±1.768 |                          | V rms      |                                                                                                                                                                                                                                |

| COMMON MODE                                     |        |        |                          |            |                                                                                                                                                                                                                                |

| AC Mode                                         |        | 1.65   |                          | V          | Each output has a common mode of $0.5 V \times AV_{DD}$<br>and swings $0.5 V \times V_{REF}$ above and below this;                                                                                                             |

| DC Mode                                         |        | 1.5    |                          | v          | V <sub>REF</sub> is the internal 2.5 V reference<br>Each output has a common mode of 0.5 V × V <sub>REF</sub><br>and swings 0.6 V × V <sub>REF</sub> above and below this;<br>V <sub>RFF</sub> is the internal 2.5 V reference |

| DIFFERENTIAL INPUT IMPEDANCE                    | 11     | 13     |                          | kΩ         | Line driver buffer disabled                                                                                                                                                                                                    |

| Leakage Current LD1TX, LD2TX                    |        | 15     | 7                        | μΑ         | Line driver buffer disabled                                                                                                                                                                                                    |

| Short-Circuit Current                           |        | ±50    | ,                        | mA         |                                                                                                                                                                                                                                |

| Line Driver Tx Power-Up Time                    |        | ±30    | 20                       |            | No protection diodes, max allowable current                                                                                                                                                                                    |

| COMPARATOR                                      |        |        | 20                       | μs         |                                                                                                                                                                                                                                |

|                                                 |        | . 15   |                          |            |                                                                                                                                                                                                                                |

| Input Offset Voltage                            |        | ±15    |                          | mV         |                                                                                                                                                                                                                                |

| Input Bias Current                              | AGND   | 1      | AV. 1.2.V.               | μΑ         |                                                                                                                                                                                                                                |

| Input Voltage Range                             | AGND   | 7      | AV <sub>DD</sub> – 1.2 V | <b>"</b> Г |                                                                                                                                                                                                                                |

| Input Capacitance<br>Hysteresis <sup>3, 5</sup> | 2      | 7      | 1 5                      | pF         |                                                                                                                                                                                                                                |

| nysteresis                                      | 2      |        | 15                       | mV         | Hysteresis can be turned on or off via the CMPHYST bit in the CMPCON register                                                                                                                                                  |

| Response Time                                   |        | 1      |                          | μs         | Response time can be modified via the CMPRES<br>bits in the CMPCON register                                                                                                                                                    |

| TEMPERATURE SENSOR                              |        |        |                          |            |                                                                                                                                                                                                                                |

| Voltage Output at 25°C                          |        | 780    |                          | mV         |                                                                                                                                                                                                                                |

| Voltage Temperature Coefficient                 |        | -1.3   |                          | mV/°C      |                                                                                                                                                                                                                                |

| Accuracy                                        |        | ±3     |                          | °C         |                                                                                                                                                                                                                                |

| POWER SUPPLY MONITOR (PSM)                      |        |        |                          |            |                                                                                                                                                                                                                                |

| IOV <sub>DD</sub> Trip Point Selection          |        | 2.79   |                          | V          | Two selectable trip points                                                                                                                                                                                                     |

|                                                 |        | 3.07   |                          | V          |                                                                                                                                                                                                                                |

| Power Supply Trip Point Accuracy                |        | ±2.5   |                          | %          | Of the selected nominal trip point voltage                                                                                                                                                                                     |

| GLITCH IMMUNITY ON RST PIN <sup>3</sup>         |        | 50     |                          | μs         |                                                                                                                                                                                                                                |

| WATCHDOG TIMER (WDT)                            |        |        |                          |            |                                                                                                                                                                                                                                |

| Timeout Period                                  | 0      |        |                          | ms         |                                                                                                                                                                                                                                |

|                                                 |        |        | 512                      | sec        |                                                                                                                                                                                                                                |

| FLASH/EE MEMORY <sup>7, 8</sup>                 |        |        | -                        |            |                                                                                                                                                                                                                                |

| Endurance                                       | 10,000 |        |                          | Cycles     |                                                                                                                                                                                                                                |

| Data Retention                                  | 20     |        |                          | Years      | T <sub>J</sub> = 85°C                                                                                                                                                                                                          |

| DIGITAL INPUTS                                  |        |        |                          |            | All digital inputs, including XCLKI and XCLKO                                                                                                                                                                                  |

| Logic 1 Input Current (Leakage<br>Current)      |        | ±0.2   | ±1                       | μΑ         | $V_{\text{INH}} = V_{\text{DD}} \text{ or } V_{\text{INH}} = 5 \text{ V}$                                                                                                                                                      |

| Logic 0 Input Current (Leakage<br>Current)      |        | -40    | -65                      | μΑ         | $V_{INL} = 0 V$ , except TDI                                                                                                                                                                                                   |

|                                                 |        | -80    | +125                     | μA         | V <sub>INL</sub> = 0 V, TDI Only                                                                                                                                                                                               |

| Input Capacitance                               |        | 15     |                          | pF         |                                                                                                                                                                                                                                |

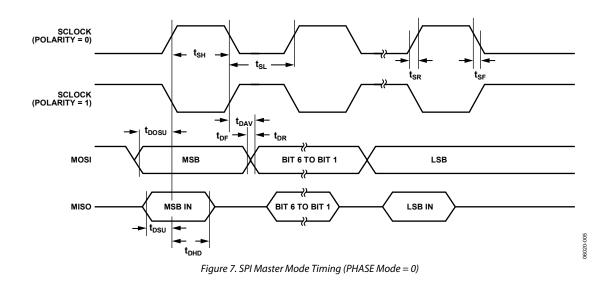

### Table 6. SPI Master Mode Timing (PHASE Mode = 0)

| Parameter         | Description                                           | Min                 | Тур                            | Max                                                   | Unit |

|-------------------|-------------------------------------------------------|---------------------|--------------------------------|-------------------------------------------------------|------|

| t <sub>sL</sub>   | SCLOCK low pulse width <sup>1</sup>                   |                     | $(SPIDIV + 1) \times t_{HCLK}$ |                                                       | ns   |

| t <sub>sн</sub>   | SCLOCK high pulse width <sup>1</sup>                  |                     | $(SPIDIV + 1) \times t_{HCLK}$ |                                                       | ns   |

| t <sub>DAV</sub>  | Data output valid after SCLOCK edge                   |                     |                                | $2 \times t_{\text{HCLK}} + 2 \times t_{\text{UCLK}}$ | ns   |

| t <sub>DOSU</sub> | Data output setup before SCLOCK edge                  |                     |                                | 75                                                    | ns   |

| t <sub>DSU</sub>  | Data input setup time before SCLOCK edge <sup>2</sup> | $1 \times t_{UCLK}$ |                                |                                                       | ns   |

| t <sub>DHD</sub>  | Data input hold time after SCLOCK edge <sup>2</sup>   | $2 	imes t_{UCLK}$  |                                |                                                       | ns   |

| t <sub>DF</sub>   | Data output fall time                                 |                     | 5                              | 12.5                                                  | ns   |

| t <sub>DR</sub>   | Data output rise time                                 |                     | 5                              | 12.5                                                  | ns   |

| t <sub>sr</sub>   | SCLOCK rise time                                      |                     | 5                              | 12.5                                                  | ns   |

| t <sub>SF</sub>   | SCLOCK fall time                                      |                     | 5                              | 12.5                                                  | ns   |

$^1$  t<sub>HCLK</sub> depends on the clock divider or CD bits in the PLLCON MMR, t<sub>HCLK</sub> = t<sub>UCLK</sub>/2<sup>CD</sup>.  $^2$  t<sub>UCLK</sub> = 23.9 ns. It corresponds to the 41.78 MHz internal clock from the PLL before the clock divider.

| Pin<br>No. | Mnemonic                       | Type <sup>1</sup> | Description                                                                                                                                          |

|------------|--------------------------------|-------------------|------------------------------------------------------------------------------------------------------------------------------------------------------|

| 21         | LV <sub>DD</sub>               | S                 | 2.5 V Output of the On-Chip Voltage Regulator. Must be connected to a 0.47 $\mu\text{F}$ capacitor to DGND.                                          |

| 22         | DGND                           | S                 | Ground for Core Logic.                                                                                                                               |

| 23         | P3.0/PWM1                      | I/O               | General-Purpose Input and Output Port 3.0/PWM1 Output.                                                                                               |

| 24         | P3.1/PWM2                      | I/O               | General-Purpose Input and Output Port 3.1/PWM2 Output.                                                                                               |

| 25         | P3.2/PWM3                      | I/O               | General-Purpose Input and Output Port 3.2/PWM3 Output.                                                                                               |

| 26         | P3.3/PWM4                      | I/O               | General-Purpose Input and Output Port 3.3/PWM4 Output.                                                                                               |

| 27         | P0.3/ADC <sub>BUSY</sub> /TRST | I/O               | General-Purpose Input and Output Port 3.3/ADC <sub>BUSY</sub> Signal/JTAG Test Port Input, Test Reset.<br>Debug and download access.                 |

| 28         | RST                            | 1                 | Reset Input (Active Low).                                                                                                                            |

| 29         | P3.4/PWM5                      | I/O               | General-Purpose Input and Output Port 3.4/PWM5 Output.                                                                                               |

| 30         | P3.5/PWM6                      | I/O               | General-Purpose Input and Output Port 3.5/PWM6 Output.                                                                                               |

| 31         | P0.4/IRQ0/CONVST               | I/O               | General-Purpose Input and Output Port 0.5/External Interrupt Request 0, Active High/Start Conversion Input Signal for ADC.                           |

| 32         | P0.5/IRQ1/ADC <sub>BUSY</sub>  | I/O               | General-Purpose Input and Output Port 0.6/External Interrupt Request 1, Active High/ADC <sub>BUSY</sub> Signal.                                      |

| 33         | P2.0/SPM9                      | I/O               | General-Purpose Input and Output Port 2.0/Serial Port Mux Pin 9.                                                                                     |

| 34         | P0.7/SPM8/ECLK/XCLK            | I/O               | General-Purpose Input and Output Port 0.7/Serial Port Mux Pin 8/Output for the External Clock Signal/Input to the Internal Clock Generator Circuits. |

| 35         | XCLKO                          | 0                 | Output from the Crystal Oscillator Inverter.                                                                                                         |

| 36         | XCLKI                          | 1                 | Input to the Crystal Oscillator Inverter and Input to the Internal Clock Generator Circuits.                                                         |

| 37         | PV <sub>DD</sub>               | S                 | 2.5 V PLL Supply. Must be connected to a 0.1 $\mu\text{F}$ capacitor to DGND. Should be connected to 2.5 V LDO output.                               |

| 38         | DGND                           | S                 | Ground for PLL.                                                                                                                                      |

| 39         | P1.7/SPM7                      | I/O               | General-Purpose Input and Output Port 1.7/Serial Port Mux Pin 7.                                                                                     |

| 40         | P1.6/SPM6                      | I/O               | General-Purpose Input and Output Port 1.6/Serial Port Mux Pin 6.                                                                                     |

| 43         | P4.0/S1                        | I/O               | General-Purpose Input and Output Port 4.0/Quadrature Input 1.                                                                                        |

| 44         | P4.1/S2                        | I/O               | General-Purpose Input and Output Port 4.1/Quadrature Input 2.                                                                                        |

| 45         | P1.5/SPM5                      | I/O               | General-Purpose Input and Output Port 1.5/Serial Port Mux Pin 5.                                                                                     |

| 46         | P1.4/SPM4                      | I/O               | General-Purpose Input and Output Port 1.4/Serial Port Mux Pin 4.                                                                                     |

| 47         | P1.3/SPM3                      | I/O               | General-Purpose Input and Output Port 1.3/Serial Port Mux Pin 3.                                                                                     |

| 48         | P1.2/SPM2                      | I/O               | General-Purpose Input and Output Port 1.2/Serial Port Mux Pin 2.                                                                                     |

| 49         | P1.1/SPM1                      | I/O               | General-Purpose Input and Output Port 1.1/Serial Port Mux Pin 1.                                                                                     |

| 50         | P1.0/SPM0                      | I/O               | General-Purpose Input and Output Port 1.0/Serial Port Mux Pin 0.                                                                                     |

| 51         | P4.2                           | I/O               | General-Purpose Input and Output Port 4.2.                                                                                                           |

| 52         | P4.3/ PWM <sub>TRIP</sub>      | I/O               | General-Purpose Input and Output Port 4.3/PWM Safety Cutoff.                                                                                         |

| 53         | P4.4                           | I/O               | General-Purpose Input and Output Port 4.4.                                                                                                           |

| 54         | P4.5                           | I/O               | General-Purpose Input and Output Port 4.5.                                                                                                           |

| 55         | V <sub>REF</sub>               | I/O               | 2.5 V Internal Voltage Reference. Must be connected to a 0.47 $\mu\text{F}$ capacitor when using the internal reference.                             |

| 56         | DACGND                         | S                 | Ground for the DAC. Typically connected to AGND.                                                                                                     |

| 59         | DACVDD                         | S                 | Power Supply for the DAC. This must be supplied with 2.5 V. This can be connected to the LDO output.                                                 |

| 60         | ADC0                           | I                 | Single-Ended or Differential Analog Input 0.                                                                                                         |

| 61         | ADC1                           | 1                 | Single-Ended or Differential Analog Input 1.                                                                                                         |

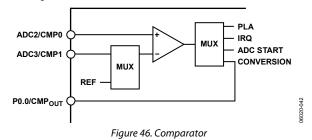

| 62         | ADC2/CMP0                      | I                 | Single-Ended or Differential Analog Input 2/Comparator Positive Input.                                                                               |

| 63         | ADC3/CMP1                      | 1                 | Single-Ended or Differential Analog Input 3/Comparator Negative Input.                                                                               |

| 64         | ADC4                           | I                 | Single-Ended or Differential Analog Input 4.                                                                                                         |

$^{1}$  I = input, O = output, S = supply.

| Pin<br>No. | Mnemonic                           | Type <sup>1</sup> | Description                                                                                                                                                                                                                                  |

|------------|------------------------------------|-------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 17         | P4.6/SPM10/AD14                    | I/O               | General-Purpose Input and Output Port 4.6/Serial Port Mux Pin 10/External Memory AD14.                                                                                                                                                       |

| 18         | P4.7/SPM11/AD15                    | I/O               | General-Purpose Input and Output Port 4.7/Serial Port Mux Pin 11/External Memory AD15.                                                                                                                                                       |

| 19         | P0.0/BM/CMP <sub>out</sub> /MS0    | I/O               | General-Purpose Input and Output Port 0.0 /Boot Mode. The ADuC7129 enters download mode if BM is low at reset and executes code if BM is pulled high at reset through a 1 k $\Omega$ resistor/voltage comparator output/external memory MS0. |

| 20         | P0.6/T1/MRST                       | 0                 | General-Purpose Output Port 0.6/Timer1 Input/Power-On Reset Output/External Memory AE.                                                                                                                                                       |

| 20         | TCK                                |                   | JTAG Test Port Input, Test Clock. Debug and download access.                                                                                                                                                                                 |

| 22         | TDO/P0.2/BHE                       | 0                 | JTAG Test Port Output, Test Clock. Debug and download access.<br>JTAG Test Port Output, Test Data Out. <u>Debug</u> and download access/general-purpose input<br>and output Port 0.2/External Memory BHE.                                    |

| 23, 53, 67 | IOGND                              | S                 | Ground for GPIO. Typically connected to DGND.                                                                                                                                                                                                |

| 24, 54     | IOV <sub>DD</sub>                  | S                 | 3.3 V Supply for GPIO and Input of the On-Chip Voltage Regulator.                                                                                                                                                                            |

| 25         | LV <sub>DD</sub>                   | S                 | 2.5 V Output of the On-Chip Voltage Regulator. Must be connected to a 0.47 μF capacitor to DGND.                                                                                                                                             |

| 26         | DGND                               | S                 | Ground for Core Logic.                                                                                                                                                                                                                       |

| 27         | P3.0/PWM1/AD0                      | I/O               | General-Purpose Input and Output Port 3.0/PWM1 Output/External Memory AD0.                                                                                                                                                                   |

| 28         | P3.1/PWM2/AD1                      | I/O               | General-Purpose Input and Output Port 3.1/PWM2 Output/External Memory AD1.                                                                                                                                                                   |

| 29         | P3.2/PWM3/AD2                      | I/O               | General-Purpose Input and Output Port 3.2/PWM3 Output/External Memory AD2.                                                                                                                                                                   |

| 30         | P3.3/PWM4/AD3                      | I/O               | General-Purpose Input and Output Port 3.3/PWM4 Output//External Memory AD3.                                                                                                                                                                  |

| 31         | P2.4/MS0                           | I/O               | General-Purpose Input and Output Port 2.4/Memory Select 0.                                                                                                                                                                                   |

| 32         | P0.3/ADC <sub>BUSY</sub> /TRST/A16 | I/O               | General-Purpose Input and Output Port 3.3/ADC <sub>BUSY</sub> Signal/JTAG Test Port Input, Test Reset.<br>Debug and download access/External Memory A16.                                                                                     |

| 33         | P2.5/MS1                           | I/O               | General-Purpose Input and Output Port 2.5/Memory Select 1.                                                                                                                                                                                   |

| 34         | P2.6/MS2                           | I/O               | General-Purpose Input and Output Port 2.6/Memory Select 2.                                                                                                                                                                                   |

| 35         | RST                                | 1                 | Reset Input (Active Low).                                                                                                                                                                                                                    |

| 36         | P3.4/PWM5/AD4                      | I/O               | General-Purpose Input and Output Port 3.4/PWM5 Output/External Memory AD4.                                                                                                                                                                   |

| 37         | P3.5/PWM6/AD5                      | I/O               | General-Purpose Input and Output Port 3.5/PWM6 Output/External Memory AD5.                                                                                                                                                                   |

| 38         | P0.4/IRQ0/CONVST/MS1               | 1/0               | General-Purpose Input and Output Port 0.5/External Interrupt Request 0, Active High/Start<br>Conversion Input Signal for ADC/External Memory MS1.                                                                                            |

| 39         | P0.5/IRQ1/ADC <sub>BUSY</sub>      | I/O               | General-Purpose Input and Output Port 0.6/External Interrupt Request 1, Active High/ADC <sub>BUSY</sub> Signal.                                                                                                                              |

| 40         | P2.0/SPM9                          | I/O               | General-Purpose Input and Output Port 2.0/Serial Port Mux Pin 9.                                                                                                                                                                             |

| 41         | P0.7/SPM8/ECLK/XCLK                | I/O               | General-Purpose Input and Output Port 0.7/Serial Port Mux Pin 8/Output for the External Clock Signal/Input to the Internal Clock Generator Circuits.                                                                                         |

| 42         | XCLKO                              | 0                 | Output from the Crystal Oscillator Inverter.                                                                                                                                                                                                 |

| 43<br>44   | XCLKI<br>PV <sub>DD</sub>          | I<br>S            | Input to the Crystal Oscillator Inverter and Input to the Internal Clock Generator Circuits.<br>2.5 V PLL Supply. Must be connected to a 0.1 μF capacitor to DGND. Should be connected<br>to 2.5 V LDO output.                               |

| 45         | DGND                               | s                 | Ground for PLL.                                                                                                                                                                                                                              |

| 45         | P3.6/AD6                           | J/O               | General-Purpose Input and Output Port 3.6/External Memory AD6.                                                                                                                                                                               |

| 47         | P3.7/AD7                           | 1/O               | General-Purpose Input and Output Fort 3.7/External Memory ADO.                                                                                                                                                                               |

| 48         | P2.7/MS3                           | 1/O               | General-Purpose Input and Output Port 2.7/Memory Select 3.                                                                                                                                                                                   |

| 49         | P2.1/WS                            | I/O               | General-Purpose Input and Output Fort 2.1/Memory Write Select.                                                                                                                                                                               |

| 50         | P2.2/RS                            | I/O               | General-Purpose Input and Output Port 2.1/Memory Read Select.                                                                                                                                                                                |

| 50         | P1.7/SPM7                          | I/O               | General-Purpose Input and Output Port 1.7/Serial Port Mux Pin 7.                                                                                                                                                                             |

| 52         | P1.6/SPM6                          | 1/O               | General-Purpose Input and Output Port 1.6/Serial Port Mux Pin 6.                                                                                                                                                                             |

| 55         | P4.0/S1/AD8                        | I/O               | General-Purpose Input and Output Port 4.0/Quadrature Input 1/External Memory AD8.                                                                                                                                                            |

| 56         | P4.1/S2/AD9                        | I/O               | General-Purpose Input and Output Port 4.1/Quadrature Input 7/External Memory AD9.                                                                                                                                                            |

| 57         | P1.5/SPM5                          | I/O               | General-Purpose Input and Output Port 1.5/Serial Port Mux Pin 5.                                                                                                                                                                             |

| 58         | P1.4/SPM4                          | I/O               | General-Purpose Input and Output Port 1.4/Serial Port Mux Pin 4.                                                                                                                                                                             |

| 59         | P1.3/SPM3                          | I/O               | General-Purpose Input and Output Port 1.3/Serial Port Mux Pin 3.                                                                                                                                                                             |

| 60         | P1.2/SPM2                          | I/O               | General-Purpose Input and Output Port 1.2/Serial Port Mux Pin 2.                                                                                                                                                                             |

| 61         | P1.1/SPM1                          | I/O               | General-Purpose Input and Output Port 1.1/Serial Port Mux Pin 1.                                                                                                                                                                             |

| 62         | P1.0/SPM0                          | I/O               | General-Purpose Input and Output Port 1.0/Serial Port Mux Pin 0.                                                                                                                                                                             |

### TERMINOLOGY ADC SPECIFICATIONS

### **Integral Nonlinearity**

The maximum deviation of any code from a straight line passing through the endpoints of the ADC transfer function. The endpoints of the transfer function are zero scale, a point ½ LSB below the first code transition and full scale, a point ½ LSB above the last code transition.

### **Differential Nonlinearity**

The difference between the measured and the ideal 1 LSB change between any two adjacent codes in the ADC.

### **Offset Error**

The deviation of the first code transition (0000 . . . 000) to (0000 . . . 001) from the ideal, that is,  $+\frac{1}{2}$  LSB.

### **Gain Error**

The deviation of the last code transition from the ideal AIN voltage (full scale – 1.5 LSB) after the offset error has been adjusted out.

### Signal to (Noise + Distortion) Ratio

The measured ratio of signal to (noise + distortion) at the output of the ADC. The signal is the rms amplitude of the fundamental. Noise is the rms sum of all nonfundamental signals up to half the sampling frequency ( $f_s/2$ ), excluding dc. The ratio is dependent on the number of quantization levels in the digitization process; the more levels, the smaller the quantization noise.

The theoretical signal to (noise + distortion) ratio for an ideal N-bit converter with a sine wave input is given by

Signal to (Noise + Distortion) = (6.02 N + 1.76) dB

Thus, for a 12-bit converter, this is 74 dB.

### Total Harmonic Distortion

The ratio of the rms sum of the harmonics to the fundamental.

### DAC SPECIFICATIONS

### **Relative Accuracy**

Otherwise known as endpoint linearity, relative accuracy is a measure of the maximum deviation from a straight line passing through the endpoints of the DAC transfer function. It is measured after adjusting for zero error and full-scale error.

### Voltage Output Settling Time

The amount of time it takes for the output to settle to within a 1 LSB level for a full-scale input change.

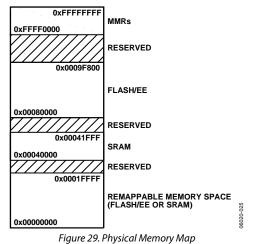

### **MEMORY ORGANIZATION**

The ADuC7128/ADuC7129 incorporate three separate blocks of memory: 8 kB of SRAM and two 64 kB of on-chip Flash/EE memory. There are 126 kB of on-chip Flash/EE memory available to the user, and the remaining 2 kB are reserved for the factory-configured boot page. These two blocks are mapped as shown in Figure 29.

Note that by default, after a reset, the Flash/EE memory is mirrored at Address 0x00000000. It is possible to remap the SRAM at Address 0x00000000 by clearing Bit 0 of the REMAP MMR. This remap function is described in more detail in the Flash/EE Memory section.

### **MEMORY ACCESS**

The ARM7 core sees memory as a linear array of  $2^{32}$  byte locations where the different blocks of memory are mapped as outlined in Figure 29.

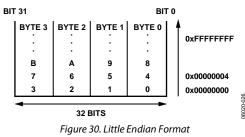

The ADuC7128/ADuC7129 memory organization is configured in little endian format: the least significant byte is located in the lowest byte address and the most significant byte in the highest byte address.

### **FLASH/EE MEMORY**

The 128 kB of Flash/EE is organized as two banks of 32 k  $\times$  16 bits. In the first block, 31 k  $\times$  16 bits are user space and 1 k  $\times$  16 bits is reserved for the factory-configured boot page. The page size of this Flash/EE memory is 512 bytes.

The second 64 kB block is organized in a similar manner. It is arranged in 32 k  $\times$  16 bits. All of this is available as user space.

The 126 kB of Flash/EE is available to the user as code and nonvolatile data memory. There is no distinction between data and program as ARM code shares the same space. The real width of the Flash/EE memory is 16 bits, meaning that in ARM mode (32-bit instruction), two accesses to the Flash/EE are necessary for each instruction fetch. Therefore, it is recommended that Thumb mode be used when executing from Flash/EE memory for optimum access speed. The maximum access speed for the Flash/EE memory is 41.78 MHz in Thumb mode and 20.89 MHz in full ARM mode (see the Execution Time from SRAM and FLASH/EE section).

### SRAM

The 8 kB of SRAM are available to the user, organized as 2 k  $\times$  32 bits, that is, 2 k words. ARM code can run directly from SRAM at 41.78 MHz, given that the SRAM array is configured as a 32-bit wide memory array (see the Execution Time from SRAM and FLASH/EE section).

### MEMORY MAPPED REGISTERS

The memory mapped register (MMR) space is mapped into the upper two pages of the memory array and accessed by indirect addressing through the ARM7 banked registers.

The MMR space provides an interface between the CPU and all on-chip peripherals. All registers except the core registers reside in the MMR area. All shaded locations shown in Figure 31 are unoccupied or reserved locations and should not be accessed by user software. See Table 12 through Table 31 for a full MMR memory map.

The access time reading or writing a MMR depends on the advanced microcontroller bus architecture (AMBA) bus used to access the peripheral. The processor has two AMBA buses: advanced high performance bus (AHB) used for system modules, and advanced peripheral bus (APB) used for lower performance peripherals. Access to the AHB is one cycle, and access to the APB is two cycles. All peripherals on the ADuC7128/ADuC7129 are on the APB except the Flash/EE memory and the GPIOs.

### FEE1DAT Register

| Name    | Address    | Default Value | Access |

|---------|------------|---------------|--------|

| FEE1DAT | 0xFFFF0E8C | 0xXXXX        | R/W    |

|         |            |               |        |

FEE1DAT is a 16-bit data register.

### FEE1ADR Register

| Name    | Address    | Default Value | Access |

|---------|------------|---------------|--------|

| FEE1ADR | 0xFFFF0E90 | 0x0000        | R/W    |

FEE1ADR is a 16-bit address register.

### FEE1SGN Register

| Name    | Address    | Default Value | Access |

|---------|------------|---------------|--------|

| FEE1SGN | 0xFFFF0E98 | 0xFFFFFF      | R      |

FEE1SGN is a 24-bit code signature.

### FEE1PRO Register

| Name    | Address    | Default Value | Access |

|---------|------------|---------------|--------|

| FEE1PRO | 0xFFFF0E9C | 0x0000000     | R/W    |

FEE1PRO provides protection following subsequent reset MMR. It requires a software key (see Table 45).

### FEE1HID Register

| Name    | Address    | Default Value | Access |

|---------|------------|---------------|--------|

| FEE1HID | 0xFFFF0EA0 | 0xFFFFFFF     | R/W    |

FEE1HID provides immediate protection MMR. It does not require any software keys (see Table 45).

### FEE0STA Register

| Name    | Address    | Default Value | Access |

|---------|------------|---------------|--------|

| FEE0STA | 0xFFFF0E00 | 0x0000        | R/W    |

### FEE1STA Register

| Name    | Address    | Default Value | Access |

|---------|------------|---------------|--------|

| FEE1STA | 0xFFFF0E80 | 0x0000        | R/W    |

### FEE0MOD Register

| Name Address   |            | Default Value | Access |

|----------------|------------|---------------|--------|

| <b>FEE0MOD</b> | 0xFFFF0E04 | 0x80          | R/W    |

### FEE1MOD Register

| Name Address |            | Default Value | Access |

|--------------|------------|---------------|--------|

| FEE1MOD      | 0xFFFF0E84 | 0x80          | R/W    |

### **FEE0CON** Register

| Name Address   |            | Default Value | Access |

|----------------|------------|---------------|--------|

| <b>FEE0CON</b> | 0xFFFF0E08 | 0x0000        | R/W    |

### FEE1CON Register

| Name    | Address    | Default Value | Access |

|---------|------------|---------------|--------|

| FEE1CON | 0xFFFF0E88 | 0x0000        | R/W    |

### DDSFRQ Register

| Name   | Address    | Default Value | Access |

|--------|------------|---------------|--------|

| DDSFRQ | 0xFFFF0694 | 0x0000000     | R/W    |

### Table 54. DDSFRQ MMR Bit Designations

| Bit  | Description                 |  |

|------|-----------------------------|--|

| 31:0 | Frequency select word (FSW) |  |

The DDS frequency is controlled via the DDSFRQ MMR. This MMR contains a 32-bit word (FSW) that controls the frequency according to the following formula:

$$Frequency = \frac{FSW \times 20.8896 \text{ MHz}}{2^{32}}$$

### DDSPHS Register

| Name   | Address    | Default Value | Access |

|--------|------------|---------------|--------|

| DDSPHS | 0xFFFF0698 | 0x0000000     | R/W    |

Table 55. DDSPHS MMR Bit Designations

| Bit   | Description |

|-------|-------------|

| 31:12 | Reserved    |

| 11:0  | Phase       |

The DDS phase offset is controlled via the DDSPHS MMR. This MMR contains a 12-bit value that controls the phase of the DDS output according to the following formula:

*Phase Offset* =

$$\frac{2 \times \pi \times Phase}{2^{12}}$$

### POWER SUPPLY MONITOR

The power supply monitor on the ADuC7128/ADuC7129 indicates when the  $IOV_{DD}$  supply pin drops below one of two supply trip points. The monitor function is controlled via the PSMCON register (see Table 56). If enabled in the IRQEN or FIQEN register, the monitor interrupts the core using the PSMI bit in the PSMCON MMR. This bit is cleared immediately once CMP goes high. Note that if the interrupt generated is exited before CMP goes high (IOV<sub>DD</sub> is above the trip point), no further interrupts are generated until CMP returns high. The user should ensure that code execution remains within the ISR until CMP returns high.

| Bit | Name  | Description                                                                                                                                                                                                                                                                                                                                                                  |

|-----|-------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 3   | СМР   | Comparator Bit. This is a read-only bit that directly reflects the state of the comparator.<br>Read 1 indicates the IOV <sub>DD</sub> supply is above its selected trip point or the PSM is in power-down mode.<br>Read 0 indicates the IOV <sub>DD</sub> supply is below its selected trip point. This bit should be set before leaving<br>the interrupt service routine.   |

| 2   | TP    | Trip Point Selection Bit.<br>0 = 2.79 V<br>1 = 3.07 V                                                                                                                                                                                                                                                                                                                        |

| 1   | PSMEN | Power Supply Monitor Enable Bit.<br>Set to 1 by the user to enable the power supply monitor circuit.<br>Cleared to 0 by the user to disable the power supply monitor circuit.                                                                                                                                                                                                |

| 0   | PSMI  | Power Supply Monitor Interrupt Bit. This bit is set high by the MicroConverter if CMP is low, indicating low I/O supply. The PSMI bit can be used to interrupt the processor. Once CMP returns high, the PSMI bit can be cleared by writing a 1 to this location. A write of 0 has no effect. There is no timeout delay. PSMI can be cleared immediately once CMP goes high. |

### Table 56. PSMCON MMR Bit Designations

This monitor function allows the user to save working registers to avoid possible data loss due to the low supply or brown-out conditions. It also ensures that normal code execution does not resume until a safe supply level has been established.

The PSM does not operate correctly when using JTAG debug. It should be disabled in JTAG debug mode.

### COMPARATOR

The ADuC7128/ADuC7129 integrate an uncommitted voltage comparator. The positive input is multiplexed with ADC2, and the negative input has two options: ADC3 or the internal reference. The output of the comparator can be configured to generate a system interrupt, can be routed directly to the programmable logic array, can start an ADC conversion, or can be on an external pin, CMP<sub>OUT</sub>.

### Hysteresis

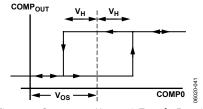

Figure 47 shows how the input offset voltage and hysteresis terms are defined. Input offset voltage ( $V_{OS}$ ) is the difference between the center of the hysteresis range and the ground level. This can either be positive or negative. The hysteresis voltage ( $V_H$ ) is  $\frac{1}{2}$  the width of the hysteresis range.

Figure 47. Comparator Hysteresis Transfer Function

### **Comparator Interface**

The comparator interface consists of a 16-bit MMR, CMPCON, described in Table 57.

| Bit   | Value | Name    | Description                                                                                                                                                                                                                                          |

|-------|-------|---------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 15:11 |       |         | Reserved.                                                                                                                                                                                                                                            |

| 10    |       | CMPEN   | Comparator Enable Bit.<br>Set by user to enable the comparator.<br>Cleared by user to disable the comparator.<br>Note: A comparator interrupt is generated on the enable of the comparator. This should be cleared in the<br>user software.          |

| 9:8   |       | CMPIN   | Comparator Negative Input Select Bits.                                                                                                                                                                                                               |

|       | 00    |         | AVDD/2.                                                                                                                                                                                                                                              |

|       | 01    |         | ADC3 input.                                                                                                                                                                                                                                          |

|       | 10    |         | $V_{REF} \times 0.6.$                                                                                                                                                                                                                                |

|       | 11    |         | Reserved.                                                                                                                                                                                                                                            |

| 7:6   |       | CMPOC   | Comparator Output Configuration Bits.                                                                                                                                                                                                                |

|       | 00    |         | IRQ and PLA connections disabled.                                                                                                                                                                                                                    |

|       | 01    |         | IRQ and PLA connections disabled.                                                                                                                                                                                                                    |

|       | 10    |         | PLA connections enabled.                                                                                                                                                                                                                             |

|       | 11    |         | IRQ connections enabled.                                                                                                                                                                                                                             |

| 5     |       | CMPOL   | Comparator Output Logic State Bit.<br>When low, the comparator output is high when the positive input (CMP0) is above the negative<br>input (CMP1).<br>When high, the comparator output is high when the positive input is below the negative input. |

| 4:3   |       | CMPRES  | Response Time.                                                                                                                                                                                                                                       |

|       | 00    |         | 5 μs response time typical for large signals (2.5 V differential).<br>17 μs response time typical for small signals (0.65 mV differential).                                                                                                          |

|       | 01    |         | Reserved.                                                                                                                                                                                                                                            |

|       | 10    |         | Reserved.                                                                                                                                                                                                                                            |

|       | 11    |         | 3 μs response time typical for any signal type.                                                                                                                                                                                                      |

| 2     |       | CMPHYST | Comparator Hysteresis Bit.<br>Set by user to have a hysteresis of about 7.5 mV.<br>Cleared by user to have no hysteresis.                                                                                                                            |

| 1     |       | CMPORI  | Comparator Output Rising Edge Interrupt.<br>Set automatically when a rising edge occurs on the monitored voltage (CMP0).<br>Cleared by user by writing a 1 to this bit.                                                                              |

| 0     |       | CMPOFI  | Comparator Output Falling Edge Interrupt.<br>Set automatically when a falling edge occurs on the monitored voltage (CMP0).<br>Cleared by user.                                                                                                       |

### Table 57. CMPCON MMR Bit Designations

### **GPxDAT** Reaister

| Name   | Address    | Default Value | Access |

|--------|------------|---------------|--------|

| GP0DAT | 0xFFFF0D20 | 0x000000XX    | R/W    |

| GP1DAT | 0xFFFF0D30 | 0x000000XX    | R/W    |

| GP2DAT | 0xFFFF0D40 | 0x000000XX    | R/W    |

| GP3DAT | 0xFFFF0D50 | 0x000000XX    | R/W    |

| GP4DAT | 0xFFFF0D60 | 0x00000XX     | R/W    |

GPxDAT is a Port x configuration and data register. It configures the direction of the GPIO pins of Port x, sets the output value for the pins configured as output, and receives and stores the input value of the pins configured as input.

### Table 73. GPxDAT MMR Bit Designations

| Bit   | Description                                                                                                                                        |

|-------|----------------------------------------------------------------------------------------------------------------------------------------------------|

| 31:24 | Direction of the Data.<br>Set to 1 by user to configure the GPIO pins as outputs.<br>Cleared to 0 by user to configure the GPIO pins as<br>inputs. |

| 23:16 | Port x Data Output.                                                                                                                                |

| 15:8  | Reflect the state of Port x pins at reset (read only).                                                                                             |

| 7:0   | Port x Data Input (Read Only).                                                                                                                     |

### **GPxSET** Reaister

| Name          | Address    | Default Value | Access |  |  |  |

|---------------|------------|---------------|--------|--|--|--|

| GP0SET        | 0xFFFF0D24 | 0x000000XX    | W      |  |  |  |

| GP1SET        | 0xFFFF0D34 | 0x000000XX    | W      |  |  |  |

| GP2SET        | 0xFFFF0D44 | 0x000000XX    | W      |  |  |  |

| <b>GP3SET</b> | 0xFFFF0D54 | 0x000000XX    | W      |  |  |  |

| GP4SET        | 0xFFFF0D64 | 0x000000XX    | W      |  |  |  |

|               |            |               |        |  |  |  |

GPxSET is a data set Port x register.

### Table 74. GPxSET MMR Bit Designations

| Bit   | Description                                                                                                                                                                 |

|-------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 31:24 | Reserved.                                                                                                                                                                   |

| 23:16 | Data Port x Set Bit.<br>Set to 1 by user to set bit on Port x; also sets the<br>corresponding bit in the GPxDAT MMR.<br>Cleared to 0 by user; does not affect the data out. |

| 15:0  | Reserved.                                                                                                                                                                   |

### **GPxCLR** Reaister

| Name   | Address    | Default Value | Access |

|--------|------------|---------------|--------|

| GP0CLR | 0xFFFF0D28 | 0x000000XX    | W      |

| GP1CLR | 0xFFFF0D38 | 0x000000XX    | W      |

| GP2CLR | 0xFFFF0D48 | 0x000000XX    | W      |

| GP3CLR | 0xFFFF0D58 | 0x000000XX    | W      |

| GP4CLR | 0xFFFF0D68 | 0x000000XX    | W      |

GPxCLR is a data clear Port x register.

### Table 75. GPxCLR MMR Bit Designations

| Bit   | Description                                                                                                                                                                       |

|-------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 31:24 | Reserved.                                                                                                                                                                         |

| 23:16 | Data Port x Clear Bit.<br>Set to 1 by user to clear bit on Port x; also clears<br>the corresponding bit in the GPxDAT MMR.<br>Cleared to 0 by user; does not affect the data out. |

| 15:0  | Reserved.                                                                                                                                                                         |

### SERIAL PORT MUX

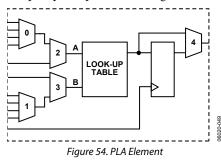

The serial port mux multiplexes the serial port peripherals (two I<sup>2</sup>Cs, an SPI, and two UARTs) and the programmable logic array (PLA) to a set of 10 GPIO pins. Each pin must be configured to its specific I/O function as described in Table 76.

#### **Table 76. SPM Configuration**

|       | GPIO              | UART    | UART/I2C/SPI | PLA      |

|-------|-------------------|---------|--------------|----------|

| Pin   | (00)              | (01)    | (10)         | (11)     |

| SPM0  | P1.0              | SIN0    | I2C0SCL      | PLAI[0]  |

| SPM1  | P1.1              | SOUT0   | I2C0SDA      | PLAI[1]  |

| SPM2  | P1.2              | RTS0    | I2C1SCL      | PLAI[2]  |

| SPM3  | P1.3              | CTS0    | I2C1SDA      | PLAI[3]  |

| SPM4  | P1.4              | RIO     | SPICLK       | PLAI[4]  |

| SPM5  | P1.5              | DCD0    | SPIMISO      | PLAI[5]  |

| SPM6  | P1.6              | DSR0    | SPIMOSI      | PLAI[6]  |

| SPM7  | P1.7              | DTR0    | SPICSL       | PLAO[0]  |

| SPM8  | P0.7              | ECLK    | SIN0         | PLAO[4]  |

| SPM9  | P2.0 <sup>1</sup> | PWMSYNC | SOUT0        | PLAO[5]  |

| SPM10 | P2.2 <sup>1</sup> | RTS1    | RS           | PLAO[7]  |

| SPM11 | P2.3 <sup>1</sup> | CTS1    | AE           |          |

| SPM12 | P2.4 <sup>1</sup> | RI1     | MS0          |          |

| SPM13 | P2.5 <sup>1</sup> | DCD1    | MS1          |          |

| SPM14 | P2.6 <sup>1</sup> | DSR1    | MS2          |          |

| SPM15 | P2.7 <sup>1</sup> | DTR1    | MS3          |          |

| SPM16 | P4.6              | SIN1    | AD14         | PLAO[14] |

| SPM17 | P4.7              | SOUT1   | AD15         | PLAO[15] |

<sup>1</sup> Available only on the 80-lead ADuC7129.

Table 76 details the mode for each of the SPMUX GPIO pins. This configuration has to be performed via the GP0CON, GP1CON and GP2CON MMRs. By default these pins are configured as GPIOs.

### **UART SERIAL INTERFACE**

The ADuC7128/ADuC7129 contain two identical UART blocks. Although only UART0 is described here, UART1 functions in exactly the same way.

The UART peripheral is a full-duplex universal asynchronous receiver/transmitter, fully compatible with the 16450 serial port standard.

The UART performs serial-to-parallel conversion on data characters received from a peripheral device or a modem, and parallel-to-serial conversion on data characters received from the CPU. The UART includes a fractional divider for baud rate generation and has a network-addressable mode. The UART function is made available on 10 pins of the ADuC7128/ ADuC7129 (see Table 77).

# Table 80. COMxCON0 MMR Bit Designations Bit Value Name Description

| Bit | Value | Name | Description                                                                                                                                                                                                                     |

|-----|-------|------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7   |       | DLAB | Divisor Latch Access.                                                                                                                                                                                                           |

|     |       |      | Set by user to enable access to COMxDIV0 and COMxDIV1 registers.                                                                                                                                                                |

|     |       |      | Cleared by user to disable access to COMxDIV0 and COMxDIV1 and enable access to COMxRX and COMxTX.                                                                                                                              |

| 6   |       | BRK  | Set Break.                                                                                                                                                                                                                      |

|     |       |      | Set by user to force SOUT to 0.                                                                                                                                                                                                 |

|     |       |      | Cleared to operate in normal mode.                                                                                                                                                                                              |

| 5   |       | SP   | Stick Parity.                                                                                                                                                                                                                   |

|     |       |      | Set by user to force parity to defined values.                                                                                                                                                                                  |

|     |       |      | 1 if $EPS = 1$ and $PEN = 1$                                                                                                                                                                                                    |

|     |       |      | 0 if EPS = 0 and PEN = 1                                                                                                                                                                                                        |

| 4   |       | EPS  | Even Parity Select Bit.                                                                                                                                                                                                         |

|     |       |      | Set for even parity.                                                                                                                                                                                                            |

|     |       |      | Cleared for odd parity.                                                                                                                                                                                                         |

| 3   |       | PEN  | Parity Enable Bit.                                                                                                                                                                                                              |

|     |       |      | Set by user to transmit and check the parity bit.                                                                                                                                                                               |

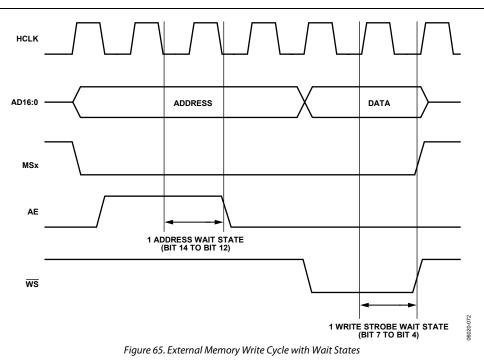

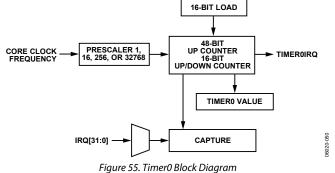

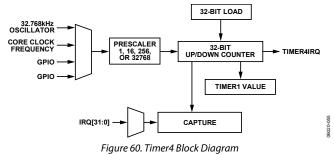

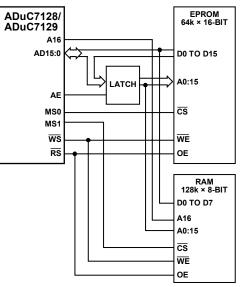

|     |       |      | Cleared by user for no parity transmission or checking.                                                                                                                                                                         |