Welcome to E-XFL.COM

Embedded - Microcontrollers - Application Specific: Tailored Solutions for Precision and Performance

### Embedded - Microcontrollers - Application Specific

represents a category of microcontrollers designed with unique features and capabilities tailored to specific application needs. Unlike general-purpose microcontrollers, application-specific microcontrollers are optimized for particular tasks, offering enhanced performance, efficiency, and functionality to meet the demands of specialized applications.

### What Are <u>Embedded - Microcontrollers -</u> <u>Application Specific</u>?

Application enacific microcontrollars are angineered to

### Details

| Details                 |                                                                           |

|-------------------------|---------------------------------------------------------------------------|

| Product Status          | Active                                                                    |

| Applications            | SuperSpeed USB Peripheral Controller                                      |

| Core Processor          | ARM9®                                                                     |

| Program Memory Type     | External Program Memory                                                   |

| Controller Series       | CYUSB                                                                     |

| RAM Size                | 512K x 8                                                                  |

| Interface               | I <sup>2</sup> C, I <sup>2</sup> S, MMC/SD, SPI, UART, USB                |

| Number of I/O           | 59                                                                        |

| Voltage - Supply        | 1.15V ~ 1.25V                                                             |

| Operating Temperature   | 0°C ~ 70°C                                                                |

| Mounting Type           | Surface Mount                                                             |

| Package / Case          | 121-TFBGA                                                                 |

| Supplier Device Package | 121-FBGA (10x10)                                                          |

| Purchase URL            | https://www.e-xfl.com/product-detail/infineon-technologies/cyusb2014-bzxc |

|                         |                                                                           |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# CYUSB301X/CYUSB201X

# Contents

| Functional Overview               | 5  |

|-----------------------------------|----|

| Application Examples              | 5  |

| USB Interface                     | 6  |

| OTG                               | 6  |

| ReNumeration                      | 7  |

| EZ-Dtect                          | 7  |

| VBUS Overvoltage Protection       | 7  |

| Carkit UART Mode                  | 7  |

| GPIF II                           | 8  |

| CPU                               | 8  |

| JTAG Interface                    | 8  |

| Other Interfaces                  | 8  |

| SPI Interface                     | 8  |

| UART Interface                    | 9  |

| I2C Interface                     | 9  |

| I2S Interface                     | 9  |

| Boot Options                      | 9  |

| Reset                             | 9  |

| Hard Reset                        |    |

| Soft Reset                        | 9  |

| Clocking                          | 10 |

| 32-kHz Watchdog Timer Clock Input | 10 |

| Power                             |    |

| Power Modes                       |    |

| Digital I/Os                      | 13 |

| GPIOs                             | 13 |

| System-level ESD                  |    |

| Pin Configurations                |    |

|                                   |    |

| Pin Description                          | 15 |

|------------------------------------------|----|

| Electrical Specifications                |    |

| Absolute Maximum Ratings                 |    |

| Operating Conditions                     |    |

| DC Specifications                        |    |

| AC Timing Parameters                     |    |

| GPIF II Timing                           |    |

| Slave FIFO Interface                     |    |

| Host Processor Interface (P-Port) Timing |    |

| Serial Peripherals Timing                |    |

| Reset Sequence                           |    |

| Package Diagram                          | 43 |

| Ordering Information                     | 45 |

| Ordering Code Definitions                | 45 |

| Acronyms                                 |    |

| Document Conventions                     |    |

| Units of Measure                         |    |

| Errata                                   | 47 |

| Qualification Status                     | 47 |

| Errata Summary                           | 47 |

| Document History Page                    | 50 |

| Sales, Solutions, and Legal Information  | 54 |

| Worldwide Sales and Design Support       |    |

| Products                                 |    |

| PSoC®Solutions                           | 54 |

| Cypress Developer Community              | 54 |

| Technical Support                        | 54 |

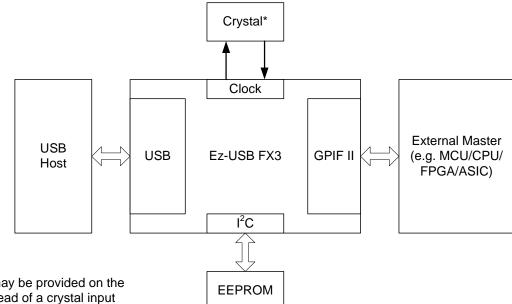

Figure 2. EZ-USB FX3 as a Coprocessor

\* A clock input may be provided on the CLKIN pin instead of a crystal input

# **USB** Interface

FX3 complies with the following specifications and supports the following features:

- Supports USB peripheral functionality compliant with USB 3.1 Specification Revision 1.0 and is also backward compatible with the USB 2.0 Specification.

- FX3 Hi-Speed parts (CYUSB201X) only support USB 2.0.

- Complies with OTG Supplement Revision 2.0. It supports High-Speed, Full-Speed, and Low-Speed OTG dual-role device capability. As a peripheral, FX3 is capable of SuperSpeed, High-Speed, and Full-Speed. As a host, it is capable of High-Speed, Full-Speed, and Low-Speed.

- Supports Carkit Pass-Through UART functionality on USB D+/D- lines based on the CEA-936A specification.

- Supports 16 IN and 16 OUT endpoints.

- Supports the USB 3.0 Streams feature. It also supports USB Attached SCSI (UAS) device-class to optimize mass-storage access performance.

- As a USB peripheral, application examples show that the FX3 supports UAS, USB Video Class (UVC), and Mass Storage Class (MSC) USB peripheral classes. All other device classes can be supported by customer firmware; a template example is provided as a starting point.

- As an OTG host, application examples show that FX3 supports MSC and HID device classes.

Note When the USB port is not in use, disable the PHY and transceiver to save power.

# OTG

FX3 is compliant with the OTG Specification Revision 2.0. In OTG mode, FX3 supports both A and B device modes and supports Control, Interrupt, Bulk, and Isochronous data transfers.

FX3 requires an external charge pump (either standalone or integrated into a PMIC) to power VBUS in the OTG A-device mode.

The Target Peripheral List for OTG host implementation consists of MSC- and HID-class devices.

FX3 does not support Attach Detection Protocol (ADP).

### OTG Connectivity

In OTG mode, FX3 can be configured to be an A, B, or dual-role device. It can connect to the following:

- ACA device

- Targeted USB peripheral

- SRP-capable USB peripheral

- HNP-capable USB peripheral

- OTG host

- HNP-capable host

- OTG device

# Clocking

FX3 allows either a crystal to be connected between the XTALIN and XTALOUT pins or an external clock to be connected at the CLKIN pin. The XTALIN, XTALOUT, CLKIN, and CLKIN\_32 pins can be left unconnected if they are not used.

Crystal frequency supported is 19.2 MHz, while the external clock frequencies supported are 19.2, 26, 38.4, and 52 MHz.

FX3 has an on-chip oscillator circuit that uses an external 19.2-MHz (±100 ppm) crystal (when the crystal option is used). An appropriate load capacitance is required with a crystal. Refer to the specification of the crystal used to determine the appropriate load capacitance. The FSLC[2:0] pins must be configured appropriately to select the crystal- or clock-frequency option. The configuration options are shown in Table 3.

Clock inputs to FX3 must meet the phase noise and jitter requirements specified in Table 4 on page 10.

The input clock frequency is independent of the clock and data rate of the FX3 core or any of the device interfaces. The internal PLL applies the appropriate clock multiply option depending on the input frequency.

Table 3. Crystal/Clock Frequency Selection

| FSLC[2] | FSLC[1] | FSLC[0] | Crystal/Clock<br>Frequency |

|---------|---------|---------|----------------------------|

| 0       | 0       | 0       | 19.2-MHz crystal           |

| 1       | 0       | 0       | 19.2-MHz input CLK         |

| 1       | 0       | 1       | 26-MHz input CLK           |

| 1       | 1       | 0       | 38.4-MHz input CLK         |

| 1       | 1       | 1       | 52-MHz input CLK           |

### Table 4. FX3 Input Clock Specifications

| Parameter                   | Description    | Specif | Units |       |

|-----------------------------|----------------|--------|-------|-------|

| Farameter                   | Description    | Min    | Max   | Units |

|                             | 100-Hz offset  | -      | -75   |       |

|                             | 1-kHz offset   | -      | -104  |       |

| Phase noise                 | 10-kHz offset  | -      | -120  | dB    |

|                             | 100-kHz offset | -      | -128  |       |

|                             | 1-MHz offset   | -      | -130  |       |

| Maximum frequency deviation | -              | -      | 150   | ppm   |

| Duty cycle                  | -              | 30     | 70    |       |

| Overshoot                   | -              | -      | 3     | %     |

| Undershoot                  | -              | -      | -3    |       |

| Rise time/fall time         | _              | _      | 3     | ns    |

### 32-kHz Watchdog Timer Clock Input

FX3 includes a watchdog timer. The watchdog timer can be used to interrupt the ARM926EJ-S core, automatically wake up the FX3 in Standby mode, and reset the ARM926EJ-S core. The watchdog timer runs a 32-kHz clock, which may be optionally supplied from an external source on a dedicated FX3 pin.

The firmware can disable the watchdog timer. Requirements for the optional 32-kHz clock input are listed in Table 5.

### Table 5. 32-kHz Clock Input Requirements

| Parameter           | Min | Max  | Units |

|---------------------|-----|------|-------|

| Duty cycle          | 40  | 60   | %     |

| Frequency deviation | -   | ±200 | ppm   |

| Rise time/fall time | -   | 200  | ns    |

| BGA | WLCSP | Power<br>Domain | I/O | Name | Description |

|-----|-------|-----------------|-----|------|-------------|

| B9  | E4    | -               | PWR | VSS  | -           |

| F11 | F6    | -               | PWR | VDD  | -           |

| -   | E5    | -               | PWR | VSS  | GND         |

| -   | F7    | -               | PWR | VDD  | -           |

| -   | E6    | -               | PWR | VSS  | GND         |

| -   | E7    | -               | PWR | VSS  | GND         |

| H1  | G6    | -               | PWR | VDD  | -           |

| L7  | D7    | -               | PWR | VDD  | -           |

| J11 | L10   | -               | PWR | VDD  | -           |

| L5  | L12   | -               | PWR | VDD  | -           |

| K4  | H7    | -               | PWR | VSS  | -           |

| L3  | G7    | -               | PWR | VSS  | -           |

| K3  | L11   | -               | PWR | VSS  | -           |

| L2  | G8    | -               | PWR | VSS  | -           |

| A8  | G5    | _               | PWR | VSS  | -           |

| _   | B4    | _               | —   | NC   | No Connect  |

| A11 | B2    | _               | —   | NC   | No Connect  |

# Table 7. CYUSB3012 and CYUSB3014 Pin List (continued)

# Table 8. DC Specifications (continued)

| Parameter            | Description                                                                      | Min       | Max       | Units | Notes                                                                                                                                                                        |

|----------------------|----------------------------------------------------------------------------------|-----------|-----------|-------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| V <sub>OH</sub>      | Output HIGH voltage                                                              | 0.9 × VCC | _         | V     | $I_{OH}$ (max) = -100 µA tested at quarter drive<br>strength. VCC is the corresponding I/O<br>voltage supply.                                                                |

| V <sub>OL</sub>      | Output LOW voltage                                                               | _         | 0.1 × VCC | V     | $I_{OL}$ (min) = +100 µA tested at quarter drive<br>strength. VCC is the corresponding I/O<br>voltage supply.                                                                |

| I <sub>IX</sub>      | Input leakage current for all pins<br>except<br>SSTXP/SSXM/SSRXP/SSRXM           | -1        | 1         | μΑ    | All I/O signals held at $V_{DDQ}$<br>(For I/Os with a pull-up or pull-down resistor connected, the leakage current increases by $V_{DDQ}/R_{pu}$ or $V_{DDQ}/R_{PD}$         |

| I <sub>OZ</sub>      | Output High-Z leakage current for all<br>pins except SSTXP/ SSXM/<br>SSRXP/SSRXM | -1        | 1         | μA    | All I/O signals held at V <sub>DDQ</sub>                                                                                                                                     |

| I <sub>CC</sub> Core | Core and analog voltage operating<br>current                                     | -         | 200       | mA    | Total current through A <sub>VDD</sub> , V <sub>DD</sub>                                                                                                                     |

| I <sub>CC</sub> USB  | USB voltage supply operating current                                             | -         | 60        | mA    | -                                                                                                                                                                            |

| I <sub>SB1</sub>     | Total suspend current during<br>suspend mode with USB 3.0 PHY<br>enabled (L1)    | _         | _         | mA    | Core current: 1.5 mA<br>I/O current: 20 µA<br>USB current: 2 mA<br>For typical PVT (typical silicon, all power<br>supplies at their respective nominal levels at<br>25 °C)   |

| I <sub>SB2</sub>     | Total suspend current during<br>suspend mode with USB 3.0 PHY<br>disabled (L2)   | _         | _         | mA    | Core current: 250 µA<br>I/O current: 20 µA<br>USB current: 1.2 mA<br>For typical PVT (Typical silicon, all power<br>supplies at their respective nominal levels at<br>25 °C) |

| I <sub>SB3</sub>     | Total standby current during standby mode (L3)                                   | -         | _         | μA    | Core current: 60 μA<br>I/O current: 20 μA<br>USB current: 40 μA<br>For typical PVT (typical silicon, all power<br>supplies at their respective nominal levels at<br>25 °C)   |

| I <sub>SB4</sub>     | Total standby current during core power-down mode (L4)                           | _         | _         | μA    | Core current: 0 μA<br>I/O current: 20 μA<br>USB current: 40 μA<br>For typical PVT (typical silicon, all power<br>supplies at their respective nominal levels at<br>25 °C)    |

| V <sub>RAMP</sub>    | Voltage ramp rate on core and I/O supplies                                       | 0.2       | 50        | V/ms  | Voltage ramp must be monotonic                                                                                                                                               |

| V <sub>N</sub>       | Noise level permitted on $V_{DD}$ and I/O supplies                               | -         | 100       | mV    | Max p-p noise level permitted on all supplies except $A_{\mbox{VDD}}$                                                                                                        |

| V <sub>N_AVDD</sub>  | Noise level permitted on A <sub>VDD</sub> supply                                 | _         | 20        | mV    | Max p-p noise level permitted on A <sub>VDD</sub>                                                                                                                            |

### Table 10. GPIF II Timing in Asynchronous Mode<sup>[3, 4]</sup>

Note The following parameters assume one state transition

| Parameter               | Description                                                                                                                                                                                            | Min | Max | Units |

|-------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|-----|-------|

| tDS                     | Data In to DLE setup time. Valid in DDR async mode.                                                                                                                                                    | 2.3 | -   | ns    |

| tDH                     | Data In to DLE hold time. Valid in DDR async mode.                                                                                                                                                     | 2   | -   | ns    |

| tAS                     | Address In to ALE setup time                                                                                                                                                                           | 2.3 | -   | ns    |

| tAH                     | Address In to ALE hold time                                                                                                                                                                            | 2   | -   | ns    |

| tCTLassert              | CTL I/O asserted width for CTRL inputs without DQ input association and for outputs.                                                                                                                   | 7   | -   | ns    |

| tCTLdeassert            | CTL I/O deasserted width for CTRL inputs without DQ input association and for outputs.                                                                                                                 | 7   | -   | ns    |

| tCTLassert_DQassert     | CTL asserted pulse width for CTL inputs that signify DQ inputs valid<br>at the asserting edge but do not employ in-built latches (ALE/DLE) for<br>those DQ inputs.                                     | 20  | -   | ns    |

| tCTLdeassert_DQassert   | CTL deasserted pulse width for CTL inputs that signify DQ input valid at the asserting edge but do not employ in-built latches (ALE/DLE) for those DQ inputs.                                          | 7   | -   | ns    |

| tCTLassert_DQdeassert   | CTL asserted pulse width for CTL inputs that signify DQ inputs valid<br>at the deasserting edge but do not employ in-built latches (ALE/DLE)<br>for those DQ inputs.                                   | 7   | -   | ns    |

| tCTLdeassert_DQdeassert | CTL deasserted pulse width for CTL inputs that signify DQ inputs valid<br>at the deasserting edge but do not employ in-built latches (ALE/DLE)<br>for those DQ inputs.                                 | 20  | -   | ns    |

| tCTLassert_DQlatch      | CTL asserted pulse width for CTL inputs that employ in-built latches (ALE/DLE) to latch the DQ inputs. In this non-DDR case, in-built latches are always close at the deasserting edge.                | 7   | _   | ns    |

| tCTLdeassert_DQlatch    | deassert_DQlatch CTL deasserted pulse width for CTL inputs that employ in-built latches (ALE/DLE) to latch the DQ inputs. In this non-DDR case, in-built latches always close at the deasserting edge. |     | -   | ns    |

| tCTLassert_DQlatchDDR   | CTL asserted pulse width for CTL inputs that employ in-built latches (DLE) to latch the DQ inputs in DDR mode.                                                                                         | 10  | -   | ns    |

| tCTLdeassert_DQlatchDDR | CTL deasserted pulse width for CTL inputs that employ in-built latches (DLE) to latch the DQ inputs in DDR mode.                                                                                       | 10  | -   | ns    |

| tAA                     | DQ/CTL input to DQ output time when DQ change or CTL change needs to be detected and affects internal updates of input and output DQ lines.                                                            | -   | 30  | ns    |

| tDO                     | CTL to data out when the CTL change merely enables the output flop update whose data was already established.                                                                                          | -   | 25  | ns    |

| tOELZ                   | CTL designated as OE to low-Z. Time when external devices should stop driving data.                                                                                                                    | 0   | -   | ns    |

| tOEHZ                   | CTL designated as OE to high-Z                                                                                                                                                                         | 8   | 8   | ns    |

| tCLZ                    | CTL (non-OE) to low-Z. Time when external devices should stop driving data.                                                                                                                            | 0   | -   | ns    |

| tCHZ                    | CTL (non-OE) to high-Z                                                                                                                                                                                 | 30  | 30  | ns    |

| tCTLalpha               | CTL to alpha change at output                                                                                                                                                                          | _   | 25  | ns    |

| tCTLbeta                | CTL to beta change at output                                                                                                                                                                           | _   | 30  | ns    |

| tDST                    | Addr/data setup when DLE/ALE not used                                                                                                                                                                  | 2   | -   | ns    |

| tDHT                    | Addr/data hold when DLE/ALE not used                                                                                                                                                                   | 20  | _   | ns    |

#### Notes

All parameters guaranteed by design and validated through characterization.

"alpha" output corresponds to "early output" and "beta" corresponds to "delayed output". Please refer to the GPIFII Designer Tool for the use of these outputs.

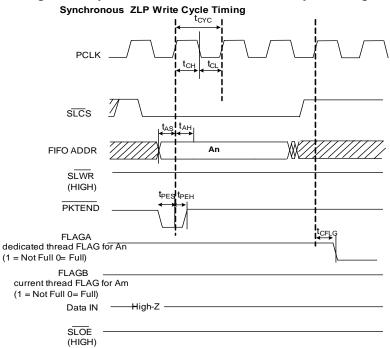

# Figure 14. Synchronous Slave FIFO ZLP Write Cycle Timing

# Table 11. Synchronous Slave FIFO Parameters<sup>[5]</sup>

| Parameter     | Description                          | Min | Max | Units        |

|---------------|--------------------------------------|-----|-----|--------------|

| FREQ          | Interface clock frequency            | -   | 100 | MHz          |

| tCYC          | Clock period                         | 10  | -   | ns           |

| tCH           | Clock high time                      | 4   | -   | ns           |

| tCL           | Clock low time                       | 4   | -   | ns           |

| tRDS          | SLRD# to CLK setup time              | 2   | -   | ns           |

| tRDH          | SLRD# to CLK hold time               | 0.5 | -   | ns           |

| tWRS          | SLWR# to CLK setup time              | 2   | -   | ns           |

| tWRH          | SLWR# to CLK hold time               | 0.5 | -   | ns           |

| tCO           | Clock to valid data                  | -   | 7   | ns           |

| tDS           | Data input setup time                | 2   | -   | ns           |

| tDH           | CLK to data input hold               | 0.5 | -   | ns           |

| tAS           | Address to CLK setup time            | 2   | -   | ns           |

| tAH           | CLK to address hold time             | 0.5 | -   | ns           |

| tOELZ         | SLOE# to data low-Z                  | 0   | -   | ns           |

| tCFLG         | CLK to flag output propagation delay | -   | 8   | ns           |

| tOEZ          | SLOE# deassert to Data Hi Z          | -   | 8   | ns           |

| tPES          | PKTEND# to CLK setup                 | 2   | -   | ns           |

| tPEH          | CLK to PKTEND# hold                  | 0.5 | -   | ns           |

| tCDH          | CLK to data output hold              | 2   | -   | ns           |

| tSSD          | Socket switching delay               | 2   | 68  | Clock cycles |

| tACCD         | Latency from SLRD# to Data           | 2   | 2   | Clock cycles |

| tFAD          | Latency from SLWR# to FLAG           | 3   | 3   | Clock cycles |

| Note Three-cy | cle latency from ADDR to DATA/FLAGS. | I   | •   | •            |

#### Note

5. All parameters guaranteed by design and validated through characterization.

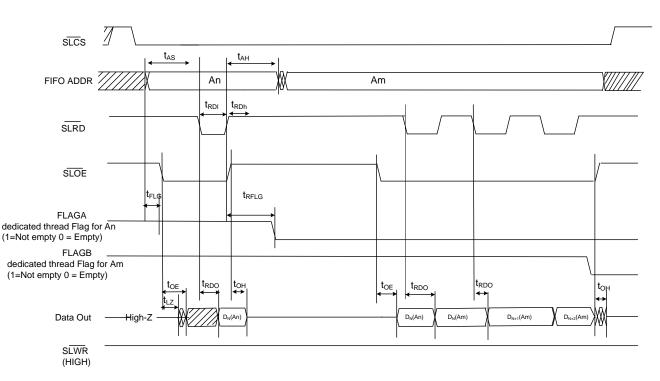

Asynchronous Slave FIFO Read Sequence Description

- FIFO address is stable and the SLCS# signal is asserted.

- SLOE# is asserted. This results in driving the data bus.

- SLRD # is asserted.

- Data from the FIFO is driven after assertion of SLRD#. This data is valid after a propagation delay of tRDO from the falling edge of SLRD#.

- FIFO pointer is incremented on deassertion of SLRD#

In Figure 15, data N is the first valid data read from the FIFO. For data to appear on the data bus during the read cycle, SLOE# must be in an asserted state. SLRD# and SLOE# can also be tied.

The same sequence of events is also shown for a burst read.

**Note** In the burst read mode, during SLOE# assertion, the data bus is in a driven state (data is driven from a previously addressed FIFO). After assertion of SLRD# data from the FIFO is driven on the data bus (SLOE# must also be asserted). The FIFO pointer is incremented after deassertion of SLRD#.

### Figure 15. Asynchronous Slave FIFO Read Mode

#### Asynchronous Read Cycle Timing

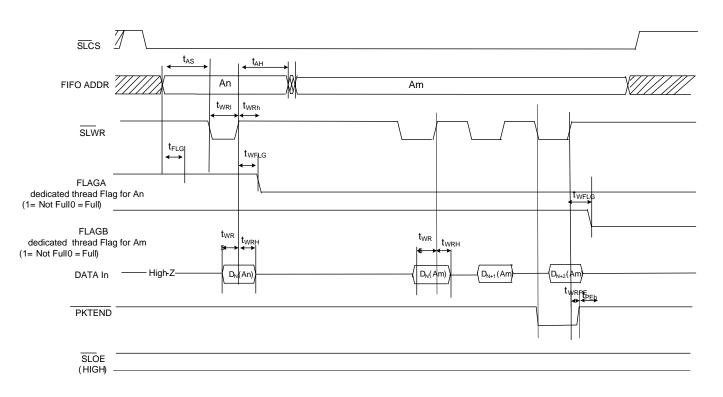

Asynchronous Slave FIFO Write Sequence Description

- FIFO address is driven and SLCS# is asserted

- SLWR# is asserted. SLCS# must be asserted with SLWR# or before SLWR# is asserted

- Data must be present on the tWRS bus before the deasserting edge of SLWR#

- Deassertion of SLWR# causes the data to be written from the data bus to the FIFO, and then the FIFO pointer is incremented

- The FIFO flag is updated after the tWFLG from the deasserting edge of SLWR.

The same sequence of events is shown for a burst write.

Note that in the burst write mode, after SLWR# deassertion, the data is written to the FIFO, and then the FIFO pointer is incremented.

**Short Packet**: A short packet can be committed to the USB host by using the PKTEND#. The external device or processor should be designed to assert the PKTEND# along with the last word of data and SLWR# pulse corresponding to the last word. The FIFOADDR lines must be held constant during the PKTEND# assertion.

**Zero-Length Packet**: The external device or processor can signal a zero-length packet (ZLP) to FX3 simply by asserting PKTEND#, without asserting SLWR#. SLCS# and the address must be driven as shown in Figure 17 on page 29.

**FLAG Usage**: The FLAG signals are monitored by the external processor for flow control. FLAG signals are FX3 outputs that can be configured to show empty, full, and partial status for a dedicated address or the current address.

### Figure 16. Asynchronous Slave FIFO Write Mode

tWRPE: SLWR#de- assert to PKTEND deasset 2 ns min( Note: PKTEND must be asserted at the same time as SL₩/R

### Asynchronous Write Cycle Timing

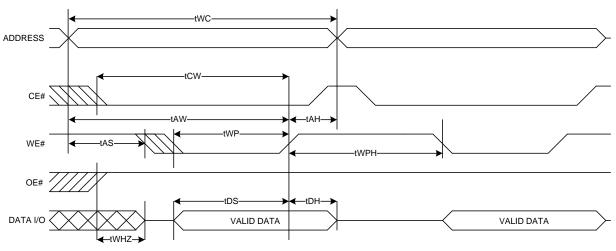

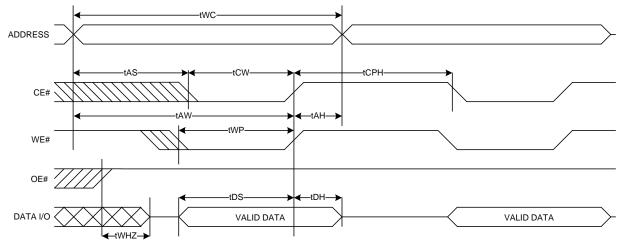

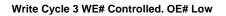

### Figure 19. Non-multiplexed Asynchronous SRAM Write Timing (WE# and CE# Controlled)

Write Cycle 1 WE# Controlled, OE# High During Write

## Figure 20. Non-multiplexed Asynchronous SRAM Write Timing (WE# controlled, OE# LOW)

**Note**: tWP must be adjusted such that tWP > tWHZ + tDS

# Table 13. Asynchronous SRAM Timing Parameters<sup>[7]</sup>

| Parameter | Description                          | Min  | Max  | Units |

|-----------|--------------------------------------|------|------|-------|

| _         | SRAM interface bandwidth             | -    | 61.5 | Mbps  |

| tRC       | Read cycle time                      | 32.5 | -    | ns    |

| tAA       | Address to data valid                | -    | 30   | ns    |

| tAOS      | Address to OE# LOW setup time        | 7    | -    | ns    |

| tOH       | Data output hold from address change | 3    | -    | ns    |

| tOHH      | OE# HIGH hold time                   | 7.5  | -    | ns    |

| tOHC      | OE# HIGH to CE# HIGH                 | 2    | -    | ns    |

| tOE       | OE# LOW to data valid                | -    | 25   | ns    |

| tOLZ      | OE# LOW to LOW-Z                     | 0    | -    | ns    |

| tWC       | Write cycle time                     | 30   | -    | ns    |

| tCW       | CE# LOW to write end                 | 30   | -    | ns    |

| tAW       | Address valid to write end           | 30   | -    | ns    |

| tAS       | Address setup to write start         | 7    | -    | ns    |

| tAH       | Address hold time from CE# or WE#    | 2    | -    | ns    |

| tWP       | WE# pulse width                      | 20   | -    | ns    |

| tWPH      | WE# HIGH time                        | 10   | -    | ns    |

| tCPH      | CE# HIGH time                        | 10   | -    | ns    |

| tDS       | Data setup to write end              | 7    | -    | ns    |

| tDH       | Data hold to write end               | 2    | _    | ns    |

| tWHZ      | Write to DQ HIGH-Z output            | -    | 22.5 | ns    |

| tOEZ      | OE# HIGH to DQ HIGH-Z output         | -    | 22.5 | ns    |

| tOW       | End of write to LOW-Z output         | 0    | _    | ns    |

#### Note

<sup>7.</sup> All parameters guaranteed by design and validated through characterization.

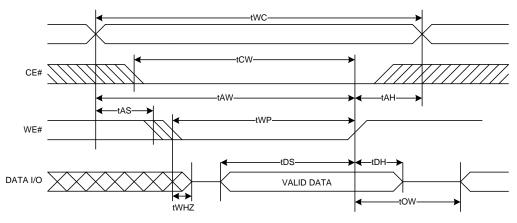

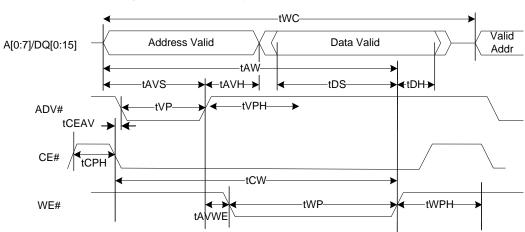

### ADMux Timing for Asynchronous Access

Note:

1. Multiple read cycles can be executed while keeping CE# low.

2. Read operation ends with either de-assertion of either OE# or CE#, whichever comes earlier.

Note:

- 1. Multiple write cycles can be executed while keeping CE# low.

- 2. Write operation ends with de-assertion of either WE# or CE#, whichever comes earlier.

# Table 14. Asynchronous ADMux Timing Parameters<sup>[8]</sup>

| Parameter | Description                                       | Min      | Max      | Units    | Notes                                                                   |  |  |  |

|-----------|---------------------------------------------------|----------|----------|----------|-------------------------------------------------------------------------|--|--|--|

|           | ADMux Asynchronous READ Access Timing Parameters  |          |          |          |                                                                         |  |  |  |

| tRC       | Read cycle time (address valid to address valid)  | 54.5     | _        | ns       | This parameter is dependent on when the P-port processors deasserts OE# |  |  |  |

| tACC      | Address valid to data valid                       | -        | 32       | ns       | -                                                                       |  |  |  |

| tCO       | CE# assert to data valid                          | -        | 34.5     | ns       | -                                                                       |  |  |  |

| tAVOE     | ADV# deassert to OE# assert                       | 2        | -        | ns       | -                                                                       |  |  |  |

| tOLZ      | OE# assert to data LOW-Z                          | 0        | -        | ns       | -                                                                       |  |  |  |

| tOE       | OE# assert to data valid                          | -        | 25       | ns       | -                                                                       |  |  |  |

| tHZ       | Read cycle end to data HIGH-Z                     | -        | 22.5     | ns       | -                                                                       |  |  |  |

|           | ADMux Asynchronous                                | VRITE Ac | cess Tim | ing Para | meters                                                                  |  |  |  |

| tWC       | Write cycle time (Address Valid to Address Valid) | _        | 52.5     | ns       | -                                                                       |  |  |  |

| tAW       | Address valid to write end                        | 30       | -        | ns       | -                                                                       |  |  |  |

| tCW       | CE# assert to write end                           | 30       | -        | ns       | -                                                                       |  |  |  |

| tAVWE     | ADV# deassert to WE# assert                       | 2        | -        | ns       | -                                                                       |  |  |  |

| tWP       | WE# LOW pulse width                               | 20       | -        | ns       | -                                                                       |  |  |  |

| tWPH      | WE# HIGH pulse width                              | 10       | -        | ns       | -                                                                       |  |  |  |

| tDS       | Data valid setup to WE# deassert                  | 18       | -        | ns       | -                                                                       |  |  |  |

| tDH       | Data valid hold from WE# deassert                 | 2        | _        | ns       | _                                                                       |  |  |  |

|           | ADMux Asynchronous Common                         | READ/W   | RITE Aco | cess Tim | ing Parameters                                                          |  |  |  |

| tAVS      | Address valid setup to ADV# deassert              | 5        | -        | ns       | _                                                                       |  |  |  |

| tAVH      | Address valid hold from ADV# deassert             | 2        | -        | ns       | -                                                                       |  |  |  |

| tVP       | ADV# LOW pulse width                              | 7.5      | -        | ns       | -                                                                       |  |  |  |

| tCPH      | CE# HIGH pulse width                              | 10       | -        | ns       | -                                                                       |  |  |  |

| tVPH      | ADV# HIGH pulse width                             | 15       | -        | ns       | -                                                                       |  |  |  |

| tCEAV     | CE# assert to ADV# assert                         | 0        | -        | ns       | -                                                                       |  |  |  |

\_\_\_\_\_

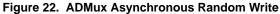

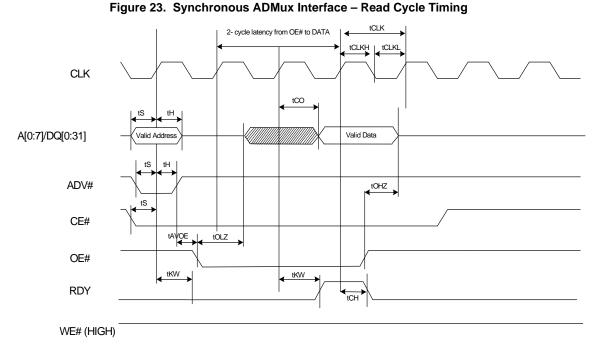

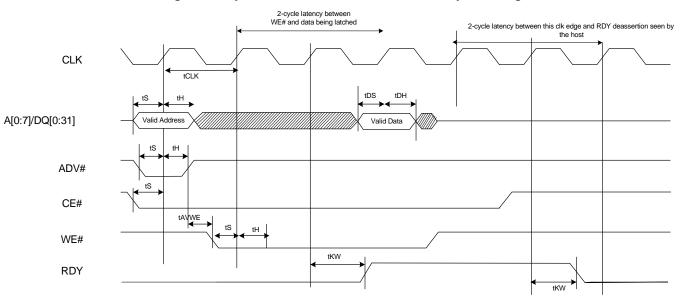

### Synchronous ADMux Timing

#### Note:

External P-Port processor and FX3 operate on the same clock edge

External processor sees RDY assert 2 cycles after OE # asserts andand sees RDY deassert a cycle after the data appears on the output

Valid output data appears 2 cycle after OE # asserted. The data is held until OE # deasserts

Two cycle latency is shown for 0-100 MHz operation. Latency can be reduced by 1 cycle for operations at less than 50 MHz (this 1 cycle latency is not supported by the bootloader)

Note:

1) External P-Port processor and FX3 operate on the same clock edge

2) External processor sees RDY assert 2 cycles after WE # asserts and deassert 3 cycles after the edge sampling the data.

3) Two cycle latency is shown for 0-100 MHz operation. Latency can be reduced by 1 cycle for operations at less than 50 MHz (this 1 cycle latency is not supported by the bootloader)

| Parameter | Description                    | Min | Max | Unit |

|-----------|--------------------------------|-----|-----|------|

| FREQ      | Interface clock frequency      | -   | 100 | MHz  |

| tCLK      | Clock period                   | 10  | _   | ns   |

| tCLKH     | Clock HIGH time                | 4   | -   | ns   |

| tCLKL     | Clock LOW time                 | 4   | -   | ns   |

| tS        | CE#/WE#/DQ setup time          | 2   | _   | ns   |

| tH        | CE#/WE#/DQ hold time           | 0.5 | -   | ns   |

| tCH       | Clock to data output hold time | 0   | _   | ns   |

| tDS       | Data input setup time          | 2   | _   | ns   |

| tDH       | Clock to data input hold       | 0.5 | _   | ns   |

| tAVDOE    | ADV# HIGH to OE# LOW           | 0   | -   | ns   |

| tAVDWE    | ADV# HIGH to WE# LOW           | 0   | -   | ns   |

| tHZ       | CE# HIGH to Data HIGH-Z        | -   | 8   | ns   |

| tOHZ      | OE# HIGH to Data HIGH-Z        | -   | 8   | ns   |

| tOLZ      | OE# LOW to Data LOW-Z          | 0   | -   | ns   |

| tKW       | Clock to RDY valid             | -   | 8   | ns   |

# Table 15. Synchronous ADMux Timing Parameters<sup>[9]</sup>

# **Serial Peripherals Timing**

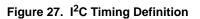

# I<sup>2</sup>C Timing

Note9. All parameters guaranteed by design and validated through characterization.

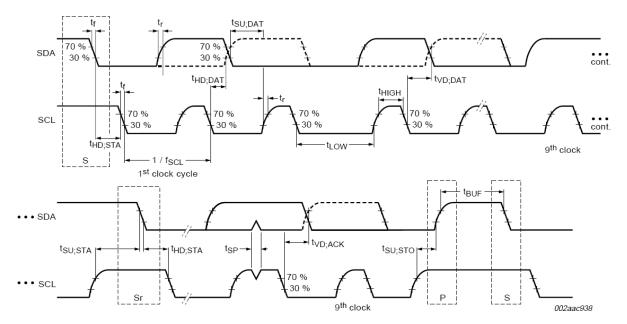

### SPI Timing Specification

SPI Master Timing for CPHA = 1

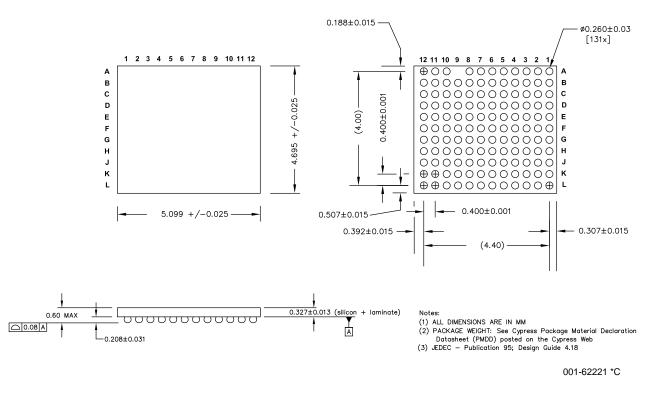

Figure 32. 131-ball WLCSP (5.099 × 4.695 × 0.60 mm) Package Diagram

Note Underfill is required on the board design. Contact fx3@cypress.com for details.

### Trigger Conditions

This condition is triggered when FX3 is self-powered in USB boot mode.

# ■Scope Of Impact

Device does not enumerate

### Workaround

Reset the device after connecting to USB host.

#### ■Fix Status

No fix. Workaround is required.

### 3. Extra ZLP is generated by the COMMIT action in the GPIF II state.

### ■Problem Definition

When COMMIT action is used in a GPIF-II state without IN\_DATA action then an extra Zero Length Packet (ZLP) is committed along with the data packets.

### ■Parameters Affected

N/A

### ■Trigger Conditions

This condition is triggered when COMMIT action is used in a state without IN\_DATA action.

### ■Scope Of Impact

Extra ZLP is generated.

### Workaround

Use IN\_DATA action along with COMMIT action in the same state.

# ■Fix Status

No fix. Workaround is required.

### 4. Invalid PID Sequence in USB 2.0 ISOC data transfer.

### Problem Definition

When the FX3 device is functioning as a high speed USB device with high bandwidth isochronous endpoints, the PID sequence of the ISO data packets is governed solely by the isomult setting. The length of the data packet is not considered while generating the PID sequence during each microframe. For example, even if a short packet is being sent on an endpoint with MULT set to 2; the PID used will be DATA2

### ■Parameters Affected

N/A

### ■Trigger Conditions

This condition is triggered when high bandwidth ISOC transfer endpoints are used.

### Scope Of Impact

ISOC data transfers failure.

### Workaround

This problem can be worked around by reconfiguring the endpoint with a lower isomult setting prior to sending short packets, and then switching back to the original value.

### Fix Status

No fix. Workaround is required.

### 5. USB data transfer errors are seen when ZLP is followed by data packet within same microframe.

### Problem Definition

Some data transfer errors may be seen if a Zero Length Packet is followed very quickly (within one microframe or 125 us) by another data packet on a burst enabled USB IN endpoint operating at super speed.

### ■Parameters Affected

N/A

### ■Trigger Conditions

This condition is triggered in SuperSpeed transfer with ZLPs

### ■Scope Of Impact

Data failure and lower data speed.

### ■Workaround

The solution is to ensure that some time is allowed to elapse between a ZLP and the next data packet on burst enabled USB IN endpoints. If this cannot be ensured at the data source, the CyU3PDmaChannelSetSuspend() API can be used to suspend the

# Document History Page (continued)

| Revision | ECN     | Orig. of<br>Change | Submission<br>Date | Description of Change                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

|----------|---------|--------------------|--------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| *0       | 4368374 | RSKV               | 05/02/2014         | Updated Package Diagram:<br>spec 001-62221 – Changed revision from *B to *C.<br>Updated to new template.<br>Completing Sunset Review.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| *P       | 4474200 | ANOP               | 08/14/2014         | Added CYUSB201x MPNs, ball map, and pin list to the datasheet.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| *Q       | 4668496 | DBIR               | 02/24/2015         | Updated Features.<br>Updated Logic Block Diagram.<br>Updated Functional Description:<br>Added "For a complete list of related documentation, click here." at the end<br>Added More Information.<br>Updated Functional Overview:<br>Updated Application Examples:<br>Updated Figure 1.<br>Updated Figure 2.<br>Updated description.<br>Removed Figure "USB Interface Signals".<br>Updated Pin Configurations:<br>Updated Figure 6.<br>Updated Reset:<br>Updated Hard Reset:<br>Updated Hard Reset:<br>Updated description.<br>Updated Pin Description.<br>Updated Table 7:<br>Updated Table 7:<br>Updated atble 7:<br>Updated entire table.<br>Modified CVDDQ power domain description.<br>Removed Table "CYUSB2014 Pin List (GPIF II with 32-bit Data Bus Width)"<br>Updated Electrical Specifications:<br>Updated Sparameter and its details.<br>Updated Siave FIFO Interface:<br>Updated Siave FIFO Interface:<br>Updated Figure 12.<br>Updated Figure 13.<br>Updated Table 11.<br>Updated AC Timing Parameters:<br>Added Horst Processor Interface (P-Port) Timing.<br>Updated Acronyms.<br>Added Errata.<br>Replaced West Bridge Benicia with FX3. |

| *R       | 4703347 | AMDK               | 03/27/2015         | Updated Slave FIFO Interface:<br>Updated Synchronous Slave FIFO Read Sequence Description:<br>Updated Figure 12.<br>Updated Synchronous Slave FIFO Write Sequence Description:<br>Updated Figure 13.<br>Updated Table 11:<br>Updated minimum value of tSSD parameter.<br>Added tACCD, tFAD parameters and their details.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| *S       | 5160624 | AJAI               | 04/07/2016         | Removed ISS parameter.<br>Added item 6 in Errata.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

# Document History Page (continued)

| Document Title: CYUSB301X/CYUSB201X, EZ-USB <sup>®</sup> FX3: SuperSpeed USB Controller<br>Document Number: 001-52136 |         |                    |                    |                                                                                                                                                                                                                                                                                                                                                                                |  |  |  |

|-----------------------------------------------------------------------------------------------------------------------|---------|--------------------|--------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| Revision                                                                                                              | ECN     | Orig. of<br>Change | Submission<br>Date | Description of Change                                                                                                                                                                                                                                                                                                                                                          |  |  |  |

| *Т                                                                                                                    | 5306567 | MDDD               | 06/29/2016         | Updated AC Timing Parameters:<br>Updated GPIF II Timing:<br>Updated Table 9:<br>Changed maximum value of t <sub>CO</sub> parameter from 8 ns to 7 ns.<br>Updated Slave FIFO Interface:<br>Updated Synchronous Slave FIFO Write Sequence Description:<br>Updated Table 11:<br>Changed maximum value of t <sub>CO</sub> parameter from 8 ns to 7 ns.<br>Updated to new template. |  |  |  |

| *U                                                                                                                    | 5703914 | GNKK               | 04/20/2017         | Updated the Cypress logo and copyright information.                                                                                                                                                                                                                                                                                                                            |  |  |  |