Welcome to E-XFL.COM

#### Embedded - Microcontrollers - Application Specific: Tailored Solutions for Precision and Performance

### Embedded - Microcontrollers - Application Specific

represents a category of microcontrollers designed with unique features and capabilities tailored to specific application needs. Unlike general-purpose microcontrollers, application-specific microcontrollers are optimized for particular tasks, offering enhanced performance, efficiency, and functionality to meet the demands of specialized applications.

#### What Are <u>Embedded - Microcontrollers -</u> <u>Application Specific</u>?

Application enacific microcontrollars are angineered to

#### Details

| Details                 |                                                                           |

|-------------------------|---------------------------------------------------------------------------|

| Product Status          | Active                                                                    |

| Applications            | SuperSpeed USB Peripheral Controller                                      |

| Core Processor          | ARM9®                                                                     |

| Program Memory Type     | External Program Memory                                                   |

| Controller Series       | CYUSB                                                                     |

| RAM Size                | 256K x 8                                                                  |

| Interface               | GPIF, I <sup>2</sup> C, I <sup>2</sup> S, SPI, UART, USB                  |

| Number of I/O           | 60                                                                        |

| Voltage - Supply        | 1.15V ~ 1.25V                                                             |

| Operating Temperature   | 0°C ~ 70°C                                                                |

| Mounting Type           | Surface Mount                                                             |

| Package / Case          | 121-TFBGA                                                                 |

| Supplier Device Package | 121-FBGA (10x10)                                                          |

| Purchase URL            | https://www.e-xfl.com/product-detail/infineon-technologies/cyusb3011-bzxc |

|                         |                                                                           |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

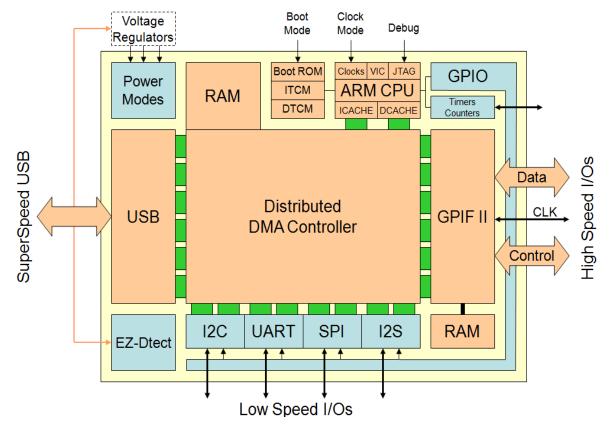

# Logic Block Diagram

## **GPIF II**

The high-performance GPIF II interface enables functionality similar to, but more advanced than, FX2LP's GPIF and Slave FIFO interfaces.

The GPIF II is a programmable state machine that enables a flexible interface that may function either as a master or slave in industry-standard or proprietary interfaces. Both parallel and serial interfaces may be implemented with GPIF II.

Here is a list of GPIF II features:

- Functions as master or slave

- Provides 256 firmware programmable states

- Supports 8-bit, 16-bit, 24-bit, and 32-bit parallel data bus

- Enables interface frequencies up to 100 MHz

- Supports 14 configurable control pins when a 32- bit data bus is used. All control pins can be either input/output or bidirectional.

- Supports 16 configurable control pins when a 16/8 data bus is used. All control pins can be either input/output or bi-directional.

GPIF II state transitions are based on control input signals. The control output signals are driven as a result of the GPIF II state transitions. The INT# output signal can be controlled by GPIF II. Refer to the GPIFII Designer tool. The GPIF II state machine's behavior is defined by a GPIF II descriptor. The GPIF II descriptor is designed such that the required interface specifications are met. 8 KB of memory (separate from the 256/512 KB of embedded SRAM) is dedicated to the GPIF II waveform where the GPIF II descriptor is stored in a specific format.

Cypress's GPIFII Designer Tool enables fast development of GPIF II descriptors and includes examples for common interfaces.

Example implementations of GPIF II are the asynchronous slave FIFO and synchronous slave FIFO interfaces.

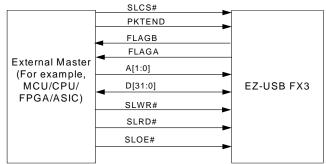

#### Slave FIFO interface

The Slave FIFO interface signals are shown in Figure 5. This interface allows an external processor to directly access up to four buffers internal to FX3. Further details of the Slave FIFO interface are described on page 24.

**Note** Access to all 32 buffers is also supported over the slave FIFO interface. For details, contact Cypress Applications Support.

#### Figure 5. Slave FIFO Interface

Note: Multiple Flags may be configured.

## CPU

FX3 has an on-chip 32-bit, 200-MHz ARM926EJ-S core CPU. The core has direct access to 16 KB of Instruction Tightly Coupled Memory (TCM) and 8 KB of Data TCM. The ARM926EJ-S core provides a JTAG interface for firmware debugging.

FX3 offers the following advantages:

- Integrates 256/512 KB of embedded SRAM for code and data and 8 KB of Instruction cache and Data cache.

- Implements efficient and flexible DMA connectivity between the various peripherals (such as, USB, GPIF II, I<sup>2</sup>S, SPI, UART, I<sup>2</sup>C), requiring firmware only to configure data accesses between peripherals, which are then managed by the DMA fabric.

- Allows easy application development using industry-standard development tools for ARM926EJ-S.

Examples of the FX3 firmware are available with the Cypress EZ-USB FX3 Development Kit.

## JTAG Interface

FX3's JTAG interface has a standard five-pin interface to connect to a JTAG debugger in order to debug firmware through the CPU-core's on-chip-debug circuitry.

Industry-standard debugging tools for the ARM926EJ-S core can be used for the FX3 application development.

### Other Interfaces

FX3 supports the following serial peripherals:

- SPI

- UART

- ∎ I<sup>2</sup>C

- I<sup>2</sup>S

The SPI, UART, and I<sup>2</sup>S interfaces are multiplexed on the serial peripheral port.

The CYUSB3012 and CYUSB3014 Pin List on page 15 shows details of how these interfaces are multiplexed. Note that when GPIF II is configured for a 32-bit data bus width (CYUSB3012 and CYUSB3014), then the SPI interface is not available.

#### **SPI Interface**

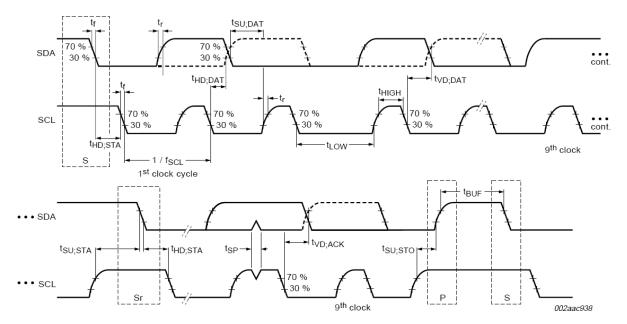

FX3 supports an SPI Master interface on the Serial Peripherals port. The maximum operation frequency is 33 MHz.

The SPI controller supports four modes of SPI communication (see SPI Timing Specification on page 40 for details on the modes) with the Start-Stop clock. This controller is a single-master controller with a single automated SSN control. It supports transaction sizes ranging from four bits to 32 bits.

| Table 6. Entry | y and Exit Methods for Low-P | ower Modes (continued) |

|----------------|------------------------------|------------------------|

|                |                              |                        |

| Low-Power Mode | Characteristics                                                                                                                              | Methods of Entry           | Methods of Exit     |

|----------------|----------------------------------------------------------------------------------------------------------------------------------------------|----------------------------|---------------------|

|                | ■ The power consumption in this mode does                                                                                                    | ■ Turn off V <sub>DD</sub> | Reapply VDD         |

| Mode (L4)      | not exceed ISB <sub>4</sub>                                                                                                                  |                            | Assertion of RESET# |

|                | Core power is turned off                                                                                                                     |                            |                     |

|                | All buffer memory, configuration registers,<br>and the program RAM do not maintain<br>state. After exiting this mode, reload the<br>firmware |                            |                     |

|                | In this mode, all other power domains can<br>be turned on/off individually                                                                   |                            |                     |

## Digital I/Os

FX3 has internal firmware-controlled pull-up or pull-down resistors on all digital I/O pins. An internal 50-k $\Omega$  resistor pulls the pins high, while an internal 10-k $\Omega$  resistor pulls the pins low to prevent them from floating. The I/O pins may have the following states:

- Tristated (High-Z)

- Weak pull-up (via internal 50 kΩ)

- Pull-down (via internal 10 kΩ)

- Hold (I/O hold its value) when in low-power modes

- The JTAG TDI, TMS, and TRST# signals have fixed 50-kΩ internal pull-ups, and the TCK signal has a fixed 10-kΩ pull-down resistor.

All unused I/Os should be pulled high by using the internal pull-up resistors. All unused outputs should be left floating. All I/Os can be driven at full-strength, three-quarter strength, half-strength, or quarter-strength. These drive strengths are configured separately for each interface.

## **GPIOs**

EZ-USB enables a flexible pin configuration both on the GPIF II and the serial peripheral interfaces. Any unused control pins (except CTL[15]) on the GPIF II interface can be used as GPIOs. Similarly, any unused pins on the serial peripheral interfaces may be configured as GPIOs. See Pin Configurations for pin configuration options.

All GPIF II and GPIO pins support an external load of up to 16 pF for every pin.

## EMI

FX3 meets EMI requirements outlined by FCC 15B (USA) and EN55022 (Europe) for consumer electronics. FX3 can tolerate EMI, conducted by the aggressor, outlined by these specifications and continue to function as expected.

# System-level ESD

FX3 has built-in ESD protection on the D+, D–, and GND pins on the USB interface. The ESD protection levels provided on these ports are:

- ±2.2-kV human body model (HBM) based on JESD22-A114 Specification

- ±6-kV contact discharge and ±8-kV air gap discharge based on IEC61000-4-2 level 3A

- ±8-kV Contact Discharge and ±15-kV Air Gap Discharge based on IEC61000-4-2 level 4C.

This protection ensures the device continues to function after ESD events up to the levels stated in this section.

The SSRX+, SSRX–, SSTX+, and SSTX– pins only have up to  $\pm 2.2$ -kV HBM internal ESD protection.

# **Pin Configurations**

|   | 1        | 2        | 3        | 4        | 5        | 6        | 7        | 8        | 9            | 10           | 11       |

|---|----------|----------|----------|----------|----------|----------|----------|----------|--------------|--------------|----------|

| А | U3VSSQ   | U3RXVDDQ | SSRXM    | SSRXP    | SSTXP    | SSTXM    | AVDD     | VSS      | DP           | DM           | NC       |

| В | VIO4     | FSLC[0]  | R_USB3   | FSLC[1]  | U3TXVDDQ | CVDDQ    | AVSS     | VSS      | VSS          | VDD          | TRST#    |

| С | GPIO[54] | GPIO[55] | VDD      | GPIQ[57] | RESET#   | XTALIN   | XTALOUT  | R_USB2   | OTG_ID       | TDO          | VIO5     |

| D | GPIO[50] | GPIQ[51] | GPIO[52] | GPIO[53] | GPIO[56] | CLKIN_32 | CLKIN    | VSS      | 12C_GPIO[58] | 12C_GPIO[59] | Q[60]    |

| Е | GPIO[47] | VSS      | VIO3     | GPIO[49] | GPIO[48] | FSLC[2]  | TDI      | TMS      | VDD          | VBATT        | VBUS     |

| F | VIO2     | GPIO[45] | GPIO[44] | GPIO[41] | GPIO[46] | TCK      | GPIO[2]  | GPIO[5]  | GPIQ[1]      | GPIQ[0]      | VDD      |

| G | VSS      | GPIO[42] | GPIO[43] | GPIO[30] | GPIO[25] | GPIQ[22] | GPIO[21] | GPIO[15] | GPIO[4]      | GPIO[3]      | VSS      |

| Н | VDD      | GPIO[39] | GPIO[40] | GPIO[31] | GPIO[29] | GPIO[26] | GPIQ[20] | GPIO[24] | GPIO[7]      | GPIO[6]      | VIO1     |

| J | GPIO[38] | GPIO[36] | GPIO[37] | GPIO[34] | GPIO[28] | GPIO[16] | GPIO[19] | GPIO[14] | GPIO[9]      | GPIO[8]      | VDD      |

| К | GPIO[35] | GPIO[33] | VSS      | VSS      | GPIO[27] | GPIQ[23] | GPIO[18] | GPIQ[17] | GPIO[13]     | GPIO[12]     | GPIO[10] |

| L | VSS      | VSS      | VSS      | GPIQ[32] | VDD      | VSS      | VDD      | INT#     | VIO1         | GPIQ[11]     | VSS      |

## Figure 6. FX3 121-ball BGA Ball Map (Top View)

## Figure 7. FX3 131-Ball WLCSP Ball Map (Bottom View)

|   | 12       | 11       | 10       | 9        | 8        | 7        | 6                | 5        | 4        | 3         | 2                | 1       |

|---|----------|----------|----------|----------|----------|----------|------------------|----------|----------|-----------|------------------|---------|

| А | VSS      | VSS      | SSRXM    |          | SSTXM    | FSLC[0]  | AVSS             | AVDD     | DP       | VSS       | DM               | VDD     |

| В | GPIO[55] | VIO4     | SSRXP    | R_USB3   | SSTXP    | FSLC[2]  | XTALIN           | XTALOUT  | NC       | R_USB2    | NC               | VDD     |

| С | GPIO[56] | VIO3     | U3RXVDDQ | U3VSSQ   | U3TXVDDQ | CVDDQ    | CLKIN_32         | CLKIN    | VSS      | OTG_ID    | TDO              | TRST#   |

| D | GPIO[49] | GPIO[50] | GPIO[53] | GPIO[54] | RESET#   | VDD      | 12C_GPIO[58<br>] | TMS      | VIO5     | тск       | 12C_GPIO[59<br>] | VSS     |

| Е | GPIO[57] | GPIO[48] | GPIO[51] | GPIO[52] | O[60]    | VSS      | VSS              | VSS      | VSS      | GPIO[3]   | VBATT            | VBUS    |

| F | VSS      | GPIO[46] | GPIO[47] | FSLC[1]  | TDI      | VDD      | VDD              | VDD      | VDD      | GPIO[4]   | GPIO[1]          | GPIO[0] |

| G | VIO2     | GPIO[43] | GPIO[44] | GPIO[45] | VSS      | VSS      | VDD              | VSS      | GPIO[9]  | GPIO[7]   | GPIO[6]          | GPIO[2] |

| Н | VSS      | GPIO[40] | GPIO[41] | GPIO[42] | GPIO[39] | VSS      | GPIO[20]         | GPIO[18] | GPIO[14] | GPIO[12]  | GPIO[8]          | VIO1    |

| J | VIO2     | GPIO[38] | GPIO[37] | GPIO[36] | GPIO[31] | GPIO[27] | GPIO[25]         | GPIO[22] | GPIO[19] | GPIO[ 15] | GPIO[10]         | GPIO[5] |

| К | GPIO[35] | GPIO[34] | GPIO[33] | GPIO[32] | GPIO[28] | GPIO[26] | GPIO[16]         | GPIO[21] | INT#     | GPIO[24]  | GPIO[11]         | VSS     |

| L | VDD      | VSS      | VDD      | GPIO[30] | GPIO[29] | VIO1     | GPIO[23]         | VSS      | VIO1     | GPIO[17]  | GPIO[13]         | VSS     |

**Note** No ball is populated at location A9.

## Figure 8. FX3 Hi-Speed 121-Ball BGA Ball Map (Top View)

|   | 1        | 2        | 3        | 4        | 5        | 6        | 7         | 8        | 9            | 10           | 11       |

|---|----------|----------|----------|----------|----------|----------|-----------|----------|--------------|--------------|----------|

| А | U3VSSQ   | VDD      | NC       | NC       | NC       | NC       | AVDD      | VSS      | DP           | DM           | NC       |

| В | VIO4     | FSLC[0]  | NC       | FSLC[1]  | VDD      | CVDDQ    | AVSS      | VSS      | VSS          | VDD          | TRST#    |

| С | GPIO[54] | GPIO[55] | VDD      | GPIO[57] | RESET#   | XTALIN   | XTALOUT   | R_USB2   | OTG_ID       | TDO          | VIO5     |

| D | GPIO[50] | GPIO[51] | GPIO[52] | GPIO[53] | GPIO[56] | CLKIN_32 | CLKIN     | VSS      | I2C_GPIO[58] | I2C_GPIO[59] | O[60]    |

| Е | GPIO[47] | VSS      | VIO3     | GPIO[49] | GPIO[48] | FSLC[2]  | TDI       | TMS      | VDD          | VBATT        | VBUS     |

| F | VIO2     | GPIO[45] | GPIO[44] | GPIO[41] | GPIO[46] | ТСК      | GPIO[2]   | GPIO[5]  | GPIO[1]      | GPIO[0]      | VDD      |

| G | VSS      | GPIO[42] | GPIO[43] | GPIO[30] | GPIO[25] | GPIO[22] | GPIO[21]  | GPIO[15] | GPIO[4]      | GPIO[3]      | VSS      |

| Н | VDD      | GPIO[39] | GPIO[40] | GPIO[31] | GPIO[29] | GPIO[26] | GPIO[20]  | GPIO[24] | GPIO[7]      | GPIO[6]      | VIO1     |

| J | GPIO[38] | GPIO[36] | GPIO[37] | GPIO[34] | GPIO[28] | GPIO[16] | GPIO[ 19] | GPIO[14] | GPIO[9]      | GPIO[8]      | VDD      |

| К | GPIO[35] | GPIO[33] | VSS      | VSS      | GPIO[27] | GPIO[23] | GPIO[ 18] | GPIO[17] | GPIO[13]     | GPIO[12]     | GPIO[10] |

| L | VSS      | VSS      | VSS      | GPIO[32] | VDD      | VSS      | VDD       | INT#     | VIO1         | GPIO[11]     | VSS      |

### Table 7. CYUSB3012 and CYUSB3014 Pin List (continued)

| BGA      | WLCSP    | Power          | I/O       | Name                 |                  |                                               | Description        |               |                  |          |

|----------|----------|----------------|-----------|----------------------|------------------|-----------------------------------------------|--------------------|---------------|------------------|----------|

| J1       | J11      | Domain<br>VIO2 | I/O       | GPIO[38]             | DQ[21]           | GPIO                                          | GPIO               | GPIO          | GPIO             | GPIO     |

| H2       | H8       | VIO2<br>VIO2   | I/O       | GPIO[38]<br>GPIO[39] | DQ[21]           | GPIO                                          | GPIO               | GPIO          | GPIO             | GPIO     |

| H3       | H11      | VIO2<br>VIO2   | I/O       | GPIO[40]             | DQ[22]<br>DQ[23] | GPIO                                          | GPIO               | GPIO          | GPIO             | GPIO     |

| F4       | H10      | VIO2<br>VIO2   | I/O       | GPIO[40]             | DQ[23]           | GPIO                                          | GPIO               | GPIO          | GPIO             | GPIO     |

| G2       | H9       | VIO2<br>VIO2   | 1/O       | GPIO[41]<br>GPIO[42] | DQ[24]<br>DQ[25] | GPIO                                          | GPIO               | GPIO          | GPIO             | GPIO     |

| G2<br>G3 | G11      | VIO2<br>VIO2   | 1/O       | GPIO[42]<br>GPIO[43] | DQ[25]           | GPIO                                          | GPIO               | GPIO          | GPIO             | GPIO     |

| F3       | G10      | VIO2<br>VIO2   | 1/O       | GPIO[43]<br>GPIO[44] | DQ[20]<br>DQ[27] | GPIO                                          | GPIO               | GPIO          | GPIO             | GPIO     |

| F2       | G09      | VIO2<br>VIO2   | I/O       | GPIO[45]             | GPIO             | GPIO                                          | GPIO               | GPIO          | GPIO             | GPIO     |

| F5       | F11      | VIO2<br>VIO3   | I/O       | GPIO[46]             | DQ[28]           | UART_RT S                                     | GPIO               | GPIO          | GPIO             | GPIO     |

| E1       | F10      | VIO3           | I/O       | GPIO[47]             | DQ[20]           | UART_CT S                                     | GPIO               | GPIO          | GPIO             | GPIO     |

| E5       | E11      | VIO3           | I/O       | GPIO[48]             | DQ[29]           | UART_TX                                       | GPIO               | GPIO          | GPIO             | GPIO     |

| E4       | D12      | VIO3           | I/O       | GPIO[49]             | DQ[31]           | UART_R X                                      | GPIO               | GPIO          | GPIO             | GPIO     |

| D1       | D12      | VIO3           | I/O       | GPIO[50]             | I2S_CLK          | I2S_CLK                                       | GPIO               | GPIO          | GPIO             | GPIO     |

| D2       | E10      | VIO3           | I/O       | GPIO[51]             | I2S_SD           | 128_SD                                        | GPIO               | GPIO          | GPIO             | GPIO     |

| D2<br>D3 | E10      | VIO3           | I/O       | GPIO[52]             | 125_5D<br>12S_WS | 125_00<br>12S_WS                              | GPIO               | GPIO          | GPIO             | GPIO     |

| D3       | D10      | VIO3<br>VIO4   | I/O       | GPIO[53]             | UART_RTS         | SPI SCK                                       | UART_RTS           | SPI_SCK       | GPIO             | GPIO     |

| C1       | D10      | VIO4<br>VIO4   | I/O       | GPIO[54]             | UART_CTS         | SPI_SSN                                       | UART_CTS           | SPI_SSN       | I2S_CLK          | GPIO     |

| C2       | B12      | VIO4<br>VIO4   | I/O       | GPIO[55]             | UART_TX          | SPI MIS O                                     | UART_TX            | SPI MISO      | I2S_OEK          | GPIO     |

| D5       | C12      | VIO4<br>VIO4   | I/O       | GPIO[56]             | UART_RX          | SPI_MOS I                                     | UART RX            | SPI_MOSI      | 125_5D<br>12S_WS | GPIO     |

| C4       | E12      | VIO4<br>VIO4   | I/O       | GPIO[57]             | I2S_MCLK         | I2S_MCL K                                     | GPIO               | GPIO          | 125_W5           | GPIO     |

| 04       |          | 104            | 1/0       | 0110[37]             | 120_WOLK         |                                               | USB Port           | 0110          | 120_INCL R       |          |

|          |          |                |           |                      |                  | CYUSB301X                                     |                    | C             | YUSB201X         |          |

| A3       | A10      | <b>U3RXVD</b>  | 1         | SSRXM                |                  | SSRX-                                         |                    |               | NC               |          |

|          | 7.10     | DQ             |           |                      |                  |                                               |                    |               |                  |          |

| A4       | B10      | U3RXVD<br>DQ   | Ι         | SSRXP                |                  | SSRX+                                         |                    |               | NC               |          |

| A6       | A8       | U3TXVD<br>DQ   | 0         | SSTXM                |                  | SSTX-                                         |                    |               | NC               |          |

| A5       | B8       | U3TXVD<br>DQ   | 0         | SSTXP                |                  | SSTX+                                         |                    |               | NC               |          |

| B3       | B9       | U3TXVD<br>DQ   | I/O       | R_usb3               |                  | stor for USB 3.0 (Co<br>or between this pin a |                    |               | NC               |          |

| C9       | C3       | VBUS/<br>VBATT | Ι         | OTG_ID               |                  |                                               | OTG_ID             |               |                  |          |

| A9       | A4       | VBUS/V<br>BATT | I/O       | DP                   |                  |                                               | D+                 |               |                  |          |

| A10      | A2       | VBUS/V<br>BATT | I/O       | DM                   |                  |                                               | D-                 |               |                  |          |

| C8       | B3       | VBUS/VBAT<br>T | I/O       | R_usb2               | Precision resist | tor for USB 2.0 (Cor                          | nnect a 6.04 k ±1  | % resistor be | tween this pin a | and GND) |

| [        |          | II             |           |                      |                  |                                               | Clock and Res      | set           |                  |          |

| B2       | A7       | CVDDQ          | Ι         | FSLC[0]              |                  |                                               | FSLC[0]            |               |                  |          |

| C6       | B6       | AVDD           | I/O       | XTALIN               | XTALIN           |                                               |                    |               |                  |          |

| 07       | 1        | AVDD           | I/O       | XTALOUT              | XTALOUT          |                                               |                    |               |                  |          |

| C7       | B5       | 1000           |           |                      | FSLC[1]          |                                               |                    |               |                  |          |

| B4       | B5<br>F9 | CVDDQ          | 1         | FSLC[1]              |                  |                                               | FSLC[1]            |               |                  |          |

|          |          |                | <br> <br> |                      |                  |                                               | FSLC[1]<br>FSLC[2] |               |                  |          |

| BGA | WLCSP | Power<br>Domain | I/O | Name             | Description           |

|-----|-------|-----------------|-----|------------------|-----------------------|

| D6  | C6    | CVDDQ           | I   | CLKIN_32         | CLKIN_32              |

| C5  | D8    | CVDDQ           | I   | RESET#           | RESET#                |

|     |       |                 |     |                  | I2C and JTAG          |

| D9  | D6    | VIO5            | I/O | I2C_GPIO[58<br>] | I <sup>2</sup> C_SCL  |

| D10 | D2    | VIO5            | I/O | I2C_GPIO[59<br>] | I <sup>2</sup> C_SDA  |

| E7  | F8    | VIO5            | I   | TDI              | TDI                   |

| C10 | C2    | VIO5            | 0   | TDO              | TDO                   |

| B11 | C1    | VIO5            | I   | TRST#            | TRST#                 |

| E8  | D5    | VIO5            | I   | TMS              | TMS                   |

| F6  | D3    | VIO5            | I   | TCK              | ТСК                   |

| D11 | E8    | VIO5            | 0   | O[60]            | Charger detect output |

|     |       |                 |     |                  | Power                 |

| E10 | E2    | -               | PWR | VBATT            | -                     |

| B10 | B1    | -               | PWR | VDD              | -                     |

| -   | A1    | _               | PWR | VDD              | -                     |

| A1  | C9    | _               | PWR | U3VSSQ           | -                     |

| E11 | E1    | _               | PWR | VBUS             | -                     |

| D8  | C4    | _               | PWR | VSS              | -                     |

| H11 | H1    | _               | PWR | VIO1             | -                     |

| E2  | K1    | _               | PWR | VSS              | -                     |

| L9  | L4    | _               | PWR | VIO1             | -                     |

| G1  | L5    | _               | PWR | VSS              | -                     |

| -   | L7    | _               | PWR | VIO1             | -                     |

| -   | L1    | _               | PWR | VSS              | -                     |

| F1  | J12   | _               | PWR | VIO2             | -                     |

| G11 | H12   | _               | PWR | VSS              | -                     |

|     | G12   | -               | PWR | VIO2             | -                     |

| E3  | C11   | -               | PWR | VIO3             | -                     |

| L1  | F12   | _               | PWR | VSS              | -                     |

| B1  | B11   | -               | PWR | VIO4             | -                     |

| L6  | A11   | -               | PWR | VSS              | -                     |

| -   | A12   | -               | PWR | VSS              | -                     |

| B6  | C7    | -               | PWR | CVDDQ            | -                     |

| B5  | C8    | _               | PWR | U3TXVDDQ         | _                     |

| A2  | C10   | _               | PWR | U3RXVDDQ         | _                     |

| C11 | D4    | _               | PWR | VIO5             | _                     |

| L11 | A3    | _               | PWR | VSS              | _                     |

| A7  | A5    | _               | PWR | AVDD             | _                     |

| B7  | A6    | _               | PWR | AVSS             | _                     |

| C3  | F4    | _               | PWR | VDD              | _                     |

| B8  | D1    | _               | PWR | VSS              | _                     |

| E9  | F5    | _               | PWR | VDD              | _                     |

### Table 7. CYUSB3012 and CYUSB3014 Pin List (continued)

# **AC Timing Parameters**

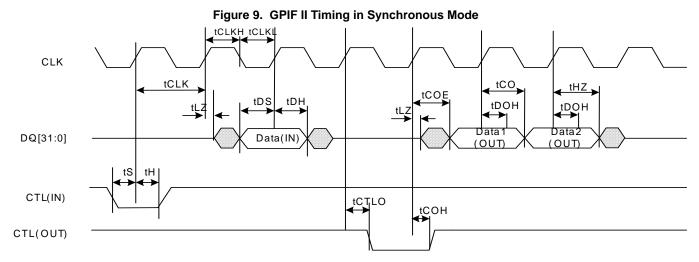

## **GPIF II Timing**

# Table 9. GPIF II Timing Parameters in Synchronous Mode [2]

| Parameter | Description                                                                                                                | Min | Max | Units |

|-----------|----------------------------------------------------------------------------------------------------------------------------|-----|-----|-------|

| Frequency | Interface clock frequency                                                                                                  | _   | 100 | MHz   |

| tCLK      | Interface clock period                                                                                                     | 10  | -   | ns    |

| tCLKH     | Clock high time                                                                                                            | 4   | -   | ns    |

| tCLKL     | Clock low time                                                                                                             | 4   | -   | ns    |

| tS        | CTL input to clock setup time                                                                                              | 2   | -   | ns    |

| tH        | CTL input to clock hold time                                                                                               | 0.5 | -   | ns    |

| tDS       | Data in to clock setup time                                                                                                | 2   | -   | ns    |

| tDH       | Data in to clock hold time                                                                                                 | 0.5 | -   | ns    |

| tCO       | Clock to data out propagation delay when DQ bus is already in output direction                                             | -   | 7   | ns    |

| tCOE      | Clock to data out propagation delay when DQ lines change to output from tristate and valid data is available on the DQ bus | -   | 9   | ns    |

| tCTLO     | Clock to CTL out propagation delay                                                                                         | -   | 8   | ns    |

| tDOH      | Clock to data out hold                                                                                                     | 2   | -   | ns    |

| tCOH      | Clock to CTL out hold                                                                                                      | 0   | -   | ns    |

| tHZ       | Clock to high-Z                                                                                                            | _   | 8   | ns    |

| tLZ       | Clock to low-Z                                                                                                             | 0   | -   | ns    |

Note2. All parameters guaranteed by design and validated through characterization.

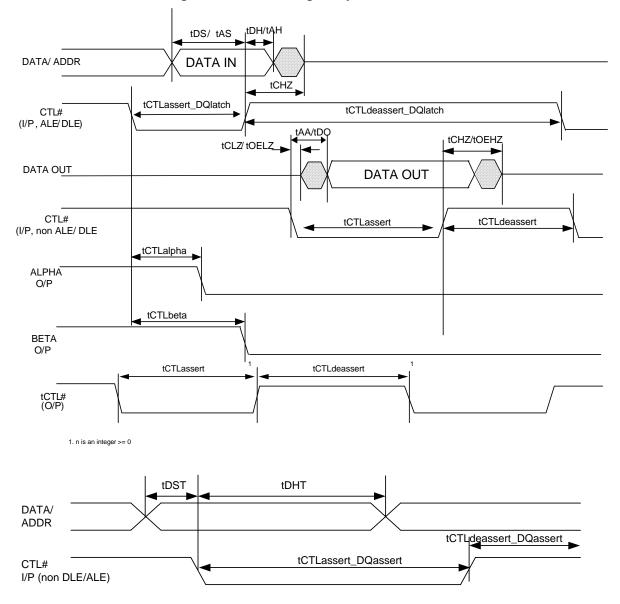

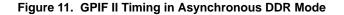

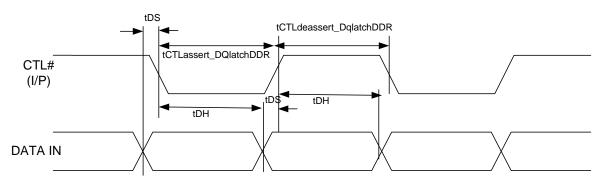

Figure 10. GPIF II Timing in Asynchronous Mode

## Table 10. GPIF II Timing in Asynchronous Mode<sup>[3, 4]</sup>

Note The following parameters assume one state transition

| Parameter               | Description                                                                                                                                                                             | Min | Max | Units |

|-------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|-----|-------|

| tDS                     | Data In to DLE setup time. Valid in DDR async mode.                                                                                                                                     | 2.3 | -   | ns    |

| tDH                     | Data In to DLE hold time. Valid in DDR async mode.                                                                                                                                      | 2   | -   | ns    |

| tAS                     | Address In to ALE setup time                                                                                                                                                            | 2.3 | -   | ns    |

| tAH                     | Address In to ALE hold time                                                                                                                                                             | 2   | -   | ns    |

| tCTLassert              | CTL I/O asserted width for CTRL inputs without DQ input association and for outputs.                                                                                                    | 7   | -   | ns    |

| tCTLdeassert            | CTL I/O deasserted width for CTRL inputs without DQ input association and for outputs.                                                                                                  | 7   | -   | ns    |

| tCTLassert_DQassert     | CTL asserted pulse width for CTL inputs that signify DQ inputs valid<br>at the asserting edge but do not employ in-built latches (ALE/DLE) for<br>those DQ inputs.                      | 20  | -   | ns    |

| tCTLdeassert_DQassert   | CTL deasserted pulse width for CTL inputs that signify DQ input valid<br>at the asserting edge but do not employ in-built latches (ALE/DLE) for<br>those DQ inputs.                     | 7   | -   | ns    |

| tCTLassert_DQdeassert   | CTL asserted pulse width for CTL inputs that signify DQ inputs valid<br>at the deasserting edge but do not employ in-built latches (ALE/DLE)<br>for those DQ inputs.                    | 7   | -   | ns    |

| tCTLdeassert_DQdeassert | CTL deasserted pulse width for CTL inputs that signify DQ inputs valid<br>at the deasserting edge but do not employ in-built latches (ALE/DLE)<br>for those DQ inputs.                  | 20  | -   | ns    |

| tCTLassert_DQlatch      | CTL asserted pulse width for CTL inputs that employ in-built latches (ALE/DLE) to latch the DQ inputs. In this non-DDR case, in-built latches are always close at the deasserting edge. | 7   | _   | ns    |

| tCTLdeassert_DQlatch    | CTL deasserted pulse width for CTL inputs that employ in-built latches (ALE/DLE) to latch the DQ inputs. In this non-DDR case, in-built latches always close at the deasserting edge.   | 10  | -   | ns    |

| tCTLassert_DQlatchDDR   | CTL asserted pulse width for CTL inputs that employ in-built latches (DLE) to latch the DQ inputs in DDR mode.                                                                          | 10  | -   | ns    |

| tCTLdeassert_DQlatchDDR | CTL deasserted pulse width for CTL inputs that employ in-built latches (DLE) to latch the DQ inputs in DDR mode.                                                                        | 10  | -   | ns    |

| tAA                     | DQ/CTL input to DQ output time when DQ change or CTL change needs to be detected and affects internal updates of input and output DQ lines.                                             | -   | 30  | ns    |

| tDO                     | CTL to data out when the CTL change merely enables the output flop update whose data was already established.                                                                           | -   | 25  | ns    |

| tOELZ                   | CTL designated as OE to low-Z. Time when external devices should stop driving data.                                                                                                     | 0   | -   | ns    |

| tOEHZ                   | CTL designated as OE to high-Z                                                                                                                                                          | 8   | 8   | ns    |

| tCLZ                    | CTL (non-OE) to low-Z. Time when external devices should stop driving data.                                                                                                             | 0   | -   | ns    |

| tCHZ                    | CTL (non-OE) to high-Z                                                                                                                                                                  | 30  | 30  | ns    |

| tCTLalpha               | CTL to alpha change at output                                                                                                                                                           | _   | 25  | ns    |

| tCTLbeta                | CTL to beta change at output                                                                                                                                                            | _   | 30  | ns    |

| tDST                    | Addr/data setup when DLE/ALE not used                                                                                                                                                   | 2   | -   | ns    |

| tDHT                    | Addr/data hold when DLE/ALE not used                                                                                                                                                    | 20  | _   | ns    |

#### Notes

All parameters guaranteed by design and validated through characterization.

"alpha" output corresponds to "early output" and "beta" corresponds to "delayed output". Please refer to the GPIFII Designer Tool for the use of these outputs.

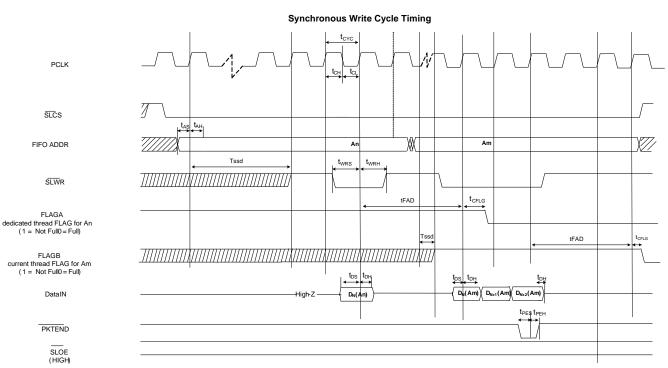

Synchronous Slave FIFO Write Sequence Description

- FIFO address is stable and the signal SLCS# is asserted

- External master or peripheral outputs the data to the data bus

- SLWR# is asserted

- While the SLWR# is asserted, data is written to the FIFO and on the rising edge of the PCLK, the FIFO pointer is incremented

- The FIFO flag is updated after a delay of t<sub>WFLG</sub> from the rising edge of the clock

The same sequence of events is also applicable for burst write

**Note** For the burst mode, SLWR# and SLCS# are asserted for the entire duration, during which all the required data values are written. In this burst write mode, after the SLWR# is asserted, the data on the FIFO data bus is written to the FIFO on every rising edge of PCLK. The FIFO pointer is updated on each rising edge of PCLK.

**Short Packet:** A short packet can be committed to the USB host by using the PKTEND#. The external device or processor should be designed to assert the PKTEND# along with the last word of data and SLWR# pulse corresponding to the last word. The FIFOADDR lines must be held constant during the PKTEND# assertion.

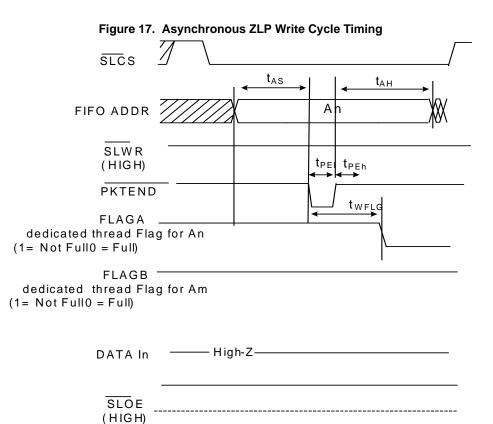

**Zero-Length Packet:** The external device or processor can signal a Zero-Length Packet (ZLP) to FX3 simply by asserting PKTEND#, without asserting SLWR#. SLCS# and address must be driven as shown in Figure 13.

## Figure 13. Synchronous Slave FIFO Write Mode

| Table 12. | Asynchronous | Slave FIFO | Parameters <sup>[6]</sup> |

|-----------|--------------|------------|---------------------------|

|-----------|--------------|------------|---------------------------|

| Parameter | Description                                    | Min | Max  | Units |

|-----------|------------------------------------------------|-----|------|-------|

| tRDI      | SLRD# low                                      | 20  | -    | ns    |

| tRDh      | SLRD# high                                     | 10  | _    | ns    |

| tAS       | Address to SLRD#/SLWR# setup time              | 7   | -    | ns    |

| tAH       | SLRD#/SLWR#/PKTEND to address hold time        | 2   | _    | ns    |

| tRFLG     | SLRD# to FLAGS output propagation delay        | -   | 35   | ns    |

| tFLG      | ADDR to FLAGS output propagation delay         | -   | 22.5 | ns    |

| tRDO      | SLRD# to data valid                            | -   | 25   | ns    |

| tOE       | OE# low to data valid                          | -   | 25   | ns    |

| tLZ       | OE# low to data low-Z                          | 0   | -    | ns    |

| tOH       | SLOE# deassert data output hold                | -   | 22.5 | ns    |

| tWRI      | SLWR# low                                      | 20  | _    | ns    |

| tWRh      | SLWR# high                                     | 10  | _    | ns    |

| tWRS      | Data to SLWR# setup time                       | 7   | -    | ns    |

| tWRH      | SLWR# to Data Hold time                        | 2   | -    | ns    |

| tWFLG     | SLWR#/PKTEND to Flags output propagation delay | -   | 35   | ns    |

| tPEI      | PKTEND low                                     | 20  | -    | ns    |

| tPEh      | PKTEND high                                    | 7.5 | -    | ns    |

| tWRPE     | SLWR# deassert to PKTEND deassert              | 2   | -    | ns    |

#### Note

6. All parameters guaranteed by design and validated through characterization.

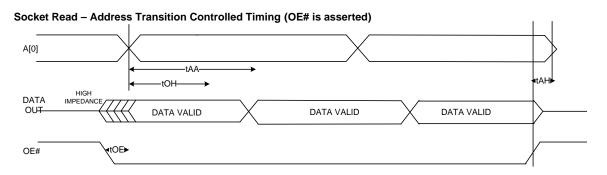

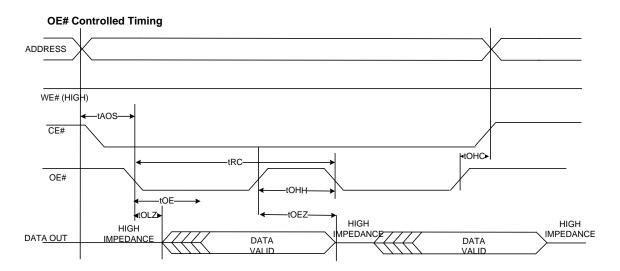

## Host Processor Interface (P-Port) Timing

### Asynchronous SRAM Timing

### Figure 18. Non-multiplexed Asynchronous SRAM Read Timing

| Parameter | Description                    | Min | Max | Unit |

|-----------|--------------------------------|-----|-----|------|

| FREQ      | Interface clock frequency      | -   | 100 | MHz  |

| tCLK      | Clock period                   | 10  | _   | ns   |

| tCLKH     | Clock HIGH time                | 4   | -   | ns   |

| tCLKL     | Clock LOW time                 | 4   | -   | ns   |

| tS        | CE#/WE#/DQ setup time          | 2   | _   | ns   |

| tH        | CE#/WE#/DQ hold time           | 0.5 | -   | ns   |

| tCH       | Clock to data output hold time | 0   | _   | ns   |

| tDS       | Data input setup time          | 2   | _   | ns   |

| tDH       | Clock to data input hold       | 0.5 | _   | ns   |

| tAVDOE    | ADV# HIGH to OE# LOW           | 0   | -   | ns   |

| tAVDWE    | ADV# HIGH to WE# LOW           | 0   | -   | ns   |

| tHZ       | CE# HIGH to Data HIGH-Z        | -   | 8   | ns   |

| tOHZ      | OE# HIGH to Data HIGH-Z        | -   | 8   | ns   |

| tOLZ      | OE# LOW to Data LOW-Z          | 0   | -   | ns   |

| tKW       | Clock to RDY valid             | -   | 8   | ns   |

# Table 15. Synchronous ADMux Timing Parameters<sup>[9]</sup>

## **Serial Peripherals Timing**

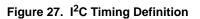

## I<sup>2</sup>C Timing

Note9. All parameters guaranteed by design and validated through characterization.

### SPI Timing Specification

SPI Master Timing for CPHA = 1

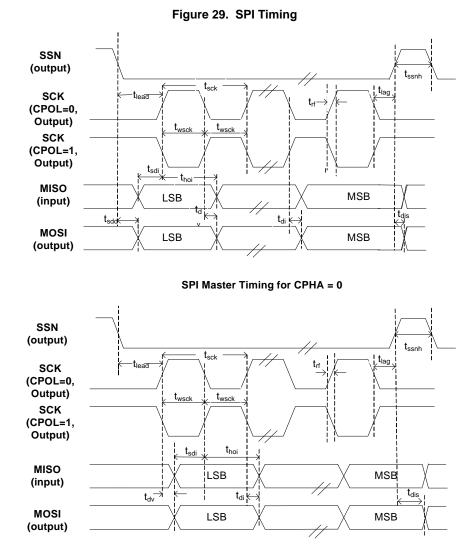

Figure 32. 131-ball WLCSP (5.099 × 4.695 × 0.60 mm) Package Diagram

Note Underfill is required on the board design. Contact fx3@cypress.com for details.

# Acronyms

| Acronym          | Description                                 |  |  |  |

|------------------|---------------------------------------------|--|--|--|

| DMA              | direct memory access                        |  |  |  |

| FIFO             | first in, first out                         |  |  |  |

| GPIF             | general programmable interface              |  |  |  |

| HNP              | host negotiation protocol                   |  |  |  |

| I <sup>2</sup> C | inter-integrated circuit                    |  |  |  |

| l <sup>2</sup> S | inter IC sound                              |  |  |  |

| MISO             | master in, slave out                        |  |  |  |

| MOSI             | master out, slave in                        |  |  |  |

| MMC              | multimedia card                             |  |  |  |

| MSC              | mass storage class                          |  |  |  |

| MTP              | media transfer protocol                     |  |  |  |

| OTG              | on-the-go                                   |  |  |  |

| OVP              | overvoltage protection                      |  |  |  |

| PHY              | physical layer                              |  |  |  |

| PLL              | phase locked loop                           |  |  |  |

| PMIC             | power management IC                         |  |  |  |

| PVT              | process voltage temperature                 |  |  |  |

| RTOS             | real-time operating system                  |  |  |  |

| SCL              | serial clock line                           |  |  |  |

| SCLK             | serial clock                                |  |  |  |

| SD               | secure digital                              |  |  |  |

| SD               | secure digital                              |  |  |  |

| SDA              | serial data clock                           |  |  |  |

| SDIO             | secure digital input / output               |  |  |  |

| SLC              | single-level cell                           |  |  |  |

| SLCS             | Slave Chip Select                           |  |  |  |

| SLOE             | Slave Output Enable                         |  |  |  |

| SLRD             | Slave Read                                  |  |  |  |

| SLWR             | Slave Write                                 |  |  |  |

| SPI              | serial peripheral interface                 |  |  |  |

| SRP              | session request protocol                    |  |  |  |

| SSN              | SPI slave select (Active low)               |  |  |  |

| UART             | universal asynchronous receiver transmitter |  |  |  |

| UVC              | USB Video Class                             |  |  |  |

| USB              | universal serial bus                        |  |  |  |

| WLCSP            | wafer level chip scale package              |  |  |  |

# **Document Conventions**

## **Units of Measure**

| Symbol | Unit of Measure      |  |  |  |

|--------|----------------------|--|--|--|

| °C     | degree Celsius       |  |  |  |

| μA     | microamperes         |  |  |  |

| μs     | microseconds         |  |  |  |

| mA     | milliamperes         |  |  |  |

| Mbps   | Megabits per second  |  |  |  |

| MBps   | Megabytes per second |  |  |  |

| MHz    | mega hertz           |  |  |  |

| ms     | milliseconds         |  |  |  |

| ns     | nanoseconds          |  |  |  |

| Ω      | ohms                 |  |  |  |

| pF     | pico Farad           |  |  |  |

| V      | volts                |  |  |  |

# **Document History Page**

| Document Title: CYUSB301X/CYUSB201X, EZ-USB <sup>®</sup> FX3: SuperSpeed USB Controller<br>Document Number: 001-52136 |         |                    |                    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

|-----------------------------------------------------------------------------------------------------------------------|---------|--------------------|--------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Revision                                                                                                              | ECN     | Orig. of<br>Change | Submission<br>Date | Description of Change                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| **                                                                                                                    | 2669761 | VSO /<br>PYRS      | 03/06/2009         | New data sheet                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| *A                                                                                                                    | 2758370 | VSO                | 09/01/2009         | Updated the part# from CYX01XXBB to CYUSB3011-BZXI<br>Changed the title from "ADVANCE" to "ADVANCE INFORMATION"<br>In page 1, the second bullet (Flexible Host Interface), add "32-bit, 100 MHz" to<br>first sub bullet.<br>In page 1, changed the second bullet "Flexible Host Interface" to General<br>Programmable Interface".<br>In page 1, the second bullet (Flexible Host Interface), removed "DMA Slave<br>Support" and "MMC Slave support with Pass through Boot" sub bullets.<br>In page 1, third bullet, changed "50 μA with Core Power" to "60 μA with Core<br>Power"<br>In page 1, fifth bullet, added "at 1 MHz"<br>In page 1, seventh bullet, added "up to 4MHz" to UART<br>In page 1, Applications Section, move "Digital Still Cameras" to second line.<br>In page 1, Applications Section, move "Digital Still Cameras" to second line.<br>In page 1, updated Logic Block Diagram.<br>In page 2, removed the section of "Product Interface"<br>In page 2, removed the section of "Product Interface"<br>In page 2, removed the section of "Other Interface"<br>In page 2, removed the section of "Other Interface"<br>In page 2, added a section of "GPIF II"<br>In page 2, added a section of "GPIF II"<br>In page 2, added a section of "Boot Options"<br>In page 2, added a section of "Roter Interface"<br>In page 2, added a section of "ReNumeration"<br>In page 2, added a section of "Power"<br>In the section of "Package", replaced "West Bridge USB 3.0 Platform" by FX3.<br>In the section of "Package", added 0.8 mm pitch in front of BGA.<br>Added Pin List (Table 1) |

| *B                                                                                                                    | 2779196 | VSO/PYRS           | 09/29/2009         | Features:<br>Added the thrid bullet "Fully accessible 32-bit ARM9 core with 512kB of<br>embedded SRAM"<br>Added the thrid line "EZ USB™ Software and DVK for easy code development"<br>Table 1: Pin 74, corrected to NC - No Connect.<br>Changed title to EZ-USB™ FX3: SuperSpeed USB Controller                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| *C                                                                                                                    | 2823531 | OSG                | 12/08/2009         | Added data sheet to the USB 3.0 EROS spec 001-51884. No technical updates.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| *D                                                                                                                    | 3080927 | OSG                | 11/08/2010         | Changed status from Advance to Preliminary<br>Changed part number from CYUSB3011 to CYUSB3014<br>Added the following sections: Power, Digital I/Os, Digital I/Os, System-level<br>ESD, Electrical Specifications, AC Timing Parameters, Reset Sequence,<br>Package Diagram<br>Added DC Specifications table<br>Updated feature list<br>Updated Pin List<br>Added support for selectable clock input frequencies.<br>Updated block diagram<br>Updated part number<br>Updated package diagram                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

# Document History Page (continued)

| Revision | ECN     | Orig. of<br>Change | Submission<br>Date | Description of Change                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

|----------|---------|--------------------|--------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| *0       | 4368374 | RSKV               | 05/02/2014         | Updated Package Diagram:<br>spec 001-62221 – Changed revision from *B to *C.<br>Updated to new template.<br>Completing Sunset Review.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| *P       | 4474200 | ANOP               | 08/14/2014         | Added CYUSB201x MPNs, ball map, and pin list to the datasheet.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| *Q       | 4668496 | DBIR               | 02/24/2015         | Updated Features.<br>Updated Logic Block Diagram.<br>Updated Functional Description:<br>Added "For a complete list of related documentation, click here." at the end<br>Added More Information.<br>Updated Functional Overview:<br>Updated Application Examples:<br>Updated Figure 1.<br>Updated Figure 2.<br>Updated description.<br>Removed Figure "USB Interface Signals".<br>Updated description.<br>Removed Figure 6.<br>Updated Figure 6.<br>Updated Reset:<br>Updated Hard Reset:<br>Updated description.<br>Updated Pin Description:<br>Updated Pin Description:<br>Updated Table 7:<br>Updated entire table.<br>Modified CVDDQ power domain description.<br>Removed Table "CYUSB3011 and CYUSB3013 Pin List (GPIF II with 16-bit<br>Data Bus Width)".<br>Removed Table "CYUSB2014 Pin List (GPIF II with 32-bit Data Bus Width)"<br>Updated Electrical Specifications:<br>Updated Sparameter and its details.<br>Updated Siave FIFO Interface:<br>Updated Siave FIFO Interface:<br>Updated Figure 12.<br>Updated Figure 13.<br>Updated Table 11.<br>Updated AC Timing Parameters:<br>Added Host Processor Interface (P-Port) Timing.<br>Updated Acronyms.<br>Added Errata.<br>Replaced West Bridge Benicia with FX3. |

| *R       | 4703347 | AMDK               | 03/27/2015         | Updated Slave FIFO Interface:<br>Updated Synchronous Slave FIFO Read Sequence Description:<br>Updated Figure 12.<br>Updated Synchronous Slave FIFO Write Sequence Description:<br>Updated Figure 13.<br>Updated Table 11:<br>Updated minimum value of tSSD parameter.<br>Added tACCD, tFAD parameters and their details.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| *S       | 5160624 | AJAI               | 04/07/2016         | Removed ISS parameter.<br>Added item 6 in Errata.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

# Document History Page (continued)

| Document Title: CYUSB301X/CYUSB201X, EZ-USB <sup>®</sup> FX3: SuperSpeed USB Controller<br>Document Number: 001-52136 |         |                    |                    |                                                                                                                                                                                                                                                                                                                                                                                |

|-----------------------------------------------------------------------------------------------------------------------|---------|--------------------|--------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Revision                                                                                                              | ECN     | Orig. of<br>Change | Submission<br>Date | Description of Change                                                                                                                                                                                                                                                                                                                                                          |

| *Т                                                                                                                    | 5306567 | MDDD               | 06/29/2016         | Updated AC Timing Parameters:<br>Updated GPIF II Timing:<br>Updated Table 9:<br>Changed maximum value of t <sub>CO</sub> parameter from 8 ns to 7 ns.<br>Updated Slave FIFO Interface:<br>Updated Synchronous Slave FIFO Write Sequence Description:<br>Updated Table 11:<br>Changed maximum value of t <sub>CO</sub> parameter from 8 ns to 7 ns.<br>Updated to new template. |

| *U                                                                                                                    | 5703914 | GNKK               | 04/20/2017         | Updated the Cypress logo and copyright information.                                                                                                                                                                                                                                                                                                                            |

## Sales, Solutions, and Legal Information

### Worldwide Sales and Design Support

Cypress maintains a worldwide network of offices, solution centers, manufacturer's representatives, and distributors. To find the office closest to you, visit us at Cypress Locations.

### Products

| ARM <sup>®</sup> Cortex <sup>®</sup> Microcontrollers | cypress.com/arm        |

|-------------------------------------------------------|------------------------|

| Automotive                                            | cypress.com/automotive |

| Clocks & Buffers                                      | cypress.com/clocks     |

| Interface                                             | cypress.com/interface  |

| Internet of Things                                    | cypress.com/iot        |

| Memory                                                | cypress.com/memory     |

| Microcontrollers                                      | cypress.com/mcu        |

| PSoC                                                  | cypress.com/psoc       |

| Power Management ICs                                  | cypress.com/pmic       |

| Touch Sensing                                         | cypress.com/touch      |

| USB Controllers                                       | cypress.com/usb        |

| Wireless Connectivity                                 | cypress.com/wireless   |

## **PSoC<sup>®</sup> Solutions**

PSoC 1 | PSoC 3 | PSoC 4 | PSoC 5LP | PSoC 6

#### **Cypress Developer Community**

Forums | WICED IOT Forums | Projects | Video | Blogs | Training | Components

#### **Technical Support**

cypress.com/support

© Cypress Semiconductor Corporation, 2009-2017. This document is the property of Cypress Semiconductor Corporation and its subsidiaries, including Spansion LLC ("Cypress"). This document, including any software or firmware included or referenced in this document ("Software"), is owned by Cypress under the intellectual property laws and treaties of the United States and other countries worldwide. Cypress reserves all rights under such laws and treaties and not except as specifically stated in this paragraph, grant any license under its patents, copyrights, trademarks, or other intellectual property rights. If the Software is not accompanied by a license agreement and you do not otherwise have a written agreement with Cypress governing the use of the Software, then Cypress berefy grants you a personal, non-exclusive, nontransferable license (without the right to sublicense) (1) under its copyright rights in the Software (a) for Software provided in source code form, to modify and reproduce the Software solely for use with Cypress hardware products, only internally within your organization, and (b) to distribute the Software in binary code form externally to end users (either directly or indirectly through resellers and distributors), solely for use on Cypress hardware product units, and (2) under those claims of Cypress's patents that are infringed by the Software (as provided by Cypress, unmodified) to make, use, distribute, and import the Software solely for use with Cypress hardware products. Any other use, reproduction, modification, translation, or compilation of the Software is prohibited.