Welcome to E-XFL.COM

#### Understanding <u>Embedded - DSP (Digital</u> <u>Signal Processors)</u>

Embedded - DSP (Digital Signal Processors) are specialized microprocessors designed to perform complex mathematical computations on digital signals in real-time. Unlike general-purpose processors, DSPs are optimized for high-speed numeric processing tasks, making them ideal for applications that require efficient and precise manipulation of digital data. These processors are fundamental in converting and processing signals in various forms, including audio, video, and communication signals, ensuring that data is accurately interpreted and utilized in embedded systems.

#### Applications of <u>Embedded - DSP (Digital</u> <u>Signal Processors)</u>

#### Details

| Detuns                  |                                                                        |

|-------------------------|------------------------------------------------------------------------|

| Product Status          | Obsolete                                                               |

| Туре                    | Floating Point                                                         |

| Interface               | Host Interface, Link Port, Serial Port                                 |

| Clock Rate              | 40MHz                                                                  |

| Non-Volatile Memory     | External                                                               |

| On-Chip RAM             | 512kB                                                                  |

| Voltage - I/O           | 3.30V                                                                  |

| Voltage - Core          | 3.30V                                                                  |

| Operating Temperature   | 0°C ~ 85°C (TC)                                                        |

| Mounting Type           | Surface Mount                                                          |

| Package / Case          | 240-BFQFP Exposed Pad                                                  |

| Supplier Device Package | 240-MQFP-EP (32x32)                                                    |

| Purchase URL            | https://www.e-xfl.com/product-detail/analog-devices/adsp-21060lksz-160 |

|                         |                                                                        |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

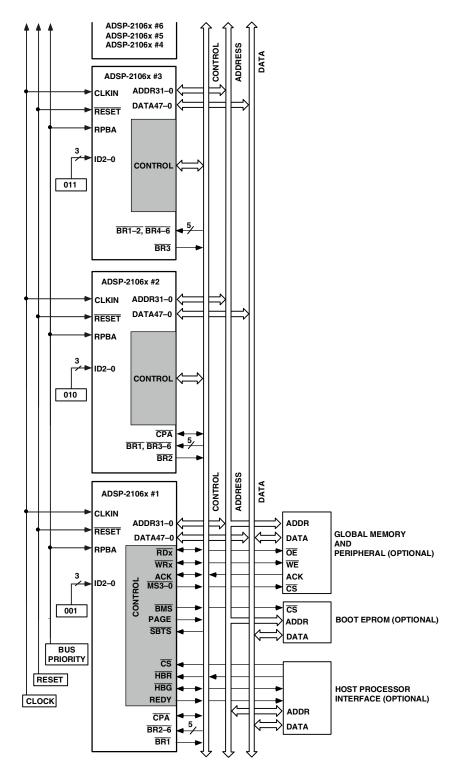

Figure 3. Shared Memory Multiprocessing System

### **Link Ports**

The ADSP-2106x features six 4-bit link ports that provide additional I/O capabilities. The link ports can be clocked twice per cycle, allowing each to transfer eight bits of data per cycle. Linkport I/O is especially useful for point-to-point interprocessor communication in multiprocessing systems.

The link ports can operate independently and simultaneously, with a maximum data throughput of 240M bytes/s. Link port data is packed into 32- or 48-bit words, and can be directly read by the core processor or DMA-transferred to on-chip memory.

Each link port has its own double-buffered input and output registers. Clock/acknowledge handshaking controls link port transfers. Transfers are programmable as either transmit or receive.

### **Program Booting**

The internal memory of the ADSP-2106x can be booted at system power-up from an 8-bit EPROM, a host processor, or through one of the link ports. Selection of the boot source is controlled by the BMS (boot memory select), EBOOT (EPROM Boot), and LBOOT (link/host boot) pins. 32-bit and 16-bit host processors can be used for booting. The processor also supports a no-boot mode in which instruction execution is sourced from the external memory.

## **DEVELOPMENT TOOLS**

Analog Devices supports its processors with a complete line of software and hardware development tools, including integrated development environments (which include CrossCore<sup>®</sup> Embedded Studio and/or VisualDSP++<sup>®</sup>), evaluation products, emulators, and a wide variety of software add-ins.

### Integrated Development Environments (IDEs)

For C/C++ software writing and editing, code generation, and debug support, Analog Devices offers two IDEs.

The newest IDE, CrossCore Embedded Studio, is based on the Eclipse<sup>™</sup> framework. Supporting most Analog Devices processor families, it is the IDE of choice for future processors, including multicore devices. CrossCore Embedded Studio seamlessly integrates available software add-ins to support real time operating systems, file systems, TCP/IP stacks, USB stacks, algorithmic software modules, and evaluation hardware board support packages. For more information visit www.analog.com/cces.

The other Analog Devices IDE, VisualDSP++, supports processor families introduced prior to the release of CrossCore Embedded Studio. This IDE includes the Analog Devices VDK real time operating system and an open source TCP/IP stack. For more information visit www.analog.com/visualdsp. Note that VisualDSP++ will not support future Analog Devices processors.

### **EZ-KIT Lite Evaluation Board**

For processor evaluation, Analog Devices provides wide range of EZ-KIT Lite<sup>®</sup> evaluation boards. Including the processor and key peripherals, the evaluation board also supports on-chip emulation capabilities and other evaluation and development features. Also available are various EZ-Extenders<sup>®</sup>, which are daughter cards delivering additional specialized functionality, including audio and video processing. For more information visit www.analog.com and search on "ezkit" or "ezextender".

## **EZ-KIT Lite Evaluation Kits**

For a cost-effective way to learn more about developing with Analog Devices processors, Analog Devices offer a range of EZ-KIT Lite evaluation kits. Each evaluation kit includes an EZ-KIT Lite evaluation board, directions for downloading an evaluation version of the available IDE(s), a USB cable, and a power supply. The USB controller on the EZ-KIT Lite board connects to the USB port of the user's PC, enabling the chosen IDE evaluation suite to emulate the on-board processor in-circuit. This permits the customer to download, execute, and debug programs for the EZ-KIT Lite system. It also supports in-circuit programming of the on-board Flash device to store user-specific boot code, enabling standalone operation. With the full version of Cross-Core Embedded Studio or VisualDSP++ installed (sold separately), engineers can develop software for supported EZ-KITs or any custom system utilizing supported Analog Devices processors.

### Software Add-Ins for CrossCore Embedded Studio

Analog Devices offers software add-ins which seamlessly integrate with CrossCore Embedded Studio to extend its capabilities and reduce development time. Add-ins include board support packages for evaluation hardware, various middleware packages, and algorithmic modules. Documentation, help, configuration dialogs, and coding examples present in these add-ins are viewable through the CrossCore Embedded Studio IDE once the add-in is installed.

### **Board Support Packages for Evaluation Hardware**

Software support for the EZ-KIT Lite evaluation boards and EZ-Extender daughter cards is provided by software add-ins called Board Support Packages (BSPs). The BSPs contain the required drivers, pertinent release notes, and select example code for the given evaluation hardware. A download link for a specific BSP is located on the web page for the associated EZ-KIT or EZ-Extender product. The link is found in the *Product Download* area of the product web page.

### **Middleware Packages**

Analog Devices separately offers middleware add-ins such as real time operating systems, file systems, USB stacks, and TCP/IP stacks. For more information see the following web pages:

- www.analog.com/ucos3

- www.analog.com/ucfs

- www.analog.com/ucusbd

- www.analog.com/lwip

#### **Algorithmic Modules**

To speed development, Analog Devices offers add-ins that perform popular audio and video processing algorithms. These are available for use with both CrossCore Embedded Studio and VisualDSP++. For more information visit www.analog.com and search on "Blackfin software modules" or "SHARC software modules".

#### Designing an Emulator-Compatible DSP Board (Target)

For embedded system test and debug, Analog Devices provides a family of emulators. On each JTAG DSP, Analog Devices supplies an IEEE 1149.1 JTAG Test Access Port (TAP). In-circuit emulation is facilitated by use of this JTAG interface. The emulator accesses the processor's internal features via the processor's TAP, allowing the developer to load code, set breakpoints, and view variables, memory, and registers. The processor must be halted to send data and commands, but once an operation is completed by the emulator, the DSP system is set to run at full speed with no impact on system timing. The emulators require the target board to include a header that supports connection of the DSP's JTAG port to the emulator.

For details on target board design issues including mechanical layout, single processor connections, signal buffering, signal termination, and emulator pod logic, see the *EE-68: Analog Devices JTAG Emulation Technical Reference* on the Analog Devices website (www.analog.com)—use site search on "EE-68." This document is updated regularly to keep pace with improvements to emulator support.

## **ADDITIONAL INFORMATION**

This data sheet provides a general overview of the ADSP-2106x architecture and functionality. For detailed information on the ADSP-21000 family core architecture and instruction set, refer to the *ADSP-2106x SHARC User's Manual*, Revision 2.1.

### **RELATED SIGNAL CHAINS**

A *signal chain* is a series of signal-conditioning electronic components that receive input (data acquired from sampling either real-time phenomena or from stored data) in tandem, with the output of one portion of the chain supplying input to the next. Signal chains are often used in signal processing applications to gather and process data or to apply system controls based on analysis of real-time phenomena. For more information about this term and related topics, see the "signal chain" entry in the Glossary of EE Terms on the Analog Devices website.

Analog Devices eases signal processing system development by providing signal processing components that are designed to work together well. A tool for viewing relationships between specific applications and related components is available on the www.analog.com website. The Application Signal Chains page in the Circuits from the Lab<sup>TM</sup> site (http://www.analog.com/signalchains) provides:

- Graphical circuit block diagram presentation of signal chains for a variety of circuit types and applications

- Drill down links for components in each chain to selection guides and application information

- Reference designs applying best practice design techniques

#### Table 3. Pin Descriptions (Continued)

| Pin      | Туре | Function                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |  |  |  |  |

|----------|------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| TFSx     | I/O  | Transmit Frame Sync (Serial Ports 0, 1).                                                                                                                                                                                                                                                                                                                                                                                                                                                |  |  |  |  |

| RFSx     | I/O  | Receive Frame Sync (Serial Ports 0, 1).                                                                                                                                                                                                                                                                                                                                                                                                                                                 |  |  |  |  |

| LxDAT3-0 | I/O  | <b>Link Port Data (Link Ports 0–5).</b> Each LxDAT pin has a 50 k $\Omega$ internal pull-down resistor that is enabled or disabled by the LPDRD bit of the LCOM register.                                                                                                                                                                                                                                                                                                               |  |  |  |  |

| LxCLK    | I/O  | <b>Link Port Clock (Link Ports 0–5).</b> Each LxCLK pin has a 50 k $\Omega$ internal pull-down resistor that is enabled or disabled by the LPDRD bit of the LCOM register.                                                                                                                                                                                                                                                                                                              |  |  |  |  |

| LxACK    | I/O  | <b>Link Port Acknowledge (Link Ports 0–5).</b> Each LxACK pin has a 50 k $\Omega$ internal pull-down resistor that is enabled or disabled by the LPDRD bit of the LCOM register.                                                                                                                                                                                                                                                                                                        |  |  |  |  |

| EBOOT    | 1    | <b>EPROM Boot Select.</b> When EBOOT is high, the ADSP-2106x is configured for booting from an 8-bit EPROM. When EBOOT is low, the LBOOT and BMS inputs determine booting mode. See the table in the BMS pin description below. This signal is a system configuration selection that should be hardwired.                                                                                                                                                                               |  |  |  |  |

| LBOOT    | I    | <b>Link Boot.</b> When LBOOT is high, the ADSP-2106x is configured for link port booting. When LBOOT is low, the ADSP-2106x is configured for host processor booting or no booting. See the table in the BMS pin description below. This signal is a system configuration selection that should be hardwired.                                                                                                                                                                           |  |  |  |  |

| BMS      | I/OT | <b>Boot Memory Select.</b> <i>Output</i> : Used as chip select for boot EPROM devices (when EBOOT = 1, LBOOT = 0).<br>In a multiprocessor system, BMS is output by the bus master. <i>Input</i> : When low, indicates that no booting will occur and that ADSP-2106x will begin executing instructions from external memory. See table below. This input is a system configuration selection that should be hardwired. *Three-statable only in EPROM boot mode (when BMS is an output). |  |  |  |  |

|          |      | EBOOT LBOOT BMS Booting Mode                                                                                                                                                                                                                                                                                                                                                                                                                                                            |  |  |  |  |

|          |      | 1 0 Output EPROM (Connect BMS to EPROM chip select.)                                                                                                                                                                                                                                                                                                                                                                                                                                    |  |  |  |  |

|          |      | 0 0 1 (Input) Host Processor                                                                                                                                                                                                                                                                                                                                                                                                                                                            |  |  |  |  |

|          |      | 0 1 1 (Input) Link Port                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |  |  |  |  |

|          |      | 0 0 0 (Input) No Booting. Processor executes from external memory.                                                                                                                                                                                                                                                                                                                                                                                                                      |  |  |  |  |

|          |      | 0 1 0 (Input) Reserved   1 1 x (Input) Reserved                                                                                                                                                                                                                                                                                                                                                                                                                                         |  |  |  |  |

| CLKIN    | I    | <b>Clock In.</b> External clock input to the ADSP-2106x. The instruction cycle rate is equal to CLKIN. CLKIN should not be halted, changed, or operated below the minimum specified frequency.                                                                                                                                                                                                                                                                                          |  |  |  |  |

| RESET    | I/A  | <b>Processor Reset.</b> Resets the ADSP-2106x to a known state and begins program execution at the program memory location specified by the hardware reset vector address. This input must be asserted (low) at power-up.                                                                                                                                                                                                                                                               |  |  |  |  |

| ТСК      | 1    | Test Clock (JTAG). Provides an asynchronous clock for JTAG boundary scan.                                                                                                                                                                                                                                                                                                                                                                                                               |  |  |  |  |

| TMS      | I/S  | Test Mode Select (JTAG). Used to control the test state machine. TMS has a 20 k $\Omega$ internal pull-up resistor.                                                                                                                                                                                                                                                                                                                                                                     |  |  |  |  |

| TDI      | I/S  | <b>Test Data Input (JTAG).</b> Provides serial data for the boundary scan logic. TDI has a 20 k $\Omega$ internal pull-up resistor.                                                                                                                                                                                                                                                                                                                                                     |  |  |  |  |

| TDO      | 0    | Test Data Output (JTAG). Serial scan output of the boundary scan path.                                                                                                                                                                                                                                                                                                                                                                                                                  |  |  |  |  |

| TRST     | I/A  | <b>Test Reset (JTAG).</b> Resets the test state machine. TRST must be asserted (pulsed low) after power-up or held low for proper operation of the ADSP-2106x. TRST has a 20 k $\Omega$ internal pull-up resistor.                                                                                                                                                                                                                                                                      |  |  |  |  |

| EMU      | 0    | Emulation Status. Must be connected to the ADSP-2106x EZ-ICE target board connector only.                                                                                                                                                                                                                                                                                                                                                                                               |  |  |  |  |

| ICSA     | 0    | Reserved, leave unconnected.                                                                                                                                                                                                                                                                                                                                                                                                                                                            |  |  |  |  |

| VDD      | Р    | <b>Power Supply;</b> nominally 5.0 V dc for 5 V devices or 3.3 V dc for 3.3 V devices. (30 pins).                                                                                                                                                                                                                                                                                                                                                                                       |  |  |  |  |

| GND      | G    | Power Supply Return. (30 pins).                                                                                                                                                                                                                                                                                                                                                                                                                                                         |  |  |  |  |

| NC       |      | <b>Do Not Connect.</b> Reserved pins which must be left open and unconnected.                                                                                                                                                                                                                                                                                                                                                                                                           |  |  |  |  |

T = Three-State (when  $\overline{SBTS}$  is asserted, or when the ADSP-2106x is a bus slave)

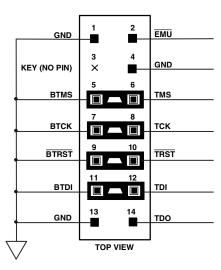

## TARGET BOARD CONNECTOR FOR EZ-ICE PROBE

The ADSP-2106x EZ-ICE<sup>®</sup> Emulator uses the IEEE 1149.1JTAG test access port of the ADSP-2106x to monitor and control the target board processor during emulation. The EZ-ICE probe requires the ADSP-2106x's CLKIN, TMS, TCK, TRST, TDI, TDO, EMU, and GND signals be made accessible on the target system via a 14-pin connector (a 2-row 7-pin strip header) such as that shown in Figure 5. The EZ-ICE probe plugs directly onto this connector for chip-on-board emulation. You must add this connector to your target board design if you intend to use the ADSP-2106x EZ-ICE. The total trace length between the EZ-ICE connector and the furthest device sharing the EZ-ICE JTAG pin should be limited to 15 inches maximum for guaranteed operation. This length restriction must include EZ-ICE JTAG signals that are routed to one or more ADSP-2106x devices, or a combination of ADSP-2106x devices and other JTAG devices on the chain.

Figure 5. Target Board Connector for ADSP-2106x EZ-ICE Emulator (Jumpers in Place)

The 14-pin, 2-row pin strip header is keyed at the Pin 3 location—Pin 3 must be removed from the header. The pins must be 0.025 inch square and at least 0.20 inch in length. Pin spacing should be  $0.1 \times 0.1$  inches. Pin strip headers are available from vendors such as 3M, McKenzie, and Samtec. The BTMS, BTCK, BTRST, and BTDI signals are provided so that the test access port can also be used for board-level testing.

When the connector is not being used for emulation, place jumpers on the Bxxx pins as shown in Figure 5. If you are not going to use the test access port for board testing, tie  $\overline{\text{BTRST}}$  to GND and tie or pull up BTCK to V<sub>DD</sub>. The  $\overline{\text{TRST}}$  pin must be asserted (pulsed low) after power-up (through  $\overline{\text{BTRST}}$  on the connector) or held low for proper operation of the ADSP-2106x. None of the Bxxx pins (Pins 5, 7, 9, and 11) are connected on the EZ-ICE probe.

The JTAG signals are terminated on the EZ-ICE probe as shown in Table 4.

| Signal            | Termination                                                                                                 |

|-------------------|-------------------------------------------------------------------------------------------------------------|

| TMS               | Driven Through 22 $\Omega$ Resistor (16 mA Driver)                                                          |

| ТСК               | Driven at 10 MHz Through 22 $\Omega$ Resistor (16 mA Driver)                                                |

| TRST <sup>1</sup> | Active Low Driven Through 22 $\Omega$ Resistor (16 mA Driver) (Pulled-Up by On-Chip 20 k $\Omega$ Resistor) |

| TDI               | Driven by 22 $\Omega$ Resistor (16 mA Driver)                                                               |

| TDO               | One TTL Load, Split Termination (160/220)                                                                   |

| CLKIN             | One TTL Load, Split Termination (160/220)                                                                   |

| EMU               | Active Low 4.7 k $\Omega$ Pull-Up Resistor, One TTL Load (Open-Drain Output from the DSP)                   |

<sup>1</sup>TRST is driven low until the EZ-ICE probe is turned on by the emulator at software start-up. After software start-up, is driven high.

Figure 6 shows JTAG scan path connections for systems that contain multiple ADSP-2106x processors.

Connecting CLKIN to Pin 4 of the EZ-ICE header is optional. The emulator only uses CLKIN when directed to perform operations such as starting, stopping, and single-stepping multiple ADSP-2106xs in a synchronous manner. If you do not need these operations to occur synchronously on the multiple processors, simply tie Pin 4 of the EZ-ICE header to ground.

If synchronous multiprocessor operations are needed and CLKIN is connected, clock skew between the multiple ADSP-2106x processors and the CLKIN pin on the EZ-ICE header must be minimal. If the skew is too large, synchronous operations may be off by one or more cycles between processors. For synchronous multiprocessor operation TCK, TMS, CLKIN, and EMU should be treated as critical signals in terms of skew, and should be laid out as short as possible on your board. If TCK, TMS, and CLKIN are driving a large number of ADSP-2106xs (more than eight) in your system, then treat them as a "clock tree" using multiple drivers to minimize skew. (See Figure 7 and "JTAG Clock Tree" and "Clock Distribution" in the "High Frequency Design Considerations" section of the *ADSP-2106x User's Manual*, Revision 2.1.)

If synchronous multiprocessor operations are not needed (i.e., CLKIN is not connected), just use appropriate parallel termination on TCK and TMS. TDI, TDO, EMU and TRST are not critical signals in terms of skew.

For complete information on the SHARC EZ-ICE, see the *ADSP-21000 Family JTAG EZ-ICE User's Guide and Reference*.

### **EXTERNAL POWER DISSIPATION (3.3 V)**

Total power dissipation has two components, one due to internal circuitry and one due to the switching of external output drivers. Internal power dissipation is dependent on the instruction execution sequence and the data operands involved. Internal power dissipation is calculated in the following way:

$$P_{INT} = I_{DDIN} \times V_{DD}$$

The external component of total power dissipation is caused by the switching of output pins. Its magnitude depends on:

- the number of output pins that switch during each cycle (O)

- the maximum frequency at which they can switch (f)

- their load capacitance (C)

- their voltage swing  $(V_{DD})$

and is calculated by:

$P_{EXT} = O \times C \times V_{DD}^{2} \times f$

The load capacitance should include the processor's package capacitance (CIN). The switching frequency includes driving the load high and then back low. Address and data pins can

drive high and low at a maximum rate of  $1/(2t_{CK})$ . The write strobe can switch every cycle at a frequency of  $1/t_{CK}$ . Select pins switch at  $1/(2t_{CK})$ , but selects can switch on each cycle.

*Example:* Estimate P<sub>EXT</sub> with the following assumptions:

- A system with one bank of external data memory RAM (32-bit)

- + Four 128K  $\times$  8 RAM chips are used, each with a load of 10 pF

- External data memory writes occur every other cycle, a rate of  $1/(4t_{\mbox{\tiny CK}}),$  with 50% of the pins switching

- The instruction cycle rate is 40 MHz ( $t_{CK} = 25$  ns)

The  $P_{\mbox{\scriptsize EXT}}$  equation is calculated for each class of pins that can drive:

A typical power consumption can now be calculated for these conditions by adding a typical internal power dissipation:

$$P_{\text{TOTAL}} = P_{EXT} + (I_{DDIN2} \times 3.3 \text{ V})$$

Note that the conditions causing a worst-case  $P_{EXT}$  are different from those causing a worst-case  $P_{INT}$ . Maximum  $P_{INT}$  cannot occur while 100% of the output pins are switching from all ones to all zeros. Note also that it is not common for an application to have 100% or even 50% of the outputs switching simultaneously.

| Pin Type | No. of Pins | % Switching | ×C        | ×f          | $\times V_{DD}^{2}$ | = P <sub>EXT</sub> |

|----------|-------------|-------------|-----------|-------------|---------------------|--------------------|

| Address  | 15          | 50          | × 44.7 pF | imes 10 MHz | × 10.9 V            | = 0.037 W          |

| MS0      | 1           | 0           | × 44.7 pF | imes 10 MHz | × 10.9 V            | = 0.000 W          |

| WR       | 1           | -           | × 44.7 pF | imes 20 MHz | × 10.9 V            | = 0.010 W          |

| Data     | 32          | 50          | × 14.7 pF | imes 10 MHz | × 10.9 V            | = 0.026 W          |

| ADDRCLK  | 1           | -           | × 4.7 pF  | imes 20 MHz | × 10.9 V            | = 0.001 W          |

P<sub>EXT</sub> = 0.074 W

## **ABSOLUTE MAXIMUM RATINGS**

Stresses greater than those listed Table 7 may cause permanent damage to the device. These are stress ratings only; functional operation of the device at these or any other conditions greater

than those indicated in the operational sections of this specification is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

#### Table 7. Absolute Maximum Ratings

|                                   | ADSP-21060/ADSP-21060C<br>ADSP-21062 | ADSP-21060L/ADSP-21060LC<br>ADSP-21062L |

|-----------------------------------|--------------------------------------|-----------------------------------------|

| Parameter                         | 5 V                                  | 3.3 V                                   |

| Supply Voltage (V <sub>DD</sub> ) | -0.3 V to +7.0 V                     | -0.3 V to +4.6 V                        |

| Input Voltage                     | -0.5 V to V <sub>DD</sub> + 0.5 V    | -0.5 V to V <sub>DD</sub> $+0.5$ V      |

| Output Voltage Swing              | -0.5 V to V <sub>DD</sub> + 0.5 V    | -0.5 V to V <sub>DD</sub> + 0.5 V       |

| Load Capacitance                  | 200 pF                               | 200 pF                                  |

| Storage Temperature Range         | -65°C to +150°C                      | –65°C to +150°C                         |

| Lead Temperature (5 seconds)      | 280°C                                | 280°C                                   |

| Junction Temperature Under Bias   | 130°C                                | 130°C                                   |

### Table 6. External Power Calculations (3.3 V Devices)

## **ESD CAUTION**

**ESD** (electrostatic discharge) sensitive device. Charged devices and circuit boards can discharge without detection. Although this product features patented or proprietary protection circuitry, damage may occur on devices subjected to high energy ESD. Therefore, proper ESD precautions should be taken to avoid performance degradation or loss of functionality.

### PACKAGE MARKING INFORMATION

Figure 8 and Table 8 provide information on detail contained within the package marking for the ADSP-2106x processors (actual marking format may vary). For a complete listing of product availability, see Ordering Guide on Page 62.

Figure 8. Typical Package Brand

#### Table 8. Package Brand Information

| Brand Key | Field Description     |

|-----------|-----------------------|

| t         | Temperature Range     |

| рр        | Package Type          |

| Z         | Lead (Pb) Free Option |

| ссс       | See Ordering Guide    |

| vvvvv.x   | Assembly Lot Code     |

| n.n       | Silicon Revision      |

| yyww      | Date Code             |

### TIMING SPECIFICATIONS

The ADSP-2106x processors are available at maximum processor speeds of 33 MHz (–133), and 40 MHz (–160). The timing specifications are based on a CLKIN frequency of 40 MHz  $t_{CK} = 25$  ns). The DT derating factor enables the calculation for timing specifications within the min to max range of the  $t_{CK}$  specification (see Table 9). DT is the difference between the derated CLKIN period and a CLKIN period of 25 ns:

#### $DT = t_{\rm CK} - 25 \text{ ns}$

Use the exact timing information given. Do not attempt to derive parameters from the addition or subtraction of others. While addition or subtraction would yield meaningful results for an individual device, the values given in this data sheet reflect statistical variations and worst cases. Consequently, you cannot meaningfully add parameters to derive longer times.

For voltage reference levels, see Figure 28 on Page 48 under Test Conditions.

*Timing Requirements* apply to signals that are controlled by circuitry external to the processor, such as the data input for a read operation. Timing requirements guarantee that the processor operates correctly with other devices. (O/D) = Open Drain, (A/D) = Active Drive.

*Switching Characteristics* specify how the processor changes its signals. You have no control over this timing—circuitry external to the processor must be designed for compatibility with these signal characteristics. Switching characteristics tell you what the processor will do in a given circumstance. You can also use switching characteristics to ensure that any timing requirement of a device connected to the processor (such as memory) is satisfied.

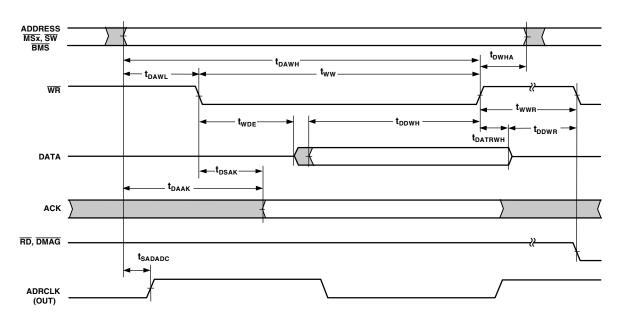

#### Memory Write—Bus Master

Use these specifications for asynchronous interfacing to memories (and memory-mapped peripherals) without reference to CLKIN. These specifications apply when the ADSP-2106x is the

#### Table 15. Memory Write-Bus Master

bus master accessing external memory space in asynchronous access mode. Note that timing for ACK, DATA,  $\overline{\text{RD}}$ ,  $\overline{\text{WR}}$ , and  $\overline{\text{DMAGx}}$  strobe timing parameters only applies to asynchronous access mode.

|                     |                                                        | 5                | 5 V and 3.3 V  |      |

|---------------------|--------------------------------------------------------|------------------|----------------|------|

| Parameter           |                                                        | Min              | Max            | Unit |

| Timing Req          | uirements                                              |                  |                |      |

| t <sub>DAAK</sub>   | ACK Delay from Address, Selects <sup>1, 2</sup>        |                  | 14 + 7DT/8 + W | ns   |

| t <sub>DSAK</sub>   | ACK Delay from WR Low <sup>1</sup>                     |                  | 8 + DT/2 + W   | ns   |

| Switching C         | <i>Characteristics</i>                                 |                  |                |      |

| t <sub>DAWH</sub>   | Address Selects to WR Deasserted <sup>2</sup>          | 17 + 15DT/16 + W |                | ns   |

| t <sub>DAWL</sub>   | Address Selects to WR Low <sup>2</sup>                 | 3 + 3DT/8        |                | ns   |

| t <sub>WW</sub>     | WR Pulse Width                                         | 12 + 9DT/16 + W  |                | ns   |

| t <sub>DDWH</sub>   | Data Setup Before WR High                              | 7 + DT/2 + W     |                | ns   |

| t <sub>DWHA</sub>   | Address Hold After WR Deasserted                       | 0.5 + DT/16 + H  |                | ns   |

| t <sub>DATRWH</sub> | Data Disable After WR Deasserted <sup>3</sup>          | 1 + DT/16 + H    | 6+DT/16+H      | ns   |

| t <sub>WWR</sub>    | WR High to WR, RD, DMAGx Low                           | 8 + 7DT/16 + H   |                | ns   |

| t <sub>DDWR</sub>   | Data Disable Before WR or RD Low                       | 5 + 3DT/8 + I    |                | ns   |

| t <sub>WDE</sub>    | WR Low to Data Enabled                                 | -1 + DT/16       |                | ns   |

| t <sub>SADADC</sub> | Address, Selects Setup Before ADRCLK High <sup>2</sup> | 0 + DT/4         |                | ns   |

W = (number of wait states specified in WAIT register)  $\times$  t<sub>CK</sub>.

$H = t_{CK}$  (if an address hold cycle occurs, as specified in WAIT register; otherwise H = 0).

$HI = t_{CK}$  (if an address hold cycle or bus idle cycle occurs, as specified in WAIT register; otherwise HI = 0).

$I = t_{CK}$  (if a bus idle cycle occurs, as specified in WAIT register; otherwise I = 0).

<sup>1</sup>ACK is not sampled on external memory accesses that use the internal wait state mode. For the first CLKIN cycle of a new external memory access, ACK must be valid by t<sub>DAAK</sub> or t<sub>DSAK</sub> or t<sub>DSAK</sub> or synchronous specification t<sub>SACKC</sub> for wait state modes external, either, or both (both, if the internal wait state is zero). For the second and subsequent cycles of a wait stated external memory access, synchronous specifications t<sub>SACKC</sub> and t<sub>HACK</sub> must be met for wait state modes external, either, or both (both, after internal wait states have completed).

<sup>2</sup> The falling edge of  $\overline{MSx}$ ,  $\overline{SW}$ ,  $\overline{BMS}$  is referenced.

<sup>3</sup>See Example System Hold Time Calculation on Page 48 for calculation of hold times given capacitive and dc loads.

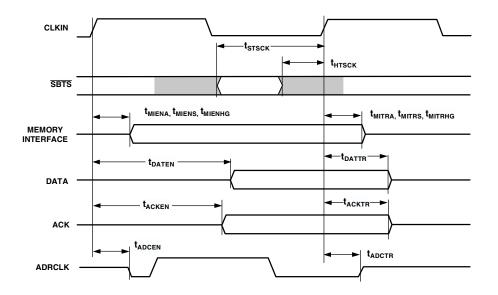

Figure 15. Memory Write—Bus Master

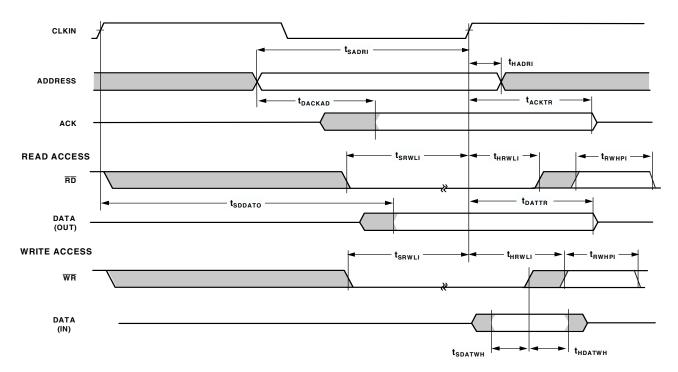

#### Synchronous Read/Write—Bus Slave

Use these specifications for bus master accesses of a slave's IOP registers or internal memory (in multiprocessor memory space). The bus master must meet the bus slave timing requirements.

#### Table 17. Synchronous Read/Write-Bus Slave

|                     |                                                    | 5            | V and 3.3 V |      |

|---------------------|----------------------------------------------------|--------------|-------------|------|

| Parameter           |                                                    | Min          | Мах         | Unit |

| Timing Requir       | rements                                            |              |             |      |

| t <sub>SADRI</sub>  | Address, SW Setup Before CLKIN                     | 15 + DT/2    |             | ns   |

| t <sub>HADRI</sub>  | Address, SW Hold After CLKIN                       |              | 5 + DT/2    | ns   |

| t <sub>SRWLI</sub>  | RD/WR Low Setup Before CLKIN <sup>1</sup>          | 9.5 + 5DT/16 |             | ns   |

| t <sub>HRWLI</sub>  | RD/WR Low Hold After CLKIN <sup>2</sup>            | -4 - 5DT/16  | 8 + 7DT/16  | ns   |

| t <sub>RWHPI</sub>  | RD/WR Pulse High                                   | 3            |             | ns   |

| t <sub>SDATWH</sub> | Data Setup Before WR High                          | 5            |             | ns   |

| t <sub>HDATWH</sub> | Data Hold After WR High                            | 1            |             | ns   |

| Switching Cha       | aracteristics                                      |              |             |      |

| t <sub>SDDATO</sub> | Data Delay After CLKIN <sup>3</sup>                |              | 18 + 5DT/16 | ns   |

| t <sub>DATTR</sub>  | Data Disable After CLKIN <sup>4</sup>              | 0 – DT/8     | 7 – DT/8    | ns   |

| t <sub>DACKAD</sub> | ACK Delay After Address, <del>SW<sup>5</sup></del> |              | 9           | ns   |

| t <sub>ACKTR</sub>  | ACK Disable After CLKIN <sup>5</sup>               | -1 - DT/8    | 6 – DT/8    | ns   |

<sup>1</sup>t<sub>SRWL1</sub> (min) = 9.5 + 5DT/16 when Multiprocessor Memory Space Wait State (MMSWS bit in WAIT register) is disabled; when MMSWS is enabled, t<sub>SRWL1</sub> (min) = 4 + DT/8. <sup>2</sup> For ADSP-21060C specification is -3.5 - 5DT/16 ns min, 8 + 7DT/16 ns max; for ADSP-21060LC specification is -3.75 - 5DT/16 ns min, 8 + 7DT/16 ns max. <sup>3</sup> For ADSP-21062L/ADSP-21062L/ADSP-21060C specification is 19 + 5DT/16 ns max; for ADSP-21060LC specification is 19.25 + 5DT/16 ns max.

<sup>4</sup>See Example System Hold Time Calculation on Page 48 for calculation of hold times given capacitive and dc loads.

<sup>5</sup> t<sub>DACKAD</sub> is true only if the address and  $\overline{SW}$  inputs have setup times (before CLKIN) greater than 10 + DT/8 and less than 19 + 3DT/4. If the address and inputs have setup times greater than 19 + 3DT/4, then ACK is valid 14 + DT/4 (max) after CLKIN. A slave that sees an address with an M field match will respond with ACK regardless of the state of MMSWS or strobes. A slave will three-state ACK every cycle with t<sub>ACKTR</sub>.

Figure 17. Synchronous Read/Write—Bus Slave

#### Asynchronous Read/Write—Host to ADSP-2106x

Use these specifications for asynchronous host processor accesses of an ADSP-2106x, after the host has asserted  $\overline{CS}$  and  $\overline{HBR}$  (low). After  $\overline{HBG}$  is returned by the ADSP-2106x, the host can drive the  $\overline{RD}$  and  $\overline{WR}$  pins to access the ADSP-2106x's internal memory or IOP registers.  $\overline{HBR}$  and  $\overline{HBG}$  are assumed low for this timing. Not required if and address are valid t<sub>HBGRCSV</sub> after goes low. For first access after asserted, ADDR31–0 must be a non-MMS value 1/2  $t_{CLK}$  before or goes low or by  $t_{HBGRCSV}$ after goes low. This is easily accomplished by driving an upper address signal high when is asserted. See the "Host Processor Control of the ADSP-2106x" section in the ADSP-2106x SHARC User's Manual, Revision 2.1.

#### Table 19. Read Cycle

|                      |                                                                             |             | 5 V and 3.3 V |      |

|----------------------|-----------------------------------------------------------------------------|-------------|---------------|------|

| Parameter            |                                                                             | Min         | Max           | Unit |

| Timing Require       | ements                                                                      |             |               |      |

| t <sub>SADRDL</sub>  | Address Setup/CS Low Before RD Low <sup>1</sup>                             | 0           |               | ns   |

| t <sub>HADRDH</sub>  | Address Hold/CS Hold Low After RD                                           | 0           |               | ns   |

| t <sub>WRWH</sub>    | RD/WR High Width                                                            | 6           |               | ns   |

| t <sub>DRDHRDY</sub> | RD High Delay After REDY (O/D) Disable                                      | 0           |               | ns   |

| t <sub>DRDHRDY</sub> | RD High Delay After REDY (A/D) Disable                                      | 0           |               | ns   |

| Switching Cha        | aracteristics                                                               |             |               |      |

| t <sub>SDATRDY</sub> | Data Valid Before REDY Disable from Low                                     | 2           |               | ns   |

| t <sub>DRDYRDL</sub> | REDY (O/D) or (A/D) Low Delay After $\overline{\text{RD}}$ Low <sup>2</sup> |             | 10            | ns   |

| t <sub>RDYPRD</sub>  | REDY (O/D) or (A/D) Low Pulse Width for Read                                | 45 + 21DT/1 | 6             | ns   |

| t <sub>HDARWH</sub>  | Data Disable After RD High <sup>3</sup>                                     | 2           | 8             | ns   |

<sup>1</sup>Not required if RD and address are valid t<sub>HBGRCSV</sub> after HBG goes low. For first access after HBR asserted, ADDR31-0 must be a non-MMS value 1/2 t<sub>CLK</sub> before RD or WR goes low or by t<sub>HBGRCSV</sub> after HBG goes low. This is easily accomplished by driving an upper address signal high when HBG is asserted. See the "Host Processor Control of the ADSP-2106x" section in the ADSP-2106x SHARC User's Manual, Revision 2.1.

<sup>2</sup>For ADSP-21060L, specification is 10.5 ns max; for ADSP-21060LC, specification is 12.5 ns max.

<sup>3</sup>For ADSP-21060L/ADSP-21060LC, specification is 2 ns min, 8.5 ns max.

#### Table 20. Write Cycle

|                      |                                                 | 5 V -       | and 3.3 V  |      |

|----------------------|-------------------------------------------------|-------------|------------|------|

| Parameter            |                                                 | Min         | Мах        | Unit |

| Timing Require       | ements                                          |             |            |      |

| t <sub>SCSWRL</sub>  | CS Low Setup Before WR Low                      | 0           |            | ns   |

| t <sub>HCSWRH</sub>  | CS Low Hold After WR High                       | 0           |            | ns   |

| t <sub>SADWRH</sub>  | Address Setup Before WR High                    | 5           |            | ns   |

| t <sub>HADWRH</sub>  | Address Hold After WR High                      | 2           |            | ns   |

| t <sub>WWRL</sub>    | WR Low Width                                    | 7           |            | ns   |

| t <sub>WRWH</sub>    | RD/WR High Width                                | 6           |            | ns   |

| t <sub>DWRHRDY</sub> | WR High Delay After REDY (O/D) or (A/D) Disable | 0           |            | ns   |

| t <sub>SDATWH</sub>  | Data Setup Before WR High                       | 5           |            | ns   |

| t <sub>HDATWH</sub>  | Data Hold After WR High                         | 1           |            | ns   |

| Switching Cha        | racteristics                                    |             |            |      |

| t <sub>DRDYWRL</sub> | REDY (O/D) or (A/D) Low Delay After WR/CS Low   |             | 10         | ns   |

| t <sub>RDYPWR</sub>  | REDY (O/D) or (A/D) Low Pulse Width for Write   | 15 + 7DT/16 |            | ns   |

| t <sub>SRDYCK</sub>  | REDY (O/D) or (A/D) Disable to CLKIN            | 1 + 7DT/16  | 8 + 7DT/16 | ns   |

Figure 22. Three-State Timing (Bus Transition Cycle, SBTS Assertion)

|                   |                                               | 5 V |     |     | 3.3 V |      |

|-------------------|-----------------------------------------------|-----|-----|-----|-------|------|

| Parameter         |                                               | Min | Max | Min | Max   | Unit |

| Timing Requi      | irements                                      |     |     |     |       |      |

| t <sub>SLCK</sub> | LACK/LCLK Setup Before CLKIN Low <sup>1</sup> | 10  |     | 10  |       | ns   |

| t <sub>HLCK</sub> | LACK/LCLK Hold After CLKIN Low <sup>1</sup>   | 2   |     | 2   |       | ns   |

#### Table 25. Link Port Service Request Interrupts: 1× and 2× Speed Operations

<sup>1</sup>Only required for interrupt recognition in the current cycle.

#### Link Ports $-2 \times CLK$ Speed Operation

Calculation of link receiver data setup and hold relative to link clock is required to determine the maximum allowable skew that can be introduced in the transmission path between LDATA and LCLK. Setup skew is the maximum delay that can be introduced in LDATA relative to LCLK:

Setup Skew =  $t_{LCLKTWH} \min - t_{DLDCH} - t_{SLDCL}$

Hold skew is the maximum delay that can be introduced in LCLK relative to LDATA:

*Hold Skew* =  $t_{LCLKTWL}$  min –  $t_{HLDCH}$  –  $t_{HLDCL}$

Calculations made directly from 2 speed specifications will result in unrealistically small skew times because they include multiple tester guardbands.

Note that link port transfers at 2× CLK speed at 40 MHz ( $t_{CK} = 25$  ns) may fail. However, 2× CLK speed link port transfers at 33 MHz ( $t_{CK} = 30$  ns) work as specified.

#### Table 26. Link Ports-Receive

|                      |                                               |                    | 3.3 V       |                    |             |      |

|----------------------|-----------------------------------------------|--------------------|-------------|--------------------|-------------|------|

| Parameter            |                                               | Min                | Min Max     |                    | Max         | Unit |

| Timing Req           | uirements                                     |                    |             |                    |             |      |

| t <sub>SLDCL</sub>   | Data Setup Before LCLK Low                    | 2.5                |             | 2.25               |             | ns   |

| t <sub>HLDCL</sub>   | Data Hold After LCLK Low                      | 2.25               |             | 2.25               |             | ns   |

| t <sub>LCLKIW</sub>  | LCLK Period (2× Operation)                    | t <sub>CK</sub> /2 |             | t <sub>CK</sub> /2 |             | ns   |

| t <sub>LCLKRWL</sub> | LCLK Width Low <sup>1</sup>                   | 4.5                |             | 5.25               |             | ns   |

| t <sub>LCLKRWH</sub> | LCLK Width High <sup>2</sup>                  | 4.25               |             | 4                  |             | ns   |

| Switching (          | Characteristics                               |                    |             |                    |             |      |

| t <sub>DLAHC</sub>   | LACK High Delay After CLKIN High <sup>3</sup> | 18 + DT/2          | 28.5 + DT/2 | 18 + DT/2          | 29.5 + DT/2 | ns   |

| t <sub>DLALC</sub>   | LACK Low Delay After LCLK High <sup>4</sup>   | 6                  | 16          | 6                  | 16          | ns   |

<sup>1</sup>For ADSP-21060L, specification is 5 ns min.

<sup>2</sup> For ADSP-21062, specification is 4 ns min, for ADSP-21060LC, specification is 4.5 ns min.

<sup>3</sup>LACK goes low with t<sub>DLALC</sub> relative to rise of LCLK after first nibble, but does not go low if the receiver's link buffer is not about to fill.

<sup>4</sup> For ADSP-21060L, specification is 6 ns min, 18 ns max. For ADSP-21060C, specification is 6 ns min, 16.5 ns max. For ADSP-21060LC, specification is 6 ns min, 18.5 ns max.

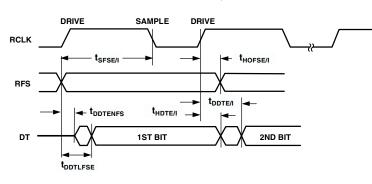

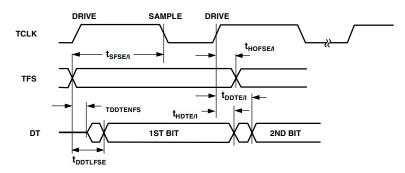

EXTERNAL RFS WITH MCE = 1, MFD = 0

LATE EXTERNAL TFS

Figure 26. Serial Ports—External Late Frame Sync

## 240-LEAD MQFP\_PQ4/CQFP PIN CONFIGURATION

| Din Nama        | Din No. | Din Norma       | Din No. | Din Norra       | Din Ma  | Din Norra       | Din No. | Din Name        | Din Na  | Din Norro       | Dim No         |

|-----------------|---------|-----------------|---------|-----------------|---------|-----------------|---------|-----------------|---------|-----------------|----------------|

| Pin Name        | Pin No. | Pin Name        | <b>Pin No.</b> |

| TDI             | 1       | ADDR20          | 41      | TCLK0           | 81      | DATA41          | 121     | DATA14          | 161     | L2DAT0          | 201            |

| TRST            | 2       | ADDR21          | 42      | TFS0            | 82      | DATA40          | 122     | DATA13          | 162     | L2CLK           | 202            |

| V <sub>DD</sub> | 3       | GND             | 43      | DR0             | 83      | DATA39          | 123     | DATA12          | 163     | L2ACK           | 203            |

| TDO             | 4       | ADDR22          | 44      | RCLK0           | 84      | V <sub>DD</sub> | 124     | GND             | 164     | NC              | 204            |

| TIMEXP          | 5       | ADDR23          | 45      | RFS0            | 85      | DATA38          | 125     | DATA11          | 165     | V <sub>DD</sub> | 205            |

| EMU             | 6       | ADDR24          | 46      | V <sub>DD</sub> | 86      | DATA37          | 126     | DATA10          | 166     | L3DAT3          | 206            |

| ICSA            | 7       | V <sub>DD</sub> | 47      | V <sub>DD</sub> | 87      | DATA36          | 127     | DATA9           | 167     | L3DAT2          | 207            |

| FLAG3           | 8       | GND             | 48      | GND             | 88      | GND             | 128     | V <sub>DD</sub> | 168     | L3DAT1          | 208            |

| FLAG2           | 9       | V <sub>DD</sub> | 49      | ADRCLK          | 89      | NC              | 129     | DATA8           | 169     | L3DAT0          | 209            |

| FLAG1           | 10      | ADDR25          | 50      | REDY            | 90      | DATA35          | 130     | DATA7           | 170     | L3CLK           | 210            |

| FLAG0           | 11      | ADDR26          | 51      | HBG             | 91      | DATA34          | 131     | DATA6           | 171     | L3ACK           | 211            |

| GND             | 12      | ADDR27          | 52      |                 | 92      | DATA33          | 132     | GND             | 172     | GND             | 212            |

| ADDRO           | 13      | GND             | 53      | RD              | 93      | V <sub>DD</sub> | 133     | DATA5           | 173     | L4DAT3          | 213            |

| ADDR1           | 14      | MS3             | 54      | WR              | 94      | V <sub>DD</sub> | 134     | DATA4           | 174     | L4DAT2          | 214            |

| V <sub>DD</sub> | 15      | MS2             | 55      | GND             | 95      | GND             | 135     | DATA3           | 175     | L4DAT1          | 215            |

| ADDR2           | 16      | MS1             | 56      | V <sub>DD</sub> | 96      | DATA32          | 136     | V <sub>DD</sub> | 176     | L4DAT0          | 216            |

| ADDR3           | 17      | MS0             | 57      | GND             | 97      | DATA31          | 137     | DATA2           | 177     | L4CLK           | 217            |

| ADDR4           | 18      | SW              | 58      | CLKIN           | 98      | DATA30          | 138     | DATA1           | 178     | L4ACK           | 218            |

| GND             | 19      | BMS             | 59      | ACK             | 99      | GND             | 139     | DATA0           | 179     | V <sub>DD</sub> | 219            |

| ADDR5           | 20      | ADDR28          | 60      | DMAG2           | 100     | DATA29          | 140     | GND             | 180     | GND             | 220            |

| ADDR6           | 21      | GND             | 61      | DMAG1           | 101     | DATA28          | 141     | GND             | 181     | V <sub>DD</sub> | 221            |

| ADDR7           | 22      | V <sub>DD</sub> | 62      | PAGE            | 102     | DATA27          | 142     | L0DAT3          | 182     | L5DAT3          | 222            |

| V <sub>DD</sub> | 23      | V <sub>DD</sub> | 63      | V <sub>DD</sub> | 103     | V <sub>DD</sub> | 143     | L0DAT2          | 183     | L5DAT2          | 223            |

| ADDR8           | 24      | ADDR29          | 64      | BR6             | 104     | V <sub>DD</sub> | 144     | L0DAT1          | 184     | L5DAT1          | 224            |

| ADDR9           | 25      | ADDR30          | 65      | BR5             | 105     | DATA26          | 145     | L0DAT0          | 185     | L5DAT0          | 225            |

| ADDR10          | 26      | ADDR31          | 66      | BR4             | 106     | DATA25          | 146     | LOCLK           | 186     | L5CLK           | 226            |

| GND             | 27      | GND             | 67      | BR3             | 107     | DATA24          | 147     | LOACK           | 187     | L5ACK           | 227            |

| ADDR11          | 28      | SBTS            | 68      | BR2             | 108     | GND             | 148     | V <sub>DD</sub> | 188     | GND             | 228            |

| ADDR12          | 29      | DMAR2           | 69      | BR1             | 109     | DATA23          | 149     | L1DAT3          | 189     | ID2             | 229            |

| ADDR13          | 30      | DMAR1           | 70      | GND             | 110     | DATA22          | 150     | L1DAT2          | 190     | ID1             | 230            |

| V <sub>DD</sub> | 31      | HBR             | 71      | V <sub>DD</sub> | 111     | DATA21          | 151     | L1DAT1          | 191     | ID0             | 231            |

| ADDR14          | 32      | DT1             | 72      | GND             | 112     | V <sub>DD</sub> | 152     | L1DAT0          | 192     | LBOOT           | 232            |

| ADDR15          | 33      | TCLK1           | 73      | DATA47          | 113     | DATA20          | 153     | L1CLK           | 193     | RPBA            | 233            |

| GND             | 34      | TFS1            | 74      | DATA46          | 114     | DATA19          | 154     | L1ACK           | 194     | RESET           | 234            |

| ADDR16          | 35      | DR1             | 75      | DATA45          | 115     | DATA18          | 155     | GND             | 195     | EBOOT           | 235            |

| ADDR17          | 36      | RCLK1           | 76      | V <sub>DD</sub> | 116     | GND             | 156     | GND             | 196     | IRQ2            | 236            |

| ADDR18          | 37      | RFS1            | 77      | DATA44          | 117     | DATA17          | 157     | V <sub>DD</sub> | 197     | IRQ1            | 237            |

| V <sub>DD</sub> | 38      | GND             | 78      | DATA43          | 118     | DATA16          | 158     | L2DAT3          | 198     | IRQ0            | 238            |

| V <sub>DD</sub> | 39      | CPA             | 79      | DATA42          | 119     | DATA15          | 159     | L2DAT2          | 199     | ТСК             | 239            |

| ADDR19          | 40      | DT0             | 80      | GND             | 120     | V <sub>DD</sub> | 160     | L2DAT1          | 200     | TMS             | 240            |

Table 41. ADSP-2106x MQFP\_PQ4 and ADSP-21060CZ CQFP Pin Assignments (SP-240-2, QS-240-2A, QS-240-2B)

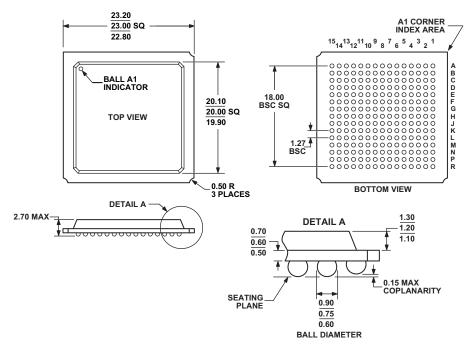

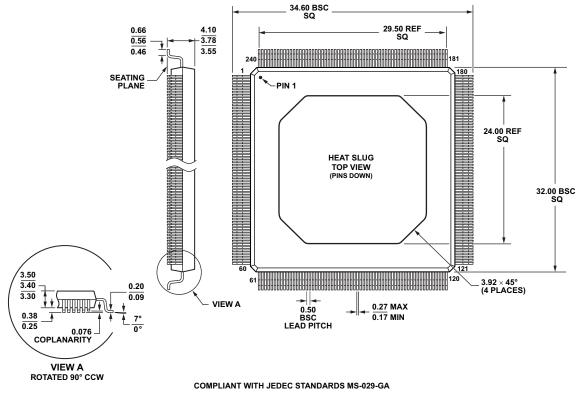

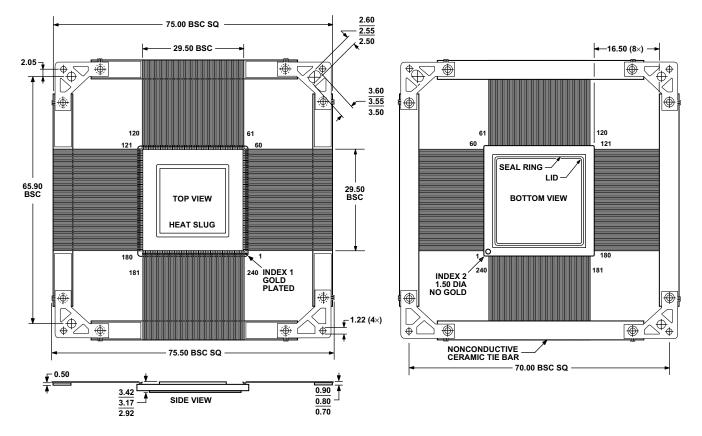

## **OUTLINE DIMENSIONS**

COMPLIANT TO JEDEC STANDARDS MS-034-AAJ-2

Figure 40. 225-Ball Plastic Ball Grid Array [PBGA] (B-225-2) Dimensions shown in millimeters

Figure 41. 240-Lead Metric Quad Flat Package, Thermally Enhanced "PowerQuad" [MQFP\_PQ4] (SP-240-2) Dimensions shown in millimeters

Figure 43. 240-Lead Ceramic Quad Flat Package, Mounted with Cavity Down [CQFP] (QS-240-2B) Dimensions shown in millimeters

## **ORDERING GUIDE**

| Model                                   | Notes | Temperature<br>Range                | Instruction<br>Rate<br>33 MHz | On-Chip<br>SRAM<br>4M Bit | Operating<br>Voltage | Package Description                    | Package<br>Option      |

|-----------------------------------------|-------|-------------------------------------|-------------------------------|---------------------------|----------------------|----------------------------------------|------------------------|

| ASDP-21060CZ-133                        | 1, 2  | -40°C to +100°C                     |                               |                           | 5 V                  | 240-Lead CQFP [Heat Slug Up]           | QS-240-2A              |

| ASDP-21060CZ-155                        | 1, 2  | $-40^{\circ}$ C to $+100^{\circ}$ C | 40 MHz                        | 4M Bit                    | 5 V                  | 240-Lead CQFP [Heat Slug Up]           | QS-240-2A<br>QS-240-2A |

| ASDP-21060CW-133                        | 1, 2  | $-40^{\circ}$ C to $+100^{\circ}$ C | 33 MHz                        | 4M Bit                    | 5 V                  | 240-Lead CQFP [Heat Slug Down]         | QS-240-2A<br>QS-240-1A |

| ASDP-21060CW-160                        | 1, 2  | $-40^{\circ}$ C to $+100^{\circ}$ C | 40 MHz                        | 4M Bit                    | 5 V                  | 240-Lead CQFP [Heat Slug Down]         | QS-240-1A              |

| ADSP-21060KS-133                        |       | -40 C to +100 C                     | 33 MHz                        | 4M Bit                    | 5 V                  | 240-Lead MQFP PQ4                      | SP-240-1A              |

| ADSP-21060KSZ-133                       | 2     | 0°C to 85°C                         | 33 MHz                        | 4M Bit                    | 5 V                  | 240-Lead MQFP_PQ4                      | SP-240-2               |

| ADSP-21060KS-160                        |       | 0°C to 85°C                         | 40 MHz                        | 4M Bit                    | 5 V                  | 240-Lead MQFP_PQ4<br>240-Lead MQFP_PQ4 | SP-240-2               |

| ADSP-21060KSZ-160                       | 2     | 0°C to 85°C                         | 40 MHz                        | 4M Bit                    | 5 V                  | 240-Lead MQFP_PQ4<br>240-Lead MQFP_PQ4 | SP-240-2               |

| ADSP-21060KB-160                        |       | 0°C to 85°C                         | 40 MHz                        | 4M Bit                    | 5 V                  | 225-Ball PBGA                          | B-225-2                |

| ADSP-21060KBZ-160                       | 2     | 0°C to 85°C                         | 40 MHz                        | 4M Bit                    | 5 V<br>5 V           | 225-Ball PBGA                          | В-225-2<br>В-225-2     |

| ADSP-21060KBZ-160<br>ADSP-21060LKSZ-133 | 2     | 0°C to 85°C                         | 40 MHz                        | 4M Bit                    | 3.3 V                | 240-Lead MQFP PQ4                      | Б-223-2<br>SP-240-2    |

| ADSP-21060LKS2-155<br>ADSP-21060LKS-160 |       | 0°C to 85°C                         | 40 MHz                        | 4M Bit                    | 3.3 V<br>3.3 V       | 240-Lead MQFP_PQ4<br>240-Lead MQFP_PQ4 | SP-240-2<br>SP-240-2   |

| ADSP-21060LKSZ-160                      | 2     | 0°C to 85°C                         | 40 MHz                        | 4M Bit                    | 3.3 V<br>3.3 V       |                                        | SP-240-2<br>SP-240-2   |

| ADSP-21060LKS2-160<br>ADSP-21060LKB-160 |       | 0°C to 85°C                         | 40 MHz                        | 4M Bit                    | 3.3 V<br>3.3 V       | 240-Lead MQFP_PQ4<br>225-Ball PBGA     | B-225-2                |

| ADSP-21060LAB-160                       |       | -40°C to +85°C                      | 40 MHz                        | 4M Bit                    | 3.3 V<br>3.3 V       | 225-Ball PBGA                          | В-225-2<br>В-225-2     |

|                                         | 2     |                                     | 40 MHz                        |                           | 3.3 V<br>3.3 V       |                                        |                        |

| ADSP-21060LABZ-160<br>ADSP-21060LCB-133 |       | -40°C to +85°C<br>-40°C to +100°C   | 40 MHZ<br>33 MHz              | 4M Bit<br>4M Bit          | 3.3 V<br>3.3 V       | 225-Ball PBGA<br>225-Ball PBGA         | B-225-2<br>B-225-2     |

| ADSP-21060LCB-133<br>ADSP-21060LCBZ-133 | 2     | $-40^{\circ}$ C to $+100^{\circ}$ C | 33 MHz                        | 4M Bit                    | 3.3 V<br>3.3 V       | 225-Ball PBGA                          | в-225-2<br>В-225-2     |

|                                         | 1, 2  |                                     |                               |                           |                      |                                        |                        |

| ASDP-21060LCW-160                       | .,_   | $-40^{\circ}$ C to $+100^{\circ}$ C | 40 MHz                        | 4M Bit                    | 3.3 V<br>5 V         | 240-Lead CQFP [Heat Slug Down]         | QS-240-1A              |

| ADSP-21062KS-133                        | 2     | 0°C to 85°C                         | 33 MHz                        | 2M Bit                    |                      | 240-Lead MQFP_PQ4                      | SP-240-2               |

| ADSP-21062KSZ-133                       | -     | 0°C to 85°C                         | 33 MHz                        | 2M Bit                    | 5 V                  | 240-Lead MQFP_PQ4                      | SP-240-2               |

| ADSP-21062KS-160                        | 2     | 0°C to 85°C                         | 40 MHz                        | 2M Bit                    | 5 V                  | 240-Lead MQFP_PQ4                      | SP-240-2               |

| ADSP-21062KSZ-160                       | 2     | 0°C to 85°C                         | 40 MHz                        | 2M Bit                    | 5 V                  | 240-Lead MQFP_PQ4                      | SP-240-2               |

| ADSP-21062KB-160                        | 2     | 0°C to 85°C                         | 40 MHz                        | 2M Bit                    | 5 V                  | 225-Ball PBGA                          | B-225-2                |

| ADSP-21062KBZ-160                       | 2     | 0°C to 85°C                         | 40 MHz                        | 2M Bit                    | 5 V                  | 225-Ball PBGA                          | B-225-2                |

| ADSP-21062CS-160                        | 2     | -40°C to +100°C                     | 40 MHz                        | 2M Bit                    | 5 V                  | 240-Lead MQFP_PQ4                      | SP-240-2               |

| ADSP-21062CSZ-160                       | 2     | -40°C to +100°C                     | 40 MHz                        | 2M Bit                    | 5 V                  | 240-Lead MQFP_PQ4                      | SP-240-2               |

| ADSP-21062LKSZ-133                      | 2     | 0°C to 85°C                         | 33 MHz                        | 2M Bit                    | 3.3 V                | 240-Lead MQFP_PQ4                      | SP-240-2               |

| ADSP-21062LKS-160                       | 2     | 0°C to 85°C                         | 40 MHz                        | 2M Bit                    | 3.3 V                | 240-Lead MQFP_PQ4                      | SP-240-2               |

| ADSP-21062LKSZ-160                      | 2     | 0°C to 85°C                         | 40 MHz                        | 2M Bit                    | 3.3 V                | 240-Lead MQFP_PQ4                      | SP-240-2               |

| ADSP-21062LKB-160                       |       | 0°C to 85°C                         | 40 MHz                        | 2M Bit                    | 3.3 V                | 225-Ball PBGA                          | B-225-2                |

| ADSP-21062LKBZ-160                      | 2     | 0°C to 85°C                         | 40 MHz                        | 2M Bit                    | 3.3 V                | 225-Ball PBGA                          | B-225-2                |

| ADSP-21062LAB-160                       |       | –40°C to 85°C                       | 40 MHz                        | 2M Bit                    | 3.3 V                | 225-Ball PBGA                          | B-225-2                |

| ADSP-21062LABZ-160                      | 2     | –40°C to 85°C                       | 40 MHz                        | 2M Bit                    | 3.3 V                | 225-Ball PBGA                          | B-225-2                |

| ADSP-21062LCS-160                       |       | -40°C to +100°C                     | 40 MHz                        | 2M Bit                    | 3.3 V                | 240-Lead MQFP_PQ4                      | SP-240-2               |

| ADSP-21062LCSZ-160                      | 2     | -40°C to +100°C                     | 40 MHz                        | 2M Bit                    | 3.3 V                | 240-Lead MQFP_PQ4                      | SP-240-2               |

<sup>1</sup>Model refers to package with formed leads. For model numbers of unformed lead versions (QS-240-1B, QS-240-2B), contact Analog Devices or an Analog Devices sales representative.

<sup>2</sup>RoHS compliant part.