#### Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                                |

|----------------------------|-----------------------------------------------------------------------|

| Core Processor             | 56800E                                                                |

| Core Size                  | 16-Bit                                                                |

| Speed                      | 32MHz                                                                 |

| Connectivity               | I <sup>2</sup> C, SCI, SPI                                            |

| Peripherals                | POR, PWM, WDT                                                         |

| Number of I/O              | 26                                                                    |

| Program Memory Size        | 16KB (8K × 16)                                                        |

| Program Memory Type        | FLASH                                                                 |

| EEPROM Size                | -                                                                     |

| RAM Size                   | 2K x 16                                                               |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 3.6V                                                             |

| Data Converters            | A/D 6x12b                                                             |

| Oscillator Type            | Internal                                                              |

| Operating Temperature      | -40°C ~ 105°C (TA)                                                    |

| Mounting Type              | Surface Mount                                                         |

| Package / Case             | 32-LQFP                                                               |

| Supplier Device Package    | 32-LQFP (7x7)                                                         |

| Purchase URL               | https://www.e-xfl.com/product-detail/nxp-semiconductors/mc56f8013vfae |

|                            |                                                                       |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

## **Document Revision History**

| Version History | Description of Change                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

|-----------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Rev. 0          | Initial release.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| Rev. 1          | Updates to Part 10, Specifications,<br>Table 10-1, added maximum clamp current, per pin<br>Table 10-12, clarified variation over temperature table and graph<br>Table 10-16, added LIN slave timing                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| Rev. 2          | Added alternate pins to Figure 11-1 and Table 11-1.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| Rev. 3          | Corrected ADC offering on page 3, clarified Section 1.4.1, corrected bit selects in Timer Channel 3 Input (TC3_INP) bit 9, Section 6.3.1.7, and simplified notes in Table 10-9.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| Rev. 4          | Added clarification on sync inputs in <b>Section 1.4.1</b> , added voltage difference specification to <b>Table 10-1</b> and <b>Table 10-4</b> , deleted formula for Ambient Operating Temperature in <b>Table 10-4</b> , also a note for pin group 3 to <b>Table 10-1</b> , corrected <b>Table 8-1</b> , error in Port C peripheral function configuration, removed text from notes in <b>Table 10-9</b> that referred to multiple flash blocks - this family has one flash block. Added RoHs and "pb-free" language to back cover.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| Rev. 5          | Updates to Section 10<br>Table 10-5, corrected max values for ADC Input Current High and Low; corrected typ value<br>for pull-up disabled Digital Input Current Low (a)<br>Table 10-6, corrected typ and added max values for Standby > Stop and Powerdown modes<br>Table 10-7, corrected min value for Low-Voltage Interrupt for 3.3V<br>Table 10-11, corrected typ and max values and units for PLL lock time<br>Table 10-12, corrected typ values for Relaxation Oscillator output frequency and variation<br>over temperature (also increased temp range to 150 degreesC) and added variation over<br>temperature from 0—105 degreesC<br>Updated Figure 10-5<br>Table 10-19, updated max values for Integral Non-Linearity full input signal range, Negative<br>Differential Non-Linearity, ADC internal clock, Offset Voltage Internal Ref, Gain Error and<br>Offset Voltage External Ref; updated typ values for Negative Differential Non-Linearity, Offset<br>Voltage Internal Ref, Gain Error and Offset Voltage External Ref; added new min values and<br>corrected typ values for Signal-to-noise ratio, Total Harmonic Distortion, Spurious Free<br>Dynamic Range, Signal-to-noise plus distortion, Effective Number of Bits |

| Rev. 6          | Added details to Section 1. Clarified language in State During Reset column in <b>Table 2-3</b> ; corrected flash data retention temperature in <b>Table 10-4</b> ; moved input current high/low to <b>Table 10-19</b> and location of footnotes in <b>Table 10-5</b> ; reorganized <b>Table 10-19</b> ; clarified title of <b>Figure 10-1</b> .                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| Rev. 7          | Added information on automotive device for 56F8013.<br>Added information on 56F8011device; edited to indicate differences in 56F8013 and 56F8011 devices.<br>Updated values for $V_{EI3.3}$ and $V_{EI2.5}$ in Table 10-7.<br>Deleted values for input and output voltage in Table 10-8.<br>Added row for MC56F8013MFAE in Table 10-12.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

# Part 1 Overview

# 1.1 56F8013/56F8011 Features

### 1.1.1 Digital Signal Controller Core

- Efficient 16-bit 56800E family Digital Signal Controller (DSC) engine with dual Harvard architecture

- As many as 32 Million Instructions Per Second (MIPS) at 32MHz core frequency

- Single-cycle 16 × 16-bit parallel Multiplier-Accumulator (MAC)

- Four 36-bit accumulators, including extension bits

- 32-bit arithmetic and logic multi-bit shifter

- Parallel instruction set with unique DSP addressing modes

- Hardware DO and REP loops

- Three internal address buses

- Four internal data buses

- Instruction set supports both DSP and controller functions

- Controller-style addressing modes and instructions for compact code

- Efficient C compiler and local variable support

- Software subroutine and interrupt stack with depth limited only by memory

- JTAG/Enhanced On-Chip Emulation (OnCE) for unobtrusive, processor speed-independent, real-time debugging

### 1.1.2 Differences Between Devices

Table 1-1 outlines the key differences between the 56F8013 and 56F8011 devices.

| Feature                  | 56F8013 | 56F8011 |

|--------------------------|---------|---------|

| Program Flash            | 16KB    | 12KB    |

| Unified Data/Program RAM | 4KB     | 2KB     |

#### **Table 1-1 Device Differences**

#### 1.1.3 Memory

- Dual Harvard architecture permits as many as three simultaneous accesses to program and data memory

- Flash security and protection that prevent unauthorized users from gaining access to the internal Flash

- On-chip memory:

- 16KB of Program Flash (56F8013 device) 12KB of Program Flash (56F8011 device)

- 4KB of Unified Data/Program RAM (56F8013 device)

2KB of Unified Data/Program RAM (56F8011 device)

- EEPROM emulation capability using Flash

- Up to 26 General-Purpose I/O (GPIO) pins with 5V tolerance

- Integrated Power-On Reset and Low-Voltage Interrupt Module

- Phase Lock Loop (PLL) provides a high-speed clock to the core and peripherals

- Clock Sources:

- On-chip relaxation oscillator

- External clock source

- On-chip regulators for digital and analog circuitry to lower cost and reduce noise

- JTAG/EOnCE debug programming interface for real-time debugging

### 1.1.5 Energy Information

- Fabricated in high-density CMOS with 5V tolerance

- On-chip regulators for digital and analog circuitry to lower cost and reduce noise

- Wait and Stop modes available

- ADC smart power management

- Each peripheral can be individually disabled to save power

# 1.2 56F8013/56F8011 Description

The 56F8013/56F8011 is a member of the 56800E core-based family of Digital Signal Controllers (DSCs). It combines, on a single chip, the processing power of a DSP and the functionality of a microcontroller with a flexible set of peripherals to create an extremely cost-effective solution. Because of its low cost, configuration flexibility, and compact program code, the 56F8013/56F8011 is well-suited for many applications. The 56F8013/56F8011 includes many peripherals that are especially useful for industrial control, motion control, home appliances, general purpose inverters, smart sensors, fire and security systems, switched mode power supply, power management, and medical monitoring applications.

The 56800E core is based on a dual Harvard-style architecture consisting of three execution units operating in parallel, allowing as many as six operations per instruction cycle. The MCU-style programming model and optimized instruction set allow straightforward generation of efficient, compact DSP and control code. The instruction set is also highly efficient for C compilers to enable rapid development of optimized control applications.

The 56F8013/56F8011 supports program execution from internal memories. Two data operands can be accessed from the on-chip data RAM per instruction cycle. The 56F8013/56F8011 also offers up to 26 General Purpose Input/Output (GPIO) lines, depending on peripheral configuration.

The 56F8013 Digital Signal Controller includes 16KB of Program Flash and 4KB of Unified Data/Program RAM. *The 56F8011 Digital Signal Controller includes 12KB of Program Flash and 2KB of Unified Data/Program RAM*. Program Flash memory can be independently bulk erased or erased in pages. Program Flash page erase size is 512 Bytes (256 Words).

A full set of programmable peripherals—PWM, ADCs, SCI, SPI, I<sup>2</sup>C, Quad Timer—supports various applications. Each peripheral can be independently shut down to save power. Any pin in these peripherals can also be used as General Purpose Input/Outputs (GPIOs).

# **1.3 Award-Winning Development Environment**

Processor Expert<sup>TM</sup> (PE) provides a Rapid Application Design (RAD) tool that combines easy-to-use component-based software application creation with an expert knowledge system.

The CodeWarrior Integrated Development Environment is a sophisticated tool for code navigation, compiling, and debugging. A complete set of evaluation modules (EVMs), demonstration board kit and development system cards will support concurrent engineering. Together, PE, CodeWarrior and EVMs create a complete, scalable tools solution for easy, fast, and efficient development.

# **1.4 Architecture Block Diagram**

The 56F8013/56F8011's architecture is shown in **Figure 1-1**, **Figure 1-2**, and **Figure 1-3**. **Figure 1-1** illustrates how the 56800E system buses communicate with internal memories and the IPBus Bridge and the internal connections between each unit of the 56800E core. **Figure 1-2** shows the peripherals and control blocks connected to the IPBus Bridge. **Figure 1-3** details how the device's I/O pins are muxed. The figures do not show the on-board regulator and power and ground signals. Please see Part 2, Signal/Connection Descriptions, to see which signals are multiplexed with those of other peripherals.

# **1.5 Synchronize ADC with PWM**

ADC conversion can be synchronized with PWM module via Quad Timer channel 2 and 3 if needed. Internally, the PWM synch signal, which is generated at every PWM reload, can be connected to the timer channel 3 input and the timer channel 2 and 3 outputs are connected to ADC sync inputs. Timer channel 3 output is connected to SYNC0 and Timer channel 2 is connected to SYNC1. The setting is controlled by TC3\_INP bit in the SIM Control Register; see Section 6.3.1.

SYNC0 is the master ADC sync input is used to trigger both ADCA and ADCB in sequence and parallel mode. SYNC1 is used to trigger ADCB in parallel independent mode, while SYNC0 is used to trigger ADCA. See 56F801X Peripheral Reference Manual for additional information.

# **1.6 Multiple Frequency PWM**

When both PWM channels of a complementary pair in software control mode and software control bits are set to 1, each complementary PWM signal pair—PWM 0 and 1; PWM 2 and 3; PWM 4 and 5—can select a PWM source of one of following sources that enables each PWM pair to output different frequency PWM signal.

- External GPIO input:

- GPIOB2 input can be used to drive PWM 0 and 1

- GPIOB3 input can be used to drive PWM 2 and 3

- GPIOB4 input can be used to drive PWM 4 and 5

- Quad Timer output:

- Timer0 output can be used to drive PWM 0 and 1

### Table 2-3 56F8013/56F8011 Signal and Package Information for the 32-Pin LQFP (Continued)

| Signal<br>Name      | LQFP<br>Pin No. | Туре                          | State During<br>Reset                        | Signal Description                                                                                                                                                                                                                                                                                                                          |

|---------------------|-----------------|-------------------------------|----------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| GPIOB7              | 3               | Input/<br>Output              | Input with<br>internal<br>pull-up            | <b>Port B GPIO</b> — This GPIO pin can be individually programmed as an input or output pin.                                                                                                                                                                                                                                                |

| (TXD)               |                 | Output                        | enabled                                      | <b>Transmit Data</b> — SCI transmit data output or transmit / receive in single wire operation.                                                                                                                                                                                                                                             |

| (SCL <sup>2</sup> ) |                 | Input/<br>Output              |                                              | <b>Serial Clock</b> — This pin serves as the I <sup>2</sup> C serial clock.                                                                                                                                                                                                                                                                 |

|                     |                 |                               |                                              | After reset, the default state is GPIOB7. The alternative peripheral functionality is controlled via the SIM. See <b>Section 6.3.8</b> .                                                                                                                                                                                                    |

| 2. This signal      | is also bro     | ought out on t                | he GPIOB0 pin.                               |                                                                                                                                                                                                                                                                                                                                             |

| RESET               | 15              | Input                         | Input with<br>internal<br>pull-up<br>enabled | <b>Reset</b> — This input is a direct hardware reset on the processor.<br>When RESET is asserted low, the chip is initialized and placed in the reset state. A Schmitt trigger input is used for noise immunity. The internal reset signal will be deasserted synchronous with the internal clocks after a fixed number of internal clocks. |

| (GPIOA7)            |                 | Input/Open<br>Drain<br>Output |                                              | <b>Port A GPIO</b> — This GPIO pin can be individually programmed as<br>an input or open drain output pin. Note that RESET functionality is<br>disabled in this mode and the chip can only be reset via POR, COP<br>reset, or software reset.<br>After reset, the default state is RESET.                                                   |

|                     |                 |                               |                                              |                                                                                                                                                                                                                                                                                                                                             |

| GPIOB4              | 19              | Input/<br>Output              | Input with<br>internal<br>pull-up<br>enabled | <b>Port B GPIO</b> — This GPIO pin can be individually programmed as an input or output pin.                                                                                                                                                                                                                                                |

| (ТО)                |                 | Input/<br>Output              | enabled                                      | <b>T0</b> — Timer, Channel 0                                                                                                                                                                                                                                                                                                                |

| (CLKO)              |                 | Output                        |                                              | <b>Clock Output</b> — This is a buffered clock signal. Using the SIM_CLKO Select Register (SIM_CLKOSR), this pin can be programmed as any of the following: disabled (logic 0), CLK_MSTR (system clock), IPBus clock, or oscillator output. See Section 6.3.7. After reset, the default state is GPIOB4. The alternative peripheral         |

|                     |                 |                               |                                              | functionality is controlled via the SIM. See Section 6.3.8.                                                                                                                                                                                                                                                                                 |

Return to Table 2-2

### 5.5.16 Interrupt Control Register (ICTRL)

| \$Base + \$12 | 15  | 14 | 13 | 12 | 11 | 10 | 9   | 8 | 7 | 6 | 5    | 4 | 3 | 2 | 1 | 0 |

|---------------|-----|----|----|----|----|----|-----|---|---|---|------|---|---|---|---|---|

| Read          | INT | IP | IC |    |    |    | VAB |   |   |   | INT_ | 1 | 1 | 1 | 0 | 0 |

| Write         |     |    |    |    |    |    |     |   |   |   | DIS  |   |   |   |   |   |

| RESET         | 0   | 0  | 0  | 0  | 0  | 0  | 0   | 0 | 0 | 0 | 0    | 1 | 1 | 1 | 0 | 0 |

#### Figure 5-18 Interrupt Control Register (ICTRL)

#### 5.5.16.1 Interrupt (INT)—Bit 15

This *read-only* bit reflects the state of the interrupt to the 56800E core.

- 0 = No interrupt is being sent to the 56800E core

- 1 = An interrupt is being sent to the 56800E core

#### 5.5.16.2 Interrupt Priority Level (IPIC)—Bits 14–13

These *read-only* bits reflect the state of the new interrupt priority level bits being presented to the 56800E core. These bits indicate the priority level needed for a new IRQ to interrupt the current interrupt being sent to the 56800E core. This field is only updated when the 56800E core jumps to a new interrupt service routine.

**Note:** Nested interrupts may cause this field to be updated before the original interrupt service routine can read it.

- 00 = Required nested exception priority levels are 0, 1, 2, or 3

- 01 = Required nested exception priority levels are 1, 2, or 3

- 10 = Required nested exception priority levels are 2 or 3

- 11 = Required nested exception priority level is 3

| IPIC_VALUE[1:0] | Current Interrupt<br>Priority Level | Required Nested<br>Exception Priority |

|-----------------|-------------------------------------|---------------------------------------|

| 00              | No interrupt or SWILP               | Priorities 0, 1, 2, 3                 |

| 01              | Priority 0                          | Priorities 1, 2, 3                    |

| 10              | Priority 1                          | Priorities 2, 3                       |

| 11              | Priority 2 or 3                     | Priority 3                            |

#### **Table 5-3 Interrupt Priority Encoding**

#### 5.5.16.3 Vector Number - Vector Address Bus (VAB)—Bits 12–6

This *read-only* field shows the vector number (VAB[6:0]) used at the time the last IRQ was taken. In the case of a Fast Interrupt, it shows the lower address bits of the jump address. This field is only updated when the 56800E core jumps to a new interrupt service routine.

# 6.3 Register Descriptions

| Address Offset | Address Acronym | Register Name                            | Section Location |

|----------------|-----------------|------------------------------------------|------------------|

| Base + \$0     | SIM_CTRL        | Control Register                         | 6.3.1            |

| Base + \$1     | SIM_RSTAT       | Reset Status Register                    | 6.3.2            |

| Base + \$2     | SIM_SWC0        | Software Control Register 0              | 6.3.3            |

| Base + \$3     | SIM_SWC1        | Software Control Register 1              | 6.3.3            |

| Base + \$4     | SIM_SWC2        | Software Control Register 2              | 6.3.3            |

| Base + \$5     | SIM_SWC3        | Software Control Register 3              | 6.3.3            |

| Base + \$6     | SIM_MSHID       | Most Significant Half of JTAG ID         | 6.3.4            |

| Base + \$7     | SIM_LSHID       | Least Significant Half of JTAG ID        | 6.3.5            |

| Base + \$8     | SIM_PWR         | Power Control Register                   | 6.3.6            |

|                |                 | Reserved                                 |                  |

| Base + \$A     | SIM_CLKOUT      | CLKO Select Register                     | 6.3.7            |

| Base + \$B     | SIM_GPS         | GPIO Peripheral Select Register          | 6.3.8            |

| Base + \$C     | SIM_PCE         | Peripheral Clock Enable Register         | 6.3.9            |

| Base + \$D     | SIM_IOSAHI      | I/O Short Address Location High Register | 6.3.10           |

| Base + \$E     | SIM_IOSALO      | I/O Short Address Location Low Register  | 6.3.10           |

### Table 6-1 SIM Registers (SIM\_BASE = \$00 F140)

| Add.<br>Offset | Address<br>Acronym |        | 15         | 14         | 13         | 12         | 11         | 10         | 9           | 8          | 7          | 6          | 5           | 4          | 3           | 2           | 1          | 0      |

|----------------|--------------------|--------|------------|------------|------------|------------|------------|------------|-------------|------------|------------|------------|-------------|------------|-------------|-------------|------------|--------|

| \$0            | SIM_<br>CTRL       | R<br>W | TC3_<br>SD | TC2_<br>SD | TC1_<br>SD | TC0_<br>SD | SCI_<br>SD | 0          | TC3_<br>INP | 0          | 0          | 0          | ONCE<br>EBL | SW<br>RST  | STO<br>DISA | OP_<br>ABLE | WA<br>DISA | ABLE   |

| \$1            | SIM_<br>RSTAT      | R<br>W | 0          | 0          | 0          | 0          | 0          | 0          | 0           | 0          | 0          | 0          | SWR         | COPR       | EXTR        | POR         | 0          | 0      |

| \$2            | SIM_SWC0           | R<br>W |            |            |            |            |            |            | Sof         | tware Co   | ontrol Dat | a 0        |             | 1          |             |             |            |        |

| \$3            | SIM_SWC1           | R<br>W |            |            |            |            |            |            | Sof         | tware Co   | ontrol Dat | a 1        |             |            |             |             |            |        |

| \$4            | SIM_SWC2           | R<br>W |            |            |            |            |            |            | Sof         | tware Co   | ontrol Dat | a 2        |             |            |             |             |            |        |

| \$5            | SIM_SWC3           | R<br>W |            |            |            |            |            |            | Sof         | tware Co   | ontrol Dat | a 3        |             |            |             |             |            |        |

| \$6            | SIM_MSHID          | R<br>W | 0          | 0          | 0          | 0          | 0          | 0          | 0           | 1          | 1          | 1          | 1           | 1          | 0           | 0           | 1          | 0      |

| \$7            | SIM_LSHID          | R<br>W | 0          | 1          | 0          | 0          | 0          | 0          | 0           | 0          | 0          | 0          | 0           | 1          | 1           | 1           | 0          | 1      |

| \$8            | SIM_PWR            | R<br>W | 0          | 0          | 0          | 0          | 0          | 0          | 0           | 0          | 0          | 0          | 0           | 0          | 0           | 0           | LRST       | ГDBY   |

|                | Reserved           |        |            |            |            |            |            |            |             |            |            |            |             |            |             |             |            |        |

| \$A            | SIM_<br>CLKOUT     | R<br>W | 0          | 0          | 0          | 0          | 0          | 0          | PWM3        | PWM2       | PWM1       | PWM0       | CLK<br>DIS  |            | C           | CLKOSEI     |            |        |

| \$В            | SIM_GPS            | R<br>W | TCR        | PCR        | 0          | 0          | CFG_<br>B7 | CFG_<br>B6 | CFG_<br>B5  | CFG_<br>B4 | CFG_<br>B3 | CFG_<br>B2 | CFG_<br>B1  | CFG_<br>B0 | CFG         | 6_A5        | CFG        | 6_A4   |

| \$C            | SIM_PCE            | R<br>W | I2C        | 0          | ADC        | 0          | 0          | 0          | 0           | 0          | 0          | TMR        | 0           | SCI        | 0           | SPI         | 0          | PWM    |

| \$D            | SIM_IOSAHI         | R<br>W | 0          | 0          | 0          | 0          | 0          | 0          | 0           | 0          | 0          | 0          | 0           | 0          | 0           | 0           | ISAL[      | 23:22] |

| \$E            | SIM_IOSALO         | R<br>W |            |            |            |            |            |            |             | ISAL       | [21:6]     |            |             |            |             |             |            |        |

|                |                    |        | 0          | = Read     | 20.0       |            | 1          | = Read     | ae 1        |            |            |            |             |            |             |             |            |        |

0 = Read as 0 = Reserved = Read as 1 = Reserved

Figure 6-1 SIM Register Map Summary

## 6.3.1 SIM Control Register (SIM\_CTRL)

| Base + \$0 | 15   | 14   | 13   | 12   | 11   | 10 | 9    | 8 | 7 | 6 | 5    | 4   | 3    | 2   | 1    | 0   |

|------------|------|------|------|------|------|----|------|---|---|---|------|-----|------|-----|------|-----|

| Read       | TC3_ | TC2_ | TC1_ | TC0_ | SCI_ | 0  | TC3_ | 0 | 0 | 0 | ONCE | SW  | STO  | _   | WA   |     |

| Write      | SD   | SD   | SD   | SD   | SD   |    | INP  |   |   |   | EBL  | RST | DISA | BLE | DISA | BLE |

| RESET      | 0    | 0    | 0    | 0    | 0    | 0  | 0    | 0 | 0 | 0 | 0    | 0   | 0    | 0   | 0    | 0   |

Figure 6-2 SIM Control Register (SIM\_CTRL)

#### 6.3.1.1 Timer Channel 3 Stop Disable (TC3\_SD)—Bit 15

This bit enables the operation of the Timer Channel 3 peripheral clock in Stop mode.

• 0 = Timer Channel 3 disabled in Stop mode

### 6.3.1.11 Stop Disable (STOP\_DISABLE[1:0])—Bits 3–2

- 00 = Stop mode will be entered when the 56800E core executes a STOP instruction

- 01 = The 56800E STOP instruction will not cause entry into Stop mode

- 10 = Stop mode will be entered when the 56800E core executes a STOP instruction and the STOP\_DISABLE field is write-protected until the next reset

- 11 = The 56800E STOP instruction will not cause entry into Stop mode and the STOP\_DISABLE field is write-protected until the next reset

#### 6.3.1.12 Wait Disable (WAIT\_DISABLE[1:0])—Bits 1–0

- 00 = Wait mode will be entered when the 56800E core executes a WAIT instruction

- 01 = The 56800E WAIT instruction will not cause entry into Wait mode

- 10 = Wait mode will be entered when the 56800E core executes a WAIT instruction and the WAIT\_DISABLE field is write-protected until the next reset

- 11 = The 56800E WAIT instruction will not cause entry into Wait mode and the WAIT\_DISABLE field is write-protected until the next reset

### 6.3.2 SIM Reset Status Register (SIM\_RSTAT)

This register is updated upon any system reset and indicates the cause of the most recent reset. It also controls whether the COP reset vector or regular reset vector in the vector table is used. This register is asynchronously reset during Power-On Reset (see power supervisor module) and subsequently is synchronously updated based on the level of the external reset, software reset, or cop reset inputs. Only one source will ever be indicated. In the event that multiple reset sources assert simultaneously, the highest-precedence source will be indicated. The precedence from highest to lowest is POR, EXTR, COPR, and SWR. While POR is always set during a Power-On Reset (POR) has deasserted.

| Base + \$1 | 15 | 14 | 13 | 12 | 11 | 10 | 9 | 8 | 7 | 6 | 5   | 4    | 3    | 2    | 1 | 0 |

|------------|----|----|----|----|----|----|---|---|---|---|-----|------|------|------|---|---|

| Read       | 0  | 0  | 0  | 0  | 0  | 0  | 0 | 0 | 0 | 0 | SWR | COPR | EXTR | POR  | 0 | 0 |

| Write      |    |    |    |    |    |    |   |   |   |   | own | oon  | EXIN | 1 OK |   |   |

| RESET      | 0  | 0  | 0  | 0  | 0  | 0  | 0 | 0 | 0 | 0 |     |      |      |      | 0 | 0 |

#### Figure 6-3 SIM Reset Status Register (SIM\_RSTAT)

#### 6.3.2.1 Reserved—Bits 15–6

This bit field is reserved or not implemented. It is read as zero and cannot be modified by writing.

#### 6.3.2.2 Software Reset (SWR)—Bit 5

When set, this bit indicates that the previous system reset occurred as a result of a software reset (written 1 to SWRST bit in the SIM\_CTRL register). It will not be set if a COP, external, or POR reset also occurred.

#### 6.3.2.3 COP Reset (COPR)—Bit 4

When set, this bit indicates that the previous system reset was caused by the Computer Operating Properly

generation and SIM modules. All functionality is for test purposes only and is subject to unspecified latencies. Glitches may be produced when the clock is enabled or switched.

The lower four bits of the GPIO A register can function as GPIO, PWM, or as additional clock output signals. GPIO has priority and is enabled/disabled via the GPIOA\_PEREN. If GPIOA[3:0] are programmed to operate as peripheral outputs, then the choice between PWM and additional clock outputs is done here in the CLKOUT. The default state is for the peripheral function of GPIOA[3:0] to be programmed as PWM. This can be changed by altering PWM3 through PWM0.

| Base + \$A | 15 | 14 | 13 | 12 | 11 | 10 | 9       | 8       | 7      | 6       | 5   | 4 | 3 | 2      | 1 | 0 |

|------------|----|----|----|----|----|----|---------|---------|--------|---------|-----|---|---|--------|---|---|

| Read       | 0  | 0  | 0  | 0  | 0  | 0  | PWM3    | PWM2    | PWM1   | PWM0    | CLK |   | C | LKOSE  | I |   |

| Write      |    |    |    |    |    |    | 1 11110 | 1 11112 | 1 1111 | 1 11110 | DIS |   | 0 | LIXOOL | - |   |

| RESET      | 0  | 0  | 0  | 0  | 0  | 0  | 0       | 0       | 0      | 0       | 1   | 0 | 0 | 0      | 0 | 0 |

#### Figure 6-8 CLKO Select Register (SIM\_CLKOUT)

#### 6.3.7.1 Reserved—Bits 15–10

This bit field is reserved or not implemented. It is read as 0 and cannot be modified by writing.

#### 6.3.7.2 **PWM**3—Bit 9

- 0 = Peripheral output function of GPIOA[3] is defined to be  $\overline{PWM3}$

- 1 = Peripheral output function of GPIOA[3] is defined to be the Relaxation Oscillator Clock

#### 6.3.7.3 PWM2—Bit 8

- 0 = Peripheral output function of GPIOA[2] is defined to be  $\overline{PWM2}$

- 1 = Peripheral output function of GPIOA[2] is defined to be the system clock

#### 6.3.7.4 PWM1—Bit 7

- $0 = Peripheral output function of GPIOA[1] is defined to be <math>\overline{PWM1}$

- 1 = Peripheral output function of GPIOA[1] is defined to be two times the rate of the system clock

#### 6.3.7.5 **PWM0**—Bit 6

- 0 = Peripheral output function of GPIOA[0] is defined to be  $\overline{PWM0}$

- 1 = Peripheral output function of GPIOA[0] is defined to be three times the rate of the system clock

#### 6.3.7.6 Clockout Disable (CLKDIS)—Bit 5

- 0 = CLKOUT output is enabled and will output the signal indicated by CLKOSEL

- 1 = CLKOUT is 0

#### 6.3.7.7 Clockout Select (CLKOSEL)—Bits 4–0

Selects clock to be muxed out on the CLKO pin.

• 00000 = Reserved for factory test—Continuous system clock

### 6.3.8.1 Quad Timer Clock Rate (TCR)—Bit 15

This bit selects the clock speed for the Quad Timermodule.

- 0 = Quad Timer module clock rate equals system clock rate, to a maximum 32MHz (default)

- 1 = Quad Timer module clock rate equals three times system clock rate, to a maximum 96MHz

Note: This bit should only be changed while the TMR module's clock is disabled. See Section 6.3.9.

Note: High-speed clocking is only available when the PLL is being used.

**Note:** If the PWM sync signal pulse is used as input to Timer 3 (See SIM\_CTRL: TC3\_INP, Section 6.3.1.7), then the clocks of the Quad Timer and PWM must be related, as shown in Table 6-2.

#### 6.3.8.2 PWM Clock Rate (PCR)—Bit 14

This bit selects the clock speed for the PWM module.

- 0 = PWM module clock rate equals system clock rate, to a maximum 32MHz (default)

- 1 = PWM module clock rate equals three times system clock rate, to a maximum 96MHz

Note: This bit should only be changed while the PWM module's clock is disabled. See Section 6.3.9.

Note: High-speed clocking is only available when the PLL is being used.

**Note:** If the PWM sync signal is used as input to Timer 3 (See SIM\_CTRL: TC3\_INP, Section 6.3.1.7), then the clocks of the Quad Timer and PWM must be related, as shown in Table 6-2.

| Table 6-2 Allowable Quad Timer and PWM Clock Rates |

|----------------------------------------------------|

| when Using PWM Reload Pulse                        |

|         |             | Quad Timer |    |  |  |  |

|---------|-------------|------------|----|--|--|--|

|         | Clock Speed | 1X         | 3Х |  |  |  |

| PWM     | 1X          | ОК         | ОК |  |  |  |

| F VVIVI | 3X          | NO         | ОК |  |  |  |

#### 6.3.8.3 Reserved—Bits 13–12

This bit field is reserved or not implemented. It is read as 0 and cannot be modified by writing.

#### 6.3.8.4 Configure GPIOB7 (CFG\_B7)—Bit 11

This bit selects the alternate function for GPIOB7.

- 0 = TXD SCI Transmit Data (default)

- 1 = SCL I2C Serial Clock

#### 6.3.8.5 Configure GPIOB6 (CFG\_B6)—Bit 10

This bit selects the alternate function for GPIOB6.

| Mode       | Core Clocks                                                                     | Peripheral Clocks                   | Description                                                                                                                                                                                                                                                                                                                                                                                                                                           |

|------------|---------------------------------------------------------------------------------|-------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Wait       | Core and memory<br>clocks disabled                                              | Peripheral clocks<br>enabled        | Core executes WAIT instruction to enter this<br>mode.<br>Typically used for power-conscious applications.<br>Possible recoveries from Wait mode to Run<br>mode are:<br>1. Any interrupt<br>2. Executing a Debug mode entry command<br>during the 56800E core JTAG interface<br>2. Any reset (POR, external, software, COP)                                                                                                                            |

| Stop       | Master clock genera<br>remains operational,<br>the generation of sys<br>clocks. | but the SIM disables                | Core executes STOP instruction to enter this<br>mode. Possible recoveries from Stop mode to<br>Run mode are:<br>1. Interrupt from Timer channels that have been<br>configured to operate in Stop mode (TCx_SD)<br>2. Interrupt for SCI configured to operate in Stop<br>mode (SCI_SD)<br>3. Low-voltage interrupt<br>4. Executing a Debug mode entry command<br>using the 56800E core JTAG interface<br>5. Any reset (POR, external, software, COP)   |

| Standby    |                                                                                 | h-speed peripheral<br>e. System and | The user configures the OCCS and SIM to select<br>the relaxation oscillator clock source (PRECS),<br>shut down the PLL (PLLPD), put the relaxation<br>oscillator in Standby mode (ROSB), and put the<br>large regulator in Standby (LRSTDBY). The part<br>is fully operational, but operating at a minimum<br>frequency and power configuration. Recovery<br>requires reversing the sequence used to enter<br>this mode (allowing for PLL lock time). |

| Power-Down | Master clock genera<br>completely shut dow<br>peripheral clocks are             | n. All system and                   | The user configures the OCCS and SIM to enter<br>Standby mode as shown in the previous<br>description, followed by powering down the<br>oscillator (ROPD). The only possible recoveries<br>from this mode are:<br>1. External Reset<br>2. Power-On Reset                                                                                                                                                                                              |

#### Table 6-3 Clock Operation in Power-Down Modes (Continued)

The power modes provide additional means to disable clock domains, configure the voltage regulator, and configure clock generation to manage power utilization, as shown in **Table 6-3**. Run, Wait, and Stop modes provide means of enabling/disabling the peripheral and/or core clocking as a group. Stop disable controls are provided for selected peripherals in the control register so that these peripheral clocks can optionally continue to operate in Stop mode and generate interrupts which will return the part from Stop to Run mode. Standby mode provides normal operation but at very low speed and power utilization. It is possible to invoke Stop or Wait mode while in Standby mode for even greater levels of power reduction. A 200kHz clock external clock can optionally be used in Standby mode to produce the required Standby 100kHz system bus rate. Power-down mode, which selects the ROSC clock source but shuts it off, fully disables the part and minimizes its power utilization but is only recoverable via reset.

When the PLL is not selected and the system bus is operating at around 100kHz, the large regulator can be put into its Standby mode (LRSTDBY) to reduce the power utilization of that regulator.

All peripherals, except the COP/watchdog timer, run at the system clock (peripheral bus) frequency<sup>1</sup>, which is the same as the main processor frequency in this architecture. The COP timer runs at MSTR\_OSC / 1024. The maximum frequency of operation is SYS\_CLK = 32MHz. The only exception is the Quad Timer and PWM, which can be configured to operate at three times the system bus rate using TCR and PCR controls, provided the PLL is active and selected.

# 6.6 Resets

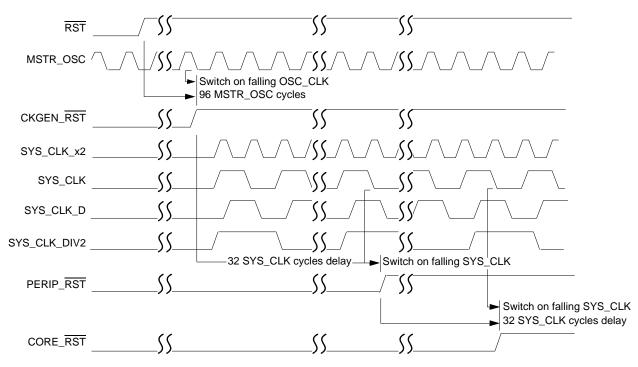

The SIM supports four sources of reset, as shown in **Figure 6-15**. The two asynchronous sources are the external reset pin and the Power-On Reset (POR). The two synchronous sources are the software reset, which is generated within the SIM itself by writing the SIM\_CTRL register in Section 6.3.1, and the COP reset. The SIM uses these to generate resets for the internal logic. These are outlined in Table 6-4. The first column lists the four primary resets which are calculated. The JTAG circuitry is reset by the Power-On Reset. Columns two through five indicate which reset sources trigger these reset signals. The last column provides additional detail.

|              |     | Reset S  | Sources  |     |                                                                                                     |

|--------------|-----|----------|----------|-----|-----------------------------------------------------------------------------------------------------|

| Reset Signal | POR | External | Software | COP | Comments                                                                                            |

| EXTENDED_POR | Х   |          |          |     | Stretched version of POR. Relevant 64<br>Relaxation Oscillator Clock cycles after<br>POR deasserts. |

| CLKGEN_RST   | Х   | Х        | Х        | Х   | Released 32 Relaxation Oscillator Clock cycles after all reset sources have released.               |

| PERIP_RST    | Х   | х        | х        | Х   | Releases 32 Relaxation Oscillator Clock cycles after the CLKGEN_RST is released.                    |

| CORE_RST     | Х   | Х        | Х        | Х   | Releases 32 SYS_CLK periods after PERIP_RST is released.                                            |

**Table 6-4 Primary System Resets**

**Figure 6-15** provides a graphic illustration of the details in **Table 6-4**. Note that the POR\_Delay blocks use the Relaxation Oscillator Clock as their time base since other system clocks are inactive during this phase of reset.

<sup>1.</sup> The Quad Timer and PWM modules can be operated at three times the IPBus clock frequency.

# Maximum Delay = 64 MSTR\_OSC cycles for POR reset extension and 32 MSTR\_OSC cycles for combined reset extension

Figure 6-16 Timing Relationships of Reset Signal to Clocks

# 6.8 Interrupts

The SIM generates no interrupts.

# Part 7 Security Features

The 56F8013/56F8011 offers security features intended to prevent unauthorized users from reading the contents of the flash memory (FM) array. The 56F8013/56F8011's flash security consists of several hardware interlocks that prevent unauthorized users from gaining access to the flash array.

After flash security is set, an authorized user is still able to access on-chip memory if the user purposely includes a subroutine to read and transfer the contents of internal memory via serial communication peripherals, as this code would defeat the purpose of security.

# 7.1 Operation with Security Enabled

After the user has programmed the flash with his application code, the 56F8013/56F8011 can be secured by programming a security word (\$E70A) into program memory location \$00 1FF7. This nonvolatile word will keep the device secured through reset and through power-down of the device. Refer to the flash

| Add.<br>Offset | Register Acronym            |                                  | 15               | 14               | 13                    | 12               | 11               | 10               | 9                | 8                | 7 | 6 | 5 | 4                   | 3                    | 2 | 1 | 0 |

|----------------|-----------------------------|----------------------------------|------------------|------------------|-----------------------|------------------|------------------|------------------|------------------|------------------|---|---|---|---------------------|----------------------|---|---|---|

| \$0            | GPIOA_PUPEN                 | R<br>W<br>RS                     | 0                | 0                | 0                     | 0                | 0                | 0                | 0                | 0                | 1 | 1 | 1 | P                   | U<br>1               | 1 | 1 | 1 |

|                |                             | R                                | 0                | 0                | 0                     | 0                | 0                | 0                | 0                | 0                | • | • | • |                     | <br>>                | • | • |   |

| \$1            | GPIOA_DATA                  | W<br>RS                          | 0                | 0                | 0                     | 0                | 0                | 0                | 0                | 0                | 0 | 1 | 1 | 1                   | 1                    | 1 | 1 | 1 |

| \$2            | GPIOA_DDIR                  | R<br>W<br>RS                     | 0                | 0                | 0                     | 0                | 0                | 0                | 0                | 0                | 0 | 0 | 0 | D<br>0              | D<br>0               | 0 | 0 | 0 |

| \$3            | GPIOA_PEREN                 | R                                | 0                | 0                | 0                     | 0                | 0                | 0                | 0                | 0                |   |   |   | P                   | ļ                    |   |   |   |

| ΨŬ             |                             | RS                               | 0                | 0                | 0                     | 0                | 0                | 0                | 0                | 0                | 1 | 0 | 0 | 0                   | 0                    | 0 | 0 | 0 |

| \$4            | GPIOA_IASSRT                | R<br>W                           | 0                | 0                | 0                     | 0                | 0                | 0                | 0                | 0                | 0 | 0 | 0 |                     | A                    |   |   |   |

|                |                             | RS<br>R                          | 0                | 0                | 0                     | 0                | 0                | 0                | 0                | 0                | 0 | 0 | 0 | 0                   | 0                    | 0 | 0 | 0 |

| \$5            | GPIOA_IEN                   | W                                | 0                | 0                | 0                     | 0                | 0                | 0                | 0                | 0                | 0 | 0 | 0 | IE<br>0             | N<br>0               | 0 | 0 | 0 |

|                |                             | R                                | 0                | 0                | 0                     | 0                | 0                | 0                | 0                | 0                |   |   |   | IEP                 |                      |   |   |   |

| \$6            | GPIOA_IEPOL                 | W<br>RS                          | 0                | 0                | 0                     | 0                | 0                | 0                | 0                | 0                | 0 | 0 | 0 | 0                   | 0                    | 0 | 0 | 0 |

| \$7            | GPIOA_IPEND                 | R<br>W                           | 0                | 0                | 0                     | 0                | 0                | 0                | 0                | 0                |   |   |   | IP                  | ۲R                   |   |   |   |

| Ψï             |                             | RS                               | 0                | 0                | 0                     | 0                | 0                | 0                | 0                | 0                | 0 | 0 | 0 | 0                   | 0                    | 0 | 0 | 0 |

| \$8            | GPIOA_IEDGE                 | R                                | 0                | 0                | 0                     | 0                | 0                | 0                | 0                | 0                |   |   |   | IE                  | S                    |   |   |   |

|                |                             | W                                |                  |                  |                       |                  |                  |                  |                  |                  |   |   |   |                     |                      |   |   |   |

|                |                             | RS                               | 0                | 0                | 0                     | 0                | 0                | 0                | 0                | 0                | 0 | 0 | 0 | 0                   | 0                    | 0 | 0 | 0 |

| \$9            | GPIOA_PPOUTM                | RS<br>R<br>W                     | 0                | 0                | 0                     | 0                | 0                | 0                | 0                | 0                |   |   | - | OE                  | ΞN                   | I | I |   |

| \$9            |                             | RS<br>R                          |                  |                  |                       |                  |                  |                  |                  |                  | 0 | 0 | 1 |                     | EN<br>1              | 1 | 0 | 0 |

| \$9<br>\$A     |                             | RS<br>R<br>W<br>RS               | 0                | 0                | 0                     | 0                | 0                | 0                | 0                | 0                |   |   | 1 | OF<br>1             | EN<br>1              | 1 | I |   |

|                | GPIOA_PPOUTM                | RS<br>R<br>R<br>R<br>S<br>R<br>S | 0<br>0           | 0                | 0                     | 0                | 0                | 0 0 0            | 0 0 0            | 0                | 1 | 1 | 1 | OF<br>1<br>RAW      | EN<br>1<br>DATA<br>X | 1 | 1 |   |

| \$A            | GPIOA_PPOUTM<br>GPIOA_RDATA |                                  | 0<br>0<br>0<br>X | 0<br>0<br>0<br>X | 0<br>0<br>0<br>X<br>0 | 0<br>0<br>0<br>X | 0<br>0<br>0<br>X | 0<br>0<br>0<br>X | 0<br>0<br>0<br>X | 0<br>0<br>0<br>X | 1 | 1 | 1 | OF<br>1<br>RAW<br>X | EN<br>1<br>DATA<br>X | 1 | 1 |   |

#### Figure 8-1 GPIOA Register Map Summary

56F8013/56F8011 Data Sheet, Rev. 12

| Characteristic                                     | Symbol             | Min  | Тур  | Мах | Unit |

|----------------------------------------------------|--------------------|------|------|-----|------|

| Low-Voltage Interrupt for 3.3V supply <sup>1</sup> | V <sub>EI3.3</sub> | 2.58 | 2.7  |     | V    |

| Low-Voltage Interrupt for 2.5V supply <sup>2</sup> | V <sub>E12.5</sub> | -    | 2.15 | -   | V    |

| Low-Voltage Interrupt Recovery Hysteresis          | V <sub>EIH</sub>   | _    | 50   | _   | mV   |

| Power-On Reset <sup>3</sup>                        | POR                | _    | 1.8  | 1.9 | V    |

Table 10-7 Power-On Reset Low-Voltage Parameters

1. When  $V_{DD}$  drops below  $V_{EI3.3}$ , an interrupt is generated.

2. When  $V_{DD}$  drops below  $V_{E132.5}$ , an interrupt is generated.

3. Power-On Reset occurs whenever the internally regulated 2.5V digital supply drops below 1.8V. While power is ramping up, this signal remains active for as long as the internal 2.5V is below 2.15V or the 3.3V 1/O voltage is below 2.7V, no matter how long the ramp-up rate is. The internally regulated voltage is typically 100mV less than V<sub>DD</sub> during ramp-up until 2.5V is reached, at which time it self-regulates.

### **10.2.1** Voltage Regulator Specifications

The 56F8013/56F8011 have two on-chip regulators. One supplies the PLL and relaxation oscillator. It has no external pins and therefore has no external characteristics which must be guaranteed (other than proper operation of the device). The second regulator supplies approximately 2.5V to the 56F8013/56F8011's core logic. This regulator requires an external  $2.2\mu$ F, or greater, capacitor for proper operation. Ceramic and tantalum capacitors tend to provide better performance tolerances. The output voltage can be measured directly on the V<sub>CAP</sub> pin. The specifications for this regulator are shown in **Table 10-8**.

Table 10-8. Regulator Parameters

| Characteristic                                        | Symbol           | Min | Typical | Max | Unit    |

|-------------------------------------------------------|------------------|-----|---------|-----|---------|

| Short Circuit Current                                 | I <sub>SS</sub>  | _   | 450     | 650 | mA      |

| Short Circuit Tolerance<br>(output shorted to ground) | T <sub>RSC</sub> | —   | —       | 30  | Minutes |

# **10.3 AC Electrical Characteristics**

Tests are conducted using the input levels specified in **Table 10-5**. Unless otherwise specified, propagation delays are measured from the 50% to the 50% point, and rise and fall times are measured between the 10% and 90% points, as shown in **Figure 10-2**.

# **10.12** Inter-Integrated Circuit Interface (I<sup>2</sup>C) Timing

|                                                                                                        |                      | Standa  | rd Mode           | Fast                              | Mode             |      |

|--------------------------------------------------------------------------------------------------------|----------------------|---------|-------------------|-----------------------------------|------------------|------|

| Characteristic                                                                                         | Symbol               | Minimum | Maximum           | Minimum                           | Maximum          | Unit |

| SCL Clock Frequency                                                                                    | f <sub>SCL</sub>     | 0       | 100               | 0                                 | 400              | kHz  |

| Hold time (repeated )<br>START condition. After<br>this period, the first clock<br>pulse is generated. | t <sub>HD; STA</sub> | 4.0     |                   | 0.6                               |                  | μS   |

| LOW period of the SCL clock                                                                            | t <sub>LOW</sub>     | 4.7     |                   | 1.25                              |                  | μS   |

| HIGH period of the SCL clock                                                                           | t <sub>HIGH</sub>    | 4.0     |                   | 0.6                               |                  | μS   |

| Set-up time for a repeated START condition                                                             | t <sub>SU; STA</sub> | 4.7     |                   | 0.6                               |                  | μS   |

| Data hold time for I <sup>2</sup> C bus devices                                                        | t <sub>HD; DAT</sub> | 01      | 3.45 <sup>2</sup> | 01                                | 0.9 <sup>2</sup> | μS   |

| Data set-up time                                                                                       | t <sub>SU; DAT</sub> | 250     |                   | 100 <sup>3</sup>                  |                  | ns   |

| Rise time of both SDA and SCL signals                                                                  | t <sub>r</sub>       |         | 1000              | 2 +0.1C <sub>b</sub> <sup>4</sup> | 300              | ns   |

| Fall time of both SDA and SCL signals                                                                  | t <sub>f</sub>       |         | 300               | 2 +0.1C <sub>b</sub> <sup>4</sup> | 300              | ns   |

| Set-up time for STOP condition                                                                         | t <sub>SU; STO</sub> | 4.0     |                   | 0.6                               |                  | μS   |

| Bus free time between<br>STOP and START<br>condition                                                   | t <sub>BUF</sub>     | 4.7     |                   | 1.3                               |                  | μS   |

| Pulse width of spikes that<br>must be suppressed by<br>the input filter                                | t <sub>SP</sub>      | N/A     | N/A               | 0.0                               | 50               | ns   |

#### Table 10-17 I<sup>2</sup>C Timing

1. A device must internally provide a hold time of at least 300ns for the SDA signal (referred to the V<sub>IH</sub> min of the SCL signal) to bridge the undefined region of the falling edge of SCL.

2. The maximum  $t_{HD; DAT}$  has only to be met if the device does not stretch the LOW period ( $t_{LOW}$ ) of the SCL signal.

3. A Fast mode I<sup>2</sup>C bus device can be used in a Standard mode I<sup>2</sup>C bus system, but the requirement  $t_{SU; DAT} > = 250$ ns must then be met. This will automatically be the case if the device does not stretch the LOW period of the SCL signal. If such a device does stretch the LOW period of the SCL signal, it must output the next data bit to the SDA line  $t_{rmax} + t_{SU; DAT} = 1000 + 250 = 1250$ ns (according to the Standard mode I<sup>2</sup>C bus specification) before the SCL line is released.

4. C<sub>b</sub> = total capacitance of the one bus line in pF.

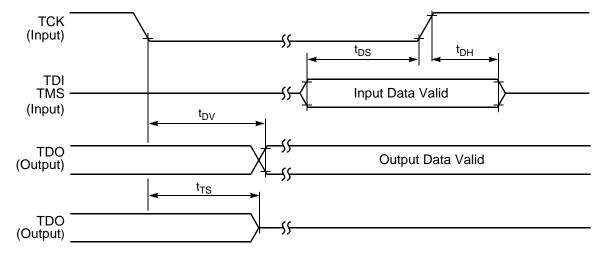

Figure 10-16 Test Access Port Timing Diagram

| Pin<br>No. | Signal Name                              | Pin<br>No. | Signal Name                              | Pin<br>No. | Signal Name                             | Pin<br>No. | Signal Name          |

|------------|------------------------------------------|------------|------------------------------------------|------------|-----------------------------------------|------------|----------------------|

| 1          | <b>GPIOB6</b><br>RXD,SDA,CLKIN           | 9          | V <sub>SSA</sub>                         | 17         | <b>GPIOB2</b><br><i>MISO,T</i> 2        | 25         | V <sub>CAP</sub>     |

| 2          | GPIOB1<br>SS,SDA                         | 10         | <b>ANA2</b><br>V <sub>REFH</sub> ,GPIOC2 | 18         | <b>GPIOA6</b><br>FAULTO                 | 26         | V <sub>DD</sub>      |

| 3          | <b>GPIOB7</b><br>TXD,SCL                 | 11         | ANA1<br>GPIOC1                           | 19         | <b>GPIOB4</b><br><i>T0,CLKO</i>         | 27         | V <sub>SS</sub>      |

| 4          | <b>GPIOB5</b><br>T1,FAULT3               | 12         | ANA0<br>GPIOC0                           | 20         | <b>GPIOA5</b><br>PWM5,FAULT2,T3         | 28         | GPIOA1<br>PWM1       |

| 5          | <b>ANB0</b><br>GPIOC4                    | 13         | V <sub>SS</sub>                          | 21         | <b>GPIOB0</b><br>SCLK,SCL               | 28         | GPIOA0<br>PWM0       |

| 6          | ANB1<br>GPIOC5                           | 14         | TCK<br>GPIOD2                            | 22         | <b>GPIOA4</b><br><i>PWM4,FAULT1,T</i> 2 | 30         | <b>TDI</b><br>GPIOD0 |

| 7          | <b>ANB2</b><br>V <sub>REFL</sub> ,GPIOC6 | 15         | RESET<br>GPIOA7                          | 23         | GPIOA2<br>PWM2                          | 31         | TMS<br>GPIOD3        |

| 8          | V <sub>DDA</sub>                         | 16         | <b>GPIOB3</b><br>MOSI,T3                 | 24         | GPIOA3<br>PWM3                          | 32         | <b>TDO</b><br>GPIOD1 |

# Table 11-1 56F8013/56F8011 32-Pin LQFP Package Identification by Pin Number<sup>1</sup>

1.Alternate signals are in iltalic

# Part 13 Ordering Information

**Table 13-1** lists the pertinent information needed to place an order. Consult a Freescale Semiconductor sales office or authorized distributor to determine availability and to order parts.

| Part      | Supply<br>Voltage | Package Type                      | Pin<br>Count | Frequency<br>(MHz) | Ambient<br>Temperature<br>Range | Order Number   |

|-----------|-------------------|-----------------------------------|--------------|--------------------|---------------------------------|----------------|

| MC56F8013 | 3.0–3.6 V         | Low-Profile Quad Flat Pack (LQFP) | 32           | 32                 | –40° to + 125°C                 | MC56F8013MFAE* |

| MC56F8013 | 3.0–3.6 V         | Low-Profile Quad Flat Pack (LQFP) | 32           | 32                 | –40° to + 125°C                 | S568013MFA00E* |

| MC56F8013 | 3.0–3.6 V         | Low-Profile Quad Flat Pack (LQFP) | 32           | 32                 | -40° to + 105°C                 | MC56F8013VFAE* |

| MC56F8011 | 3.0–3.6 V         | Low-Profile Quad Flat Pack (LQFP) | 32           | 32                 | –40° to + 105°C                 | MC56F8011VFAE* |

Table 13-1 56F8013/56F8011 Ordering Information

\*This package is RoHS compliant.

# Part 14 Appendix

Register acronyms are revised from previous device data sheets to provide a cleaner register description. A cross reference to legacy and revised acronyms are provided in the following table.

|                  |                                | Peripheral Re  | eference Manual | Data         | Sheet          | Processor         | Memory Address |                  |  |

|------------------|--------------------------------|----------------|-----------------|--------------|----------------|-------------------|----------------|------------------|--|

| Module           | Register Name                  | New<br>Acronym |                 |              | Legacy Acronym | Expert<br>Acronym | Start          | End              |  |

|                  |                                |                |                 |              |                |                   |                |                  |  |

| ADC              | Control Register 1             | CTRL1          | ADCR1           | ADC_CTRL1    | ADC_ADCR1      | ADC_ADCR1         | 0xF            | 080              |  |

|                  | Control Register 2             | CTRL2          | ADCR2           | ADC_CTRL2    | ADC_ADCR2      | ADC_ADCR2         | 0xF            | 081              |  |

|                  | Zero Crossing Control Register | ZXCTRL         | ADZCC           | ADC_ZXCTRL   | ADC_ADZCC      | ADC_ADZCC         | 0xF            | 082              |  |

|                  | Channel List Register 1        | CLIST1         | ADLST1          | ADC_CLIST1   | ADC_ADLST1     | ADC_ADLST1        | 0xF            | 083              |  |

|                  | Channel List Register 2        | CLIST2         | ADLST2          | ADC_CLIST2   | ADC_ADLST2     | ADC_ADLST2        | 0xF            | 084              |  |

|                  | Sample Disable Register        | SDIS           | ADSDIS          | ADC_SDIS     | ADC_ADSDIS     | ADC_ADSDIS        | 0xF            | 085              |  |

|                  | Status Register                | STAT           | ADSTAT          | ADC_STAT     | ADC_ADSTAT     | ADC_ADSTAT        | 0xF            | 086              |  |

|                  | Limit Status Register          | LIMSTAT        | ADLSTAT         | ADC_LIMSTAT  | ADC_ADLSTAT    | ADC_ADLSTAT       | 0xF            | 087              |  |

|                  | Zero Crossing Status Register  | ZXSTAT         | ADZCSTAT        | ADC_ZXSTAT   | ADC_ADZCSTAT   | ADC_ADZCSTAT      | 0xF            | 088              |  |

|                  | Result Registers 0-7           | RSLT0-7        | ADRSLT0-7       | ADC_RSLT0-7  | ADC_ADRSLT0-7  | ADC_ADRSLT0-7     | 0xF089         | 0XF090           |  |

|                  | Low Limit Registers 0-7        | LOLIM0-7       | ADLLMT0-7       | ADC_LOLIM0-7 | ADC_ADLLMT0-7  | ADC_ADLLMT0-7     | 0XF091         | 0XF098           |  |

|                  | High Limit Registers 0-7       | HILIM0-7       | ADHLMT0-7       | ADC_HILIM0-7 | ADC_ADHLMT0-7  | ADC_ADHLMT0-7     | 0XF099         | 0XF0A0           |  |

|                  | Offset Registers 0-7           | OFFST0-7       | ADOFS0-7        | ADC_OFFST0-7 | ADC_ADOFS0-7   | ADC_ADOFS0-7      | 0XF0A1         | 0XF0A8           |  |

|                  | Power Control Register         | PWR            | ADPOWER         | ADC_PWR      | ADC_ADPOWER    | ADC_ADPOWER       | 0XF            | 0A9              |  |

|                  | Voltage Reference Register     | CAL            | ADCAL           | ADC_VREF     | ADC_ADCAL      | ADC_CAL           | 0XF            | 0AA              |  |

| СОР              | Control Register               | CTRL           | COPCTL          | COP_CTRL     | COPCTL         | COPCTL            |                | 050              |  |

| COF              | Time-Out Register              | TOUT           | COPTO           | COP_CIRE     | COPTO          | COPTO             | <b>.</b>       | 0XF0E0           |  |

|                  | Counter Register               | CNTR           | COPCTR          | COP_TOUT     | COPCTR         | COPTO             | -              | 0XF0E1<br>0XF0E2 |  |

|                  |                                | CNTR           | COPCIR          | COF_CNTR     | COPCIN         | COPCIR            |                | UEZ              |  |

| I <sup>2</sup> C | Address Register               | ADDR           | IBAD            | I2C_ADDR     | I2C_IBAD       | IBAD              | 0xF0D0         |                  |  |

|                  | Frequency Divider Register     | FDIV           | IBFD            | I2C_FDIV     | I2C_IBFD       | IBFD              | 0xF            | 0xF0D1           |  |

|                  | Control Register               | CTRL           | IBCR            | I2C_CTRL     | I2C_IBCR       | IBCR              | 0xF            | 0xF0D2           |  |