Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Obsolete                                                     |

|----------------------------|--------------------------------------------------------------|

| Core Processor             | 8051                                                         |

| Core Size                  | 8-Bit                                                        |

| Speed                      | 25MHz                                                        |

| Connectivity               | SMBus (2-Wire/I <sup>2</sup> C), SPI, UART/USART, USB        |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, Temp Sensor, WDT           |

| Number of I/O              | 21                                                           |

| Program Memory Size        | 16KB (16K x 8)                                               |

| Program Memory Type        | FLASH                                                        |

| EEPROM Size                | -                                                            |

| RAM Size                   | 2.25K x 8                                                    |

| Voltage - Supply (Vcc/Vdd) | 2.7V ~ 3.6V                                                  |

| Data Converters            | A/D 13x10b                                                   |

| Oscillator Type            | Internal                                                     |

| Operating Temperature      | -40°C ~ 85°C (TA)                                            |

| Mounting Type              | Surface Mount                                                |

| Package / Case             | 28-VFQFN Exposed Pad                                         |

| Supplier Device Package    | 28-MLP (5x5)                                                 |

| Purchase URL               | https://www.e-xfl.com/product-detail/silicon-labs/c8051f321r |

|                            |                                                              |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# C8051F320/1

| 21.2. C2 Pin Sharing | 55 |

|----------------------|----|

|----------------------|----|

#### **1.1.3.** Additional Features

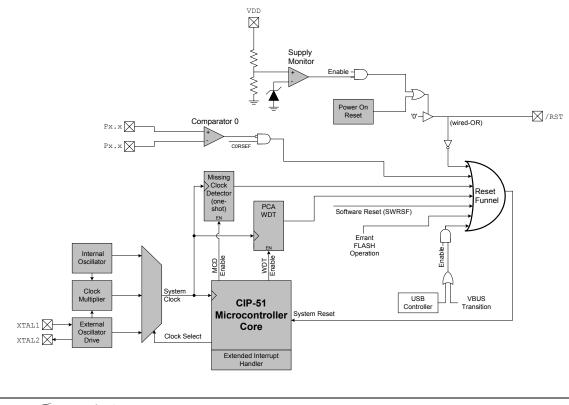

The C8051F320/1 SoC family includes several key enhancements to the CIP-51 core and peripherals to improve performance and ease of use in end applications.

The extended interrupt handler provides 16 interrupt sources into the CIP-51 (as opposed to 7 for the standard 8051), allowing numerous analog and digital peripherals to interrupt the controller. An interrupt driven system requires less intervention by the MCU, giving it more effective throughput. The extra interrupt sources are very useful when building multi-tasking, real-time systems.

Nine reset sources are available: power-on reset circuitry (POR), an on-chip VDD monitor (forces reset when power supply voltage drops below  $V_{RST}$  as given in Table 10.1 on page 105), the USB controller (USB bus reset or a VBUS transition), a Watchdog Timer, a Missing Clock Detector, a voltage level detection from Comparator0, a forced software reset, an external reset pin, and an errant FLASH read/write protection circuit. Each reset source except for the POR, Reset Input Pin, or FLASH error may be disabled by the user in software. The WDT may be permanently enabled in software after a power-on reset during MCU initialization.

The internal oscillator is factory calibrated to 12 MHz  $\pm$ 1.5%, and the internal oscillator period may be user programmed in ~0.25% increments. A clock recovery mechanism allows the internal oscillator to be used with the 4x Clock Multiplier as the USB clock source in Full Speed mode; the internal oscillator can also be used as the USB clock source in Low Speed mode. External oscillators may also be used with the 4x Clock Multiplier. An external oscillator drive circuit is also included, allowing an external crystal, ceramic resonator, capacitor, RC, or CMOS clock source to generate the system clock. The system clock may be configured to use the internal oscillator, external oscillator, or the Clock Multiplier output divided by 2. If desired, the system clock source may be switched on-the-fly between oscillator sources. An external oscillator can be extremely useful in low power applications, allowing the MCU to run from a slow (power saving) external clock source, while periodically switching to the internal oscillator as needed.

#### Figure 1.4. On-Chip Clock and Reset

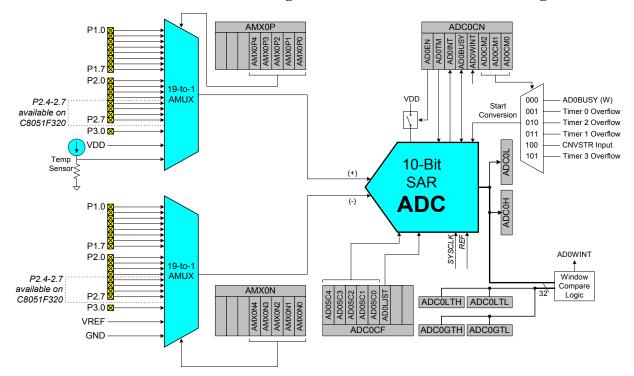

# 5. **10-BIT ADC (ADC0)**

The ADC0 subsystem for the C8051F320/1 consists of two analog multiplexers (referred to collectively as AMUX0) with 17 total input selections, and a 200 ksps, 10-bit successive-approximation-register ADC with integrated trackand-hold and programmable window detector. The AMUX0, data conversion modes, and window detector are all configurable under software control via the Special Function Registers shown in Figure 5.1. ADC0 operates in both Single-ended and Differential modes, and may be configured to measure P1.0-P3.0, the Temperature Sensor output, or VDD with respect to P1.0-P3.0, VREF, or GND. The ADC0 subsystem is enabled only when the AD0EN bit in the ADC0 Control register (ADC0CN) is set to logic 1. The ADC0 subsystem is in low power shutdown when this bit is logic 0.

| R/W      | R                                           | R/W          | R/W           | R/W            | R/W            | R/W            | R/W     | Reset Value  |  |

|----------|---------------------------------------------|--------------|---------------|----------------|----------------|----------------|---------|--------------|--|

| CP0EN    | CP0OUT                                      | CPORIF       | <b>CP0FIF</b> | CP0HYP1        | CP0HYP0        | CP0HYN1        | CP0HYN0 | 00000000     |  |

| Bit7     | Bit6                                        | Bit5         | Bit4          | Bit3           | Bit2           | Bit1           | Bit0    | SFR Address: |  |

|          |                                             |              |               |                |                |                |         | 0x9B         |  |

|          |                                             |              |               |                |                |                |         |              |  |

| Bit7:    | CP0EN: Com                                  |              |               |                |                |                |         |              |  |

|          | 0: Comparato                                | r0 Disabled. |               |                |                |                |         |              |  |

|          | 1: Comparato                                | r0 Enabled.  |               |                |                |                |         |              |  |

| Bit6:    | CP0OUT: Co                                  |              |               | Flag.          |                |                |         |              |  |

|          | 0: Voltage on                               |              |               |                |                |                |         |              |  |

|          | 1: Voltage on                               |              |               |                |                |                |         |              |  |

| Bit5:    | CPORIF: Con                                 |              |               |                |                |                |         |              |  |

|          | 0: No Compar                                |              |               |                | e this flag wa | s last cleared | d.      |              |  |

|          | 1: Comparato                                | 0            | 0             |                |                |                |         |              |  |

| Bit4:    | CP0FIF: Com                                 | -            |               | -              |                |                |         |              |  |

|          | 0: No Compar                                |              |               |                |                | as last cleare | ed.     |              |  |

|          | 1: Comparato                                |              |               |                |                |                |         |              |  |

| Bits3-2: | CP0HYP1-0:                                  |              |               | lysteresis Cor | ntrol Bits.    |                |         |              |  |

|          | 00: Positive H                              | •            |               |                |                |                |         |              |  |

|          | 01: Positive H                              |              |               |                |                |                |         |              |  |

|          | 10: Positive Hysteresis = $10 \text{ mV}$ . |              |               |                |                |                |         |              |  |

|          | 11: Positive H                              | •            |               |                | 1 - 1          |                |         |              |  |

| Bits1-0: | CP0HYN1-0:                                  |              |               | Hysteresis Co  | ontrol Bits.   |                |         |              |  |

|          | 00: Negative                                | •            |               |                |                |                |         |              |  |

|          | 01: Negative                                | •            |               |                |                |                |         |              |  |

|          | 10: Negative                                |              |               |                |                |                |         |              |  |

|          | 11: Negative l                              | Hysteresis = | 20 mV.        |                |                |                |         |              |  |

|          |                                             |              |               |                |                |                |         |              |  |

# Figure 7.4. CPT0CN: Comparator0 Control Register

| R/W   | R/W                                                 | R/W                                                                                 | R/W           | R/W           | R/W           | R/W          | R/W     | Reset Value          |  |  |  |

|-------|-----------------------------------------------------|-------------------------------------------------------------------------------------|---------------|---------------|---------------|--------------|---------|----------------------|--|--|--|

| ET3   | ECP1                                                | ECP0                                                                                | EPCA0         | EADC0         | EWADC0        | EUSB0        | ESMB0   | 00000000             |  |  |  |

| Bit7  | Bit6                                                | Bit5                                                                                | Bit4          | Bit3          | Bit2          | Bit1         | Bit0    | SFR Address:<br>0xE6 |  |  |  |

| Bit7: | ET3: Enable Timer 3 Interrupt.                      |                                                                                     |               |               |               |              |         |                      |  |  |  |

|       | This bit sets the masking of the Timer 3 interrupt. |                                                                                     |               |               |               |              |         |                      |  |  |  |

|       | 0: Disable Timer 3 interrupts.                      |                                                                                     |               |               |               |              |         |                      |  |  |  |

|       | 1: Enable inte                                      |                                                                                     |               |               | or TF3H flag  | gs.          |         |                      |  |  |  |

| Bit6: | ECP1: Enable                                        |                                                                                     |               |               |               |              |         |                      |  |  |  |

|       | This bit sets t                                     | he masking o                                                                        | of the CP1 in | terrupt.      |               |              |         |                      |  |  |  |

|       | 0: Disable CP                                       |                                                                                     |               |               |               |              |         |                      |  |  |  |

|       | 1: Enable inte                                      | errupt reques                                                                       | ts generated  | by the CP1R   | LIF or CP1FIE | F flags.     |         |                      |  |  |  |

| Bit5: | ECP0: Enable                                        | e Comparato                                                                         | r0 (CP0) Inte | errupt.       |               |              |         |                      |  |  |  |

|       | This bit sets t                                     | he masking o                                                                        | of the CP0 in | terrupt.      |               |              |         |                      |  |  |  |

|       | 0: Disable CP                                       | 0 interrupts.                                                                       |               |               |               |              |         |                      |  |  |  |

|       | 1: Enable inte                                      | errupt reques                                                                       | ts generated  | by the CP0R   | IF or CP0FIE  | F flags.     |         |                      |  |  |  |

| Bit4: | EPCA0: Enab                                         | ole Program                                                                         | nable Counte  | er Array (PC  | A0) Interrupt |              |         |                      |  |  |  |

|       | This bit sets t                                     | he masking o                                                                        | of the PCA0   | interrupts.   |               |              |         |                      |  |  |  |

|       | 0: Disable all                                      | PCA0 interr                                                                         | upts.         |               |               |              |         |                      |  |  |  |

|       | 1: Enable inte                                      | errupt reques                                                                       | ts generated  | by PCA0.      |               |              |         |                      |  |  |  |

| Bit3: | EADC0: Enal                                         | ble ADC0 C                                                                          | onversion Co  | omplete Inter | rrupt.        |              |         |                      |  |  |  |

|       | This bit sets t                                     | he masking o                                                                        | of the ADC0   | Conversion    | Complete int  | errupt.      |         |                      |  |  |  |

|       | 0: Disable AI                                       | DC0 Convers                                                                         | sion Complet  | e interrupt.  | -             | -            |         |                      |  |  |  |

|       | 1: Enable inte                                      | errupt reques                                                                       | ts generated  | by the AD0I   | NT flag.      |              |         |                      |  |  |  |

| Bit2: | EWADC0: Er                                          | nable Windo                                                                         | w Compariso   | on ADC0 Int   | errupt.       |              |         |                      |  |  |  |

|       | This bit sets t                                     |                                                                                     |               |               |               | pt.          |         |                      |  |  |  |

|       | 0: Disable AI                                       |                                                                                     |               |               | -             | •            |         |                      |  |  |  |

|       | 1: Enable inte                                      |                                                                                     |               |               | indow Comp    | are flag (AI | OWINT). |                      |  |  |  |

| Bit1: | EUSB0: Enab                                         |                                                                                     | -             | 5             | 1             | Ũ            | ,       |                      |  |  |  |

|       |                                                     |                                                                                     | 1             | interrupt.    |               |              |         |                      |  |  |  |

|       |                                                     | This bit sets the masking of the USB0 interrupt.<br>0: Disable all USB0 interrupts. |               |               |               |              |         |                      |  |  |  |

|       | 1: Enable inte                                      |                                                                                     |               | by USB0.      |               |              |         |                      |  |  |  |

| Bit0: | ESMB0: Enal                                         |                                                                                     |               |               |               |              |         |                      |  |  |  |

|       | This bit sets t                                     |                                                                                     | · · ·         | -             |               |              |         |                      |  |  |  |

|       | 0: Disable all                                      | 0                                                                                   |               | 1             |               |              |         |                      |  |  |  |

|       | 1: Enable inte                                      |                                                                                     |               | by CMDO       |               |              |         |                      |  |  |  |

# Figure 9.11. EIE1: Extended Interrupt Enable 1

#### 11.2. Non-volatile Data Storage

The FLASH memory can be used for non-volatile data storage as well as program code. This allows data such as calibration coefficients to be calculated and stored at run time. Data is written using the MOVX write instruction and read using the MOVC instruction. Note: MOVX read instructions always target XRAM.

#### **11.3.** Security Options

The CIP-51 provides security options to protect the FLASH memory from inadvertent modification by software as well as to prevent the viewing of proprietary program code and constants. The Program Store Write Enable (bit PSWE in register PSCTL) and the Program Store Erase Enable (bit PSEE in register PSCTL) bits protect the FLASH memory from accidental modification by software. PSWE must be explicitly set to '1' before software can modify the FLASH memory; both PSWE and PSEE must be set to '1' before software can erase FLASH memory. Additional security features prevent proprietary program code and data constants from being read or altered across the C2 interface.

A Security Lock Byte located at the last byte of FLASH user space offers protection of the FLASH program memory from access (reads, writes, or erases) by unprotected code or the C2 interface. The FLASH security mechanism allows the user to lock n 512-byte FLASH pages, starting at page 0 (addresses 0x0000 to 0x01FF), where n is the 1's compliment number represented by the Security Lock Byte. See example below.

| Security Lock Byte: | 11111101b |

|---------------------|-----------|

| 1's Compliment:     | 00000010b |

|                     | •         |

| FLASH pages locked: | 2         |

#### Important Notes About the FLASH Security:

1. Clearing any bit of the Lock Byte to '0' will lock the FLASH page containing the Lock Byte (in addition to the selected pages).

2. Locked pages cannot be read, written, or erased via the C2 interface.

3. Locked pages cannot be read, written, or erased by user firmware executing from unlocked memory space.

4. User firmware executing in a locked page may read and write FLASH memory in any locked or unlocked page excluding the reserved area.

5. User firmware executing in a locked page may erase FLASH memory in any locked or unlocked page excluding the reserved area and the page containing the Lock Byte.

6. Locked pages can only be unlocked through the C2 interface with a C2 Device Erase command.

7. If a user firmware FLASH access attempt is denied (per restrictions #3, #4, and #5 above), a FLASH Error system reset will be generated.

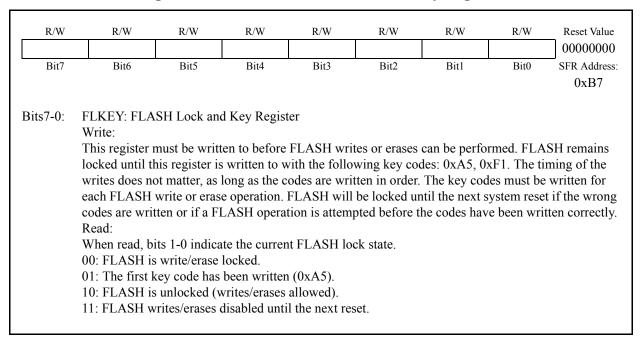

## Figure 11.3. FLKEY: FLASH Lock and Key Register

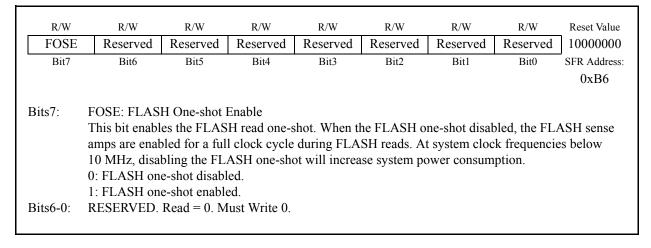

#### Figure 11.4. FLSCL: FLASH Scale Register

# Notes

# **12. EXTERNAL RAM**

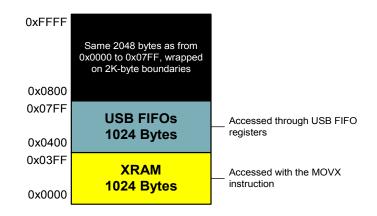

The C8051F320/1 devices include 2048 bytes of on-chip XRAM. This XRAM space is split into user RAM (addresses 0x0000 - 0x03FF) and USB0 FIFO space (addresses 0x0400 - 0x07FF).

## Figure 12.1. External Ram Memory Map

### 12.1. Accessing User XRAM

XRAM can be accessed using the external move instruction (MOVX) and the data pointer (DPTR), or using MOVX indirect addressing mode. If the MOVX instruction is used with an 8-bit address operand (such as @R1), then the high byte of the 16-bit address is provided by the External Memory Interface Control Register (EMIOCN as shown in Figure 12.3). Note: the MOVX instruction is also used for writes to the FLASH memory. See Section "11. FLASH Memory" on page 107 for details. The MOVX instruction accesses XRAM by default.

For any of the addressing modes the upper 5 bits of the 16-bit external data memory address word are "don't cares". As a result, the 2048-byte RAM is mapped modulo style over the entire 64k external data memory address range. For example, the XRAM byte at address 0x0000 is also at address 0x0800, 0x1000, 0x1800, 0x2000, etc.

Important Note: The upper 1k of the 2k XRAM functions as USB FIFO space. See Section 12.2 for details on accessing this memory space.

#### 14.2. Port I/O Initialization

Port I/O initialization consists of the following steps:

- Step 1. Select the input mode (analog or digital) for all Port pins, using the Port Input Mode register (PnMDIN).

- Step 2. Select the output mode (open-drain or push-pull) for all Port pins, using the Port Output Mode register (PnMDOUT).

- Step 3. Select any pins to be skipped by the I/O Crossbar using the Port Skip registers (PnSKIP).

- Step 4. Assign Port pins to desired peripherals (XBR0, XBR1).

- Step 5. Enable the Crossbar (XBARE =  $^{1}$ ).

All Port pins must be configured as either analog or digital inputs. Any pins to be used as Comparator or ADC inputs should be configured as an analog inputs. When a pin is configured as an analog input, its weak pull-up, digital driver, and digital receiver are disabled. This process saves power and reduces noise on the analog input. Pins configured as digital inputs may still be used by analog peripherals; however this practice is not recommended. To configure a Port pin for digital input, write '0' to the corresponding bit in register PnMDOUT, and write '1' to the corresponding Port latch (register Pn).

Additionally, all analog input pins should be configured to be skipped by the Crossbar (accomplished by setting the associated bits in PnSKIP). Port input mode is set in the PnMDIN register, where a '1' indicates a digital input, and a '0' indicates an analog input. All pins default to digital inputs on reset. See Figure 14.8 for the PnMDIN register details.

The output driver characteristics of the I/O pins are defined using the Port Output Mode registers (PnMDOUT). Each Port Output driver can be configured as either open drain or push-pull. This selection is required even for the digital resources selected in the XBRn registers, and is not automatic. The only exception to this is the SMBus (SDA, SCL) pins, which are configured as open-drain regardless of the PnMDOUT settings. When the WEAKPUD bit in XBR1 is '0', a weak pull-up is enabled for all Port I/O configured as open-drain. WEAKPUD does not affect the push-pull Port I/O. Furthermore, the weak pull-up is turned off on an output that is driving a '0' to avoid unnecessary power dissipation.

Registers XBR0 and XBR1 must be loaded with the appropriate values to select the digital I/O functions required by the design. Setting the XBARE bit in XBR1 to '1' enables the Crossbar. Until the Crossbar is enabled, the external pins remain as standard Port I/O (in input mode), regardless of the XBRn Register settings. For given XBRn Register settings, one can determine the I/O pin-out using the Priority Decode Table; as an alternative, the Configuration Wizard utility of the Silicon Labs IDE software will determine the Port I/O pin-assignments based on the XBRn Register settings.

**Important Note:** The Crossbar must be enabled to use Ports P0, P1, and P2.0-P2.3 as standard Port I/O in output mode. These Port output drivers are disabled while the Crossbar is disabled. P2.4-P2.7 and P3.0 always function as standard GPIO.

| R/W      | R/W                                                             | R/W                   | R/W           | R/W           | R/W            | R/W            | R/W         | Reset Value 00000000 |

|----------|-----------------------------------------------------------------|-----------------------|---------------|---------------|----------------|----------------|-------------|----------------------|

| Bit7     | Bit6                                                            | Bit5                  | Bit4          | Bit3          | Bit2           | Bit1           | Bit0        | SFR Address:<br>0xA4 |

| Bits7-0: | Output Config<br>P0MDIN is lo<br>0: Correspond<br>1: Correspond | gic 0.<br>ing P0.n Ou | tput is open- | drain.        | ely): ignored  | if correspond  | ding bit in | register             |

|          | (Note: When S<br>of P0MDOUT                                     |                       | L appear on   | any of the Po | rt I/O, each a | are open-drain | n regardles | s of the value       |

# Figure 14.9. POMDOUT: Port0 Output Mode Register

Figure 14.10. POSKIP: Port0 Skip Register

| R/W      | R/W                                                                                               | R/W                                                             | R/W                                                            | R/W                                                     | R/W                    | R/W  | R/W  | Reset Value 00000000 |

|----------|---------------------------------------------------------------------------------------------------|-----------------------------------------------------------------|----------------------------------------------------------------|---------------------------------------------------------|------------------------|------|------|----------------------|

| Bit7     | Bit6                                                                                              | Bit5                                                            | Bit4                                                           | Bit3                                                    | Bit2                   | Bit1 | Bit0 | SFR Address:<br>0xD4 |

| Bits7-0: | P0SKIP[7:0]:<br>These bits sele<br>ADC or Comp<br>input) should<br>0: Correspond<br>1: Correspond | ect Port pins<br>barator) or u<br>be skipped b<br>ling P0.n pin | to be skipped<br>sed as specia<br>y the Crossb<br>is not skipp | d by the Cros<br>l functions (<br>par.<br>ed by the Cro | VREF input,<br>ossbar. | 1    |      | <b>U</b> 1 \         |

# C8051F320/1

| R/W  | R/W                                                             | R/W                   | R/W           | R/W    | R/W           | R/W          | R/W         | Reset Value |

|------|-----------------------------------------------------------------|-----------------------|---------------|--------|---------------|--------------|-------------|-------------|

|      |                                                                 |                       |               |        |               |              |             | 00000000    |

| Bit7 | Bit6                                                            | Bit5                  | Bit4          | Bit3   | Bit2          | Bit1         | Bit0        | SFR Address |

|      |                                                                 |                       |               |        |               |              |             | 0xA5        |

|      | Output Config<br>P1MDIN is lo<br>0: Correspond<br>1: Correspond | gic 0.<br>ing P1.n Ou | tput is open- | drain. | ely): ignored | if correspon | ding bit in | register    |

# Figure 14.13. P1MDOUT: Port1 Output Mode Register

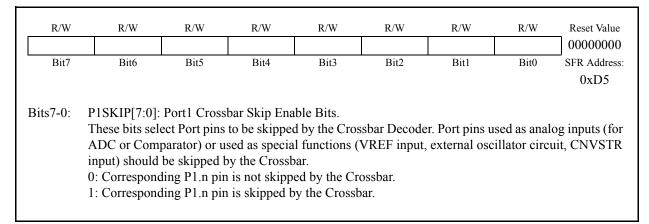

# Figure 14.14. P1SKIP: Port1 Skip Register

| R/W  | R/W                                                                                 | R/W                        | R/W                 | R/W            | R/W                        | R/W             | R/W           | Reset Value    |  |  |  |  |  |  |

|------|-------------------------------------------------------------------------------------|----------------------------|---------------------|----------------|----------------------------|-----------------|---------------|----------------|--|--|--|--|--|--|

|      |                                                                                     |                            | USB                 | 0DAT           |                            |                 |               | 00000000       |  |  |  |  |  |  |

| Bit7 | Bit6                                                                                | Bit5                       | Bit4                | Bit3           | Bit2                       | Bit2 Bit1       | Bit0          | SFR Address:   |  |  |  |  |  |  |

|      |                                                                                     |                            |                     |                |                            |                 |               | 0x97           |  |  |  |  |  |  |

|      | This SFR is u                                                                       | sed to indire              | ctly read and       | l write USB(   | ) registers.               |                 |               |                |  |  |  |  |  |  |

|      | Write Procedu                                                                       | ire:                       |                     |                |                            |                 |               |                |  |  |  |  |  |  |

|      | 1. Poll for BU                                                                      | JSY (USB0/                 | ADR.7) => '         | 0'.            |                            |                 |               |                |  |  |  |  |  |  |

|      | 2. Load the ta                                                                      | arget USB0 1               | egister addro       | ess into the U | JSBADDR b                  | oits in registe | r USB0AD      | R.             |  |  |  |  |  |  |

|      | 3. Write data                                                                       | to USB0DA                  | Т.                  |                |                            |                 |               |                |  |  |  |  |  |  |

|      | 4. Repeat (St                                                                       | ep 2 may be                | skipped whe         | en writing to  | the same US                | B0 register).   |               |                |  |  |  |  |  |  |

|      | Read Procedu                                                                        | re:                        |                     |                |                            |                 |               |                |  |  |  |  |  |  |

|      | 1. Poll for BUSY (USB0ADR.7) $=>$ '0'.                                              |                            |                     |                |                            |                 |               |                |  |  |  |  |  |  |

|      | 2. Load the target USB0 register address into the USBADDR bits in register USB0ADR. |                            |                     |                |                            |                 |               |                |  |  |  |  |  |  |

|      |                                                                                     |                            | 0                   |                | R (steps 2 and             | 13 can be pe    | rformed in    | the same write |  |  |  |  |  |  |

|      | 4. Poll for BUSY (USB0ADR.7) $\Rightarrow$ '0'.                                     |                            |                     |                |                            |                 |               |                |  |  |  |  |  |  |

|      | 4. Poll for BU                                                                      |                            | ,                   |                | 5. Read data from USB0DAT. |                 |               |                |  |  |  |  |  |  |

|      | 5. Read data                                                                        | from USB0I                 | DAT.                |                |                            |                 |               |                |  |  |  |  |  |  |

|      | <ol> <li>Read data</li> <li>Repeat from</li> </ol>                                  | from USB0I<br>m Step 2 (St | DAT.<br>ep 2 may be |                | -                          | e same USB(     | ) register; S | Step 3 may be  |  |  |  |  |  |  |

# Figure 15.5. USB0DAT: USB0 Data Register

# Figure 15.6. INDEX: USB0 Endpoint Index (USB Register)

| R        | R<br>-                                                 | R<br>_                      | R<br>-                                     | R/W         | Reset Value 00000000 |                |             |                     |

|----------|--------------------------------------------------------|-----------------------------|--------------------------------------------|-------------|----------------------|----------------|-------------|---------------------|

| Bit7     | Bit6                                                   | Bit5                        | Bit4                                       | Bit3        | Bit2                 | Bit1           | Bit0        | USB Address<br>0x0E |

| Bits7-4: | Unused. Read                                           | = 0000b; W                  | /rite = don't ca                           | are         |                      |                |             |                     |

| Bits3-0: | EPSEL: Endpo<br>These bits sele                        | oint Select<br>ect which en | ndpoint is targe                           | eted when i | ndexed USB           | 0 registers a  | e accessed  |                     |

| Bits3-0: | EPSEL: Endpo<br>These bits sele                        | oint Select<br>ect which en | ndpoint is targe<br>rget Endpoin           | eted when i | ndexed USB           | 0 registers ar | e accessed  |                     |

| Bits3-0: | EPSEL: Endpo<br>These bits sele<br>INDEX<br>0x0        | oint Select<br>ect which en | ndpoint is targe                           | eted when i | ndexed USB           | 0 registers ar | e accessed  |                     |

| Bits3-0: | EPSEL: Endpo<br>These bits sele                        | oint Select<br>ect which en | ndpoint is targe<br>rget Endpoin           | eted when i | ndexed USB           | 0 registers ar | e accessed  |                     |

| Bits3-0: | EPSEL: Endpo<br>These bits sele<br>INDEX<br>0x0<br>0x1 | oint Select<br>ect which en | ndpoint is targe<br>rget Endpoin<br>0<br>1 | eted when i | ndexed USB           | 0 registers ar | re accessed |                     |

## 15.11. Configuring Endpoints1-3

Endpoints1-3 are configured and controlled through their own sets of the following control/status registers: IN registers EINCSRL and EINCSRH, and OUT registers EOUTCSRL and EOUTCSRH. Only one set of endpoint control/status registers is mapped into the USB register address space at a time, defined by the contents of the INDEX register (Figure 15.6).

Endpoints1-3 can be configured as IN, OUT, or both IN/OUT (Split Mode) as described in Section 15.5.1. The endpoint mode (Split/Normal) is selected via the SPLIT bit in register EINCSRH.

When SPLIT = '1', the corresponding endpoint FIFO is split, and both IN and OUT pipes are available.

When SPLIT = '0', the corresponding endpoint functions as either IN or OUT; the endpoint direction is selected by the DIRSEL bit in register EINCSRH.

### 15.12. Controlling Endpoints1-3 IN

Endpoints1-3 IN are managed via USB registers EINCSRL and EINCSRH. All IN endpoints can be used for Interrupt, Bulk, or Isochronous transfers. Isochronous (ISO) mode is enabled by writing '1' to the ISO bit in register EINCSRH. Bulk and Interrupt transfers are handled identically by hardware.

An Endpoint1-3 IN interrupt is generated by any of the following conditions:

- 1. An IN packet is successfully transferred to the host.

- 2. Software writes '1' to the FLUSH bit (EINCSRL.3) when the target FIFO is not empty.

- 3. Hardware generates a STALL condition.

#### 15.12.1.Endpoints1-3 IN Interrupt or Bulk Mode

When the ISO bit (EINCSRH.6) = '0' the target endpoint operates in Bulk or Interrupt Mode. Once an endpoint has been configured to operate in Bulk/Interrupt IN mode (typically following an Endpoint0 SET\_INTERFACE command), firmware should load an IN packet into the endpoint IN FIFO and set the INPRDY bit (EINCSRL.0). Upon reception of an IN token, hardware will transmit the data, clear the INPRDY bit, and generate an interrupt.

Writing '1' to INPRDY without writing any data to the endpoint FIFO will cause a zero-length packet to be transmitted upon reception of the next IN token.

A Bulk or Interrupt pipe can be shut down (or Halted) by writing '1' to the SDSTL bit (EINCSRL.4). While SDSTL = '1', hardware will respond to all IN requests with a STALL condition. Each time hardware generates a STALL condition, an interrupt will be generated and the STSTL bit (EINCSRL.5) set to '1'. The STSTL bit must be reset to '0' by firmware.

Hardware will automatically reset INPRDY to '0' when a packet slot is open in the endpoint FIFO. Note that if double buffering is enabled for the target endpoint, it is possible for firmware to load two packets into the IN FIFO at a time. In this case, hardware will reset INPRDY to '0' immediately after firmware loads the first packet into the FIFO and sets INPRDY to '1'. An interrupt will not be generated in this case; an interrupt will only be generated when a data packet is transmitted.

When firmware writes '1' to the FCDT bit (EINCSRH.3), the data toggle for each IN packet will be toggled continuously, regardless of the handshake received from the host. This feature is typically used by Interrupt endpoints functioning as rate feedback communication for Isochronous endpoints. When FCDT = '0', the data toggle bit will only be toggled when an ACK is sent from the host in response to an IN packet.

| Bit     | Set by Hardware When:                                                                                                | Cleared by Hardware When:                                    |

|---------|----------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------|

| MASTER  | • A START is generated.                                                                                              | • A STOP is generated.                                       |

| WIAGTER |                                                                                                                      | • Arbitration is lost.                                       |

|         | START is generated.                                                                                                  | • A START is detected.                                       |

| TXMODE  | • SMB0DAT is written before the start of an SMBus                                                                    | Arbitration is lost.                                         |

| TAMODE  | frame.                                                                                                               | • SMB0DAT is not written before the start of an SMBus frame. |

| STA     | • A START followed by an address byte is received.                                                                   | <ul> <li>Must be cleared by software.</li> </ul>             |

| STO     | <ul><li>A STOP is detected while addressed as a slave.</li><li>Arbitration is lost due to a detected STOP.</li></ul> | • A pending STOP is generated.                               |

| ACKRQ   | • A byte has been received and an ACK response value is needed.                                                      | After each ACK cycle.                                        |

|         | • A repeated START is detected as a MASTER when                                                                      | • Each time SI is cleared.                                   |

|         | STA is low (unwanted repeated START).                                                                                |                                                              |

| ARBLOST | • SCL is sensed low while attempting to generate a                                                                   |                                                              |

|         | STOP or repeated START condition.                                                                                    |                                                              |

|         | • SDA is sensed low while transmitting a '1'                                                                         |                                                              |

|         | (excluding ACK bits).                                                                                                |                                                              |

| ACK     | • The incoming ACK value is low (ACKNOWL-<br>EDGE).                                                                  | • The incoming ACK value is high (NOT ACKNOWLEDGE).          |

|         | • A START has been generated.                                                                                        | • Must be cleared by software.                               |

|         | Lost arbitration.                                                                                                    |                                                              |

|         | • A byte has been transmitted and an ACK/NACK                                                                        |                                                              |

| SI      | received.                                                                                                            |                                                              |

| 51      | • A byte has been received.                                                                                          |                                                              |

|         | • A START or repeated START followed by a slave                                                                      |                                                              |

|         | address $+ R/W$ has been received.                                                                                   |                                                              |

|         | • A STOP has been received.                                                                                          |                                                              |

# Table 16.3. Sources for Hardware Changes to SMB0CN

# C8051F320/1

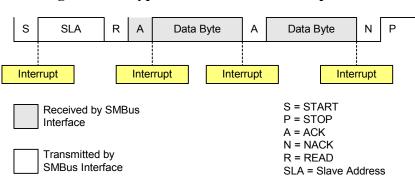

### 16.5.2. Master Receiver Mode

Serial data is received on SDA while the serial clock is output on SCL. The SMBus interface generates the START condition and transmits the first byte containing the address of the target slave and the data direction bit. In this case the data direction bit (R/W) will be logic 1 (READ). Serial data is then received from the slave on SDA while the SMBus outputs the serial clock. The slave transmits one or more bytes of serial data. After each byte is received, ACKRQ is set to '1' and an interrupt is generated. Software must write the ACK bit (SMB0CN.1) to define the outgoing acknowledge value (Note: writing a '1' to the ACK bit generates an ACK; writing a '0' generates a NACK). Software should write a '0' to the ACK bit after the last byte is received, to transmit a NACK. The interface exits Master Receiver Mode after the STO bit is set and a STOP is generated. Note that the interface will switch to Master Transmitter Mode if SMB0DAT is written while an active Master Receiver. Figure 16.9 shows a typical Master Receiver sequence. Two received data bytes are shown, though any number of bytes may be received. Notice that the 'data byte transferred' interrupts occur **before** the ACK cycle in this mode.

Figure 16.9. Typical Master Receiver Sequence

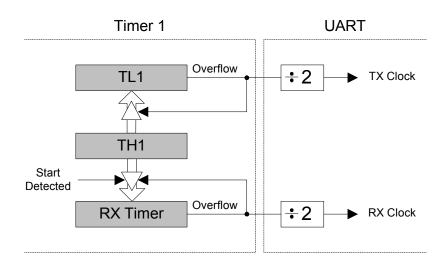

## 17.1. Enhanced Baud Rate Generation

The UART0 baud rate is generated by Timer 1 in 8-bit auto-reload mode. The TX clock is generated by TL1; the RX clock is generated by a copy of TL1 (shown as RX Timer in Figure 17.2), which is not user-accessible. Both TX and RX Timer overflows are divided by two to generate the TX and RX baud rates. The RX Timer runs when Timer 1 is enabled, and uses the same reload value (TH1). However, an RX Timer reload is forced when a START condition is detected on the RX pin. This allows a receive to begin any time a START is detected, independent of the TX Timer state.

Figure 17.2. UARTO Baud Rate Logic

Timer 1 should be configured for Mode 2, 8-bit auto-reload (see Section "19.1.3. Mode 2: 8-bit Counter/Timer with Auto-Reload" on page 219). The Timer 1 reload value should be set so that overflows will occur at two times the desired UART baud rate frequency. Note that Timer 1 may be clocked by one of six sources: SYSCLK, SYSCLK / 4, SYSCLK / 12, SYSCLK / 48, the external oscillator clock / 8, or an external input T1. For any given Timer 1 clock source, the UART0 baud rate is determined by Equation 17.1.

#### **Equation 17.1. UARTO Baud Rate**

$$UartBaudRate = \frac{T1_{CLK}}{(256 - T1H)} \times \frac{1}{2}$$

Where  $TI_{CLK}$  is the frequency of the clock supplied to Timer 1, and TIH is the high byte of Timer 1 (reload value). Timer 1 clock frequency is selected as described in Section "19. Timers" on page 217. A quick reference for typical baud rates and system clock frequencies is given in Table 17.1 through Table 17.6. Note that the internal oscillator may still generate the system clock when the external oscillator is driving Timer 1.

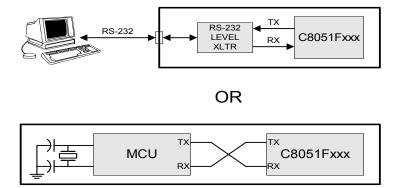

### **17.2.** Operational Modes

UART0 provides standard asynchronous, full duplex communication. The UART mode (8-bit or 9-bit) is selected by the S0MODE bit (SCON0.7). Typical UART connection options are shown below.

Figure 17.3. UART Interconnect Diagram

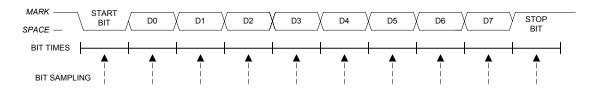

### 17.2.1. 8-Bit UART

8-Bit UART mode uses a total of 10 bits per data byte: one start bit, eight data bits (LSB first), and one stop bit. Data are transmitted LSB first from the TX0 pin and received at the RX0 pin. On receive, the eight data bits are stored in SBUF0 and the stop bit goes into RB80 (SCON0.2).

Data transmission begins when software writes a data byte to the SBUF0 register. The TI0 Transmit Interrupt Flag (SCON0.1) is set at the end of the transmission (the beginning of the stop-bit time). Data reception can begin any time after the REN0 Receive Enable bit (SCON0.4) is set to logic 1. After the stop bit is received, the data byte will be loaded into the SBUF0 receive register if the following conditions are met: RI0 must be logic 0, and if MCE0 is logic 1, the stop bit must be logic 1. In the event of a receive data overrun, the first received 8 bits are latched into the SBUF0 receive register and the following overrun data bits are lost.

If these conditions are met, the eight bits of data is stored in SBUF0, the stop bit is stored in RB80 and the RI0 flag is set. If these conditions are not met, SBUF0 and RB80 will not be loaded and the RI0 flag will not be set. An interrupt will occur if enabled when either TI0 or RI0 is set.

Figure 17.4. 8-Bit UART Timing Diagram

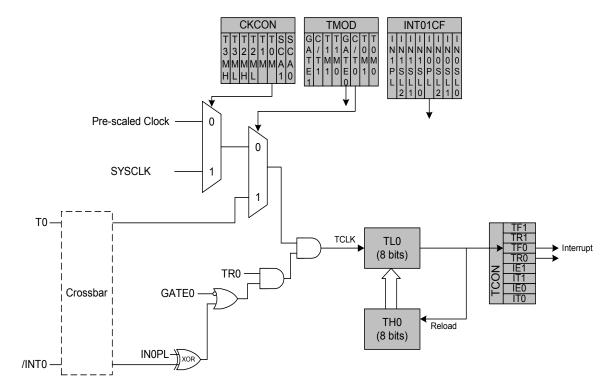

#### 19.1.3. Mode 2: 8-bit Counter/Timer with Auto-Reload

Mode 2 configures Timer 0 and Timer 1 to operate as 8-bit counter/timers with automatic reload of the start value. TL0 holds the count and TH0 holds the reload value. When the counter in TL0 overflows from all ones to 0x00, the timer overflow flag TF0 (TCON.5) is set and the counter in TL0 is reloaded from TH0. If Timer 0 interrupts are enabled, an interrupt will occur when the TF0 flag is set. The reload value in TH0 is not changed. TL0 must be initialized to the desired value before enabling the timer for the first count to be correct. When in Mode 2, Timer 1 operates identically to Timer 0.

Both counter/timers are enabled and configured in Mode 2 in the same manner as Mode 0. Setting the TR0 bit (TCON.4) enables the timer when either GATE0 (TMOD.3) is logic 0 or when the input signal /INT0 is active as defined by bit IN0PL in register INT01CF (see Section "8.3.2. External Interrupts" on page 59 for details on the external input signals /INT0 and /INT1).

Figure 19.2. T0 Mode 2 Block Diagram

# C8051F320/1

|   |                                                                                                                                      | •    | 8    |      | e e e e e e e e e e e e e e e e e e e |      |      |      |                         |  |

|---|--------------------------------------------------------------------------------------------------------------------------------------|------|------|------|---------------------------------------|------|------|------|-------------------------|--|

|   | R/W                                                                                                                                  | R/W  | R/W  | R/W  | R/W                                   | R/W  | R/W  | R/W  | Reset Value<br>00000000 |  |

|   | Bit7                                                                                                                                 | Bit6 | Bit5 | Bit4 | Bit3                                  | Bit2 | Bit1 | Bit0 | SFR Address:<br>0xF9    |  |

| F | 0xF9<br>Bits 7-0: PCA0L: PCA Counter/Timer Low Byte.<br>The PCA0L register holds the low byte (LSB) of the 16-bit PCA Counter/Timer. |      |      |      |                                       |      |      |      |                         |  |

## Figure 20.14. PCA0L: PCA Counter/Timer Low Byte

# Figure 20.15. PCA0H: PCA Counter/Timer High Byte

| R/W       | R/W                                                                                                                  | R/W  | R/W  | R/W  | R/W  | R/W  | R/W  | Reset Value 0000000  |

|-----------|----------------------------------------------------------------------------------------------------------------------|------|------|------|------|------|------|----------------------|

| Bit7      | Bit6                                                                                                                 | Bit5 | Bit4 | Bit3 | Bit2 | Bit1 | Bit0 | SFR Address:<br>0xFA |

| Bits 7-0: | PCA0H: PCA Counter/Timer High Byte.<br>The PCA0H register holds the high byte (MSB) of the 16-bit PCA Counter/Timer. |      |      |      |      |      |      |                      |