Welcome to E-XFL.COM

### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

### Details

E·XFI

| Product Status             | Active                                                                           |

|----------------------------|----------------------------------------------------------------------------------|

| Core Processor             | MIPS32® M-Class                                                                  |

| Core Size                  | 32-Bit Single-Core                                                               |

| Speed                      | 180MHz                                                                           |

| Connectivity               | Ethernet, I <sup>2</sup> C, PMP, SPI, SQI, UART/USART, USB OTG                   |

| Peripherals                | Brown-out Detect/Reset, DMA, I <sup>2</sup> S, POR, PWM, WDT                     |

| Number of I/O              | 46                                                                               |

| Program Memory Size        | 512KB (512K x 8)                                                                 |

| Program Memory Type        | FLASH                                                                            |

| EEPROM Size                |                                                                                  |

| RAM Size                   | 128K x 8                                                                         |

| Voltage - Supply (Vcc/Vdd) | 2.1V ~ 3.6V                                                                      |

| Data Converters            | A/D 24x12b                                                                       |

| Oscillator Type            | Internal                                                                         |

| Operating Temperature      | -40°C ~ 125°C                                                                    |

| Mounting Type              | Surface Mount                                                                    |

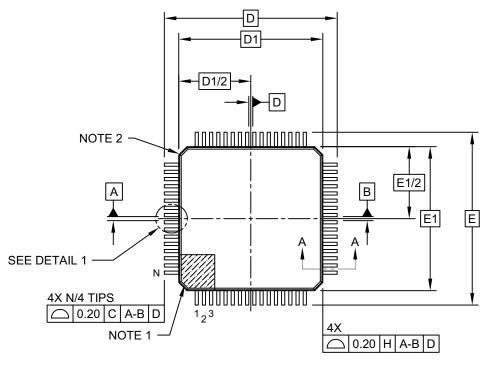

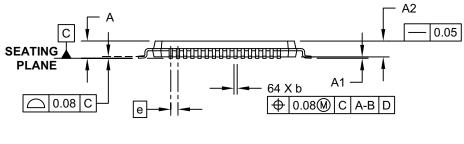

| Package / Case             | 64-TQFP                                                                          |

| Supplier Device Package    | 64-TQFP (10x10)                                                                  |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic32mz0512efe064-e-pt |

|                            |                                                                                  |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |  |  |  |  |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|--|--|--|--|

| 04.04        | W-0               | W-0               | W-0               | W-0               | W-0               | W-0               | W-0              | W-0              |  |  |  |  |

| 31:24        | NVMKEY<31:24>     |                   |                   |                   |                   |                   |                  |                  |  |  |  |  |

| 00.40        | W-0               | W-0               | W-0               | W-0               | W-0               | W-0               | W-0              | W-0              |  |  |  |  |

| 23:16        | NVMKEY<23:16>     |                   |                   |                   |                   |                   |                  |                  |  |  |  |  |

| 45.0         | W-0               | W-0               | W-0               | W-0               | W-0               | W-0               | W-0              | W-0              |  |  |  |  |

| 15:8         |                   | •                 |                   | NVMK              | EY<15:8>          |                   |                  |                  |  |  |  |  |

| 7.0          | W-0               | W-0               | W-0               | W-0               | W-0               | W-0               | W-0              | W-0              |  |  |  |  |

| 7:0          | NVMKEY<7:0>       |                   |                   |                   |                   |                   |                  |                  |  |  |  |  |

### REGISTER 5-3: NVMKEY: PROGRAMMING UNLOCK REGISTER

# Legend:

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, re | ead as '0'         |

|-------------------|------------------|---------------------------|--------------------|

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared      | x = Bit is unknown |

bit 31-0 **NVMKEY<31:0>:** Unlock Register bits These bits are write-only, and read as '0' on any read

Note: This register is used as part of the unlock sequence to prevent inadvertent writes to the PFM.

# REGISTER 5-4: NVMADDR: FLASH ADDRESS REGISTER

| Bit<br>Range | Bit<br>31/23/15/7             | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3       | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |  |  |  |  |

|--------------|-------------------------------|-------------------|-------------------|-------------------|-------------------------|-------------------|------------------|------------------|--|--|--|--|

| 04.04        | R/W-0                         | R/W-0             | R/W-0             | R/W-0             | R/W-0                   | R/W-0             | R/W-0            | R/W-0            |  |  |  |  |

| 31:24        | NVMADDR<31:24> <sup>(1)</sup> |                   |                   |                   |                         |                   |                  |                  |  |  |  |  |

| 00.40        | R/W-0                         | R/W-0             | R/W-0             | R/W-0             | R/W-0                   | R/W-0             | R/W-0            | R/W-0            |  |  |  |  |

| 23:16        | NVMADDR<23:16> <sup>(1)</sup> |                   |                   |                   |                         |                   |                  |                  |  |  |  |  |

| 45.0         | R/W-0                         | R/W-0             | R/W-0             | R/W-0             | R/W-0                   | R/W-0             | R/W-0            | R/W-0            |  |  |  |  |

| 15:8         |                               | •                 |                   | NVMADE            | DR<15:8> <sup>(1)</sup> |                   |                  |                  |  |  |  |  |

| 7.0          | R/W-0                         | R/W-0             | R/W-0             | R/W-0             | R/W-0                   | R/W-0             | R/W-0            | R/W-0            |  |  |  |  |

| 7:0          | NVMADDR<7:0> <sup>(1)</sup>   |                   |                   |                   |                         |                   |                  |                  |  |  |  |  |

| Legend:           |                  |                           |                    |

|-------------------|------------------|---------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, re | ead as '0'         |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared      | x = Bit is unknown |

### bit 31-0 NVMADDR<31:0>: Flash Address bits<sup>(1)</sup>

| NVMOP<3:0><br>Selection | Flash Address Bits (NVMADDR<31:0>)                                                                                             |  |  |  |  |  |

|-------------------------|--------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|

| Page Erase              | Address identifies the page to erase (NVMADDR<13:0> are ignored).                                                              |  |  |  |  |  |

| Row Program             | Address identifies the row to program (NVMADDR<10:0> are ignored).                                                             |  |  |  |  |  |

| Word Program            | Address identifies the word to program (NVMADDR<1:0> are ignored).                                                             |  |  |  |  |  |

| Quad Word Program       | Address identifies the quad word (128-bit) to program (NVMADDR<3:0> bits are ignored).                                         |  |  |  |  |  |

|                         | r NVMOP<3:0> bit settings, the Flash address is ignored. See the NVMCON egister 5-1) for additional information on these bits. |  |  |  |  |  |

Note: The bits in this register are only reset by a Power-on Reset (POR) and are not affected by other reset sources.

#### **TABLE 7-3**: **INTERRUPT REGISTER MAP (CONTINUED)**

| ress<br>f)                  | <b>b</b> -a                     | e         |               |               |              |          |                         |                         |                       | Bi                    | ts                    |                        |            |                        |            |                         |                         |                        | s          |

|-----------------------------|---------------------------------|-----------|---------------|---------------|--------------|----------|-------------------------|-------------------------|-----------------------|-----------------------|-----------------------|------------------------|------------|------------------------|------------|-------------------------|-------------------------|------------------------|------------|

| Virtual Address<br>(BF81_#) | Register<br>Name <sup>(1)</sup> | Bit Range | 31/15         | 30/14         | 29/13        | 28/12    | 27/11                   | 26/10                   | 25/9                  | 24/8                  | 23/7                  | 22/6                   | 21/5       | 20/4                   | 19/3       | 18/2                    | 17/1                    | 16/0                   | All Resets |

|                             | u= c. c.(6)                     | 31:16     | CNKIE         | CNJIE         | CNHIE        | CNGIE    | CNFIE                   | CNEIE                   | CNDIE                 | CNCIE                 | CNBIE                 | CNAIE                  | I2C1MIE    | I2C1SIE                | I2C1BIE    | U1TXIE                  | U1RXIE                  | U1EIE                  | 0000       |

| 00F0                        | IEC3 <sup>(6)</sup>             | 15:0      | SPI1TXIE      | SPI1RXIE      | SPI1EIE      | -        | CRPTIE <sup>(7)</sup>   | SBIE                    | CFDCIE                | CPCIE                 | ADCD44IE              | ADCD43IE               | ADCD42IE   | ADCD41IE               | ADCD40IE   | ADCD39IE                | ADCD38IE                | ADCD37IE               | 0000       |

| 04.00                       | 1504                            | 31:16     | <b>U3TXIE</b> | <b>U3RXIE</b> | <b>U3EIE</b> | SPI3TXIE | SPI3RXIE                | SPI3EIE                 | ETHIE                 | CAN2IE <sup>(3)</sup> | CAN1IE <sup>(3)</sup> | 12C2MIE <sup>(2)</sup> | 12C2SIE(2) | I2C2BIE <sup>(2)</sup> | U2TXIE     | U2RXIE                  | U2EIE                   | SPI2TXIE               | 0000       |

| 0100                        | IEC4                            | 15:0      | SPI2RXIE      | SPI2EIE       | DMA7IE       | DMA6IE   | DMA5IE                  | DMA4IE                  | <b>DMA3IE</b>         | DMA2IE                | DMA1IE                | DMA0IE                 | USBDMAIE   | USBIE                  | CMP2IE     | CMP1IE                  | PMPEIE                  | PMPIE                  | 0000       |

| 0110                        |                                 | 31:16     | _             | U6TXIE        | U6RXIE       | U6EIE    | SPI6TXIE <sup>(2)</sup> | SPI6RXIE <sup>(2)</sup> | SPI6IE <sup>(2)</sup> | I2C5MIE               | I2C5SIE               | I2C5BIE                | U5TXIE     | U5RXIE                 | U5EIE      | SPI5TXIE <sup>(2)</sup> | SPI5RXIE <sup>(2)</sup> | SPI5EIE <sup>(2)</sup> | 0000       |

| 0110                        | IECS                            | 15:0      | I2C4MIE       | I2C4SIE       | I2C4BIE      | U4TXIE   | U4RXIE                  | U4EIE                   | SQI1IE                | PREIE                 | FCEIE                 | RTCCIE                 | SPI4TXIE   | SPI4RXIE               | SPI4EIE    | I2C3MIE                 | I2C3SIE                 | I2C3BIE                | 0000       |

| 04.00                       | 1500                            | 31:16     | _             | _             | _            | _        | _                       | _                       | _                     | —                     | _                     | _                      | ADC7WIE    | _                      | _          | ADC4WIE                 | ADC3WIE                 | ADC2WIE                | 0000       |

| 0120                        | IEC6                            | 15:0      | ADC1WIE       | ADC0WIE       | ADC7EIE      | _        | —                       | ADC4EIE                 | ADC3EIF               | ADC2EIE               | ADC1EIE               | ADC0EIE                | —          | ADCGRPIE               | _          | ADCURDYIE               | ADCARDYIE               | ADCEOSIE               | 0000       |

| 04.40                       |                                 | 31:16     | _             | _             | _            |          | INT0IP<2:0>             |                         | INTOIS                | 6<1:0>                | _                     | _                      | _          |                        | CS1IP<2:0: | >                       | CS1IS                   | i<1:0>                 | 0000       |

| 0140                        | IPC0                            | 15:0      | _             | _             | _            |          | CS0IP<2:0>              |                         | CS0IS                 | <1:0>                 | _                     | _                      | _          |                        | CTIP<2:0>  |                         | CTIS                    | <1:0>                  | 0000       |

| 0150                        |                                 | 31:16     | _             | _             | _            |          | OC1IP<2:0>              |                         | OC1IS                 | 5<1:0>                | _                     | _                      | _          |                        | IC1IP<2:0> | •                       | IC1IS                   | <1:0>                  | 0000       |

| 0150                        | IPC1                            | 15:0      | _             | _             | _            |          | IC1EIP<2:0>             |                         | IC1EIS                | S<1:0>                | _                     | _                      | _          |                        | T1IP<2:0>  |                         | T1IS∢                   | <1:0>                  | 0000       |

| 04.00                       | 1000                            | 31:16     | _             | _             | _            |          | IC2IP<2:0>              |                         | IC2IS                 | <1:0>                 | _                     | _                      | _          |                        | IC2EIP<2:0 | >                       | IC2EIS                  | S<1:0>                 | 0000       |

| 0160                        | IPC2                            | 15:0      | _             | _             | _            |          | T2IP<2:0>               |                         | T2IS<                 | <1:0>                 | _                     | _                      | _          |                        | INT1IP<2:0 | >                       | INT1IS                  | S<1:0>                 | 0000       |

| 0470                        | IPC3                            | 31:16     | -             | _             | _            |          | IC3EIP<2:0>             |                         | IC3EIS                | S<1:0>                | _                     | -                      | _          |                        | T3IP<2:0>  |                         | T3IS<                   | <1:0>                  | 0000       |

| 0170                        | IPCS                            | 15:0      | -             | _             | _            |          | INT2IP<2:0>             |                         | INT2IS                | S<1:0>                | _                     | _                      | _          |                        | OC2IP<2:0  | >                       | OC2IS                   | S<1:0>                 | 0000       |

| 0180                        |                                 | 31:16     | -             | _             | _            |          | T4IP<2:0>               |                         | T4IS<                 | <1:0>                 | _                     | _                      | _          |                        | INT3IP<2:0 | >                       | INT3IS                  | S<1:0>                 | 0000       |

| 0180                        | IPC4                            | 15:0      | -             | _             | _            |          | OC3IP<2:0>              |                         | OC3IS                 | i<1:0>                | _                     | -                      | _          |                        | IC3IP<2:0> | •                       | IC3IS                   | <1:0>                  | 0000       |

| 0400                        | IDOC                            | 31:16     | -             | _             | _            |          | INT4IP<2:0>             |                         | INT4IS                | 6<1:0>                | _                     | _                      | _          |                        | OC4IP<2:0  | >                       | OC4IS                   | S<1:0>                 | 0000       |

| 0190                        | IPC5                            | 15:0      | _             | _             | _            |          | IC4IP<2:0>              |                         | IC4IS                 | <1:0>                 | _                     | _                      | —          |                        | IC4EIP<2:0 | >                       | IC4EIS                  | S<1:0>                 | 0000       |

| 0140                        | IDCC                            | 31:16     | -             | _             | _            |          | OC5IP<2:0>              |                         | OC5IS                 | i<1:0>                | _                     | _                      | _          |                        | IC5IP<2:0> | •                       | IC5IS                   | <1:0>                  | 0000       |

| 01A0                        | IPCO                            | 15:0      | -             | _             | _            |          | IC5EIP<2:0>             |                         | IC5EIS                | S<1:0>                | _                     | -                      | _          |                        | T5IP<2:0>  |                         | T5IS<                   | <1:0>                  | 0000       |

| 0400                        | 1007                            | 31:16     | -             | _             | _            |          | OC6IP<2:0>              |                         | OC6IS                 | <1:0>                 | _                     | _                      | _          |                        | IC6IP<2:0> | •                       | IC6IS                   | <1:0>                  | 0000       |

| 01B0                        | IPC7                            | 15:0      | -             | _             | _            |          | IC6EIP<2:0>             |                         | IC6EIS                | S<1:0>                | _                     | -                      | _          |                        | T6IP<2:0>  |                         | T6IS<                   | <1:0>                  | 0000       |

| 04.00                       |                                 | 31:16     | _             | _             | _            |          | OC7IP<2:0>              |                         | OC7IS                 | 5<1:0>                | _                     | _                      | —          |                        | IC7IP<2:0> | •                       | IC7IS                   | <1:0>                  | 0000       |

| 0100                        | IPC8                            | 15:0      | _             | _             | _            |          | IC7EIP<2:0>             |                         | IC7EIS                | S<1:0>                | _                     | _                      | —          |                        | T7IP<2:0>  |                         | T7IS∢                   | <1:0>                  | 0000       |

| 04 D 0                      |                                 | 31:16     | _             | _             | _            |          | OC8IP<2:0>              |                         | OC8IS                 | i<1:0>                | -                     | _                      | —          |                        | IC8IP<2:0> | •                       | IC8IS                   | <1:0>                  | 0000       |

| 01D0                        | IPC9                            | 15:0      | _             | _             | —            |          | IC8EIP<2:0>             |                         | IC8EIS                | S<1:0>                | _                     | —                      | —          |                        | T8IP<2:0>  |                         | T8IS<                   | <1:0>                  | 0000       |

| 0450                        | 10040                           | 31:16     | _             | _             | _            |          | OC9IP<2:0>              |                         | OC9IS                 | i<1:0>                | _                     | —                      | —          |                        | IC9IP<2:0> | •                       | IC9IS                   | <1:0>                  | 0000       |

| 01E0                        | IPC10                           | 15:0      | _             | _             | _            |          | IC9EIP<2:0>             |                         | IC9EIS                | S<1:0>                | _                     | _                      | —          |                        | T9IP<2:0>  |                         | T9IS<                   | <1:0>                  | 0000       |

PIC32MZ Embedded Connectivity with Floating Point Unit (EF) Family

Legend: x = unknown value on Reset; — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

Note 1: All registers in this table with the exception of the OFFx registers, have corresponding CLR, SET, and INV registers at their virtual addresses, plus offsets of 0x4, 0x8 and 0xC, respectively. See Section 12.3 "CLR, SET, and INV **Registers**" for more information. This bit or register is not available on 64-pin devices.

2:

This bit or register is not available on devices without a CAN module. 3:

4: This bit or register is not available on 100-pin devices.

Bits 31 and 30 are not available on 64-pin and 100-pin devices; bits 29 through 14 are not available on 64-pin devices. 5:

Bits 31, 30, 29, and bits 5 through 0 are not available on 64-pin and 100-pin devices; bit 31 is not available on 124-pin devices; bit 22 is not available on 64-pin devices. 6:

7: This bit or register is not available on devices without a Crypto module.

This bit or register is not available on 124-pin devices. 8:

#### **TABLE 7-3: INTERRUPT REGISTER MAP (CONTINUED)**

| ress<br>)                   |                                 | e         |       |       |       |       |       |       |      | Bi         | ts   |      |      |      |      |      |       |        | s          |

|-----------------------------|---------------------------------|-----------|-------|-------|-------|-------|-------|-------|------|------------|------|------|------|------|------|------|-------|--------|------------|

| Virtual Address<br>(BF81_#) | Register<br>Name <sup>(1)</sup> | Bit Range | 31/15 | 30/14 | 29/13 | 28/12 | 27/11 | 26/10 | 25/9 | 24/8       | 23/7 | 22/6 | 21/5 | 20/4 | 19/3 | 18/2 | 17/1  | 16/0   | All Resets |

|                             | OFF107 <sup>(7)</sup>           | 31:16     | _     |       | —     | _     | _     | —     | _    | —          | _    | _    | _    | _    | —    | _    | VOFF< | 17:16> | 0000       |

| 06EC                        | OFF107                          | 15:0      |       |       |       |       |       |       |      | VOFF<15:1> |      |      |      |      |      |      |       | _      | 0000       |

| 0654                        | OFF109                          | 31:16     | _     | —     | _     | -     |       | —     | _    | —          | —    | _    |      | -    | —    | _    | VOFF< | 17:16> | 0000       |

| 001 4                       | 011109                          | 15:0      |       |       |       |       |       |       |      | VOFF<15:1> |      |      |      |      |      |      |       | —      | 0000       |

| 0658                        | OFF110                          | 31:16     | —     | _     | —     | —     | _     | —     | —    | —          | _    | —    | —    | —    | —    | —    | VOFF< | 17:16> | 0000       |

| 001 0                       |                                 | 15:0      |       |       |       |       |       | -     | -    | VOFF<15:1> |      |      |      |      | -    |      |       | —      | 0000       |

| 06EC                        | OFF111                          | 31:16     | —     |       | —     | —     | _     | —     | _    | —          | —    | —    | —    | —    | —    | _    | VOFF< | 17:16> | 0000       |

| 0010                        | onn                             | 15:0      |       |       |       |       |       | -     | -    | VOFF<15:1> |      |      |      |      | -    |      |       | —      | 0000       |

| 0700                        | OFF112                          | 31:16     | _     | _     | —     | —     | _     | —     | _    | —          | _    | —    | -    | _    | —    | _    | VOFF< | 17:16> | 0000       |

| 0700                        |                                 | 15:0      |       |       |       |       |       |       |      | VOFF<15:1> |      |      |      |      |      |      |       | —      | 0000       |

| 0704                        | OFF113                          | 31:16     | —     | _     | —     | —     | _     | —     | —    | —          | _    | —    | —    | —    | —    | —    | VOFF< | 17:16> | 0000       |

| 0704                        | 011113                          | 15:0      |       |       |       |       |       |       |      | VOFF<15:1> |      |      |      |      |      |      |       | —      | 0000       |

| 0709                        | OFF114                          | 31:16     | -     | —     | —     | -     |       | _     | _    | —          | —    | —    |      |      | —    | -    | VOFF< | 17:16> | 0000       |

| 0708                        | OFF114                          | 15:0      |       |       |       |       |       |       |      | VOFF<15:1> |      |      |      |      |      |      |       | —      | 0000       |

| 0700                        | OFF115                          | 31:16     | _     | _     | —     | —     | _     | _     | _    | —          | —    | —    | -    | _    | —    | _    | VOFF< | 17:16> | 0000       |

| 0700                        | 011113                          | 15:0      |       |       |       |       |       |       |      | VOFF<15:1> |      |      |      |      |      |      |       | —      | 0000       |

| 0710                        | OFF116                          | 31:16     | -     | —     | —     | -     |       | _     | _    | —          | —    | —    |      |      | _    |      | VOFF< | 17:16> | 0000       |

| 0710                        | OFFIIO                          | 15:0      |       |       |       |       |       |       |      | VOFF<15:1> |      |      |      |      |      |      |       | —      | 0000       |

| 0714                        | OFF117                          | 31:16     | _     | _     | —     | —     | _     | _     | _    | —          | —    | —    | -    | _    | —    | _    | VOFF< | 17:16> | 0000       |

| 0714                        |                                 | 15:0      |       |       |       |       |       | -     | -    | VOFF<15:1> |      |      |      |      | -    |      |       | —      | 0000       |

| 0718                        | OFF118 <sup>(2)</sup>           | 31:16     | _     | _     | —     | —     | _     | —     | _    | —          | _    | —    | -    | _    | —    | _    | VOFF< | 17:16> | 0000       |

| 0710                        |                                 | 15:0      |       |       |       |       |       |       |      | VOFF<15:1> |      |      |      |      |      |      |       | —      | 0000       |

| 0710                        | OFF119                          | 31:16     | —     | _     | —     | _     |       | —     | —    | —          | _    | —    |      | _    | —    |      | VOFF< | 17:16> | 0000       |

| 0/10                        | OFFII9                          | 15:0      |       |       |       |       |       | -     | -    | VOFF<15:1> |      | -    |      |      | -    | -    | -     | —      | 0000       |

| 0720                        | OFF120                          | 31:16     | —     | —     | —     | —     | —     | —     | -    | -          | —    | —    | —    | _    | —    | _    | VOFF< | 17:16> | 0000       |

| 0120                        |                                 | 15:0      |       |       |       |       |       |       |      | VOFF<15:1> |      |      |      |      |      |      |       | —      | 0000       |

| 0724                        | OFF121                          | 31:16     | _     | _     | _     | _     | _     | _     | _    | —          |      |      | _    |      | _    | _    | VOFF< | 17:16> | 0000       |

| 0724                        |                                 | 15:0      |       |       |       |       |       |       |      | VOFF<15:1> |      |      |      |      |      |      |       | _      | 0000       |

| 0700                        | 055400                          | 31:16     | —     |       | _     | —     | _     | —     | —    | —          | _    | —    | _    | _    | —    | —    | VOFF< | 17:16> | 0000       |

| 0728                        | OFF122                          | 15:0      |       |       |       |       |       |       |      | VOFF<15:1> |      |      |      |      |      |      |       | _      | 0000       |

All registers in this table with the exception of the OFFx registers, have corresponding CLR, SET, and INV registers at their virtual addresses, plus offsets of 0x4, 0x8 and 0xC, respectively. See Section 12.3 "CLR, SET, and INV Note 1: **Registers**" for more information. This bit or register is not available on 64-pin devices.

2:

3: This bit or register is not available on devices without a CAN module.

4: This bit or register is not available on 100-pin devices.

5: Bits 31 and 30 are not available on 64-pin and 100-pin devices; bits 29 through 14 are not available on 64-pin devices.

6: Bits 31, 30, 29, and bits 5 through 0 are not available on 64-pin and 100-pin devices; bit 31 is not available on 124-pin devices; bit 22 is not available on 64-pin devices.

7: This bit or register is not available on devices without a Crypto module.

This bit or register is not available on 124-pin devices. 8:

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|

| 04.04        | R-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 31:24        | RDWR              | _                 | _                 | _                 | —                 | —                 | —                | —                |

| 23:16        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 23.10        | _                 | _                 |                   |                   | —                 |                   | —                | —                |

| 45.0         | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 15:8         | _                 | _                 | _                 | _                 | —                 | _                 | —                | —                |

| 7.0          | U-0               | U-0               | U-0               | U-0               | U-0               | R-0               | R-0              | R-0              |

| 7:0          |                   |                   |                   |                   |                   | [                 | DMACH<2:0>       | <b>&gt;</b>      |

### REGISTER 10-2: DMASTAT: DMA STATUS REGISTER

# Legend:

| 0                               |                  |                                    |                    |  |  |  |

|---------------------------------|------------------|------------------------------------|--------------------|--|--|--|

| = Readable bit W = Writable bit |                  | U = Unimplemented bit, read as '0' |                    |  |  |  |

| -n = Value at POR               | '1' = Bit is set | '0' = Bit is cleared               | x = Bit is unknown |  |  |  |

bit 31 RDWR: Read/Write Status bit

1 = Last DMA bus access when an error was detected was a read 0 = Last DMA bus access when an error was detected was a write

bit 30-3 Unimplemented: Read as '0'

bit 2-0 **DMACH<2:0>:** DMA Channel bits These bits contain the value of the most recent active DMA channel when an error was detected.

# REGISTER 10-3: DMAADDR: DMA ADDRESS REGISTER

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |  |  |  |  |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|--|--|--|--|

| 04-04        | R-0               | R-0               | R-0               | R-0               | R-0               | R-0               | R-0              | R-0              |  |  |  |  |

| 31:24        | DMAADDR<31:24>    |                   |                   |                   |                   |                   |                  |                  |  |  |  |  |

| 00.40        | R-0               | R-0               | R-0               | R-0               | R-0               | R-0               | R-0              | R-0              |  |  |  |  |

| 23:16        | DMAADDR<23:16>    |                   |                   |                   |                   |                   |                  |                  |  |  |  |  |

| 45.0         | R-0               | R-0               | R-0               | R-0               | R-0               | R-0               | R-0              | R-0              |  |  |  |  |

| 15:8         |                   |                   |                   | DMAADDI           | R<15:8>           |                   |                  |                  |  |  |  |  |

| 7.0          | R-0               | R-0               | R-0               | R-0               | R-0               | R-0               | R-0              | R-0              |  |  |  |  |

| 7:0          |                   |                   |                   | DMAADD            | R<7:0>            |                   |                  |                  |  |  |  |  |

# Legend:

| Logona.           |                  |                                    |                    |  |  |  |

|-------------------|------------------|------------------------------------|--------------------|--|--|--|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, read as '0' |                    |  |  |  |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared               | x = Bit is unknown |  |  |  |

## bit 31-0 DMAADDR<31:0>: DMA Module Address bits

These bits contain the address of the most recent DMA access when an error was detected.

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6     | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3  | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |

|--------------|-------------------|-----------------------|-------------------|-------------------|--------------------|-------------------|------------------|------------------|

| 04.04        | U-0               | U-0                   | R/W-0             | R/W-0             | R/W-0              | U-0               | U-0              | R/W-0            |

| 31:24        | —                 | —                     | BYTC              | <1:0>             | WBO <sup>(1)</sup> | _                 | _                | BITO             |

| 00.40        | U-0               | U-0                   | U-0               | U-0               | U-0                | U-0               | U-0              | U-0              |

| 23:16        | —                 | —                     | —                 | —                 | —                  | _                 | _                | —                |

| 45.0         | U-0               | U-0                   | U-0               | R/W-0             | R/W-0              | R/W-0             | R/W-0            | R/W-0            |

| 15:8         | —                 | —                     | _                 |                   |                    | PLEN<4:0>         |                  |                  |

| 7.0          | R/W-0             | R/W-0                 | R/W-0             | U-0               | U-0                | R/W-0             | R/W-0            | R/W-0            |

| 7:0          | CRCEN             | CRCAPP <sup>(1)</sup> | CRCTYP            | _                 | —                  | (                 | CRCCH<2:0>       |                  |

### REGISTER 10-4: DCRCCON: DMA CRC CONTROL REGISTER

# Legend:

| - J      |            |                  |                          |                    |

|----------|------------|------------------|--------------------------|--------------------|

| R = Rea  | adable bit | W = Writable bit | U = Unimplemented bit, r | ead as '0'         |

| -n = Val | lue at POR | '1' = Bit is set | '0' = Bit is cleared     | x = Bit is unknown |

### bit 31-30 Unimplemented: Read as '0'

- bit 29-28 **BYTO<1:0>:** CRC Byte Order Selection bits

- 11 = Endian byte swap on half-word boundaries (i.e., source half-word order with reverse source byte order per half-word)

- 10 = Swap half-words on word boundaries (i.e., reverse source half-word order with source byte order per half-word)

- 01 = Endian byte swap on word boundaries (i.e., reverse source byte order)

- 00 = No swapping (i.e., source byte order)

- bit 27 WBO: CRC Write Byte Order Selection bit<sup>(1)</sup>

- 1 = Source data is written to the destination re-ordered as defined by BYTO<1:0>

- 0 = Source data is written to the destination unaltered

- bit 26-25 Unimplemented: Read as '0'

- bit 24 BITO: CRC Bit Order Selection bit

When CRCTYP (DCRCCON<15>) = 1 (CRC module is in IP Header mode):

- 1 = The IP header checksum is calculated Least Significant bit (LSb) first (i.e., reflected)

- 0 = The IP header checksum is calculated Most Significant bit (MSb) first (i.e., not reflected)

<u>When CRCTYP (DCRCCON<15>) = 0</u> (CRC module is in LFSR mode):

- 1 = The LFSR CRC is calculated Least Significant bit first (i.e., reflected)

- 0 = The LFSR CRC is calculated Most Significant bit first (i.e., not reflected)

- bit 23-13 Unimplemented: Read as '0'

- bit 12-8 **PLEN<4:0>:** Polynomial Length bits<sup>(1)</sup>

<u>When CRCTYP (DCRCCON<15>) = 1</u> (CRC module is in IP Header mode): These bits are unused.

<u>When CRCTYP (DCRCCON<15>) = 0</u> (CRC module is in LFSR mode): Denotes the length of the polynomial -1.

- bit 7 CRCEN: CRC Enable bit

- 1 = CRC module is enabled and channel transfers are routed through the CRC module

- 0 = CRC module is disabled and channel transfers proceed normally

- **Note 1:** When WBO = 1, unaligned transfers are not supported and the CRCAPP bit cannot be set.

### REGISTER 11-30: USBCRCON: USB CLOCK/RESET CONTROL REGISTER (CONTINUED)

- bit 3 SENDMONEN: Session End VBUS Monitoring for OTG Enable bit

- 1 = Enable monitoring for VBUS in Session End range (between 0.2V and 0.8V)

- 0 = Disable monitoring for VBUS in Session End range

- bit 2 USBIE: USB General Interrupt Enable bit

- 1 = Enables general interrupt from USB module

- 0 = Disables general interrupt from USB module

- bit 1 USBRIE: USB Resume Interrupt Enable bit

- 1 = Enable remote resume from suspend Interrupt

- 0 = Disable interrupt to a Remote Devices USB resume signaling

### bit 0 USBWKUPEN: USB Activity Detection Interrupt Enable bit

- 1 = Enable interrupt for detection of activity on USB bus in Sleep mode

- 0 = Disable interrupt for detection of activity on USB bus in Sleep mode

| Bit<br>Range | Bit<br>31/23/15/7    | Bit<br>30/22/14/6 | Bit<br>29/21/13/5   | Bit<br>28/20/12/4 | Bit<br>27/19/11/3  | Bit<br>26/18/10/2 | Bit<br>25/17/9/1   | Bit<br>24/16/8/0 |

|--------------|----------------------|-------------------|---------------------|-------------------|--------------------|-------------------|--------------------|------------------|

| 31:24        | U-0                  | U-0               | U-0                 | U-0               | U-0                | U-0               | U-0                | U-0              |

| 31.24        |                      | —                 |                     |                   | —                  |                   |                    | —                |

| 22:46        | U-0                  | U-0               | U-0                 | U-0               | U-0                | U-0               | U-0                | U-0              |

| 23:16        |                      | —                 | _                   | —                 | —                  | —                 | —                  | —                |

| 45.0         | R/W-0                | U-0               | R/W-0               | U-0               | U-0                | U-0               | U-0                | U-0              |

| 15:8         | ON <sup>(1)</sup>    | —                 | SIDL <sup>(2)</sup> | _                 | —                  | _                 | _                  | —                |

| 7:0          | R/W-0                | R/W-0             | R/W-0               | R/W-0             | R/W-0              | U-0               | R/W-0              | U-0              |

| 7:0          | TGATE <sup>(1)</sup> | Т                 | CKPS<2:0>(          | 1)                | T32 <sup>(3)</sup> | _                 | TCS <sup>(1)</sup> | —                |

#### TxCON: TYPE B TIMER CONTROL REGISTER ('x' = 2-9) REGISTER 14-1:

### Legend:

bit 3

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, r | ead as '0'         |

|-------------------|------------------|--------------------------|--------------------|

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared     | x = Bit is unknown |

#### bit 31-16 Unimplemented: Read as '0'

- bit 15 ON: Timer On bit<sup>(1)</sup>

- 1 = Module is enabled 0 = Module is disabled

- Unimplemented: Read as '0'

#### bit 14 bit 13 SIDL: Stop in Idle Mode bit<sup>(2)</sup>

- 1 = Discontinue operation when device enters Idle mode

- 0 = Continue operation even in Idle mode

#### Unimplemented: Read as '0' bit 12-8

TGATE: Timer Gated Time Accumulation Enable bit<sup>(1)</sup> bit 7

### When TCS = 1:

This bit is ignored and is read as '0'.

# When TCS = 0:

- 1 = Gated time accumulation is enabled

- 0 = Gated time accumulation is disabled

#### bit 6-4 TCKPS<2:0>: Timer Input Clock Prescale Select bits<sup>(1)</sup>

- 111 = 1:256 prescale value

- 110 = 1:64 prescale value

- 101 = 1:32 prescale value

- 100 = 1:16 prescale value

- 011 = 1:8 prescale value

- 010 = 1:4 prescale value

- 001 = 1:2 prescale value

# 000 = 1:1 prescale value

# T32: 32-Bit Timer Mode Select bit(3)

- 1 = Odd numbered and even numbered timers form a 32-bit timer

- 0 = Odd numbered and even numbered timers form separate 16-bit timers

- Note 1: While operating in 32-bit mode, this bit has no effect for odd numbered timers (Timer1, Timer3, Timer5, Timer7, and Timer9). All timer functions are set through the even numbered timers.

- While operating in 32-bit mode, this bit must be cleared on odd numbered timers to enable the 32-bit timer 2: in Idle mode.

- 3: This bit is available only on even numbered timers (Timer2, Timer4, Timer6, and Timer8).

NOTES:

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|

| 04.04        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 31:24        |                   |                   | —                 | _                 | _                 | _                 | _                | —                |

| 22:46        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 23:16        |                   | —                 | —                 | _                 | _                 | —                 | _                | —                |

| 45.0         | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |

| 15:8         |                   |                   |                   | RDATAIN<          | 15:8>             |                   |                  |                  |

| 7:0          | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |

|              |                   |                   |                   | RDATAIN<          | :7:0>             |                   |                  |                  |

# REGISTER 23-10: PMRDIN: PARALLEL PORT READ INPUT DATA REGISTER

Legend:

| _090              |                  |                        |                    |

|-------------------|------------------|------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, | read as '0'        |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared   | x = Bit is unknown |

bit 31-16 Unimplemented: Read as '0'

bit 15-0 RDATAIN<15:0>: Port Read Input Data bits

**Note:** This register is only used when the DUALBUF bit (PMCON<17>) is set to '1' and exclusively for reads. If the DUALBUF bit is '0', the PMDIN register (Register 23-5) is used for reads instead of PMRDIN.

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|

| 24.24        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 31:24        | —                 | _                 | _                 | _                 | _                 |                   | _                | —                |

| 22:46        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 23:16        | —                 |                   |                   |                   |                   |                   | _                | —                |

| 45.0         | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 15:8         | —                 | _                 | _                 | _                 | _                 |                   | _                | —                |

| 7.0          | R/W-0             | R/W-0, HC         | R/W-0             | U-0               | U-0               | R/W-0             | R/W-0            | R/W-0            |

| 7:0          | SWAPOEN           | SWRST             | SWAPEN            |                   |                   | BDPCHST           | BDPPLEN          | DMAEN            |

### REGISTER 26-2: CECON: CRYPTO ENGINE CONTROL REGISTER

| Legend:           |                  | HC = Hardware Cleare  | d                  |

|-------------------|------------------|-----------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit | t, read as '0'     |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared  | x = Bit is unknown |

### bit 31-8 Unimplemented: Read as '0'

- bit 7 SWAPOEN: Swap Output Data Enable bit

- 1 = Output data is byte swapped when written by dedicated DMA

- 0 = Output data is not byte swapped when written by dedicated DMA

- bit 6 SWRST: Software Reset bit

- 1 = Initiate a software reset of the Crypto Engine

- 0 = Normal operation

- bit 5 **SWAPEN:** Input Data Swap Enable bit

- 1 = Input data is byte swapped when read by dedicated DMA

- 0 = Input data is not byte swapped when read by dedicated DMA

- bit 4-3 Unimplemented: Read as '0'

### bit 2 BDPCHST: Buffer Descriptor Processor (BDP) Fetch Enable bit

This bit should be enabled only after all DMA descriptor programming is completed.

- 1 = BDP descriptor fetch is enabled

- 0 = BDP descriptor fetch is disabled

### bit 1 **BDPPLEN:** Buffer Descriptor Processor Poll Enable bit

This bit should be enabled only after all DMA descriptor programming is completed.

- 1 = Poll for descriptor until valid bit is set

- 0 = Do not poll

# bit 0 DMAEN: DMA Enable bit

- 1 = Crypto Engine DMA is enabled

- 0 = Crypto Engine DMA is disabled

| Bit         |                         |                                                                                 |                                                                                                                           |                                                                                                            |                                                                                                                                                                                                                                                                                                                                                                                                      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |  |  |  |

|-------------|-------------------------|---------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| 31/23/15/7  | Bit<br>30/22/14/6       | Bit<br>29/21/13/5                                                               | Bit<br>28/20/12/4                                                                                                         | Bit<br>27/19/11/3                                                                                          | Bit<br>26/18/10/2                                                                                                                                                                                                                                                                                                                                                                                    | Bit<br>25/17/9/1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | Bit<br>24/16/8/0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |  |  |  |

| R/W-1       | R/W-1                   | R/W-1                                                                           | R/W-1                                                                                                                     | R/W-1                                                                                                      | R/W-1                                                                                                                                                                                                                                                                                                                                                                                                | R/W-1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | R/W-1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |  |  |  |

| POLY<31:24> |                         |                                                                                 |                                                                                                                           |                                                                                                            |                                                                                                                                                                                                                                                                                                                                                                                                      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |  |  |  |

| R/W-1       | R/W-1                   | R/W-1                                                                           | R/W-1                                                                                                                     | R/W-1                                                                                                      | R/W-1                                                                                                                                                                                                                                                                                                                                                                                                | R/W-1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | R/W-1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |  |  |  |

| POLY<23:16> |                         |                                                                                 |                                                                                                                           |                                                                                                            |                                                                                                                                                                                                                                                                                                                                                                                                      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |  |  |  |

| R/W-0       | R/W-0                   | R/W-0                                                                           | R/W-0                                                                                                                     | R/W-0                                                                                                      | R/W-0                                                                                                                                                                                                                                                                                                                                                                                                | R/W-0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | R/W-0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |  |  |  |

| POLY<15:8>  |                         |                                                                                 |                                                                                                                           |                                                                                                            |                                                                                                                                                                                                                                                                                                                                                                                                      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |  |  |  |

| R/W-0       | R/W-0                   | R/W-0                                                                           | R/W-0                                                                                                                     | R/W-0                                                                                                      | R/W-0                                                                                                                                                                                                                                                                                                                                                                                                | R/W-0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | R/W-0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |  |  |  |