Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFI

| Product Status             | Active                                                                           |

|----------------------------|----------------------------------------------------------------------------------|

| Core Processor             | MIPS32® M-Class                                                                  |

| Core Size                  | 32-Bit Single-Core                                                               |

| Speed                      | 200MHz                                                                           |

| Connectivity               | Ethernet, I <sup>2</sup> C, PMP, SPI, SQI, UART/USART, USB OTG                   |

| Peripherals                | Brown-out Detect/Reset, DMA, I <sup>2</sup> S, POR, PWM, WDT                     |

| Number of I/O              | 46                                                                               |

| Program Memory Size        | 512KB (512K x 8)                                                                 |

| Program Memory Type        | FLASH                                                                            |

| EEPROM Size                | -                                                                                |

| RAM Size                   | 128K x 8                                                                         |

| Voltage - Supply (Vcc/Vdd) | 2.1V ~ 3.6V                                                                      |

| Data Converters            | A/D 24x12b                                                                       |

| Oscillator Type            | Internal                                                                         |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                                |

| Mounting Type              | Surface Mount                                                                    |

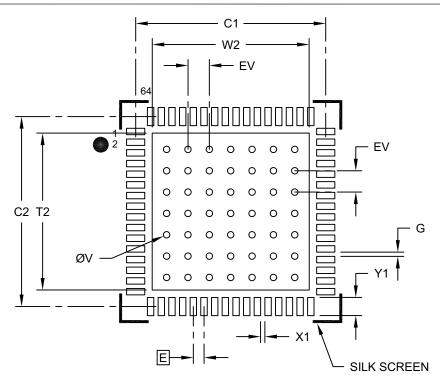

| Package / Case             | 64-VFQFN Exposed Pad                                                             |

| Supplier Device Package    | 64-QFN (9x9)                                                                     |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic32mz0512efe064-i-mr |

|                            |                                                                                  |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

|                 |                        | Pin Nu          | mber            |                          |             |                |                                   |

|-----------------|------------------------|-----------------|-----------------|--------------------------|-------------|----------------|-----------------------------------|

| Pin Name        | 64-pin<br>QFN/<br>TQFP | 100-pin<br>TQFP | 124-pin<br>VTLA | 144-pin<br>TQFP/<br>LQFP | Pin<br>Type | Buffer<br>Type | Description                       |

|                 |                        |                 | •               |                          | PO          | RTA            | ·                                 |

| RA0             | _                      | 17              | A11             | 22                       | I/O         | ST             | PORTA is a bidirectional I/O port |

| RA1             | —                      | 38              | B21             | 56                       | I/O         | ST             |                                   |

| RA2             | —                      | 59              | A41             | 85                       | I/O         | ST             |                                   |

| RA3             | —                      | 60              | B34             | 86                       | I/O         | ST             |                                   |

| RA4             | —                      | 61              | A42             | 87                       | I/O         | ST             |                                   |

| RA5             | —                      | 2               | B1              | 2                        | I/O         | ST             |                                   |

| RA6             | —                      | 89              | A61             | 129                      | I/O         | ST             |                                   |

| RA7             | —                      | 90              | B51             | 130                      | I/O         | ST             |                                   |

| RA9             | —                      | 28              | B15             | 39                       | I/O         | ST             |                                   |

| RA10            | _                      | 29              | A20             | 40                       | I/O         | ST             | ]                                 |

| RA14            | _                      | 66              | B37             | 95                       | I/O         | ST             |                                   |

| RA15            | _                      | 67              | A45             | 96                       | I/O         | ST             |                                   |

|                 |                        |                 |                 |                          | PO          | RTB            |                                   |

| RB0             | 16                     | 25              | A18             | 36                       | I/O         | ST             | PORTB is a bidirectional I/O port |

| RB1             | 15                     | 24              | A17             | 35                       | I/O         | ST             |                                   |

| RB2             | 14                     | 23              | A16             | 34                       | I/O         | ST             |                                   |

| RB3             | 13                     | 22              | A14             | 31                       | I/O         | ST             |                                   |

| RB4             | 12                     | 21              | A13             | 26                       | I/O         | ST             |                                   |

| RB5             | 11                     | 20              | B11             | 25                       | I/O         | ST             |                                   |

| RB6             | 17                     | 26              | B14             | 37                       | I/O         | ST             |                                   |

| RB7             | 18                     | 27              | A19             | 38                       | I/O         | ST             |                                   |

| RB8             | 21                     | 32              | B18             | 47                       | I/O         | ST             |                                   |

| RB9             | 22                     | 33              | A23             | 48                       | I/O         | ST             |                                   |

| RB10            | 23                     | 34              | B19             | 49                       | I/O         | ST             | _                                 |

| RB11            | 24                     | 35              | A24             | 50                       | I/O         | ST             | _                                 |

| RB12            | 27                     | 41              | A27             | 59                       | I/O         | ST             | _                                 |

| RB13            | 28                     | 42              | B23             | 60                       | I/O         | ST             | -                                 |

| RB14            | 29                     | 43              | A28             | 61                       | I/O         | ST             | -                                 |

| RB15            | 30                     | 44              | B24             | 62                       | I/O         | ST             |                                   |

| <b>D</b> O1     |                        | -               |                 |                          |             | RTC            |                                   |

| RC1             | —                      | 6               | B3              | 6                        | I/O         | ST             | PORTC is a bidirectional I/O port |

| RC2             |                        | 7               | A6              | 11                       | I/O         | ST             | 4                                 |

| RC3             |                        | 8               | B5              | 12                       | I/O         | ST             | 4                                 |

| RC4             | -                      | 9               | A7              | 13                       | I/O         | ST             | 4                                 |

| RC12            | 31                     | 49              | B28             | 71                       | I/O         | ST             | 4                                 |

| RC13            | 47                     | 72              | B41             | 105                      | I/O         | ST             | 4                                 |

| RC14            | 48                     | 73              | A49             | 106                      | I/O         | ST             | 4                                 |

| RC15<br>Legend: | 32                     | 50<br>MOS-comp  | A33             | 72                       | I/O         | ST             | Analog input P = Power            |

#### **TABLE 1-6:** PORTA THROUGH PORTK PINOUT I/O DESCRIPTIONS

ST = Schmitt Trigger input with CMOS levels TTL = Transistor-transistor Logic input buffer

O = Output PPS = Peripheral Pin Select I = Input

## 4.0 MEMORY ORGANIZATION

| Note: | This data sheet summarizes the features<br>of the PIC32MZ EF family of devices. It is<br>not intended to be a comprehensive<br>reference source.For detailed<br>information, refer to <b>Section 48</b> . |

|-------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|       | "Memory Organization and<br>Permissions" in the "PIC32 Family<br>Reference Manual", which is available<br>from the Microchip web site<br>(www.microchip.com/PIC32).                                       |

PIC32MZ EF microcontrollers provide 4 GB of unified virtual memory address space. All memory regions, including program, data memory, SFRs and Configuration registers, reside in this address space at their respective unique addresses. The program and data memories can be optionally partitioned into user and kernel memories. In addition, PIC32MZ EF devices allow execution from data memory.

Key features include:

- 32-bit native data width

- Separate User (KUSEG) and Kernel (KSEG0/ KSEG1/KSEG2/KSEG3) mode address space

- Separate boot Flash memory for protected code

- Robust bus exception handling to intercept runaway code

- Cacheable (KSEG0/KSEG2) and non-cacheable (KSEG1/KSEG3) address regions

- Read/write permission access to predefined memory regions

#### 4.1 Memory Layout

PIC32MZ EF microcontrollers implement two address schemes: virtual and physical. All hardware resources, such as program memory, data memory and peripherals, are located at their respective physical addresses. Virtual addresses are exclusively used by the CPU to fetch and execute instructions as well as access peripherals. Physical addresses are used by bus master peripherals, such as DMA and the Flash controller, that access memory independently of the CPU.

The main memory maps for the PIC32MZ EF devices are illustrated in Figure 4-1 through Figure 4-4. Figure 4-5 provides memory map information for boot Flash and boot alias. Table 4-1 provides memory map information for Special Function Registers (SFRs).

#### REGISTER 4-3: SBTxELOG1: SYSTEM BUS TARGET 'x' ERROR LOG REGISTER 1 ('x' = 0-13) (CONTINUED)

- bit 7-4 REGION<3:0>: Requested Region Number bits

- 1111 0000 = Target's region that reported a permission group violation

- bit 3 Unimplemented: Read as '0'

- bit 2-0 CMD<2:0>: Transaction Command of the Requester bits

- 111 = Reserved

- 110 = Reserved

- 101 = Write (a non-posted write)

- 100 = Reserved

- 011 = Read (a locked read caused by a Read-Modify-Write transaction)

- 010 = Read

- 001 = Write

- 000 = Idle

Note: Refer to Table 4-6 for the list of available targets and their descriptions.

# 7.1 CPU Exceptions

CPU coprocessor 0 contains the logic for identifying and managing exceptions. Exceptions can be caused by a variety of sources, including boundary cases in data, external events or program errors. Table 7-1 lists the exception types in order of priority.

# TABLE 7-1: MIPS32<sup>®</sup> M-CLASS MICROPROCESSOR CORE EXCEPTION TYPES

| Exception Type<br>(In Order of<br>Priority) | Description                                                                                                                      | Branches to                       | Status<br>Bits Set | Debug Bits<br>Set | EXCCODE | XC32 Function Name         |

|---------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------|-----------------------------------|--------------------|-------------------|---------|----------------------------|

|                                             |                                                                                                                                  | Highest Priority                  |                    |                   |         |                            |

| Reset                                       | Assertion MCLR or a Power-on Reset (POR).                                                                                        | 0xBFC0_0000                       | BEV, ERL           | —                 | _       | _on_reset                  |

| Soft Reset                                  | Assertion of a software Reset.                                                                                                   | 0xBFC0_0000                       | BEV, SR,<br>ERL    | —                 | —       | _on_reset                  |

| DSS                                         | EJTAG debug single step.                                                                                                         | 0xBFC0_0480                       | —                  | DSS               | _       | —                          |

| DINT                                        | EJTAG debug interrupt. Caused by the assertion of the external EJ_DINT input or by setting the EjtagBrk bit in the ECR register. | 0xBFC0_0480                       | —                  | DINT              | _       | _                          |

| NMI                                         | Assertion of NMI signal.                                                                                                         | 0xBFC0_0000                       | BEV, NMI,<br>ERL   | —                 | —       | _nmi_handler               |

| Machine Check                               | TLB write that conflicts with an existing entry.                                                                                 | EBASE+0x180                       | MCHECK,<br>EXL     | —                 | 0x18    | _general_exception_handler |

| Interrupt                                   | Assertion of unmasked hardware or software inter-<br>rupt signal.                                                                | See Table 7-2.                    | IPL<2:0>           |                   | 0x00    | See Table 7-2.             |

| Deferred Watch                              | Deferred watch (unmasked by K DM=>!(K DM) transition).                                                                           | EBASE+0x180                       | WP, EXL            |                   | 0x17    | _general_exception_handler |

| DIB                                         | EJTAG debug hardware instruction break matched.                                                                                  | 0xBFC0_0480                       | —                  | DIB               | _       |                            |

| WATCH                                       | A reference to an address that is in one of the Watch registers (fetch).                                                         | EBASE+0x180                       | EXL                | —                 | 0x17    | _general_exception_handler |

| AdEL                                        | Fetch address alignment error. Fetch reference to protected address.                                                             | EBASE+0x180                       | EXL                | —                 | 0x04    | _general_exception_handler |

| TLBL                                        | Fetch TLB miss or fetch TLB hit to page with $V = 0$ .                                                                           | EBASE if Status.EXL = 0           | _                  | —                 | 0x02    | —                          |

|                                             |                                                                                                                                  | EBASE+0x180 if<br>Status.EXL == 1 | —                  |                   | 0x02    | _general_exception_handler |

| TLBL Execute<br>Inhibit                     | An instruction fetch matched a valid TLB entry that had the XI bit set.                                                          | EBASE+0x180                       | EXL                | —                 | 0x14    | _general_exception_handler |

| IBE                                         | Instruction fetch bus error.                                                                                                     | EBASE+0x180                       | EXL                | —                 | 0x06    | _general_exception_handler |

#### 7.3 **Interrupt Control Registers**

#### **TABLE 7-3:** INTERRUPT REGISTER MAP

| ress<br>()                  |                                 | e         |                      |               |             |                 |                       |                         |                       | B                     | its                   |                        |                        |                        |          |                         |                         |                        | s          |

|-----------------------------|---------------------------------|-----------|----------------------|---------------|-------------|-----------------|-----------------------|-------------------------|-----------------------|-----------------------|-----------------------|------------------------|------------------------|------------------------|----------|-------------------------|-------------------------|------------------------|------------|

| Virtual Address<br>(BF81_#) | Register<br>Name <sup>(1)</sup> | Bit Range | 31/15                | 30/14         | 29/13       | 28/12           | 27/11                 | 26/10                   | 25/9                  | 24/8                  | 23/7                  | 22/6                   | 21/5                   | 20/4                   | 19/3     | 18/2                    | 17/1                    | 16/0                   | All Resets |

|                             |                                 | 31:16     |                      |               |             | NMIK            | EY<7:0>               |                         |                       |                       | —                     | —                      | _                      | _                      | _        | _                       | —                       | _                      | 0000       |

| 0000                        | INTCON                          | 15:0      | _                    | _             | _           | MVEC            | _                     |                         | TPC<2:0>              |                       | —                     | _                      | _                      | INT4EP                 | INT3EP   | INT2EP                  | INT1EP                  | INT0EP                 | 0000       |

| 0010                        |                                 | 31:16     |                      | PRI7S         | S<3:0>      |                 |                       | PRI6SS                  | 8<3:0>                |                       |                       | PRI5S                  | S<3:0>                 |                        |          | PRI4S                   | S<3:0>                  |                        | 0000       |

| 0010                        | PRISS                           | 15:0      |                      | PRI3SS        | S<3:0>      |                 |                       | PRI2SS                  | 8<3:0>                |                       |                       | PRI1S                  | S<3:0>                 |                        | _        | -                       | —                       | SS0                    | 0000       |

| 0020                        | INTSTAT                         | 31:16     | _                    |               | _           | _               |                       | -                       |                       | _                     | _                     | _                      |                        | _                      | _        |                         | _                       | —                      | 0000       |

| 0020                        |                                 | 15:0      | _                    | _             | —           | —               | _                     |                         | SRIPL<2:0>            |                       |                       |                        |                        | SIR                    | Q<7:0>   |                         |                         |                        | 0000       |

| 0030                        | IPTMR                           | 31:16     |                      |               |             |                 |                       |                         |                       | IPTMR                 | <31.0>                |                        |                        |                        |          |                         |                         |                        | 0000       |

| 0000                        |                                 | 15:0      |                      |               |             |                 |                       |                         |                       |                       |                       |                        |                        | 1                      |          |                         |                         | T                      | 0000       |

| 0040                        | IFS0                            | 31:16     | OC6IF                | IC6IF         | IC6EIF      | T6IF            | OC5IF                 | IC5IF                   | IC5EIF                | T5IF                  | INT4IF                | OC4IF                  | IC4IF                  | IC4EIF                 | T4IF     | INT3IF                  | OC3IF                   | IC3IF                  | 0000       |

| 00.0                        |                                 | 15:0      | IC3EIF               | T3IF          | INT2IF      | OC2IF           | IC2IF                 | IC2EIF                  | T2IF                  | INT1IF                | OC1IF                 | IC1IF                  | IC1EIF                 | T1IF                   | INT0IF   | CS1IF                   | CS0IF                   | CTIF                   | 0000       |

| 0050                        | IFS1                            | 31:16     | ADCD4IF              | ADCD3IF       | ADCD2IF     | ADCD1IF         | ADCD0IF               | ADCFLTIF                | ADCDF6IF              | ADCDF5IF              | ADCDF4IF              | ADCDF3IF               | ADCDF2IF               | ADCDF1IF               | ADCDC6IF | ADCDC5IF                | ADCDC4IF                | ADCDC3IF               |            |

|                             |                                 | 15:0      | ADCDC2IF             |               | ADCFIFOIF   | ADCIF           | OC9IF                 | IC9IF                   | IC9EIF                | T9IF                  | OC8IF                 | IC8IF                  | IC8EIF                 | T8IF                   | OC7IF    | IC7IF                   | IC7EIF                  | T7IF                   | 0000       |

| 0060                        | IFS2 <sup>(5)</sup>             | 31:16     | ADCD36IF             | ADCD35IF      | ADCD34IF    | ADCD33IF        | ADCD32IF              | ADCD31IF                | ADCD30IF              | ADCD29IF              | ADCD28IF              | ADCD27IF               | ADCD26IF               | ADCD25IF               | ADCD24IF | ADCD23IF                | ADCD22IF                | ADCD21IF               | -          |

|                             |                                 | 15:0      | ADCD20IF             | ADCD19IF      | ADCD18IF    | ADCD17IF        | ADCD16IF              | ADCD15IF                | ADCD14IF              | ADCD13IF              | ADCD12IF              | ADCD11IF               | ADCD10IF               | ADCD9IF                | ADCD8IF  | ADCD7IF                 | ADCD6IF                 | ADCD5IF                | 0000       |

| 0070                        | IFS3 <sup>(6)</sup>             | 31:16     | CNKIF <sup>(8)</sup> | CNJIF         | CNHIF       | CNGIF           | CNFIF                 | CNEIF                   | CNDIF                 | CNCIF                 | CNBIF                 | CNAIF                  | I2C1MIF                | I2C1SIF                | I2C1BIF  | U1TXIF                  | U1RXIF                  | U1EIF                  | 0000       |

|                             |                                 | 15:0      | SPI1TXIF             | SPI1RXIF      | SPI1EIF     | —               | CRPTIF <sup>(7)</sup> | SBIF                    | CFDCIF                | CPCIF                 | ADCD44IF              | ADCD43IF               | ADCD42IF               | ADCD41IF               | ADCD40IF | ADCD39IF                | ADCD38IF                | ADCD37IF               |            |

| 0080                        | IFS4                            | 31:16     | <b>U3TXIF</b>        | U3RXIF        | U3EIF       | <b>SPI3TXIF</b> | <b>SPI3RXIF</b>       | SPI3EIF                 | ETHIF                 | CAN2IF <sup>(3)</sup> | CAN1IF <sup>(3)</sup> | I2C2MIF <sup>(2)</sup> | 12C2SIF <sup>(2)</sup> | I2C2BIF <sup>(2)</sup> | U2TXIF   | U2RXIF                  | U2EIF                   | SPI2TXIF               | 0000       |

|                             |                                 | 15:0      | SPI2RXIF             | SPI2EIF       | DMA7IF      | DMA6IF          | DMA5IF                | DMA4IF                  | DMA3IF                | DMA2IF                | DMA1IF                | DMA0IF                 | USBDMAIF               | USBIF                  | CMP2IF   | CMP1IF                  | PMPEIF                  | PMPIF                  | 0000       |

| 0090                        | IFS5                            | 31:16     | —                    | U6TXIF        | U6RXIF      | U6EIF           | SPI6TX <sup>(2)</sup> | SPI6RXIF <sup>(2)</sup> | SPI6IF <sup>(2)</sup> | I2C5MIF               | I2C5SIF               | I2C5BIF                | U5TXIF                 | U5RXIF                 | U5EIF    | SPI5TXIF <sup>(2)</sup> | SPI5RXIF <sup>(2)</sup> | SPI5EIF <sup>(2)</sup> |            |

|                             |                                 | 15:0      | I2C4MIF              | I2C4SIF       | I2C4BIF     | U4TXIF          | U4RXIF                | U4EIF                   | SQI1IF                | PREIF                 | FCEIF                 | RTCCIF                 | SPI4TXIF               | SPI4RXIF               | SPI4EIF  | I2C3MIF                 | I2C3SIF                 | I2C3BIF                | 0000       |

| 00A0                        | IFS6                            | 31:16     | _                    | -             | _           | _               | _                     | -                       | _                     | _                     |                       | _                      | ADC7WIF                | _                      | —        | ADC4WIF                 | ADC3WIF                 |                        | 0000       |

|                             |                                 | 15:0      | ADC1WIF              | ADC0WIF       | ADC7EIF     | —               | _                     | ADC4EIF                 | ADC3EIF               | ADC2EIF               | ADC1EIF               | ADC0EIF                | -                      | ADCGRPIF               | —        | ADCURDYIF               |                         | ADCEOSIF               | _          |

| 00C0                        | IEC0                            | 31:16     | OC6IE                | IC6IE         | IC6EIE      | T6IE            | OC5IE                 | IC5IE                   | IC5EIE                | T5IE                  | INT4IE                | OC4IE                  | IC4IE                  | IC4EIE                 | T4IE     | INT3IE                  | OC3IE                   | IC3IE                  | 0000       |

|                             |                                 | 15:0      | IC3EIE               | T3IE          | INT2IE      | OC2IE           | IC2IE                 | IC2EIE                  | T2IE                  | INT1IE                | OC1IE                 | IC1IE                  | IC1EIE                 | T1IE                   | INTOIE   | CS1IE                   | CS0IE                   | CTIE                   | 0000       |

| 00D0                        | IEC1                            | 31:16     | ADCD4IE              | ADCD3IE       | ADCD2IE     | ADCD1IE         | ADCD0IE               | ADCFLTIE                | ADCDF6IE              | ADCDF5IE              | ADCDF4IE              | ADCDF3IE               | ADCDF2IE               | ADCDF1IE               | ADCDC6IE | ADCDC5IE                | ADCDC4IE                | ADCDC3IE               | -          |

|                             |                                 | 15:0      | ADCDC2IE             |               | ADCFIFOIE   | ADCIE           | OC9IE                 | IC9IE                   | IC9EIE                | T9IE                  | OC8IE                 | IC8IE                  | IC8EIE                 | T8IE                   | OC7IE    | IC7IE                   | IC7EIE                  | T7IE                   | 0000       |

| 00E0                        | IEC2 <sup>(5)</sup>             | 31:16     |                      |               | ADCD34IE    | ADCD33IE        | ADCD32IE              | ADCD31IE                | ADCD30IE              | ADCD29IE              | ADCD28IE              | ADCD27IE               | ADCD26IE               | ADCD25IE               | ADCD24IE | ADCD23IE                | ADCD22IE                | ADCD21IE               |            |

|                             |                                 |           | ADCD20IE             | ADCD19IE      | ADCD18IE    | ADCD17IE        | ADCD16IE              | ADCD15IE                | ADCD14IE              | ADCD13IE              | ADCD12IE              | ADCD11IE               | ADCD10IE               | ADCD9IE                | ADCD8IE  | ADCD7IE                 | ADCD6IE                 | ADCD5IE                | 0000       |

| Legei                       | nd: x =                         | unknow    | n value on R         | teset; — = ur | nimplemente | d, read as '0'  | . Reset values        | s are shown ir          | n hexadecima          | l.                    |                       |                        |                        |                        |          |                         |                         |                        |            |

All registers in this table with the exception of the OFFx registers, have corresponding CLR, SET, and INV registers at their virtual addresses, plus offsets of 0x4, 0x8 and 0xC, respectively. See Section 12.3 "CLR, SET, and INV Note 1: Registers" for more information.

This bit or register is not available on 64-pin devices. 2:

3: This bit or register is not available on devices without a CAN module. This bit or register is not available on 100-pin devices.

4:

Bits 31 and 30 are not available on 64-pin and 100-pin devices; bits 29 through 14 are not available on 64-pin devices. 5:

Bits 31, 30, 29, and bits 5 through 0 are not available on 64-pin and 100-pin devices; bit 31 is not available on 124-pin devices; bit 22 is not available on 64-pin devices. This bit or register is not available on devices without a Crypto module. 6: 7:

8: This bit or register is not available on 124-pin devices.

## TABLE 8-2: OSCILLATOR CONFIGURATION REGISTER MAP (CONTINUED)

| SSS                        |                                 |           |       |       |       |       |          |       |            | Bits |      |      |             |             |           |             |                |        | (2)                      |

|----------------------------|---------------------------------|-----------|-------|-------|-------|-------|----------|-------|------------|------|------|------|-------------|-------------|-----------|-------------|----------------|--------|--------------------------|

| Virtual Addres<br>(BF80_#) | Register<br>Name <sup>(1)</sup> | Bit Range | 31/15 | 30/14 | 29/13 | 28/12 | 27/11    | 26/10 | 25/9       | 24/8 | 23/7 | 22/6 | 21/5        | 20/4        | 19/3      | 18/2        | 17/1           | 16/0   | All Resets <sup>(3</sup> |

| 1360                       | PB7DIV                          | 31:16     | —     | _     | -     | -     | —        |       | _          | _    | _    | —    | -           |             | -         | _           | —              | _      | 0000                     |

| 1300                       | I DI DIV                        | 15:0      | ON    | _     |       |       | PBDIVRDY |       | _          | _    | —    |      |             | Р           | BDIV<6:0> | <b>`</b>    |                |        | 8800                     |

| 1370                       | PB8DIV                          | 31:16     | —     | -     | _     | _     | —        | —     | —          |      | _    | _    | —           | —           | _         | _           | _              | _      | 0000                     |

| 1370                       | FBODIV                          | 15:0      | ON    | -     | —     | —     | PBDIVRDY | —     | -          | -    | —    |      |             | Р           | BDIV<6:0> | <b>`</b>    |                |        | 8801                     |

| 13C0                       | SLEWCON                         | 31:16     | —     | _     | _     | _     | _        | _     | —          | _    | _    | —    | _           | —           |           | SYSD        | IV<3:0>        |        | 0000                     |

| 1300                       | SLEWCON                         | 15:0      | —     | —     | _     | _     | _        | S     | SLWDIV<2:0 | >    | —    | —    | —           | —           | —         | UPEN        | DNEN           | BUSY   | 0204                     |

|                            |                                 | 31:16     | —     | _     | -     | -     | _        |       | —          | _    | _    | —    | -           |             | -         | _           | _              | _      | 0000                     |

| 13D0                       | CLKSTAT                         | 15:0      | —     | _     | -     | _     | _        |       | —          | _    | _    | —    | LPRC<br>RDY | SOSC<br>RDY |           | POSC<br>RDY | SPLL<br>DIVRDY | FRCRDY | 0000                     |

Legend: x = unknown value on Reset; -- = unimplemented, read as '0'. Reset values are shown in hexadecimal.

Note 1: All registers in this table have corresponding CLR, SET, and INV registers at their virtual addresses, plus offsets of 0x4, 0x8 and 0xC, respectively. See Section 12.3 "CLR, SET, and INV Registers" for more information.

2: Reset values are dependent on the DEVCFGx Configuration bits and the type of reset.

|          |                  |               |       |       |       |       |       |       | n    |               | Bits          |           | •    | •    |      |      |      |      |

|----------|------------------|---------------|-------|-------|-------|-------|-------|-------|------|---------------|---------------|-----------|------|------|------|------|------|------|

| (BF8E_#) | Register<br>Name | Bit Range     | 31/15 | 30/14 | 29/13 | 28/12 | 27/11 | 26/10 | 25/9 | 24/8          | 23/7          | 22/6      | 21/5 | 20/4 | 19/3 | 18/2 | 17/1 | 16/0 |

| 28       | USB<br>E2CSR2    | 31:16<br>15:0 |       | •     |       | •     | •     |       | Inde | exed by the s | ame bits in U | SBIE2CSR2 | ·    | ·    |      |      | •    |      |

| 2C       | USB<br>E2CSR3    | 31:16<br>15:0 |       |       |       |       |       |       | Inde | exed by the s | ame bits in U | SBIE2CSR3 |      |      |      |      |      |      |

| 30       | USB<br>E3CSR0    | 31:16<br>15:0 |       |       |       |       |       |       | Inde | exed by the s | ame bits in U | SBIE3CSR0 |      |      |      |      |      |      |

| 34       | USB<br>E3CSR1    | 31:16<br>15:0 |       |       |       |       |       |       | Inde | exed by the s | ame bits in U | SBIE3CSR1 |      |      |      |      |      |      |

| 8        | USB<br>E3CSR2    | 31:16<br>15:0 |       |       |       |       |       |       | Inde | exed by the s | ame bits in U | SBIE3CSR2 |      |      |      |      |      |      |

| С        | USB<br>E3CSR3    | 31:16<br>15:0 |       |       |       |       |       |       | Inde | exed by the s | ame bits in U | SBIE3CSR3 |      |      |      |      |      |      |

| )        | USB<br>E4CSR0    | 31:16<br>15:0 |       |       |       |       |       |       | Inde | exed by the s | ame bits in U | SBIE4CSR0 |      |      |      |      |      |      |

| 4        | USB<br>E4CSR1    | 31:16<br>15:0 |       |       |       |       |       |       | Inde | exed by the s | ame bits in U | SBIE4CSR1 |      |      |      |      |      |      |

| 3        | USB<br>E4CSR2    | 31:16<br>15:0 |       |       |       |       |       |       | Inde | exed by the s | ame bits in U | SBIE4CSR2 |      |      |      |      |      |      |

| 2        | USB<br>E4CSR3    | 31:16<br>15:0 |       |       |       |       |       |       | Inde | exed by the s | ame bits in U | SBIE4CSR3 |      |      |      |      |      |      |

| )        | USB<br>E5CSR0    | 31:16<br>15:0 |       |       |       |       |       |       | Inde | exed by the s | ame bits in U | SBIE5CSR0 |      |      |      |      |      |      |

| 4        | USB<br>E5CSR1    | 31:16<br>15:0 |       |       |       |       |       |       | Inde | exed by the s | ame bits in U | SBIE5CSR1 |      |      |      |      |      |      |

| в        | USB<br>E5CSR2    | 31:16<br>15:0 |       |       |       |       |       |       | Inde | exed by the s | ame bits in U | SBIE5CSR2 |      |      |      |      |      |      |

| С        | USB<br>E5CSR3    | 31:16<br>15:0 |       |       |       |       |       |       | Inde | exed by the s | ame bits in U | SBIE5CSR3 |      |      |      |      |      |      |

| 0        | USB<br>E6CSR0    | 31:16<br>15:0 |       |       |       |       |       |       | Inde | exed by the s | ame bits in U | SBIE6CSR0 |      |      |      |      |      |      |

| 4        | USB<br>E6CSR1    | 31:16<br>15:0 |       |       |       |       |       |       | Inde | exed by the s | ame bits in U | SBIE6CSR1 |      |      |      |      |      |      |

| 3        | USB<br>E6CSR2    | 31:16<br>15:0 |       |       |       |       |       |       | Inde | exed by the s | ame bits in U | SBIE6CSR2 |      |      |      |      |      |      |

| С        | USB<br>E6CSR3    | 31:16<br>15:0 |       |       |       |       |       |       | Inde | exed by the s | ame bits in U | SBIE6CSR3 |      |      |      |      |      |      |

1: 2: 3: 4:

Device mode.

Host mode.

Definition for Endpoint 0 (ENDPOINT<3:0> (USBCSR<19:16>) = 0).

Definition for Endpoints 1-7 (ENDPOINT<3:0> (USBCSR<19:16>) = 1 through 7).

|              | -11 11-1.         |                   |                   |                   |                   |                   |                  |                  |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |

| 04.04        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 31:24        | —                 | _                 | _                 |                   | _                 |                   | _                | -                |

| 00.40        | R-0, HS           | R-0, HS          | R-0, HS          |

| 23:16        | EP7TXIF           | EP6TXIF           | EP5TXIF           | EP4TXIF           | EP3TXIF           | EP2TXIF           | EP1TXIF          | EP0IF            |

|              | R/W-0             | R/W-0             | R/W-1             | R-0, HS           | R-0               | R/W-0             | R-0, HC          | R/W-0            |

| 15:8         | ISOUPD            | SOFTCONN          | HSEN              | HSMODE            | RESET             | RESUME            | SUSPMODE         | SUSPEN           |

|              | _                 | —                 |                   |                   |                   |                   |                  |                  |

|              | U-0               | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |

| 7:0          |                   |                   |                   |                   | FUNC<6:0>         |                   |                  |                  |

|              |                   | —                 |                   | —                 | _                 | —                 | —                |                  |

#### REGISTER 11-1: USBCSR0: USB CONTROL STATUS REGISTER 0

| Legend:           | HS = Hardware Set | HC = Hardware Cleared     |                    |

|-------------------|-------------------|---------------------------|--------------------|

| R = Readable bit  | W = Writable bit  | U = Unimplemented bit, re | ead as '0'         |

| -n = Value at POR | '1' = Bit is set  | '0' = Bit is cleared      | x = Bit is unknown |

#### bit 31-24 Unimplemented: Read as '0'

#### bit 23-17 EP7TXIF:EP1TXIF: Endpoint 'n' TX Interrupt Flag bit

- 1 = Endpoint has a transmit interrupt to be serviced

- 0 = No interrupt event

- bit 16 EP0IF: Endpoint 0 Interrupt bit

- 1 = Endpoint 0 has an interrupt to be serviced

- 0 = No interrupt event

All EPxTX and EP0 bits are cleared when the byte is read. Therefore, these bits must be read independently from the remaining bits in this register to avoid accidental clearing.

#### bit 15 **ISOUPD:** ISO Update bit (*Device mode only; unimplemented in Host mode*)

- 1 = USB module will wait for a SOF token from the time TXPKTRDY is set before sending the packet

- 0 = No change in behavior

This bit only affects endpoints performing isochronous transfers when in *Device mode*. This bit is unimplemented in *Host mode*.

#### bit 14 SOFTCONN: Soft Connect/Disconnect Feature Selection bit

- 1 = The USB D+/D- lines are enabled and active

- 0 = The USB D+/D- lines are disabled and are tri-stated

This bit is only available in *Device mode*.

- bit 13 HSEN: Hi-Speed Enable bit

- 1 = The USB module will negotiate for Hi-Speed mode when the device is reset by the hub

- 0 = Module only operates in Full-Speed mode

- bit 12 **HSMODE:** Hi-Speed Mode Status bit

- 1 = Hi-Speed mode successfully negotiated during USB reset

- 0 = Module is not in Hi-Speed mode

In *Device mode*, this bit becomes valid when a USB reset completes. In *Host mode*, it becomes valid when the RESET bit is cleared.

#### bit 11 **RESET:** Module Reset Status bit

- 1 = Reset signaling is present on the bus

- 0 = Normal module operation

In Device mode, this bit is read-only. In Host mode, this bit is read/write.

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|

| 24.24        | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-1             | R/W-1            | R/W-0            |

| 31:24        | VBUSERRIE         | SESSRQIE          | DISCONIE          | CONNIE            | SOFIE             | RESETIE           | RESUMEIE         | SUSPIE           |

| 22.16        | R-0, HS           | R-0, HS          | R-0, HS          |

| 23:16        | VBUSERRIF         | SESSRQIF          | DISCONIF          | CONNIF            | SOFIF             | RESETIF           | RESUMEIF         | SUSPIF           |

| 15:8         | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 10.0         | —                 | —                 |                   | —                 | —                 | —                 | —                | —                |

| 7.0          | R/W-1             | R/W-1             | R/W-1             | R/W-1             | R/W-1             | R/W-1             | R/W-1            | U-0              |

| 7:0          | EP7RXIE           | EP6RXIE           | EP5RXIE           | EP4RXIE           | EP3RXIE           | EP2RXIE           | EP1RXIE          |                  |

#### REGISTER 11-3: USBCSR2: USB CONTROL STATUS REGISTER 2

| Legend:           | HS = Hardware Set |                           |                    |

|-------------------|-------------------|---------------------------|--------------------|

| R = Readable bit  | W = Writable bit  | U = Unimplemented bit, re | ead as '0'         |

| -n = Value at POR | '1' = Bit is set  | '0' = Bit is cleared      | x = Bit is unknown |

| bit 30       SESSRQIE: Session Request Interrupt Enable bit         1 = Session request interrupt is enabled         0 = Session request interrupt is disabled         bit 29       DISCONIE: Device Disconnect Interrupt Enable bit         1 = Device disconnect interrupt is enabled         0 = Device connection Interrupt is disabled         bit 28       CONNIE: Device Connection Interrupt Enable bit         1 = Device connection Interrupt is enabled         0 = Device connection interrupt is disabled         bit 27       SOFIE: Start of Frame Interrupt Enable bit         1 = Start of Frame event interrupt is disabled         bit 26       RESETIE: Reset/Babble Interrupt Enable bit         1 = Interrupt when reset (Device mode) or Babble (Host mode) is enabled         0 = Reset/Babble interrupt is disabled         bit 25       RESUMEIE: Resume Interrupt Enable bit         1 = Resume signaling interrupt is enabled         0 = Resume signaling interrupt is disabled         bit 24       SUSPIE: Suspend Interrupt Enable bit         1 = Suspend signaling interrupt is disabled |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| <ul> <li>1 = Device disconnect interrupt is enabled</li> <li>0 = Device disconnect interrupt is disabled</li> <li>bit 28 CONNIE: Device Connection Interrupt Enable bit</li> <li>1 = Device connection interrupt is enabled</li> <li>0 = Device connection interrupt is disabled</li> <li>bit 27 SOFIE: Start of Frame Interrupt Enable bit</li> <li>1 = Start of Frame event interrupt is enabled</li> <li>0 = Start of Frame event interrupt is disabled</li> <li>bit 26 RESETIE: Reset/Babble Interrupt Enable bit</li> <li>1 = Interrupt when reset (<i>Device mode</i>) or Babble (<i>Host mode</i>) is enabled</li> <li>0 = Reset/Babble interrupt Enable bit</li> <li>1 = Interrupt when reset (<i>Device mode</i>) or Babble (<i>Host mode</i>) is enabled</li> <li>0 = Reset/Babble interrupt is disabled</li> <li>bit 25 RESUMEIE: Resume Interrupt Enable bit</li> <li>1 = Resume signaling interrupt is enabled</li> <li>0 = Suspend signaling interrupt is enabled</li> <li>0 = Suspend signaling interrupt is disabled</li> <li>bit 23 VBUSERRIF: VBUS Error Interrupt bit</li> <li>1 = VBUS has dropped below the VBUS valid threshold during a session</li> </ul>                                                |

| <ul> <li>1 = Device connection interrupt is enabled</li> <li>0 = Device connection interrupt is disabled</li> <li>bit 27 SOFIE: Start of Frame Interrupt Enable bit</li> <li>1 = Start of Frame event interrupt is enabled</li> <li>0 = Start of Frame event interrupt is disabled</li> <li>bit 26 RESETIE: Reset/Babble Interrupt Enable bit</li> <li>1 = Interrupt when reset (<i>Device mode</i>) or Babble (<i>Host mode</i>) is enabled</li> <li>0 = Reset/Babble interrupt is disabled</li> <li>bit 25 RESUMEIE: Resume Interrupt Enable bit</li> <li>1 = Resume signaling interrupt is enabled</li> <li>0 = Suspend signaling interrupt is enabled</li> <li>0 = Suspend signaling interrupt is disabled</li> <li>bit 23 VBUSERRIF: VBUS Error Interrupt bit</li> <li>1 = VBUS has dropped below the VBUS valid threshold during a session</li> </ul>                                                                                                                                                                                                                                                                                                                                                                      |

| <ul> <li>1 = Start of Frame event interrupt is enabled</li> <li>0 = Start of Frame event interrupt is disabled</li> <li>bit 26 RESETIE: Reset/Babble Interrupt Enable bit</li> <li>1 = Interrupt when reset (<i>Device mode</i>) or Babble (<i>Host mode</i>) is enabled</li> <li>0 = Reset/Babble interrupt is disabled</li> <li>bit 25 RESUMEIE: Resume Interrupt Enable bit</li> <li>1 = Resume signaling interrupt is enabled</li> <li>0 = Resume signaling interrupt is disabled</li> <li>bit 24 SUSPIE: Suspend Interrupt Enable bit</li> <li>1 = Suspend signaling interrupt is enabled</li> <li>0 = Suspend signaling interrupt is disabled</li> <li>bit 23 VBUSERRIF: VBUS Error Interrupt bit</li> <li>1 = VBUS has dropped below the VBUS valid threshold during a session</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| <ul> <li>1 = Interrupt when reset (<i>Device mode</i>) or Babble (<i>Host mode</i>) is enabled</li> <li>0 = Reset/Babble interrupt is disabled</li> <li>bit 25 RESUMEIE: Resume Interrupt Enable bit</li> <li>1 = Resume signaling interrupt is enabled</li> <li>0 = Resume signaling interrupt is disabled</li> <li>bit 24 SUSPIE: Suspend Interrupt Enable bit</li> <li>1 = Suspend signaling interrupt is enabled</li> <li>0 = Suspend signaling interrupt is disabled</li> <li>bit 23 VBUSERRIF: VBUS Error Interrupt bit</li> <li>1 = VBUS has dropped below the VBUS valid threshold during a session</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| 1 = Resume signaling interrupt is enabled         0 = Resume signaling interrupt is disabled         bit 24       SUSPIE: Suspend Interrupt Enable bit         1 = Suspend signaling interrupt is enabled         0 = Suspend signaling interrupt is disabled         bit 23       VBUSERRIF: VBUS Error Interrupt bit         1 = VBUS has dropped below the VBUS valid threshold during a session                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| <ul> <li>1 = Suspend signaling interrupt is enabled</li> <li>0 = Suspend signaling interrupt is disabled</li> <li>bit 23 VBUSERRIF: VBUS Error Interrupt bit</li> <li>1 = VBUS has dropped below the VBUS valid threshold during a session</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| 1 = VBUS has dropped below the VBUS valid threshold during a session                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| bit 22 SESSRQIF: Session Request Interrupt bit<br>1 = Session request signaling has been detected<br>0 = No session request detected                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| <ul> <li>bit 21 DISCONIF: Device Disconnect Interrupt bit</li> <li>1 = In Host mode, indicates when a device disconnect is detected. In Device mode, indicates when session ends.</li> <li>0 = No device disconnect detected</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| bit 20 <b>CONNIF:</b> Device Connection Interrupt bit<br>1 = In <i>Host mode</i> , indicates when a device connection is detected<br>0 = No device connection detected                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

#### REGISTER 11-9: USBIENCSR1: USB INDEXED ENDPOINT CONTROL STATUS REGISTER 1 (ENDPOINT 1-7) (CONTINUED)

#### bit 18 **OVERRUN:** Data Overrun Status bit (*Device mode*)

- 1 = An OUT packet cannot be loaded into the RX FIFO.

- 0 = Written by software to clear this bit

This bit is only valid when the endpoint is operating in ISO mode. In Bulk mode, it always returns zero.

ERROR: No Data Packet Received Status bit (Host mode)

- 1 = Three attempts have been made to receive a packet and no data packet has been received. An interrupt is generated.

- 0 = Written by the software to clear this bit.

This bit is only valid when the RX endpoint is operating in Bulk or Interrupt mode. In ISO mode, it always returns zero.

- bit 17 FIFOFULL: FIFO Full Status bit

- 1 = No more packets can be loaded into the RX FIFO

- 0 = The RX FIFO has at least one free space

- bit 16 RXPKTRDY: Data Packet Reception Status bit

- 1 = A data packet has been received. An interrupt is generated.

- 0 = Written by software to clear this bit when the packet has been unloaded from the RX FIFO.

- bit 15-11 MULT<4:0>: Multiplier Control bits

For Isochronous/Interrupt endpoints or of packet splitting on Bulk endpoints, multiplies TXMAXP by MULT+1 for the payload size.

For Bulk endpoints, MULT can be up to 32 and defines the number of "USB" packets of the specified payload into which a single data packet placed in the FIFO should be split, prior to transfer. The data packet is required to be an exact multiple of the payload specified by TXMAXP.

For Isochronous/Interrupts endpoints operating in Hi-Speed mode, MULT may be either 2 or 3 and specifies the maximum number of such transactions that can take place in a single microframe.

#### bit 10-0 RXMAXP<10:0>: Maximum RX Payload Per Transaction Control bits

This field sets the maximum payload (in bytes) transmitted in a single transaction. The value is subject to the constraints placed by the USB Specification on packet sizes for Bulk, Interrupt and Isochronous transfers in Full-Speed and Hi-Speed operations.

RXMAXP must be set to an even number of bytes for proper interrupt generation in DMA Mode 1.

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|

| 31:24        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 31.24        | _                 | —                 |                   |                   |                   |                   |                  |                  |

| 23:16        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 23.10        | —                 | —                 | —                 | —                 | —                 | _                 | —                | —                |

| 15:8         | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 10.0         | —                 | —                 | —                 | —                 | —                 | _                 | —                | —                |

| 7:0          | R/W-0, HS         | R/W-0, HS        | R/W-0, HS        |

| 7.0          | DMA8IF            | DMA7IF            | DMA6IF            | DMA5IF            | DMA4IF            | DMA3IF            | DMA2IF           | DMA1IF           |

#### REGISTER 11-20: USBDMAINT: USB DMA INTERRUPT REGISTER

#### Legend:

| 5                 |                  |                           |                    |

|-------------------|------------------|---------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, re | ead as '0'         |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared      | x = Bit is unknown |

bit 31-8 Unimplemented: Read as '0'

bit 7-0 **DMAxIF:** DMA Channel 'x' Interrupt bit

1 = The DMA channel has an interrupt event

0 = No interrupt event

All bits are cleared on a read of the register.

# REGISTER 11-29: USBLPMR2: USB LINK POWER MANAGEMENT CONTROL REGISTER 2 (CONTINUED)

bit 0 LPMSTIF: LPM STALL Interrupt Flag bit

#### When in Device mode:

- 1 = A LPM transaction was received and the USB Module responded with a STALL

- 0 = No Stall condition

#### When in Host mode:

- 1 = A LPM transaction was transmitted and the device responded with a STALL

- 0 = No Stall condition

# 27.1 RNG Control Registers

# TABLE 27-2: RANDOM NUMBER GENERATOR (RNG) REGISTER MAP

| ess                         |                  |           |       | Bits       |       |       |          |       |        |        |       |      |      |        |          |      |      |      |            |

|-----------------------------|------------------|-----------|-------|------------|-------|-------|----------|-------|--------|--------|-------|------|------|--------|----------|------|------|------|------------|

| Virtual Address<br>(BF8E_#) | Register<br>Name | Bit Range | 31/15 | 30/14      | 29/13 | 28/12 | 27/11    | 26/10 | 25/9   | 24/8   | 23/7  | 22/6 | 21/5 | 20/4   | 19/3     | 18/2 | 17/1 | 16/0 | All Resets |

| 6000                        | RNGVER           | 31:16     |       |            |       |       |          |       |        | ID<15  | :0>   |      |      |        |          |      |      |      | xxxx       |

| 0000                        | RNOVER           | 15:0      |       |            |       | VERS  | ION<7:0> |       |        |        |       |      |      | REVISI | ON<7:0>  |      |      |      | xxxx       |

| 6004                        | RNGCON           | 31:16     | _     |            | _     |       | _        | _     | —      | _      |       | —    | —    | —      | —        |      | —    | —    | 0000       |

| 0004                        | KNOCON           | 15:0      | _     |            |       | LOAD  | TRNGMODE | CONT  | PRNGEN | TRNGEN |       |      |      | PLEI   | N<7:0>   |      |      |      | 0064       |

| 6008                        | RNGPOLY1         | 31:16     |       |            |       |       |          |       |        |        | 1.0   |      |      |        |          |      |      |      | FFFF       |

| 0000                        | RINGFOLTT        | 15:0      |       | POLY<31:0> |       |       |          |       |        |        |       | 0000 |      |        |          |      |      |      |            |

| 600C                        | RNGPOLY2         | 31:16     |       |            |       |       |          |       |        | POLY<3 | 1.0   |      |      |        |          |      |      |      | FFFF       |

| 0000                        | KNGFOLI Z        | 15:0      |       |            |       |       |          |       |        | FULIKS | 01.02 |      |      |        |          |      |      |      | 0000       |

| 6010                        | RNGNUMGEN1       | 31:16     |       |            |       |       |          |       |        | RNG<3  | 1.0>  |      |      |        |          |      |      |      | FFFF       |

| 0010                        | RINGINOWIGEINT   | 15:0      |       |            |       |       |          |       |        | KNOC3  | 1.0>  |      |      |        |          |      |      |      | FFFF       |

| 6014                        | RNGNUMGEN2       | 31:16     |       |            |       |       |          |       |        | DNC -2 | 1.0.  |      |      |        |          |      |      |      | FFFF       |

| 0014                        | RINGINUWIGEINZ   | 15:0      |       | RNG<31:0>  |       |       |          |       |        |        |       | FFFF |      |        |          |      |      |      |            |

| 6018                        | RNGSEED1         | 31:16     |       | 0000       |       |       |          |       |        |        |       | 0000 |      |        |          |      |      |      |            |

| 6018                        | RINGSEEDT        | 15:0      |       | SEED<31:0> |       |       |          |       |        |        |       | 0000 |      |        |          |      |      |      |            |

| 6010                        | RNGSEED2         | 31:16     |       | 000        |       |       |          |       |        |        |       |      | 0000 |        |          |      |      |      |            |

| 601C                        | RINGSEED2        | 15:0      |       | SEED<31:0> |       |       |          |       |        |        |       | 0000 |      |        |          |      |      |      |            |

| 6020                        | RNGCNT           | 31:16     | —     | —          | —     | —     | —        | —     | —      | —      | —     | —    | —    | —      | —        | —    | —    | —    | 0000       |

| 6020                        | RINGCINI         | 15:0      | _     | —          | —     | _     | —        | _     | —      | —      | _     |      |      |        | RCNT<6:0 | >    |      |      | 0000       |

Legend: x = unknown value on Reset; -- = unimplemented, read as '0'. Reset values are shown in hexadecimal.

| REGISTER | R 28-5: ADCIMCON1: ADC INPUT MODE CONTROL REGISTER 1 (CONTINUED) |

|----------|------------------------------------------------------------------|

| bit 20   | SIGN10: AN10 Signed Data Mode bit                                |

|          | 1 = AN10 is using Signed Data mode                               |

|          | 0 = AN10 is using Unsigned Data mode                             |

| bit 19   | DIFF9: AN9 Mode bit                                              |

| 2.1.10   | 1 = AN9 is using Differential mode                               |

|          | 0 = AN9 is using Single-ended mode                               |

| bit 18   | SIGN9: AN9 Signed Data Mode bit                                  |

| DIL TO   | 1 = AN9 is using Signed Data mode                                |

|          | 0 = AN9 is using Unsigned Data mode                              |

| bit 17   | DIFF8: AN 8 Mode bit                                             |

|          | 1 = AN8 is using Differential mode                               |

|          | 0 = AN8 is using Single-ended mode                               |

| bit 16   | SIGN8: AN8 Signed Data Mode bit                                  |

| DICTO    | •                                                                |

|          | 1 = AN8 is using Signed Data mode                                |

| 1.1.4.F  | 0 = AN8 is using Unsigned Data mode                              |

| bit 15   | DIFF7: AN7 Mode bit                                              |

|          | 1 = AN7 is using Differential mode                               |

|          | 0 = AN7 is using Single-ended mode                               |

| bit 14   | SIGN7: AN7 Signed Data Mode bit                                  |

|          | 1 = AN7 is using Signed Data mode                                |

|          | 0 = AN7 is using Unsigned Data mode                              |

| bit 13   | DIFF6: AN6 Mode bit                                              |

|          | 1 = AN6 is using Differential mode                               |

|          | 0 = AN6 is using Single-ended mode                               |

| bit 12   | SIGN6: AN6 Signed Data Mode bit                                  |

|          | 1 = AN6 is using Signed Data mode                                |

|          | 0 = AN6 is using Unsigned Data mode                              |

| bit 11   | DIFF5: AN5 Mode bit                                              |

|          | 1 = AN5 is using Differential mode                               |

|          | 0 = AN5 is using Single-ended mode                               |

| bit 10   | SIGN5: AN5 Signed Data Mode bit                                  |

|          | 1 = AN5 is using Signed Data mode                                |

|          | 0 = AN5 is using Unsigned Data mode                              |