Welcome to E-XFL.COM

Microchip Technology - PIC32MZ0512EFE064T-I/PT Datasheet

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Details                    |                                                                                   |

|----------------------------|-----------------------------------------------------------------------------------|

| Product Status             | Active                                                                            |

| Core Processor             | MIPS32® M-Class                                                                   |

| Core Size                  | 32-Bit Single-Core                                                                |

| Speed                      | 200MHz                                                                            |

| Connectivity               | Ethernet, I <sup>2</sup> C, PMP, SPI, SQI, UART/USART, USB OTG                    |

| Peripherals                | Brown-out Detect/Reset, DMA, I <sup>2</sup> S, POR, PWM, WDT                      |

| Number of I/O              | 46                                                                                |

| Program Memory Size        | 512KB (512K x 8)                                                                  |

| Program Memory Type        | FLASH                                                                             |

| EEPROM Size                |                                                                                   |

| RAM Size                   | 128K x 8                                                                          |

| Voltage - Supply (Vcc/Vdd) | 2.1V ~ 3.6V                                                                       |

| Data Converters            | A/D 24x12b                                                                        |

| Oscillator Type            | Internal                                                                          |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                                 |

| Mounting Type              | Surface Mount                                                                     |

| Package / Case             | 64-TQFP                                                                           |

| Supplier Device Package    | 64-TQFP (10x10)                                                                   |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic32mz0512efe064t-i-pt |

|                            |                                                                                   |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

## REGISTER 5-1: NVMCON: FLASH PROGRAMMING CONTROL REGISTER (CONTINUED)

bit 6 **BFSWAP:** Boot Flash Bank Alias Swap Control bit

This bit is only writable when WREN = 0 and the unlock sequence has been performed.

- 1 = Boot Flash Bank 2 is mapped to the lower boot alias and boot Flash Bank 1 is mapped to the upper boot alias

- 0 = Boot Flash Bank 1 is mapped to the lower boot alias and boot Flash Bank 2 is mapped to the upper boot alias

- bit 5-4 Unimplemented: Read as '0'

- bit 3-0 **NVMOP<3:0>:** NVM Operation bits

These bits are only writable when WREN = 0.

1111 = Reserved

1000 = Reserved

- 0111 = Program erase operation: erase all of program Flash memory (all pages must be unprotected, PWP<23:0> = 0x000000)

- 0110 = Upper program Flash memory erase operation: erases only the upper mapped region of program Flash (all pages in that region must be unprotected)

- 0101 = Lower program Flash memory erase operation: erases only the lower mapped region of program Flash (all pages in that region must be unprotected)

- 0100 = Page erase operation: erases page selected by NVMADDR, if it is not write-protected

- 0011 = Row program operation: programs row selected by NVMADDR, if it is not write-protected

- 0010 = Quad Word (128-bit) program operation: programs the 128-bit Flash word selected by NVMADDR, if it is not write-protected

- 0001 = Word program operation: programs word selected by NVMADDR, if it is not write-protected<sup>(2)</sup> 0000 = No operation

- Note 1: These bits are only reset by a Power-on Reset (POR) and are not affected by other reset sources.

- 2: This operation results in a "no operation" (NOP) when the Dynamic Flash ECC Configuration bits = 00 (FECCCON<1:0> (DVCFG0<9:8>)), which enables ECC at all times. For all other FECCCON<1:0> bit settings, this command will execute, but will not write the ECC bits for the word and can cause DED errors if dynamic Flash ECC is enabled (FECCCON<1:0> = 01). Refer to Section 52. "Flash Program Memory with Support for Live Update" (DS60001193) for information regarding ECC and Flash programming.

#### **TABLE 7-3**: **INTERRUPT REGISTER MAP (CONTINUED)**

| ress<br>()                  |                                 | a         |       |       |       |       |       | -     |      | Bi         | ts   |      |      |      |      |      |       |        | s          |

|-----------------------------|---------------------------------|-----------|-------|-------|-------|-------|-------|-------|------|------------|------|------|------|------|------|------|-------|--------|------------|

| Virtual Address<br>(BF81_#) | Register<br>Name <sup>(1)</sup> | Bit Range | 31/15 | 30/14 | 29/13 | 28/12 | 27/11 | 26/10 | 25/9 | 24/8       | 23/7 | 22/6 | 21/5 | 20/4 | 19/3 | 18/2 | 17/1  | 16/0   | All Resets |

| 0010                        | OFF183                          | 31:16     | —     | —     | -     | —     | —     | -     | —    | -          | —    | —    | —    | —    | —    | —    | VOFF< | 17:16> | 0000       |

| 0010                        | 066103                          | 15:0      |       |       |       |       |       |       |      | VOFF<15:1> |      |      |      |      |      |      |       | —      | 0000       |

| 0020                        | OFF184                          | 31:16     | —     | —     | —     | _     |       |       |      |            | —    |      | _    |      | —    |      | VOFF< | 17:16> | 0000       |

| 0620                        | UFF 164                         | 15:0      |       |       |       |       |       |       |      | VOFF<15:1> |      |      |      |      |      |      |       | _      | 0000       |

| 0824                        | OFF185 <sup>(2)</sup>           | 31:16     |       | —     | -     | —     | _     | —     | —    | —          | _    | —    | —    | —    | —    | —    | VOFF< | 17:16> | 0000       |

| 0024                        | 011103                          | 15:0      |       |       |       |       |       |       |      | VOFF<15:1> |      |      |      |      |      |      |       | —      | 0000       |

| 0828                        | OFF186 <sup>(2)</sup>           | 31:16     | _     | —     | —     | —     | _     | -     | -    | _          | _    |      | —    | -    | —    | -    | VOFF< | 17:16> | 0000       |

| 0020                        | 011100                          | 15:0      |       | -     | -     | -     |       |       |      | VOFF<15:1> |      |      | -    |      |      |      |       | —      | 0000       |

| 0820                        | OFF187 <sup>(2)</sup>           | 31:16     |       | —     | -     | —     | _     | —     | —    | —          | _    | —    | —    | —    | —    | —    | VOFF< | 17:16> | 0000       |

| 0020                        | 01110/                          | 15:0      |       |       |       |       |       |       |      | VOFF<15:1> |      |      |      |      |      |      |       | —      | 0000       |

| 0830                        | OFF188                          | 31:16     |       | —     | -     | —     | _     | —     | —    | —          | _    | —    | —    | —    | —    | —    | VOFF< | 17:16> | 0000       |

| 0000                        | 011100                          | 15:0      |       | -     | -     | -     |       |       |      | VOFF<15:1> |      |      | -    |      |      |      |       | —      | 0000       |

| 0834                        | OFF189                          | 31:16     | —     | —     | —     | —     | —     | —     | —    | —          | —    | —    | —    | —    | —    | —    | VOFF< | 17:16> | 0000       |

| 0004                        | 011103                          | 15:0      |       |       |       |       |       |       |      | VOFF<15:1> |      |      |      |      |      |      |       | —      | 0000       |

| 0838                        | OFF190                          | 31:16     | —     | —     | —     | —     | —     | —     | —    | —          | —    | —    | —    | —    | —    | —    | VOFF< | 17:16> | 0000       |

| 0000                        | 011130                          | 15:0      |       | -     | -     | -     |       |       |      | VOFF<15:1> |      |      | -    |      |      |      |       | —      | 0000       |

| 0840                        | OFF192                          | 31:16     | —     | —     | —     | —     | —     | —     | —    | —          | —    | —    | —    | —    | —    | —    | VOFF< | 17:16> | 0000       |

| 0040                        | 011132                          | 15:0      |       |       |       |       |       |       |      | VOFF<15:1> |      |      |      |      |      |      |       | —      | 0000       |

| 0844                        | OFF193                          | 31:16     | —     | —     | —     | —     | —     | —     | —    | —          | —    | —    | —    | —    | —    | —    | VOFF< | 17:16> | 0000       |

| 0011                        | 011100                          | 15:0      |       |       | -     |       |       |       |      | VOFF<15:1> |      |      |      |      |      |      |       | —      | 0000       |

| 0848                        | OFF194                          | 31:16     | —     | —     | -     | —     | —     | —     | —    | —          | —    | —    | —    | —    | —    | —    | VOFF< | 17:16> | 0000       |

| 0040                        | 011104                          | 15:0      |       |       |       |       |       |       |      | VOFF<15:1> |      |      |      |      |      |      |       | —      | 0000       |

| 0850                        | OFF196                          | 31:16     | —     | —     | —     | —     |       | —     | —    |            | —    | —    | —    | —    | —    | —    | VOFF< | 17:16> | 0000       |

| 0050                        | 011130                          | 15:0      |       |       |       |       |       |       |      | VOFF<15:1> |      |      |      |      |      |      |       | —      | 0000       |

| 0858                        | OFF198                          | 31:16     | —     | —     | —     | _     |       | _     | —    |            | —    | —    | _    | —    | —    | _    | VOFF< | 17:16> | 0000       |

| 0000                        | 011100                          | 15:0      |       |       |       |       |       |       |      | VOFF<15:1> |      |      |      |      |      |      |       | —      | 0000       |

| 0850                        | OFF199                          | 31:16     | _     | —     | —     | —     | _     | —     | —    | _          | _    | —    | —    | —    | —    | —    | VOFF< | 17:16> | 0000       |

| 0000                        | 0.1100                          | 15:0      |       |       |       |       |       |       |      | VOFF<15:1> |      |      |      |      |      |      |       | —      | 0000       |

| 0860                        | OFF200                          | 31:16     | _     | —     | -     | —     | —     | —     | —    | —          | —    | —    | —    | —    | —    | —    | VOFF< | 17:16> | 0000       |

| 0000                        | 011200                          | 15:0      |       |       |       |       |       |       |      | VOFF<15:1> |      |      |      |      |      |      |       | —      | 0000       |

© 2015-2016 Microchip Technology Inc.

Legend: x = unknown value on Reset; — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

Note 1: All registers in this table with the exception of the OFFx registers, have corresponding CLR, SET, and INV registers at their virtual addresses, plus offsets of 0x4, 0x8 and 0xC, respectively. See Section 12.3 "CLR, SET, and INV **Registers**" for more information. This bit or register is not available on 64-pin devices.

2:

This bit or register is not available on devices without a CAN module. 3:

4: This bit or register is not available on 100-pin devices.

Bits 31 and 30 are not available on 64-pin and 100-pin devices; bits 29 through 14 are not available on 64-pin devices. 5:

Bits 31, 30, 29, and bits 5 through 0 are not available on 64-pin and 100-pin devices; bit 31 is not available on 124-pin devices; bit 22 is not available on 64-pin devices. 6:

7: This bit or register is not available on devices without a Crypto module.

This bit or register is not available on 124-pin devices. 8:

# 8.0 OSCILLATOR CONFIGURATION

| Note: | This data sheet summarizes the           |

|-------|------------------------------------------|

|       | features of the PIC32MZ EF family of     |

|       | devices. It is not intended to be a      |

|       | comprehensive reference source. To       |

|       | complement the information in this data  |

|       | sheet, refer to Section 42. "Oscillators |

|       | with Enhanced PLL" (DS60001250) in       |

|       | the "PIC32 Family Reference Manual",     |

|       | which is available from the Microchip    |

|       | web site (www.microchip.com/PIC32).      |

The PIC32MZ EF oscillator system has the following modules and features:

- A total of five external and internal oscillator options as clock sources

- On-Chip PLL with user-selectable input divider, multiplier and output divider to boost operating frequency on select internal and external oscillator sources

- On-Chip user-selectable divisor postscaler on select oscillator sources

- Software-controllable switching between various clock sources

- A Fail-Safe Clock Monitor (FSCM) that detects clock failure and permits safe application recovery or shutdown with dedicated Back-up FRC (BFRC)

- Dedicated On-Chip PLL for USB peripheral

- Flexible reference clock output

- Multiple clock branches for peripherals for better performance flexibility

- · Clock switch/slew control with output divider

A block diagram of the oscillator system is shown in Figure 8-1. The clock distribution is provided in Table 8-1.

Note: Devices that support 252 MHz operation should be configured for SYSCLK <= 200 MHz operation. Adjust the dividers of the PBCLKs, and then increase the SYSCLK to the desired speed.

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5      | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0     |

|--------------|-------------------|-------------------|------------------------|-------------------|-------------------|-------------------|------------------|----------------------|

| 24.24        | U-0               | U-0               | U-0                    | U-0               | U-0               | R/W-0             | R/W-0            | R/W-0                |

| 31:24        | —                 | _                 | —                      | —                 | —                 | F                 | RCDIV<2:0>       |                      |

| 22.16        | R/W-0             | U-0               | R/W-y                  | U-0               | U-0               | U-0               | U-0              | U-0                  |

| 23:16        | DRMEN             | _                 | SLP2SPD <sup>(1)</sup> | _                 | _                 | _                 | _                | _                    |

| 45.0         | U-0               | R-0               | R-0                    | R-0               | U-0               | R/W-y             | R/W-y            | R/W-y                |

| 15:8         | —                 |                   | COSC<2:0>              |                   | _                 |                   | NOSC<2:0>        |                      |

| 7.0          | R/W-0             | U-0               | U-0                    | R/W-0             | R/W-0, HS         | U-0               | R/W-y            | R/W-y                |

| 7:0          | CLKLOCK           | _                 | —                      | SLPEN             | CF                | _                 | SOSCEN           | OSWEN <sup>(1)</sup> |

#### REGISTER 8-1: OSCCON: OSCILLATOR CONTROL REGISTER

| Legend:           | y = Value set from Config | uration bits on POR       | HS = Hardware Set  |

|-------------------|---------------------------|---------------------------|--------------------|

| R = Readable bit  | W = Writable bit          | U = Unimplemented bit, re | ad as '0'          |

| -n = Value at POR | '1' = Bit is set          | '0' = Bit is cleared      | x = Bit is unknown |

#### bit 31-27 Unimplemented: Read as '0'

- bit 26-24 FRCDIV<2:0>: Internal Fast RC (FRC) Oscillator Clock Divider bits

- 111 = FRC divided by 256 110 = FRC divided by 64

- 101 = FRC divided by 32

- 100 = FRC divided by 16

- 011 = FRC divided by 8

- 010 = FRC divided by 4

- 001 = FRC divided by 2

- 000 = FRC divided by 1 (default setting)

- bit 23 **DRMEN:** Dream Mode Enable bit

- 1 = Dream mode is enabled

- 0 = Dream mode is disabled

- bit 22 Unimplemented: Read as '0'

- bit 21 SLP2SPD: Sleep 2-speed Startup Control bit<sup>(1)</sup>

- 1 = Use FRC as SYSCLK until selected clock is ready

- 0 = Use the selected clock directly

- bit 20-15 Unimplemented: Read as '0'

- bit 14-12 COSC<2:0>: Current Oscillator Selection bits

- 111 = Internal Fast RC (FRC) Oscillator divided by FRCDIV<2:0> bits (FRCDIV)

- 110 = Back-up Fast RC (BFRC) Oscillator

- 101 = Internal Low-Power RC (LPRC) Oscillator

- 100 = Secondary Oscillator (Sosc)

- 011 = Reserved

- 010 = Primary Oscillator (Posc) (HS or EC)

- 001 = System PLL (SPLL)

- 000 = Internal Fast RC (FRC) Oscillator divided by FRCDIV<2:0> bits (FRCDIV)

- bit 11 Unimplemented: Read as '0'

- **Note 1:** The reset value for this bit depends on the setting of the IESO bit (DEVCFG1<7>). When IESO = 1, the reset value is '1'. When IESO = 0, the reset value is '0'.

- Note: Writes to this register require an unlock sequence. Refer to Section 42. "Oscillators with Enhanced PLL" (DS60001250) in the "PIC32 Family Reference Manual" for details.

# 9.1 Prefetch Control Registers

## TABLE 9-1: PREFETCH REGISTER MAP

| ess (                       | _                               | ø         |       |       |       |       |        |          |      | Bit  | s    |      |       |        |          |      |          |      | s         |

|-----------------------------|---------------------------------|-----------|-------|-------|-------|-------|--------|----------|------|------|------|------|-------|--------|----------|------|----------|------|-----------|

| Virtual Address<br>(BF8E_#) | Register<br>Name <sup>(1)</sup> | Bit Range | 31/15 | 30/14 | 29/13 | 28/12 | 27/11  | 26/10    | 25/9 | 24/8 | 23/7 | 22/6 | 21/5  | 20/4   | 19/3     | 18/2 | 17/1     | 16/0 | All Reset |

|                             | PPEOON                          | 31:16     | _     | _     | _     | —     | —      | PFMSECEN | _    | _    | _    | _    | _     | _      | _        | _    | _        | _    | 0000      |

| 0000                        | PRECON                          | 15:0      | _     | —     | _     | _     | _      | _        | _    | _    | _    | _    | PREFE | N<1:0> | —        | P    | FMWS<2:0 | >    | 0007      |

| 0010                        | DDEOTAT                         | 31:16     | _     | _     | _     | _     | PFMDED | PFMSEC   | _    |      | _    | _    | _     | _      | _        | _    |          | _    | 0000      |

| 0010                        | PRESTAT                         | 15:0      | _     |       |       | —     | —      | _        |      | _    |      |      |       | PFMSEC | CNT<7:0> |      |          |      | 0000      |

Legend: x = unknown value on Reset, — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

Note 1: All registers in this table have corresponding CLR, SET and INV registers at its virtual address, plus an offset of 0x4, 0x8 and 0xC, respectively. See Section 12.3 "CLR, SET, and INV Registers" for more information.

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |  |  |  |  |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|--|--|--|--|

| 24.24        | U-0               | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |  |  |  |

| 31:24        | _                 |                   |                   | Tک                | (HUBPRT<6:        | 0>                |                  |                  |  |  |  |  |

| 23:16        | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |  |  |  |

| 23.10        | MULTTRAN          |                   |                   | ТХ                | (HUBADD<6:        | 0>                |                  |                  |  |  |  |  |

| 15:8         | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |  |  |  |  |

| 15.0         | _                 | _                 | _                 | _                 | _                 | _                 | _                | —                |  |  |  |  |

| 7.0          | U-0               | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |  |  |  |

| 7:0          | _                 | TXFADDR<6:0>      |                   |                   |                   |                   |                  |                  |  |  |  |  |

#### REGISTER 11-18: USBExTXA: USB ENDPOINT 'x' TRANSMIT ADDRESS REGISTER

## I agand.

| Legena:           |                  |                      |                    |

|-------------------|------------------|----------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bi | t, read as '0'     |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared | x = Bit is unknown |

#### bit 31 Unimplemented: Read as '0'

bit 30-24 **TXHUBPRT<6:0>:** TX Hub Port bits (Host mode) When a Low-Speed or Full-Speed device is connected to this endpoint through a Hi-Speed USB 2.0 hub, this field records the port number of that USB 2.0 hub.

- bit 23 MULTTRAN: TX Hub Multiple Translators bit (Host mode) 1 = The USB 2.0 hub has multiple transaction translators

- 0 = The USB 2.0 hub has a single transaction translator

bit 22-16 **TXHUBADD<6:0>:** TX Hub Address bits (Host mode) When a Low-Speed or Full-Speed device is connected to this endpoint through a Hi-Speed USB 2.0 hub, these bits record the address of the USB 2.0 hub.

bit 15-7 Unimplemented: Read as '0'

#### bit 6-0 TXFADDR<6:0>: TX Functional Address bits (Host mode)

Specifies the address for the target function that is be accessed through the associated endpoint. It needs to be defined for each TX endpoint that is used.

| SSS                         |                  |           |       |       |       |       |       |       |      | B    | its  |      |      |      |      |       |        |      |            |

|-----------------------------|------------------|-----------|-------|-------|-------|-------|-------|-------|------|------|------|------|------|------|------|-------|--------|------|------------|

| Virtual Address<br>(BF80_#) | Register<br>Name | Bit Range | 31/15 | 30/14 | 29/13 | 28/12 | 27/11 | 26/10 | 25/9 | 24/8 | 23/7 | 22/6 | 21/5 | 20/4 | 19/3 | 18/2  | 17/1   | 16/0 | All Resets |

| 4444                        | IC4R             | 31:16     | —     | —     | -     | —     | -     | —     | —    | —    | —    | -    | —    | —    | —    | —     | -      | —    | 0000       |

| 1444                        | IC4R             | 15:0      |       | _     | —     | _     |       | _     | _    | _    | _    | —    | —    | —    |      | IC4R  | <3:0>  |      | 0000       |

| 1448                        | IC5R             | 31:16     |       | —     | —     | _     |       | —     | —    |      | —    | _    | _    | _    | _    | _     | _      |      | 0000       |

| 1440                        | 10.51            | 15:0      |       | —     | —     | —     |       | —     | —    | —    | _    | _    | —    | —    |      | IC5R  | <3:0>  |      | 0000       |

| 144C                        | IC6R             | 31:16     | —     | —     | —     | —     | —     | —     | —    | —    | —    | —    | —    | —    | —    | —     | —      | —    | 0000       |

| 1440                        | ICOIX            | 15:0      | —     | —     | —     | —     | —     | —     | —    | —    | —    | —    | —    | —    |      | IC6R  | <3:0>  |      | 0000       |

| 1450                        | IC7R             | 31:16     | —     | —     | —     | —     | —     | —     | —    | —    | —    | —    | —    | —    | —    | —     | —      | —    | 0000       |

| 1430                        | 10/10            | 15:0      | _     | _     | —     | —     | _     | _     | —    | _    | _    | —    | _    | —    |      | IC7R  | <3:0>  |      | 0000       |

| 1454                        | IC8R             | 31:16     | -     | —     | —     | —     | —     | —     | —    | —    | —    | —    | —    | —    | —    | —     | —      | —    | 0000       |

| 1-0-1                       | 10011            | 15:0      | -     | —     | —     | —     | —     | —     | —    | —    | —    | —    | —    | —    |      | IC8R  | <3:0>  |      | 0000       |

| 1458                        | IC9R             | 31:16     | -     | —     | —     | —     | _     | —     | —    | _    | _    | —    | _    | —    | —    | —     | —      | —    | 0000       |

|                             |                  | 15:0      | -     | —     |       | —     | _     | _     | —    | —    | _    |      |      | _    |      | IC9R  | <3:0>  |      | 0000       |

| 1460                        | OCFAR            | 31:16     | _     | —     |       | —     | —     | —     | —    | _    | —    | _    | —    | —    | —    | —     | —      | —    | 0000       |

|                             |                  | 15:0      | _     | —     |       | —     |       | —     | —    |      | _    | —    | —    | —    |      | OCFA  | R<3:0> |      | 0000       |

| 1468                        | U1RXR            | 31:16     | _     | —     | _     | —     | _     | —     | —    | —    | _    | _    |      | _    |      | —     | —      | —    | 0000       |

|                             |                  | 15:0      | _     | —     | _     | —     | _     | —     | —    | —    | _    | _    |      | _    |      | U1RXI | R<3:0> |      | 0000       |

| 146C                        | U1CTSR           | 31:16     | _     |       |       | —     | _     | —     | —    | —    | _    |      |      | —    | —    | —     | —      | —    | 0000       |

|                             |                  | 15:0      | —     | —     | _     | —     | _     | —     | —    | —    | —    | —    | —    | —    |      | U1CTS |        |      | 0000       |

| 1470                        | U2RXR            | 31:16     | _     | —     |       | _     | _     | —     | —    | —    | _    | —    | _    | —    | —    | —     | —      | —    | 0000       |

|                             |                  | 15:0      | _     | —     | -     | —     | —     | —     | —    | _    | _    | —    | —    | —    |      | U2RXI |        |      | 0000       |

| 1474                        | U2CTSR           | 31:16     | _     | _     |       |       | _     | _     | _    |      | _    |      | _    | _    | _    |       | —      | —    | 0000       |

|                             |                  | 15:0      | _     | _     | -     | _     | _     | _     | _    | _    | _    | _    | _    | _    |      | U2CTS |        |      | 0000       |

| 1478                        | <b>U3RXR</b>     | 31:16     | _     |       | -     | _     | _     |       | _    | _    | _    | —    |      | _    | —    |       | —      | —    | 0000       |

|                             |                  | 15:0      |       | _     |       | _     |       | _     | _    | _    | _    | _    |      | _    |      | U3RXI |        |      | 0000       |

| 147C                        | <b>U3CTSR</b>    | 31:16     | _     | _     |       | _     | _     | _     | _    | _    | _    |      |      | _    | —    |       | —      | —    | 0000       |

|                             |                  | 15:0      |       | _     |       | _     |       | _     | _    | _    | _    | _    | _    | _    |      | U3CTS | R<3:0> |      | 0000       |

| 1480                        | U4RXR            | 31:16     |       | —     | _     | _     | _     |       | _    |      | _    | _    | _    | _    |      |       |        | _    | 0000       |

|                             |                  | 15:0      |       | —     |       | _     | _     |       | —    |      | _    | _    | _    | _    |      | U4RXI |        |      | 0000       |

| 1484                        | U4CTSR           | 31:16     |       | —     |       | _     | _     |       | —    |      | _    | _    | _    | _    |      | -     | —      | _    | 0000       |

|                             |                  | 15:0      |       | —     | —     | —     | -     | —     | —    | —    | —    |      | _    | —    |      | U4CTS | R<3:0> |      | 0000       |

## TABLE 12-22: PERIPHERAL PIN SELECT INPUT REGISTER MAP (CONTINUED)

x = unknown value on Reset; --- = unimplemented, read as '0'. Reset values are shown in hexadecimal.

Note 1: This register is not available on 64-pin devices.

2: This register is not available on devices without a CAN module.

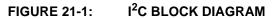

## TABLE 21-1: I2C1 THROUGH I2C5 REGISTER MAP (CONTINUED)

| SSS                         |                                 |           |         | Bits   |        |        |        |       |            |            |            |       |            |              |          |       |      |      |            |

|-----------------------------|---------------------------------|-----------|---------|--------|--------|--------|--------|-------|------------|------------|------------|-------|------------|--------------|----------|-------|------|------|------------|

| Virtual Address<br>(BF82_#) | Register<br>Name <sup>(1)</sup> | Bit Range | 31/15   | 30/14  | 29/13  | 28/12  | 27/11  | 26/10 | 25/9       | 24/8       | 23/7       | 22/6  | 21/5       | 20/4         | 19/3     | 18/2  | 17/1 | 16/0 | All Resets |

| 0430                        | I2C3MSK                         | 31:16     | _       | —      | —      | —      | _      | _     | —          | _          | _          | —     | _          | _            | _        | _     |      | _    | 0000       |

| 0 100                       | 1200111011                      | 15:0      | —       | —      |        | —      | _      | —     |            |            |            |       | Address Ma | sk Register  | •        |       |      |      | 0000       |

| 0440                        | I2C3BRG                         | 31:16     | —       | —      | —      | —      | —      | _     | —          | —          | —          |       | —          | —            | _        | —     | —    | —    | 0000       |

|                             |                                 | 15:0      |         |        |        |        |        |       |            | d Rate Gen | erator Reg | ister |            |              |          |       |      |      | 0000       |

| 0450                        | I2C3TRN                         | 31:16     | _       | —      |        | —      | —      | —     | —          |            | —          | —     | —          |              |          | —     | —    | —    | 0000       |

|                             |                                 | 15:0      | _       | _      |        | —      | _      | _     | —          | _          |            |       |            | Transmit     | Register | -     |      |      | 0000       |

| 0460                        | I2C3RCV                         | 31:16     | —       |        |        | _      | _      | _     | _          | _          | _          | —     | _          | _            | _        | _     | —    | —    | 0000       |

|                             |                                 | 15:0      | —       | —      |        | _      | _      | _     | _          |            |            | 1     |            | Receive      |          | 1     |      |      | 0000       |

| 0600                        | I2C4CON                         | 31:16     | —       | —      |        | —      | —      | —     | —          | _          | —          | PCIE  | SCIE       | BOEN         | SDAHT    | SBCDE | AHEN | DHEN | 0000       |

|                             |                                 | 15:0      | ON      |        | SIDL   | SCLREL | STRICT | A10M  | DISSLW     | SMEN       | GCEN       | STREN | ACKDT      | ACKEN        | RCEN     | PEN   | RSEN | SEN  | 1000       |

| 0610                        | I2C4STAT                        | 31:16     | —       | —      | —      | —      |        | —     | —          | _          | —          | —     | —          | —            | —        | —     | —    | —    | 0000       |

|                             |                                 | 15:0      | ACKSTAT | TRSTAT | ACKTIM | —      | —      | BCL   | GCSTAT     | ADD10      | IWCOL      | I2COV | D/A        | Р            | S        | R/W   | RBF  | TBF  | 0000       |

| 0620                        | I2C4ADD                         | 31:16     | _       | —      |        | —      |        |       | —          | _          | _          | —     | —          | —            | —        | —     | —    | —    | 0000       |

|                             |                                 | 15:0      | _       |        |        |        |        |       |            |            |            |       |            | 0000         |          |       |      |      |            |

| 0630                        | I2C4MSK                         | 31:16     |         |        |        |        |        |       |            |            |            |       | 0000       |              |          |       |      |      |            |

|                             |                                 | 15:0      | _       | —      | -      | —      | —      | —     |            |            |            |       | Address Ma | isk Register |          | -     |      |      | 0000       |

| 0640                        | I2C4BRG                         | 31:16     | —       | _      | _      |        | _      | _     | _          | -          | _          | —     | _          | _            | _        | _     | _    | —    | 0000       |

|                             |                                 | 15:0      |         |        |        |        |        |       | Bau        | d Rate Gen | erator Reg | ister |            |              |          |       |      |      | 0000       |

| 0650                        | I2C4TRN                         | 31:16     | _       |        |        |        | _      |       | _          | _          | _          | —     | _          | -            |          | —     | _    | _    | 0000       |

|                             |                                 | 15:0      | —       | _      |        |        | _      | —     | _          |            |            |       |            | Transmit     | Register |       |      |      | 0000       |

| 0660                        | I2C4RCV                         | 31:16     | _       |        | -      | _      | _      | _     | _          | _          | _          | _     | —          |              |          | —     | —    | —    | 0000       |

|                             |                                 | 15:0      | _       |        | -      | _      | _      | _     | _          | _          |            |       |            | Receive      |          |       |      |      | 0000       |

| 0800                        | I2C5CON                         | 31:16     |         | -      | —      | —      | —      | _     | —          | _          | _          | PCIE  | SCIE       | BOEN         | SDAHT    | SBCDE | AHEN | DHEN | 0000       |

|                             |                                 | 15:0      | ON      |        | SIDL   | SCLREL | STRICT | A10M  | DISSLW     | SMEN       | GCEN       | STREN | ACKDT      | ACKEN        | RCEN     | PEN   | RSEN | SEN  | 1000       |

| 0810                        | I2C5STAT                        | 31:16     | -       | -      | -      |        |        | -     | -          | -          | -          | -     | -          | _            | _        | —     | -    | -    | 0000       |

|                             |                                 | 15:0      | ACKSTAT | TRSTAT | ACKTIM |        |        | BCL   | GCSTAT     | ADD10      | IWCOL      | I2COV | D/A        | Р            | S        | R/W   | RBF  | TBF  | 0000       |

| 0820                        | I2C5ADD                         | 31:16     | _       |        |        |        |        |       | _          | _          | _          | _     |            |              | _        | —     | _    | _    | 0000       |

|                             |                                 | 15:0      | _       |        |        |        |        |       |            |            |            |       | Address    | Register     |          |       |      |      | 0000       |

| 0830                        | I2C5MSK                         | 31:16     | _       |        |        |        |        |       | _          | _          | _          | _     |            |              | _        | —     | _    | _    | 0000       |

|                             |                                 | 15:0      | _       |        |        |        |        |       |            |            |            |       | Address Ma | isk Register | -        |       |      |      | 0000       |

| 0840                        | I2C5BRG                         | 31:16     | —       | —      | —      | —      | —      | _     | — — —      | - Data O   | -          | —     | —          | —            | —        | —     | -    | —    | 0000       |

|                             |                                 | 15:0      |         |        |        |        |        |       | Bau        | d Rate Gen | erator Reg | Ister |            |              |          |       |      |      | 0000       |

| 0850                        | I2C5TRN                         | 31:16     |         |        | _      | —      | _      | _     | —          |            | _          | —     | —          |              | —        | —     | -    | —    | 0000       |

|                             |                                 | 15:0      | _       | —      | _      | —      | —      | —     | —          | _          |            |       |            | Transmit     | Register | _     |      |      | 0000       |

| 0860                        | I2C5RCV                         | 31:16     | _       | _      |        | —      | _      |       | _          | _          | —          | _     | —          | - Dessive    | —        | —     | _    | —    | 0000       |

| Legend                      |                                 | 15:0      |         | —      |        |        |        | —     | shown in h |            |            |       |            | Receive      | Register |       |      |      | 0000       |

PIC32MZ Embedded Connectivity with Floating Point Unit (EF) Family

Legend: x = unknown value on Reset; - = unimplemented, read as '0'. Reset values are shown in hexadecimal.

Note 1: All registers in this table except I2CxRCV have corresponding CLR, SET and INV registers at their virtual addresses, plus offsets of 0x4, 0x8 and 0xC, respectively. See Section 12.3 "CLR, SET, and INV Registers" for more information.

2: This register is not available on 64-pin devices.

# 26.1 Crypto Engine Control Registers

# TABLE 26-2: CRYPTO ENGINE REGISTER MAP

| ess                         |                  |               |       |                     |       |         |          |       |        |       | Bits      |       |        |        |         |         |         |        | <i>"</i>   |

|-----------------------------|------------------|---------------|-------|---------------------|-------|---------|----------|-------|--------|-------|-----------|-------|--------|--------|---------|---------|---------|--------|------------|

| Virtual Address<br>(BF8E_#) | Register<br>Name | Bit Range     | 31/15 | 30/14               | 29/13 | 28/12   | 27/11    | 26/10 | 25/9   | 24/8  | 23/7      | 22/6  | 21/5   | 20/4   | 19/3    | 18/2    | 17/1    | 16/0   | All Resets |

| 5000                        | CEVER            | 31:16         |       |                     |       | REVISIO | DN<7:0>  |       |        |       |           |       |        | VERSIC | DN<7:0> |         |         |        | 0000       |

| 3000                        | OLVER            | 15:0          |       |                     | -     | -       |          |       |        | ID    | <15:0>    |       |        |        | -       | -       |         | -      | 0000       |

| 5004                        | CECON            | 31:16         | —     | —                   | —     | —       | —        | —     | —      |       | —         | —     | —      | _      | —       | —       | —       | —      | 0000       |

| 0001                        | 020011           | 15:0          | —     | —                   | —     | —       | _        | —     | —      | _     | SWAPOEN   | SWRST | SWAPEN | —      | —       | BDPCHST | BDPPLEN | DMAEN  | 0000       |

| 5008                        | CEBDADDR         | 31:16         |       |                     |       |         |          |       |        | BDPAI | DDR<31:0> |       |        |        |         |         |         |        | 0000       |

|                             |                  | 15:0          |       |                     |       |         |          |       |        |       |           |       |        |        |         |         |         |        | 0000       |

| 500C                        | CEBDPADDR        | 31:16         |       | BASEADDR<31:0>      |       |         |          |       |        |       |           |       |        |        |         |         |         |        |            |

|                             |                  | 15:0          |       |                     |       | _       |          |       |        |       |           |       |        |        |         |         |         |        | 0000       |

| 5010                        | CESTAT           | 31:16         | ER    | RMODE<2             | 2:0>  | E       | RROP<2:0 | )>    | ERRPHA |       | —         | _     |        | BDSTA  | TE<3:0> |         | START   | ACTIVE | -          |

|                             |                  | 15:0          |       |                     |       |         |          |       |        |       | RL<15:0>  |       |        |        |         |         |         |        | 0000       |

| 5014                        | CEINTSRC         | 31:16         | _     | _                   | _     | _       | _        | _     |        | _     | _         |       | _      |        | -       |         | -       |        | 0000       |

|                             |                  | 15:0<br>31:16 | _     | _                   | _     | _       | _        | _     | _      | _     | _         | _     | _      |        | AREIF   | PKTIF   | CBDIF   | PENDIF | -          |

| 5018                        | CEINTEN          | 15:0          | _     |                     |       |         |          |       |        |       | _         |       |        |        | AREIE   | PKTIE   |         | PENDIE | 0000       |

|                             |                  | 31:16         |       |                     |       |         |          |       |        |       |           |       |        | 0000   |         |         |         |        |            |

| 501C                        | CEPOLLCON        | 15:0          | _     | BDPPLCON<15:0> 0000 |       |         |          |       |        |       |           |       |        |        |         |         |         |        |            |

|                             |                  | 31:16         | _     | _                   | _     | _       | _        | _     | _      | _     | _         | _     | _      | _      | _       | _       | _       | _      | 0000       |

| 5020                        | CEHDLEN          | 15:0          | _     |                     |       |         | _        | _     |        |       |           |       |        |        | N<7:0>  |         |         |        | 0000       |

|                             |                  | 31:16         | _     | _                   |       |         | _        | _     | _      | _     | _         | _     | _      | _      | _       | _       | — I     | _      | 0000       |

| 5024                        | CETRLLEN         | 15:0          | _     | _                   | _     |         | _        | _     | _      | _     |           |       |        | TRLRL  | EN<7:0> |         |         |        | 0000       |

|                             |                  |               |       |                     |       |         |          |       |        |       |           |       |        |        | -       |         |         |        |            |

Legend: x = unknown value on Reset; — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

| Bit<br>Range | Bit<br>31/23/15/7     | Bit<br>30/22/14/6     | Bit<br>29/21/13/5     | Bit<br>28/20/12/4     | Bit<br>27/19/11/3     | Bit<br>26/18/10/2     | Bit<br>25/17/9/1      | Bit<br>24/16/8/0      |

|--------------|-----------------------|-----------------------|-----------------------|-----------------------|-----------------------|-----------------------|-----------------------|-----------------------|

| 04.04        | R-0, HS, HC           |

| 31:24        | ARDY31 <sup>(1)</sup> | ARDY30 <sup>(1)</sup> | ARDY29 <sup>(1)</sup> | ARDY28 <sup>(1)</sup> | ARDY27 <sup>(1)</sup> | ARDY26 <sup>(1)</sup> | ARDY25 <sup>(1)</sup> | ARDY24 <sup>(1)</sup> |

| 00.40        | R-0, HS, HC           |

| 23:16        | ARDY23 <sup>(1)</sup> | ARDY22 <sup>(1)</sup> | ARDY21 <sup>(1)</sup> | ARDY20 <sup>(1)</sup> | ARDY19 <sup>(1)</sup> | ARDY18                | ARDY17                | ARDY16                |

| 15.0         | R-0, HS, HC           |

| 15:8         | ARDY15                | ARDY14                | ARDY13                | ARDY12                | ARDY11                | ARDY10                | ARDY9                 | ARDY8                 |

| 7.0          | R-0, HS, HC           |

| 7:0          | ARDY7                 | ARDY6                 | ARDY5                 | ARDY4                 | ARDY3                 | ARDY2                 | ARDY1                 | ARDY0                 |

|              |                       |                       |                       |                       |                       |                       |                       |                       |

#### REGISTER 28-12: ADCDSTAT1: ADC DATA READY STATUS REGISTER 1

| Legend: HS = Hardware Set |                  |                  | HC = Hardware Cleared              |                    |  |  |  |

|---------------------------|------------------|------------------|------------------------------------|--------------------|--|--|--|

| F                         | R = Readable bit | W = Writable bit | U = Unimplemented bit, read as '0' |                    |  |  |  |

| -                         | n = Value at POR | '1' = Bit is set | '0' = Bit is cleared               | x = Bit is unknown |  |  |  |

bit 31-0 ARDY31:ARDY0: Conversion Data Ready for Corresponding Analog Input Ready bits

- 1 = This bit is set when converted data is ready in the data register

- 0 = This bit is cleared when the associated data register is read

**Note 1:** This bit is not available on 64-pin devices.

| Bit<br>Range | Bit<br>31/23/15/7     | Bit<br>30/22/14/6     | Bit<br>29/21/13/5     | Bit<br>28/20/12/4     | Bit<br>27/19/11/3     | Bit<br>26/18/10/2     | Bit<br>25/17/9/1      | Bit<br>24/16/8/0      |

|--------------|-----------------------|-----------------------|-----------------------|-----------------------|-----------------------|-----------------------|-----------------------|-----------------------|

| 31:24        | U-0                   |

| 31.24        | _                     | _                     | _                     | _                     | _                     | _                     |                       |                       |

| 23:16        | U-0                   |

| 23.10        | —                     | —                     | —                     | —                     | —                     | —                     | —                     | _                     |

| 15.0         | U-0                   | U-0                   | U-0                   | R-0, HS, HC           |

| 15:8         | —                     | —                     | —                     | ARDY44                | ARDY43                | ARDY42 <sup>(2)</sup> | ARDY41 <sup>(2)</sup> | ARDY40 <sup>(2)</sup> |

| 7.0          | R-0, HS, HC           |

| 7:0          | ARDY39 <sup>(2)</sup> | ARDY38 <sup>(2)</sup> | ARDY37 <sup>(2)</sup> | ARDY36 <sup>(2)</sup> | ARDY35 <sup>(2)</sup> | ARDY34 <sup>(1)</sup> | ARDY33 <sup>(1)</sup> | ARDY32 <sup>(1)</sup> |

### REGISTER 28-13: ADCDSTAT2: ADC DATA READY STATUS REGISTER 2

| Legend:           | HS = Hardware Set | HC = Hardware Cleared              |                    |  |  |

|-------------------|-------------------|------------------------------------|--------------------|--|--|

| R = Readable bit  | W = Writable bit  | U = Unimplemented bit, read as '0' |                    |  |  |

| -n = Value at POR | '1' = Bit is set  | '0' = Bit is cleared               | x = Bit is unknown |  |  |

bit 31-13 Unimplemented: Read as '0'

bit 12-0 ARDY44:ARDY32: Conversion Data Ready for Corresponding Analog Input Ready bits

1 = This bit is set when converted data is ready in the data register

0 = This bit is cleared when the associated data register is read

Note 1: This bit is not available on 64-pin devices.

2: This bit is not available on 64 -pin and 100-pin devices.

| Bit Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |  |  |

|-----------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|--|--|

| 04-04     | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |  |  |

| 31:24     | _                 | —                 | —                 | —                 | —                 | _                 | —                | —                |  |  |

| 00.40     | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |  |  |

| 23:16     | _                 | —                 | —                 | —                 | —                 | _                 |                  | —                |  |  |

| 45.0      | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |  |

| 15:8      | ADCBASE<15:8>     |                   |                   |                   |                   |                   |                  |                  |  |  |

| 7.0       | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |  |

| 7:0       | ADCBASE<7:0>      |                   |                   |                   |                   |                   |                  |                  |  |  |

### REGISTER 28-24: ADCBASE: ADC BASE REGISTER

## Legend:

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, read as '0' |                    |  |  |

|-------------------|------------------|------------------------------------|--------------------|--|--|

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared               | x = Bit is unknown |  |  |

#### bit 31-0 Unimplemented: Read as '0'

#### bit 15-0 ADCBASE<15:0>: ADC ISR Base Address bits

This register, when read, contains the base address of the user's ADC ISR jump table. The interrupt vector address is determined by the IRQVS<2:0> bits of the ADCCON1 register specifying the amount of left shift done to the ARDYx status bits in the ADCDSTAT1 and ADCDSTAT2 registers, prior to adding with ADCBASE register.

Interrupt Vector Address = Read Value of ADCBASE and Read Value of ADCBASE = Value written to ADCBASE +  $x \ll$  IRQVS<2:0>, where 'x' is the smallest active analog input ID from the ADCDSTAT1 or ADCDSTAT2 registers (which has highest priority).

| Bit Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |  |  |  |

|-----------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|--|--|--|

| 24.24     | R-0               | R-0               | R-0               | R-0               | R-0               | R-0               | R-0              | R-0              |  |  |  |

| 31:24     |                   | DATA<31:24>       |                   |                   |                   |                   |                  |                  |  |  |  |

| 00.40     | R-0               | R-0               | R-0               | R-0               | R-0               | R-0               | R-0              | R-0              |  |  |  |

| 23:16     | DATA<23:16>       |                   |                   |                   |                   |                   |                  |                  |  |  |  |

| 45.0      | R-0               | R-0               | R-0               | R-0               | R-0               | R-0               | R-0              | R-0              |  |  |  |

| 15:8      | DATA<15:8>        |                   |                   |                   |                   |                   |                  |                  |  |  |  |

| 7.0       | R-0               | R-0               | R-0               | R-0               | R-0               | R-0               | R-0              | R-0              |  |  |  |

| 7:0       |                   |                   |                   | DATA              | <7:0>             |                   |                  |                  |  |  |  |

### **REGISTER 28-25:** ADCDATAX: ADC OUTPUT DATA REGISTER ('x' = 0 THROUGH 44)

# Legend:

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, read as '0'      |  |  |  |

|-------------------|------------------|-----------------------------------------|--|--|--|

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared x = Bit is unknown |  |  |  |

bit 31-0 DATA<31:0>: ADC Converted Data Output bits.

- **Note 1:** The registers, ADCDATA19 through ADCDATA34, are not available on 64-pin devices.

- 2: The registers, ADCDATA35 through ADCDATA42, are not available on 64-pin and 100-pin devices.

- **3:** When an alternate input is used as the input source for a dedicated ADC module, the data output is still read from the Primary input Data Output Register.

- 4: Reading the ADCDATAx register value after changing the FRACT bit converts the data into the format specified by FRACT bit.

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|

| 31:24        | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |

| 31.24        | FLTEN23           | MSEL2             | 3<1:0>            |                   | F                 | SEL23<4:0>        |                  |                  |

| 22:46        | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |

| 23:16        | FLTEN22           | MSEL22<1:0>       |                   | FSEL22<4:0>       |                   |                   |                  |                  |

| 15.0         | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |

| 15:8         | FLTEN21           | MSEL2             | :1<1:0>           |                   | F                 | SEL21<4:0>        |                  |                  |

| 7.0          | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |

| 7:0          | FLTEN20           | MSEL2             | :0<1:0>           |                   | F                 | SEL20<4:0>        | •                |                  |

### REGISTER 29-15: CIFLTCON5: CAN FILTER CONTROL REGISTER 5

#### Legend:

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, re | ead as '0'         |

|-------------------|------------------|---------------------------|--------------------|

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared      | x = Bit is unknown |

| bit 31    | <b>FLTEN23:</b> Filter 23 Enable bit<br>1 = Filter is enabled                                                                                                                                                                                                                                                                       |

|-----------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| bit 30-29 | <ul> <li>0 = Filter is disabled</li> <li>MSEL23&lt;1:0&gt;: Filter 23 Mask Select bits</li> <li>11 = Acceptance Mask 3 selected</li> <li>10 = Acceptance Mask 2 selected</li> <li>01 = Acceptance Mask 1 selected</li> <li>00 = Acceptance Mask 0 selected</li> </ul>                                                               |

| bit 28-24 | FSEL23<4:0>: FIFO Selection bits<br>11111 = Message matching filter is stored in FIFO buffer 31<br>11110 = Message matching filter is stored in FIFO buffer 30<br>•                                                                                                                                                                 |

|           | •<br>00001 = Message matching filter is stored in FIFO buffer 1<br>00000 = Message matching filter is stored in FIFO buffer 0                                                                                                                                                                                                       |

| bit 23    | FLTEN22: Filter 22 Enable bit<br>1 = Filter is enabled<br>0 = Filter is disabled                                                                                                                                                                                                                                                    |

| bit 22-21 | MSEL22<1:0>: Filter 22 Mask Select bits<br>11 = Acceptance Mask 3 selected<br>10 = Acceptance Mask 2 selected<br>01 = Acceptance Mask 1 selected<br>00 = Acceptance Mask 0 selected                                                                                                                                                 |

| bit 20-16 | FSEL22<4:0>: FIFO Selection bits          11111 = Message matching filter is stored in FIFO buffer 31         11110 = Message matching filter is stored in FIFO buffer 30         •         •         00001 = Message matching filter is stored in FIFO buffer 1         00000 = Message matching filter is stored in FIFO buffer 0 |

| Note:     | The bits in this register can only be modified if the corresponding filter enable (FLTENn) bit is '0'.                                                                                                                                                                                                                              |

DS60001320D-page 510

### REGISTER 34-7: CFGCON: CONFIGURATION CONTROL REGISTER (CONTINUED)

- bit 7 IOANCPEN: I/O Analog Charge Pump Enable bit

The analog IO charge pump improves analog performance when the device is operating at lower voltages. However, the charge pumps consume additional current.

1 = Charge pump is enabled

0 = Charge pump is disabled

- bit 6 Unimplemented: Read as '0'

- bit 5-4 ECCCON<1:0>: Flash ECC Configuration bits

- 11 = ECC and dynamic ECC are disabled (ECCCON<1:0> bits are writable)

- 10 = ECC and dynamic ECC are disabled (ECCCON<1:0> bits are locked)

- 01 = Dynamic Flash ECC is enabled (ECCCON<1:0> bits are locked)

- 00 = Flash ECC is enabled (ECCCON<1:0> bits are locked; disables word Flash writes)

- bit 3 JTAGEN: JTAG Port Enable bit

- 1 = Enable the JTAG port

- 0 = Disable the JTAG port

- bit 2 TROEN: Trace Output Enable bit

- 1 = Enable trace outputs and start trace clock (trace probe must be present)0 = Disable trace outputs and stop trace clock

- bit 1 Unimplemented: Read as '0'

- bit 0 TDOEN: TDO Enable for 2-Wire JTAG

- 1 = 2-wire JTAG protocol uses TDO

- 0 = 2-wire JTAG protocol does not use TDO

- Note 1: To change this bit, the unlock sequence must be performed. Refer to Section 42. "Oscillators with Enhanced PLL" (DS60001250) in the "PIC32 Family Reference Manual" for details.

|               |        |                                                         | •          | erating Con                      | ditions: 2.1 | / to 3.6\ | V (unless otherwise                                  |

|---------------|--------|---------------------------------------------------------|------------|----------------------------------|--------------|-----------|------------------------------------------------------|

| DC CHA        |        |                                                         |            | stated)<br>Operating temperature |              |           | C for Industrial<br>°C for Extended                  |

| Param.<br>No. | Symbol | Characteristics                                         | Min.       | Typ. <sup>(1)</sup>              | Max.         | Units     | Conditions                                           |

|               | VIL    | Input Low Voltage                                       |            |                                  |              |           |                                                      |

| DI10          |        | I/O Pins with PMP                                       | Vss        | —                                | 0.15 * Vdd   | V         |                                                      |

|               |        | I/O Pins                                                | Vss        | —                                | 0.2 * Vdd    | V         |                                                      |

| DI18          |        | SDAx, SCLx                                              | Vss        | _                                | 0.3 * Vdd    | V         | SMBus disabled (Note 4)                              |

| DI19          |        | SDAx, SCLx                                              | Vss        | —                                | 0.8          | V         | SMBus enabled<br>(Note 4)                            |

|               | Vih    | Input High Voltage                                      |            |                                  |              |           |                                                      |

| DI20          |        | I/O Pins not 5V-tolerant <sup>(5)</sup>                 | 0.80 * Vdd | —                                | Vdd          | V         | (Note 4,6)                                           |

|               |        | I/O Pins 5V-tolerant with<br>PMP <sup>(5)</sup>         | 0.80 * Vdd | —                                | 5.5          | V         | (Note 4,6)                                           |

|               |        | I/O Pins 5V-tolerant <sup>(5)</sup>                     | 0.80 * Vdd | —                                | 5.5          | V         |                                                      |

| DI28a         |        | SDAx, SCLx on non-5V<br>tolerant pins <sup>(5)</sup>    | 0.80 * Vdd | —                                | Vdd          | V         | SMBus disabled (Note 4,6)                            |

| DI29a         |        | SDAx, SCLx on non-5V<br>tolerant pins <sup>(5)</sup>    | 2.1        | _                                | Vdd          | V         | SMBus enabled,<br>2.1V ≤ VPIN ≤ 5.5<br>(Note 4,6)    |

| DI28b         |        | SDAx, SCLx on 5V tolerant pins <sup>(5)</sup>           | 0.80 * Vdd | —                                | 5.5          | V         | SMBus disabled (Note 4,6)                            |

| DI29b         |        | SDAx, SCLx on 5V tolerant pins <sup>(5)</sup>           | 2.1        | _                                | 5.5          | V         | SMBus enabled,<br>2.1V ≤ VPIN ≤ 5.5<br>(Note 4,6)    |

| DI30          | ICNPU  | Change Notification<br>Pull-up Current                  | —          |                                  | -40          | μA        | VDD = 3.3V, VPIN = VSS<br>(Note 3,6)                 |

| DI31          | ICNPD  | Change Notification<br>Pull-down Current <sup>(4)</sup> | 40         | —                                | -            | μA        | VDD = 3.3V, VPIN = VDD                               |

|               | liL    | Input Leakage Current<br>(Note 3)                       |            |                                  |              |           |                                                      |

| DI50          |        | I/O Ports                                               | —          | —                                | <u>+</u> 1   | μA        | VSS $\leq$ VPIN $\leq$ VDD,<br>Pin at high-impedance |

| DI51          |        | Analog Input Pins                                       | —          | —                                | <u>+</u> 1   | μA        | $VSS \le VPIN \le VDD$ ,<br>Pin at high-impedance    |

| DI55          |        | MCLR <sup>(2)</sup>                                     | —          | —                                | <u>+</u> 1   | μA        | $VSS \le VPIN \le VDD$                               |

| DI56          |        | OSC1                                                    | —          | —                                | <u>+</u> 1   | μA        | $Vss \le VPIN \le VDD,$<br>HS mode                   |

## TABLE 37-9: DC CHARACTERISTICS: I/O PIN INPUT SPECIFICATIONS

**Note 1:** Data in "Typical" column is at 3.3V, +25°C unless otherwise stated. Parameters are for design guidance only and are not tested.

2: The leakage current on the MCLR pin is strongly dependent on the applied voltage level. The specified levels represent normal operating conditions. Higher leakage current may be measured at different input voltages.

- **3:** Negative current is defined as current sourced by the pin.

- 4: This parameter is characterized, but not tested in manufacturing.

- 5: See the pin name tables (Table 2 through Table 4) for the 5V-tolerant pins.

6: The VIH specifications are only in relation to externally applied inputs, and not with respect to the userselectable internal pull-ups. External open drain input signals utilizing the internal pull-ups of the PIC32 device are guaranteed to be recognized only as a logic "high" internally to the PIC32 device, provided that the external load does not exceed the minimum value of ICNPU. For External "input" logic inputs that require a pull-up source, to guarantee the minimum VIH of those components, it is recommended to use an external pull-up resistor rather than the internal pull-ups of the PIC32 device.

# 39.0 252 MHz ELECTRICAL CHARACTERISTICS

This section provides an overview of the PIC32MZ EF electrical characteristics for devices running at 252 MHz. Additional information will be provided in future revisions of this document as it becomes available.

The specifications for 252 MHz are identical to those shown in **37.0** "Electrical Characteristics" including absolute maximum ratings, with the exception of the parameters listed in this chapter.

Parameters in this chapter begin with the letter "M", which denotes 252 MHz operation. For example, parameter DC27a in **37.0** "Electrical Characteristics", is the up to 200 MHz operation equivalent for MDC27a.

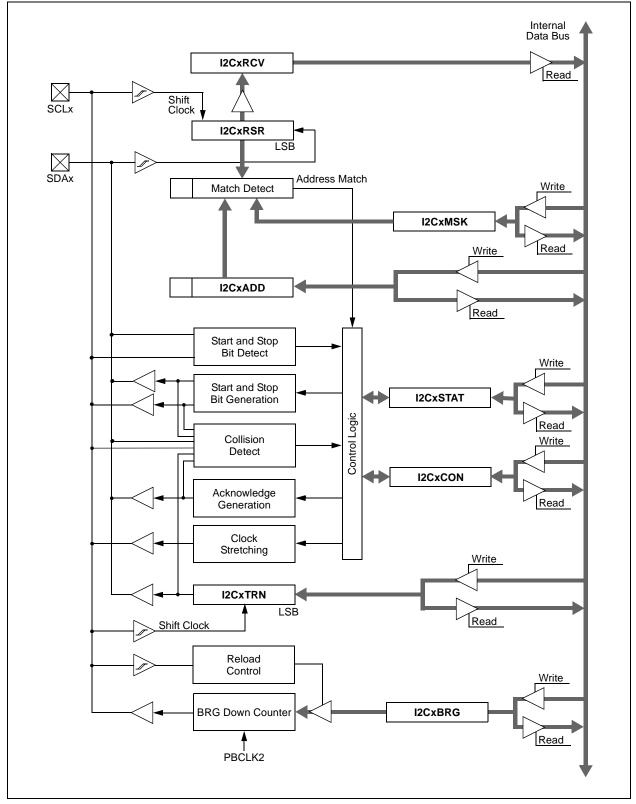

## 41.2 Package Details

64-Lead Plastic Quad Flat, No Lead Package (MR) – 9x9x0.9 mm Body [QFN] With 0.40 mm Contact Length and 7.70x7.70mm Exposed Pad

**Note:** For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

## RECOMMENDED LAND PATTERN

|                                 | MILLIMETERS |      |          |      |

|---------------------------------|-------------|------|----------|------|

| Dimension                       | Limits      | MIN  | NOM      | MAX  |

| Contact Pitch                   | E           |      | 0.50 BSC |      |

| Optional Center Pad Width       | W2          |      |          | 7.50 |

| Optional Center Pad Length      | T2          |      |          | 7.50 |

| Contact Pad Spacing             | C1          |      | 8.90     |      |

| Contact Pad Spacing             | C2          |      | 8.90     |      |

| Contact Pad Width (X20)         | X1          |      |          | 0.30 |

| Contact Pad Length (X20)        | Y1          |      |          | 0.90 |

| Contact Pad to Center Pad (X20) | G           | 0.20 |          |      |

| Thermal Via Diameter            | V           |      | 0.30     |      |

| Thermal Via Pitch               | EV          |      | 1.00     |      |

Notes:

- 1. Dimensioning and tolerancing per ASME Y14.5M

- BSC: Basic Dimension. Theoretically exact value shown without tolerances.

- 2. For best soldering results, thermal vias, if used, should be filled or tented to avoid solder loss during reflow process

Microchip Technology Drawing No. C04-2213B

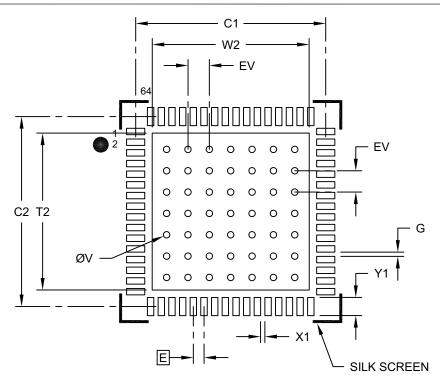

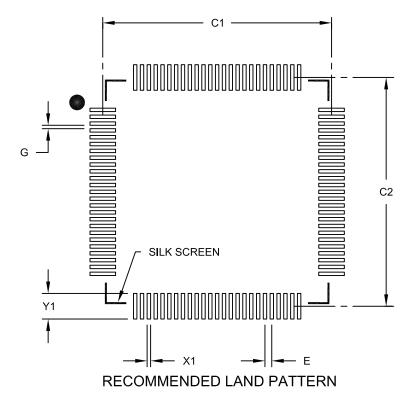

# 64-Lead Plastic Thin Quad Flatpack (PT)-10x10x1 mm Body, 2.00 mm Footprint [TQFP]

**Note:** For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

# RECOMMENDED LAND PATTERN

|                          | Units | MILLIMETERS |       |      |

|--------------------------|-------|-------------|-------|------|

| Dimension Limits         |       | MIN         | NOM   | MAX  |

| Contact Pitch            | E     | 0.50 BSC    |       |      |

| Contact Pad Spacing      | C1    |             | 11.40 |      |

| Contact Pad Spacing      | C2    |             | 11.40 |      |

| Contact Pad Width (X28)  | X1    |             |       | 0.30 |

| Contact Pad Length (X28) | Y1    |             |       | 1.50 |

| Distance Between Pads    | G     | 0.20        |       |      |

Notes:

1. Dimensioning and tolerancing per ASME Y14.5M

BSC: Basic Dimension. Theoretically exact value shown without tolerances.

Microchip Technology Drawing C04-2085B Sheet 1 of 1

100-Lead Plastic Thin Quad Flatpack (PT)-12x12x1mm Body, 2.00 mm Footprint [TQFP]

**Note:** For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

|                           | Units | MILLIMETERS |       |      |  |

|---------------------------|-------|-------------|-------|------|--|

| Dimension Limits          |       | MIN         | NOM   | MAX  |  |

| Contact Pitch             | E     | 0.40 BSC    |       |      |  |

| Contact Pad Spacing       | C1    |             | 13.40 |      |  |

| Contact Pad Spacing       | C2    |             | 13.40 |      |  |

| Contact Pad Width (X100)  | X1    |             |       | 0.20 |  |

| Contact Pad Length (X100) | Y1    |             |       | 1.50 |  |

| Distance Between Pads     | G     | 0.20        |       |      |  |

Notes:

1. Dimensioning and tolerancing per ASME Y14.5M

BSC: Basic Dimension. Theoretically exact value shown without tolerances.

Microchip Technology Drawing No. C04-2100B