Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFI

| Product Status             | Active                                                                            |

|----------------------------|-----------------------------------------------------------------------------------|

| Core Processor             | MIPS32® M-Class                                                                   |

| Core Size                  | 32-Bit Single-Core                                                                |

| Speed                      | 200MHz                                                                            |

| Connectivity               | EBI/EMI, Ethernet, I <sup>2</sup> C, PMP, SPI, SQI, UART/USART, USB OTG           |

| Peripherals                | Brown-out Detect/Reset, DMA, I <sup>2</sup> S, POR, PWM, WDT                      |

| Number of I/O              | 78                                                                                |

| Program Memory Size        | 512KB (512K x 8)                                                                  |

| Program Memory Type        | FLASH                                                                             |

| EEPROM Size                |                                                                                   |

| RAM Size                   | 128K x 8                                                                          |

| Voltage - Supply (Vcc/Vdd) | 2.1V ~ 3.6V                                                                       |

| Data Converters            | A/D 40x12b                                                                        |

| Oscillator Type            | Internal                                                                          |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                                 |

| Mounting Type              | Surface Mount                                                                     |

| Package / Case             | 100-TQFP                                                                          |

| Supplier Device Package    | 100-TQFP (14x14)                                                                  |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic32mz0512efe100t-i-pf |

|                            |                                                                                   |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

| 124              | -PIN VTLA (BOTTOM VIEW)                                                                                  | A17       |      | E                | A34<br><sub>313</sub> B29   |     |

|------------------|----------------------------------------------------------------------------------------------------------|-----------|------|------------------|-----------------------------|-----|

|                  | PIC32MZ0512EF(E/F/K)124<br>PIC32MZ1024EF(G/H/M)124<br>PIC32MZ1024EF(E/F/K)124<br>PIC32MZ2048EF(G/H/M)124 |           |      | A1               | B1 B41<br>B56               | A51 |

|                  | Pol                                                                                                      | arity Inc | lica | tor              | A68                         |     |

| Package<br>Pin # | Full Pin Name                                                                                            |           |      | Package<br>Pin # | Full Pin Name               |     |

| B1               | EBIA5/AN34/PMA5/RA5                                                                                      |           |      | B29              | Vss                         |     |

| B2               | EBID6/AN16/PMD6/RE6                                                                                      |           |      | B30              | D+                          |     |

| B3               | EBIA6/AN22/RPC1/PMA6/RC1                                                                                 |           |      | B31              | RPF2/SDA3/RF2               |     |

| B4               | AN36/ETXD1/RJ9                                                                                           |           |      | B32              | ERXD0/RH8                   |     |

| B5               | EBIWE/AN20/RPC3/PMWR/RC3                                                                                 |           |      | B33              | ECOL/RH10                   |     |

| B6               | AN14/C1IND/RPG6/SCK2/RG6                                                                                 |           |      | B34              | EBIRDY1/SDA2/RA3            |     |

| B7               | EBIA3/AN12/C2IND/RPG8/SCL4/PMA3/RG8                                                                      |           |      | B35              | VDD                         |     |

| B8               | VDD                                                                                                      |           |      | B36              | EBIA9/RPF4/SDA5/PMA9/RF4    |     |

| B9               | EBIA2/AN11/C2INC/RPG9/PMA2/RG9                                                                           |           |      | B37              | RPA14/SCL1/RA14             |     |

| B10              | AN25/RPE8/RE8                                                                                            |           |      | B38              | EBIA15/RPD9/PMCS2/PMA15/RD9 |     |

| B11              | AN45/C1INA/RPB5/RB5                                                                                      |           |      | B39              | EMDC/RPD11/RD11             |     |

| B12              | AN37/ERXCLK/EREFCLK/RJ11                                                                                 |           |      | B40              | ERXDV/ECRSDV/RH13           |     |

| B13              | Vss                                                                                                      |           |      | B41              | SOSCI/RPC13/RC13            |     |

| B14              | PGEC2/AN46/RPB6/RB6                                                                                      |           |      | B42              | EBID14/RPD2/PMD14/RD2       |     |

| B15              | Vref-/CVref-/AN27/RA9                                                                                    |           |      | B43              | EBID12/RPD12/PMD12/RD12     |     |

| B16              | AVdd                                                                                                     |           |      | B44              | ETXERR/RJ0                  |     |

| B17              | AN38/ETXD2/RH0                                                                                           |           |      | B45              | EBIRDY3/RJ2                 |     |

| B18              | EBIA10/AN48/RPB8/PMA10/RB8                                                                               |           |      | B46              | SQICS1/RPD5/RD5             |     |

| B19              | EBIA13/CVREFOUT/AN5/RPB10/PMA13/RB10                                                                     |           |      | B47              | ETXCLK/RPD7/RD7             |     |

| B20              | Vss                                                                                                      |           |      | B48              | Vss                         |     |

| B21              | TCK/EBIA19/AN29/RA1                                                                                      |           |      | B49              | EBID10/RPF1/PMD10/RF1       |     |

| B22              | TDO/EBIA17/AN31/RPF12/RF12                                                                               |           |      | B50              | EBID8/RPG0/PMD8/RG0         |     |

| B23              | AN8/RB13                                                                                                 |           |      | B51              | TRD3/SQID3/RA7              |     |

| B24              | EBIA0/AN10/RPB15/OCFB/PMA0/RB15                                                                          |           |      | B52              | EBID0/PMD0/RE0              |     |

| B25              | Vdd                                                                                                      |           |      | B53              | Vdd                         |     |

| B26              | AN41/ERXD1/RH5                                                                                           |           |      | B54              | TRD2/SQID2/RG14             |     |

| B27              | AN32/AETXD0/RPD14/RD14                                                                                   |           |      | B55              | TRD0/SQID0/RG13             |     |

| B28              | OSC1/CLKI/RC12                                                                                           |           |      | B56              | EBID3/RPE3/PMD3/RE3         |     |

#### TABLE 4: **PIN NAMES FOR 124-PIN DEVICES (CONTINUED)**

Note 1: The RPn pins can be used by remappable peripherals. See Table 1 for the available peripherals and Section 12.4 "Peripheral Pin Select (PPS)" for restrictions.

2:

Every I/O port pin (RAx-RJx) can be used as a change notification pin (CNAx-CNJx). See Section 12.0 "I/O Ports" for more information.

3: Shaded pins are 5V tolerant.

4: The metal plane at the bottom of the device is not connected to any pins and is recommended to be connected to Vss externally.

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |  |  |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|--|--|

| 24.24        | U-0               | U-0               | U-0               | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |  |

| 31:24        | —                 | —                 | —                 |                   | IP3<2:0>          |                   | IS3<1:0>         |                  |  |  |

| 23:16        | U-0               | U-0               | U-0               | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |  |

| 23.10        | _                 | —                 | _                 |                   | IP2<2:0>          | IS2<1:0>          |                  |                  |  |  |

| 15:8         | U-0               | U-0               | U-0               | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |  |

| 15.0         | _                 | —                 | _                 |                   | IP1<2:0>          |                   | IS1<             | :1:0>            |  |  |

| 7:0          | U-0               | U-0               | U-0               | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |  |

| 7.0          | _                 | —                 | _                 |                   | IP0<2:0>          |                   | IS0<1:0>         |                  |  |  |

# REGISTER 7-7: IPCx: INTERRUPT PRIORITY CONTROL REGISTER

#### Legend:

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, read as '0' |                    |  |  |

|-------------------|------------------|------------------------------------|--------------------|--|--|

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared               | x = Bit is unknown |  |  |

# bit 31-29 Unimplemented: Read as '0'

| bit 28-26 | IP3<2:0>: Interrupt Priority bits                                  |

|-----------|--------------------------------------------------------------------|

|           | 111 = Interrupt priority is 7                                      |

|           | •                                                                  |

|           | •                                                                  |

|           | 010 = Interrupt priority is 2                                      |

|           | 001 = Interrupt priority is 1                                      |

|           | 000 = Interrupt is disabled                                        |

| bit 25-24 | IS3<1:0>: Interrupt Subpriority bits                               |

|           | 11 = Interrupt subpriority is 3                                    |

|           | 10 = Interrupt subpriority is 2                                    |

|           | 01 = Interrupt subpriority is 1                                    |

|           | 00 = Interrupt subpriority is 0                                    |

| bit 23-21 |                                                                    |

| bit 20-18 | IP2<2:0>: Interrupt Priority bits                                  |

|           | 111 = Interrupt priority is 7                                      |

|           | •                                                                  |

|           | •                                                                  |

|           | 010 = Interrupt priority is 2                                      |

|           | 001 = Interrupt priority is 1                                      |

|           | 000 = Interrupt is disabled                                        |

| bit 17-16 | IS2<1:0>: Interrupt Subpriority bits                               |

|           | 11 = Interrupt subpriority is 3                                    |

|           | 10 = Interrupt subpriority is 2                                    |

|           | 01 = Interrupt subpriority is 1<br>00 = Interrupt subpriority is 0 |

| hit 15-13 | Unimplemented: Read as '0'                                         |

| 5115-15   | ommplemented. Read as 0                                            |

| Note:     | This register represents a generic defi                            |

|           |                                                                    |

Note: This register represents a generic definition of the IPCx register. Refer to Table 7-2 for the exact bit definitions.

REGISTER 11-4: USBCSR3: USB CONTROL STATUS REGISTER 3 (CONTINUED)

bit 19-16 ENDPOINT<3:0>: Endpoint Registers Select bits

- bit 19-11 Unimplemented: Read as 0

- bit 10-0 RFRMNUM<10:0>: Last Received Frame Number bits

#### TABLE 12-23: PERIPHERAL PIN SELECT OUTPUT REGISTER MAP

| ss                          |                       |           |            | Bits        |       |       |       |       |      |               |      |      |      |      |      |       |        |      |            |

|-----------------------------|-----------------------|-----------|------------|-------------|-------|-------|-------|-------|------|---------------|------|------|------|------|------|-------|--------|------|------------|

| Virtual Address<br>(BF80_#) | Register<br>Name      | Bit Range | 31/15      | 30/14       | 29/13 | 28/12 | 27/11 | 26/10 | 25/9 | 24/8          | 23/7 | 22/6 | 21/5 | 20/4 | 19/3 | 18/2  | 17/1   | 16/0 | All Resets |

|                             | (1)                   | 31:16     | _          | _           | _     | _     | _     | _     | _    | _             | _    | _    | _    | _    | _    | —     | _      | _    | 0000       |

| 1538                        | RPA14R <sup>(1)</sup> | 15:0      | _          | _           | _     | _     | _     | _     | _    |               | _    | _    |      | _    |      | RPA14 | R<3:0> |      | 0000       |

|                             |                       | 31:16     | _          | —           | —     | _     | _     | _     | _    | —             | _    | _    | _    | _    | _    | —     | —      | _    | 0000       |

| 153C                        | RPA15R <sup>(1)</sup> | 15:0      | _          | —           | —     | _     | _     | _     | _    | —             | _    | _    | _    | _    |      | RPA15 | R<3:0> |      | 0000       |

|                             |                       | 31:16     | _          | —           | —     | _     | _     | _     | _    | —             | _    | _    | _    | _    | _    | —     | —      | _    | 0000       |

| 1540                        | RPB0R                 | 15:0      | _          | —           | —     | _     | _     | _     | _    | —             | _    | _    | _    | _    |      | RPB0  | R<3:0> |      | 0000       |

|                             |                       | 31:16     | _          | _           | _     | _     | _     | _     | _    | _             | _    | _    | _    | _    |      | _     |        | _    | 0000       |

| 1544                        | RPB1R                 | 15:0      | _          | _           | _     | _     | _     | _     | _    |               | _    | _    |      | _    |      | RPB1  | R<3:0> |      | 0000       |

|                             |                       | 31:16     | _          | —           | —     | _     | _     | _     | _    | —             | _    | _    | _    | _    | _    | —     | —      | _    | 0000       |

| 1548                        | RPB2R                 | 15:0      | _          | _           | _     | _     | _     | _     | _    | _             | _    | _    | _    | _    |      | RPB2  | R<3:0> |      | 0000       |

|                             |                       | 31:16     | _          | _           | _     | _     | _     | _     | _    | _             | _    | _    | _    | _    |      | _     |        | _    | 0000       |

| 154C                        | RPB3R                 | 15:0      | _          | _           | _     | _     | _     | _     | _    | _             | _    | _    | _    | _    |      | RPB3  | R<3:0> |      | 0000       |

|                             |                       | 31:16     | _          | _           | _     | _     | _     | _     | _    | _             | _    | _    | _    | _    |      | _     |        | _    | 0000       |

| 1554                        | RPB5R                 | 15:0      | _          | _           | _     | _     | _     | _     | _    | _             | _    | _    | _    | _    |      | RPB5  | R<3:0> |      | 0000       |

| ·                           |                       | 31:16     | _          |             | _     | _     | _     | _     | _    |               | _    | _    |      | _    |      | _     | _      | _    | 0000       |

| 1558                        | RPB6R                 | 15:0      | _          | _           | _     | _     | _     | _     | _    | _             | _    | _    |      | _    |      | RPB6  | R<3:0> |      | 0000       |

|                             | RPB7R                 | 31:16     | _          | _           | _     | _     | _     | _     | _    | _             | _    | _    | _    | _    | _    | _     | _      | _    | 0000       |

| 155C                        |                       | 15:0      | _          | _           | _     | _     | _     |       | _    | _             | _    | _    | _    | _    |      | RPB7  | R<3:0> |      | 0000       |

|                             |                       | 31:16     | _          | _           | _     | _     | _     | _     | _    | _             | _    | _    | _    | _    | _    | _     | _      | _    | 0000       |

| 1560                        | RPB8R                 | 15:0      | _          | _           | _     | _     | _     | _     | _    | _             | _    | _    | _    | _    |      | RPB8  | R<3:0> |      | 0000       |

|                             |                       | 31:16     | _          | _           | _     | _     | _     | _     | _    | _             | _    | _    | _    | _    | _    | _     | _      | _    | 0000       |

| 1564                        | RPB9R                 | 15:0      | _          | _           | _     | _     | _     | _     | _    | _             | _    | _    | _    | _    |      | RPB9  | R<3:0> |      | 0000       |

|                             |                       | 31:16     | _          | _           | _     | _     | _     | _     | _    | _             | _    | _    | _    | _    | _    | _     | _      | _    | 0000       |

| 1568                        | RPB10R                | 15:0      | _          | _           | _     | _     | _     |       | _    | _             | _    | _    | _    | _    |      | RPB10 | R<3:0> |      | 0000       |

|                             |                       | 31:16     | _          | _           | _     | _     | _     | _     | _    |               | _    | _    |      | _    |      | _     | _      | _    | 0000       |

| 1578                        | RPB14R                | 15:0      | _          | _           | _     | _     | _     | _     | _    |               | _    | _    |      | _    |      | RPB14 | R<3:0> |      | 0000       |

|                             |                       | 31:16     | _          | _           | _     | _     | _     | _     | _    | _             | _    | _    | _    | _    | _    | _     | _      | _    | 0000       |

| 157C                        | RPB15R                | 15:0      | _          | _           | _     | _     | _     | _     | _    |               | _    | _    |      | _    |      | RPB15 | R<3:0> |      | 0000       |

|                             | (1)                   | 31:16     | _          | _           | _     | _     | _     | _     | _    | _             | _    | _    |      | _    | _    | _     | _      | _    | 0000       |

| 1584                        | RPC1R <sup>(1)</sup>  | 15:0      | _          |             | _     | _     | _     | _     | _    |               | _    | _    |      | _    |      | RPC1  | R<3:0> |      | 0000       |

|                             | (1)                   | 31:16     | _          | _           | _     | _     | _     | _     | _    | _             | _    | _    | _    | _    | _    | _     | _      | _    | 0000       |

| 1588                        | RPC2R <sup>(1)</sup>  | 15:0      | _          | _           | _     | _     | _     | _     | _    | _             | _    | _    | _    | _    |      | RPC2  | R<3:0> |      | 0000       |

|                             | (1)                   | 31:16     | _          | _           | _     | _     | _     | _     | _    | _             | _    | _    | _    | _    | _    | _     | _      | _    | 0000       |

| 158C                        | RPC3R <sup>(1)</sup>  | 15:0      | _          | _           | _     | _     | _     | _     | _    | _             | _    | _    | _    | _    |      | RPC3  | R<3:0> |      | 0000       |

|                             | (0)                   | 31:16     | _          | _           | _     | _     | _     | _     | _    | _             | _    | _    | _    | _    | _    | _     | _      | _    | 0000       |

| 1590                        | RPC4R <sup>(1)</sup>  | 15:0      | _          |             | _     | _     | _     |       | _    |               | _    |      | _    | _    |      | RPC4  | R<3:0> |      | 0000       |

| Legen                       | l                     |           | alua an Da | eset: — = u |       |       |       |       |      | h ava da aira |      |      |      |      | l    |       |        |      | 0000       |

Legend: x = unknown value on Reset; - = unimplemented, read as '0'. Reset values are shown in hexadecimal.

**Note** 1: This register is not available on 64-pin devices.

2: This register is not available on 64-pin and 100-pin devices.

| Bit Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |

|-----------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|

| 21.24     | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 31:24     | —                 | _                 | _                 | _                 | -                 | _                 |                  | —                |

| 22:16     | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 23:16     | —                 | _                 | _                 | _                 | -                 | _                 |                  | —                |

| 45.0      | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 15:8      | —                 | _                 | _                 | _                 | -                 | _                 |                  | —                |

| 7.0       | R-0, HC, HS       | R-0, HC, HS       | R-0, HC, HS       | U-0               | U-0               | U-0               | U-0              | R-0, HC, HS      |

| 7:0       | BAD1              | BAD2              | DMTEVENT          | _                 |                   | _                 | _                | WINOPN           |

## REGISTER 15-4: DMTSTAT: DEADMAN TIMER STATUS REGISTER

| Legend:           | HC = Hardware Cleared | HS = Hardware Set                |            |

|-------------------|-----------------------|----------------------------------|------------|

| R = Readable bit  | W = Writable bit      | U = Unimplemented bit, read as   | '0'        |

| -n = Value at POR | '1' = Bit is set      | 0' = Bit is cleared 	 x = Bit is | is unknown |

| bit 31-8 | Unimplemented: Read as '0'                                                                                                          |

|----------|-------------------------------------------------------------------------------------------------------------------------------------|

| bit 7    | BAD1: Bad STEP1<7:0> Value Detect bit                                                                                               |

|          | 1 = Incorrect STEP1<7:0> value was detected                                                                                         |

|          | 0 = Incorrect STEP1<7:0> value was not detected                                                                                     |

| bit 6    | BAD2: Bad STEP2<7:0> Value Detect bit                                                                                               |

|          | 1 = Incorrect STEP2<7:0> value was detected                                                                                         |

|          | 0 = Incorrect STEP2<7:0> value was not detected                                                                                     |

| bit 5    | DMTEVENT: Deadman Timer Event bit                                                                                                   |

|          | 1 = Deadman timer event was detected (counter expired or bad STEP1<7:0> or STEP2<7:0> value was entered prior to counter increment) |

|          | 0 = Deadman timer even was not detected                                                                                             |

| bit 4-1  | Unimplemented: Read as '0'                                                                                                          |

| bit 0    | WINOPN: Deadman Timer Clear Window bit                                                                                              |

|          | 1 = Deadman timer clear window is open                                                                                              |

|          | 0 = Deadman timer clear window is not open                                                                                          |

# TABLE 18-2: OUTPUT COMPARE 1 THROUGH OUTPUT COMPARE 9 REGISTER MAP (CONTINUED)

| ess                         |                                 | 0             |            |             |       |       |       |       |      | Bi    |        | -    |      | -            |        |              |          |      |              |

|-----------------------------|---------------------------------|---------------|------------|-------------|-------|-------|-------|-------|------|-------|--------|------|------|--------------|--------|--------------|----------|------|--------------|

| Virtual Address<br>(BF84_#) | Register<br>Name <sup>(1)</sup> | Bit Range     | 31/15      | 30/14       | 29/13 | 28/12 | 27/11 | 26/10 | 25/9 | 24/8  | 23/7   | 22/6 | 21/5 | 20/4         | 19/3   | 18/2         | 17/1     | 16/0 | All Resets   |

| 4A00                        | OC6CON                          | 31:16         | _          | _           | _     | _     | _     | _     | _    | _     | —      | _    | —    | —            |        | _            | —        | _    | 0000         |

|                             |                                 | 15:0          | ON         | —           | SIDL  | —     | —     | —     | —    | —     | —      | —    | OC32 | OCFLT        | OCTSEL |              | OCM<2:0> |      | 0000         |

| 4A10                        | OC6R                            | 31:16<br>15:0 | OC6R<31:0> |             |       |       |       |       |      |       |        |      |      |              |        | xxxx<br>xxxx |          |      |              |

| 4A20                        | OC6RS                           | 31:16<br>15:0 |            | OC6RS<31:0> |       |       |       |       |      |       |        |      |      |              |        | xxxx<br>xxxx |          |      |              |

| 4000                        | OC7CON                          | 31:16         | _          |             | —     | _     | -     | _     | -    | -     | —      |      | _    |              | —      | -            | _        | _    | 0000         |

| 4000                        |                                 | 15:0          | ON         |             | SIDL  | _     | -     | _     | -    | -     | —      |      | OC32 | OCFLT        | OCTSEL |              | OCM<2:0> |      | 0000         |

| 4C10                        | OC7R                            | 31:16<br>15:0 | OC/R<31:0> |             |       |       |       |       |      |       |        |      |      | xxxx<br>xxxx |        |              |          |      |              |

| 4C20                        | OC7RS                           | 31:16<br>15:0 |            |             |       |       |       |       |      | OC7RS | <31:0> |      |      |              |        |              |          |      | xxxx<br>xxxx |

| 4500                        | 00000                           | 31:16         | _          | _           | —     | —     | —     | —     | _    | —     | —      | —    | _    | —            | _      |              | _        | _    | 0000         |

| 4E00                        | OC8CON                          | 15:0          | ON         | -           | SIDL  | _     | -     | _     | -    | _     | _      | _    | OC32 | OCFLT        | OCTSEL |              | OCM<2:0> |      | 0000         |

| 4E10                        | OC8R                            | 31:16<br>15:0 |            |             |       |       |       |       |      | OC8R  | <31:0> |      |      |              |        |              |          |      | xxxx<br>xxxx |

| 4E20                        | OC8RS                           | 31:16<br>15:0 |            |             |       |       |       |       |      | OC8RS | <31:0> |      |      |              |        |              |          |      | xxxx<br>xxxx |

| 5000                        | 00000                           | 31:16         | _          | _           | _     | —     | _     | —     | _    | _     | —      | —    | —    | —            | _      | _            | _        | _    | 0000         |

| 5000                        | OC9CON                          | 15:0          | ON         | -           | SIDL  | —     | -     | —     | _    | _     | _      |      | OC32 | OCFLT        | OCTSEL |              | OCM<2:0> |      | 0000         |

| 5010                        | OC9R                            | 31:16         |            |             |       |       |       |       |      | OCOR  | ~21.0  |      |      |              |        |              |          |      | xxxx         |

| 5010                        | OCSR                            | 15:0          | OC9R<31:0> |             |       |       |       |       |      |       |        |      | xxxx |              |        |              |          |      |              |

| 5020                        | OC9RS                           | 31:16<br>15:0 |            |             |       |       |       |       |      | OC9RS | <31:0> |      |      |              |        |              |          |      | xxxx         |

Legend: x = unknown value on Reset; — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

Note 1: All registers in this table have corresponding CLR, SET and INV registers at their virtual addresses, plus offsets of 0x4, 0x8 and 0xC, respectively. See Section 12.3 "CLR, SET, and INV Registers" for more information.

# REGISTER 19-1: SPIxCON: SPI CONTROL REGISTER (CONTINUED)

- bit 5 MSTEN: Master Mode Enable bit

- 1 = Master mode

- 0 = Slave mode

- bit 4 **DISSDI:** Disable SDI bit<sup>(4)</sup>

- 1 = SDI pin is not used by the SPI module (pin is controlled by PORT function)

- 0 = SDI pin is controlled by the SPI module

- bit 3-2 STXISEL<1:0>: SPI Transmit Buffer Empty Interrupt Mode bits

- 11 = Interrupt is generated when the buffer is not full (has one or more empty elements)

- 10 = Interrupt is generated when the buffer is empty by one-half or more

- 01 = Interrupt is generated when the buffer is completely empty

- 00 = Interrupt is generated when the last transfer is shifted out of SPISR and transmit operations are complete

- bit 1-0 SRXISEL<1:0>: SPI Receive Buffer Full Interrupt Mode bits

- 11 = Interrupt is generated when the buffer is full

- 10 = Interrupt is generated when the buffer is full by one-half or more

- 01 = Interrupt is generated when the buffer is not empty

- 00 = Interrupt is generated when the last word in the receive buffer is read (i.e., buffer is empty)

- **Note 1:** This bit can only be written when the ON bit = 0. Refer to **Section 37.0 "Electrical Characteristics"** for maximum clock frequency requirements.

- 2: This bit is not used in the Framed SPI mode. The user should program this bit to '0' for the Framed SPI mode (FRMEN = 1).

- **3:** When AUDEN = 1, the SPI/I<sup>2</sup>S module functions as if the CKP bit is equal to '1', regardless of the actual value of the CKP bit.

- 4: This bit present for legacy compatibility and is superseded by PPS functionality on these devices (see Section 12.4 "Peripheral Pin Select (PPS)" for more information).

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |  |  |  |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|--|--|--|

| 04.04        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |  |  |  |

| 31:24        | _                 | -                 | _                 | _                 | _                 | -                 |                  | —                |  |  |  |

| 00.40        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |  |  |  |

| 23:16        | -                 | _                 | _                 | _                 | _                 | _                 | —                | —                |  |  |  |

| 45.0         | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |  |  |

| 15:8         | PTEN<             | :15:14>           | PTEN<13:8>        |                   |                   |                   |                  |                  |  |  |  |

| 7.0          | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |  |  |

| 7:0          | PTEN<7:0>         |                   |                   |                   |                   |                   |                  |                  |  |  |  |

#### REGISTER 23-6: PMAEN: PARALLEL PORT PIN ENABLE REGISTER

#### Legend:

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, re | ead as '0'         |  |

|-------------------|------------------|---------------------------|--------------------|--|

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared      | x = Bit is unknown |  |

bit 31-15 Unimplemented: Read as '0'

- bit 15-14 **PTEN<15:14>:** PMCS1 Strobe Enable bits

- 1 = PMA15 and PMA14 function as either PMA<15:14> or PMCS1 and PMCS2<sup>(1)</sup>

0 = PMA15 and PMA14 function as port I/O

- bit 13-2 **PTEN<13:2>:** PMP Address Port Enable bits

- 1 = PMA<13:2> function as PMP address lines

- 0 = PMA<13:2> function as port I/O

- bit 1-0 PTEN<1:0>: PMALH/PMALL Strobe Enable bits

- 1 = PMA1 and PMA0 function as either PMA<1:0> or PMALH and PMALL<sup>(2)</sup>

- 0 = PMA1 and PMA0 pads function as port I/O

- Note 1: The use of these pins as PMA15 and PMA14 or CS1 and CS2 is selected by the CSF<1:0> bits in the PMCON register.

- 2: The use of these pins as PMA1/PMA0 or PMALH/PMALL depends on the Address/Data Multiplex mode selected by bits ADRMUX<1:0> in the PMCON register.

| Name      |                              | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |  |

|-----------|------------------------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|--|

| SA_ENCIV1 | SA_ENCIV1 31:24 ENCIV<31:24> |                   |                   |                   |                   |                   |                   |                  |                  |  |

|           | 23:16                        |                   |                   |                   | ENCIV<23          | :16>              |                   |                  |                  |  |

|           | 15:8                         |                   |                   |                   | ENCIV<1           | 5:8>              |                   |                  |                  |  |

|           | 7:0                          |                   |                   |                   | ENCIV<7           | :0>               |                   |                  |                  |  |

| SA_ENCIV2 | 31:24                        |                   |                   |                   | ENCIV<31          | :24>              |                   |                  |                  |  |

|           | 23:16                        |                   |                   |                   | ENCIV<23          | :16>              |                   |                  |                  |  |

|           | 15:8                         |                   | ENCIV<15:8>       |                   |                   |                   |                   |                  |                  |  |

|           | 7:0                          |                   |                   |                   | ENCIV<7           | :0>               |                   |                  |                  |  |

| SA_ENCIV3 | 31:24                        |                   | ENCIV<31:24>      |                   |                   |                   |                   |                  |                  |  |

|           | 23:16                        |                   |                   |                   | ENCIV<23          | :16>              |                   |                  |                  |  |

|           | 15:8                         |                   |                   |                   | ENCIV<1           | 5:8>              |                   |                  |                  |  |

|           | 7:0                          |                   |                   |                   | ENCIV<7           | :0>               |                   |                  |                  |  |

| SA_ENCIV4 | 31:24                        |                   |                   |                   | ENCIV<31          | :24>              |                   |                  |                  |  |

|           | 23:16                        |                   | ENCIV<23:16>      |                   |                   |                   |                   |                  |                  |  |

|           | 15:8                         |                   |                   |                   | ENCIV<1           | 5:8>              |                   |                  |                  |  |

|           | 7:0                          |                   |                   |                   | ENCIV<7           | :0>               |                   |                  |                  |  |

# TABLE 26-4: CRYPTO ENGINE SECURITY ASSOCIATION STRUCTURE (CONTINUED)

| REGISTER | 28-2: ADCCON2: ADC CONTROL REGISTER 2 (CONTINUED)                                                                                                                                                                                                                                      |

|----------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| bit 14   | REFFLTIEN: Band Gap/VREF Voltage Fault Interrupt Enable bit                                                                                                                                                                                                                            |

|          | 1 = Interrupt will be generated when the REFFLT bit is set                                                                                                                                                                                                                             |

|          | 0 = No interrupt is generated when the REFFLT bit is set                                                                                                                                                                                                                               |

| bit 13   | EOSIEN: End of Scan Interrupt Enable bit                                                                                                                                                                                                                                               |

|          | 1 = Interrupt will be generated when EOSRDY bit is set                                                                                                                                                                                                                                 |

|          | 0 = No interrupt is generated when the EOSRDY bit is set                                                                                                                                                                                                                               |

| bit 12   | ADCEIOVR: Early Interrupt Request Override bit                                                                                                                                                                                                                                         |

|          | 1 = Early interrupt generation is not overridden and interrupt generation is controlled by the ADCEIEN1<br>and ADCEIEN2 registers                                                                                                                                                      |

|          | <ul> <li>Early interrupt generation is overridden and interrupt generation is controlled by the ADCGIRQEN1<br/>and ADCGIRQEN2 registers</li> </ul>                                                                                                                                     |

| bit 11   | Unimplemented: Read as '0'                                                                                                                                                                                                                                                             |

| bit 10-8 | ADCEIS<2:0>: Shared ADC (ADC7) Early Interrupt Select bits                                                                                                                                                                                                                             |

|          | These bits select the number of clocks (TAD7) prior to the arrival of valid data that the associated interrupt is generated.                                                                                                                                                           |

|          | 111 = The data ready interrupt is generated 8 ADC clocks prior to end of conversion                                                                                                                                                                                                    |

|          | 110 = The data ready interrupt is generated 7 ADC clocks prior to end of conversion                                                                                                                                                                                                    |

|          | •                                                                                                                                                                                                                                                                                      |

|          | •                                                                                                                                                                                                                                                                                      |

|          | <ul> <li>001 = The data ready interrupt is generated 2 ADC module clocks prior to end of conversion</li> <li>000 = The data ready interrupt is generated 1 ADC module clock prior to end of conversion</li> </ul>                                                                      |

|          | Note: All options are available when the selected resolution, set by the SELRES<1:0> bits (ADCCON1<22:21>), is 12-bit or 10-bit. For a selected resolution of 8-bit, options from '000' to '101' are valid. For a selected resolution of 6-bit, options from '000' to '011' are valid. |

| bit 7    | Unimplemented: Read as '0'                                                                                                                                                                                                                                                             |

| bit 6-0  | ADCDIV<6:0>: Shared ADC (ADC7) Clock Divider bits                                                                                                                                                                                                                                      |

|          | 1111111 = 254 * TQ = TAD7                                                                                                                                                                                                                                                              |

|          | •                                                                                                                                                                                                                                                                                      |

|          | •                                                                                                                                                                                                                                                                                      |

|          | 0000011 = 6 * TQ = TAD7                                                                                                                                                                                                                                                                |

|          | 0000010 = 4 * TQ = TAD7                                                                                                                                                                                                                                                                |

|          | 0000001 = 2 * TQ = TAD7<br>0000000 = Reserved                                                                                                                                                                                                                                          |

|          |                                                                                                                                                                                                                                                                                        |

The ADCDIV<6:0> bits divide the ADC control clock (TQ) to generate the clock for the Shared ADC, ADC7 (TAD7).

| REGIS   | TER 28-4: ADCTRGMODE: ADC TRIGGERING MODE FOR DEDICATED ADC REGISTER                                                                                                                 |

|---------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| bit 9   | <b>STRGEN1:</b> ADC1 Presynchronized Triggers bit<br>1 = ADC1 uses presynchronized triggers<br>0 = ADC1 does not use presynchronized triggers                                        |

| bit 8   | <b>STRGEN0:</b> ADC0 Presynchronized Triggers bit<br>1 = ADC0 uses presynchronized triggers<br>0 = ADC0 does not use presynchronized triggers                                        |

| bit 7-5 | Unimplemented: Read as '0'                                                                                                                                                           |

| bit 4   | <b>SSAMPEN4:</b> ADC4 Synchronous Sampling bit<br>1 = ADC4 uses synchronous sampling for the first sample after being idle or disabled<br>0 = ADC4 does not use synchronous sampling |

| bit 3   | <b>SSAMPEN3:</b> ADC3 Synchronous Sampling bit<br>1 = ADC3 uses synchronous sampling for the first sample after being idle or disabled<br>0 = ADC3 does not use synchronous sampling |

| bit 2   | <b>SSAMPEN2:</b> ADC2Synchronous Sampling bit<br>1 = ADC2 uses synchronous sampling for the first sample after being idle or disabled<br>0 = ADC2 does not use synchronous sampling  |

| bit 1   | <b>SSAMPEN1:</b> ADC1 Synchronous Sampling bit<br>1 = ADC1 uses synchronous sampling for the first sample after being idle or disabled<br>0 = ADC1 does not use synchronous sampling |

| bit 0   | <b>SSAMPEN0:</b> ADC0 Synchronous Sampling bit<br>1 = ADC0 uses synchronous sampling for the first sample after being idle or disabled                                               |

0 = ADC0 does not use synchronous sampling

| Bit<br>Range | Bit<br>31/23/15/7      | Bit<br>30/22/14/6      | Bit<br>29/21/13/5      | Bit<br>28/20/12/4      | Bit<br>27/19/11/3      | Bit<br>26/18/10/2      | Bit<br>25/17/9/1       | Bit<br>24/16/8/0       |

|--------------|------------------------|------------------------|------------------------|------------------------|------------------------|------------------------|------------------------|------------------------|

| 04.04        | U-0                    |

| 31:24        |                        | —                      | —                      | —                      | —                      | —                      | —                      | —                      |

| 22:46        | U-0                    |

| 23:16        | —                      | —                      | _                      | —                      | _                      | —                      | —                      | —                      |

| 45.0         | U-0                    | U-0                    | U-0                    | R-0, HS, HC            |

| 15:8         | —                      | —                      | _                      | EIRDY44 <sup>(2)</sup> | EIRDY43 <sup>(2)</sup> | EIRDY42 <sup>(2)</sup> | EIRDY41 <sup>(2)</sup> | EIRDY40 <sup>(2)</sup> |

| 7.0          | R-0, HS, HC            |

| 7:0          | EIRDY39 <sup>(2)</sup> | EIRDY38 <sup>(2)</sup> | EIRDY37 <sup>(2)</sup> | EIRDY36 <sup>(2)</sup> | EIRDY35 <sup>(2)</sup> | EIRDY34 <sup>(1)</sup> | EIRDY33 <sup>(1)</sup> | EIRDY32 <sup>(1)</sup> |

# REGISTER 28-31: ADCEISTAT2: ADC EARLY INTERRUPT STATUS REGISTER 2

| Legend:           | HS = Hardware Set | HC = Hardware Cleared                    |  |  |  |

|-------------------|-------------------|------------------------------------------|--|--|--|

| R = Readable bit  | W = Writable bit  | U = Unimplemented bit, read as '0'       |  |  |  |

| -n = Value at POR | '1' = Bit is set  | 0' = Bit is cleared $x = Bit is unknown$ |  |  |  |

#### bit 31-13 Unimplemented: Read as '0'

bit 31-0 **EIRDY44:EIRDY32:** Early Interrupt for Corresponding Analog Input Ready bits

- 1 = This bit is set when the early interrupt event occurs for the specified analog input. An interrupt will be generated if early interrupts are enabled in the ADCEIEN2 register. For the Class 1 analog inputs, this bit will set as per the configuration of the ADCEIS<2:0> bits in the ADCXTIME register. For the shared ADC module, this bit will be set as per the configuration of the ADCEIS<2:0> bits in the ADCEIS<2:0> bits in the ADCCON2 register.

- 0 = Interrupts are disabled

**Note 1:** This bit is not available on 64-pin devices.

2: This bit is not available on 64-pin and 100-pin devices.

# REGISTER 30-15: ETHSTAT: ETHERNET CONTROLLER STATUS REGISTER (CONTINUED)

- bit 6 **TXBUSY:** Transmit Busy bit<sup>(2,6)</sup>

- 1 = TX logic is receiving data

0 = TX logic is idle

This bit indicates that a packet is currently being transmitted. A change in this status bit is not necessarily reflected by the TXDONE interrupt, as TX packets may be aborted or rejected by the MAC.

bit 5 **RXBUSY:** Receive Busy bit<sup>(3,6)</sup>

1 = RX logic is receiving data 0 = RX logic is idle

This bit indicates that a packet is currently being received. A change in this status bit is not necessarily reflected by the RXDONE interrupt, as RX packets may be aborted or rejected by the RX filter.

- bit 4-0 Unimplemented: Read as '0'

- Note 1: This bit is only used for RX operations.

- **2:** This bit is only affected by TX operations.

- **3:** This bit is only affected by RX operations.

- 4: This bit is affected by TX and RX operations.

- 5: This bit will be set when the ON bit (ETHCON1 < 15 >) = 1.

- 6: This bit will be *cleared* when the ON bit (ETHCON1<15>) = 0.

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|

| 24.24        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 31:24        | —                 | —                 | _                 | _                 | _                 | —                 | _                | —                |

| 00.40        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 23:16        | —                 | —                 | _                 | _                 | _                 | —                 | _                | —                |

| 45.0         | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |

| 15:8         |                   |                   |                   | ALGNERRC          | NT<15:8>          |                   |                  |                  |

| 7.0          | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |

| 7:0          |                   |                   |                   | ALGNERRO          | CNT<7:0>          |                   |                  |                  |

# REGISTER 30-22: ETHALGNERR: ETHERNET CONTROLLER ALIGNMENT ERRORS STATISTICS REGISTER

#### Legend:

| Legena.           |                  |                           |                    |  |

|-------------------|------------------|---------------------------|--------------------|--|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, re | ead as '0'         |  |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared      | x = Bit is unknown |  |

#### bit 31-16 Unimplemented: Read as '0'

bit 15-0 ALGNERRCNT<15:0>: Alignment Error Count bits

Increment count for frames with alignment errors. Note that an alignment error is a frame that has an FCS error and the frame length in bits is not an integral multiple of 8 bits (a.k.a., dribble nibble)

#### **Note 1:** This register is only used for RX operations.

2: This register is automatically cleared by hardware after a read operation, unless the byte enables for bytes 0/1 are '0'.

3: It is recommended to use the SET, CLR, or INV registers to set or clear any bit in this register. Setting or clearing any bits in this register should be only done for debug/test purposes.

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|

| 31:24        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 51.24        |                   | _                 |                   | —                 | —                 |                   |                  | —                |

| 22:16        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 23:16        | —                 | —                 | —                 | —                 | —                 | —                 | -                | —                |

| 15.0         | R/W-P             | R/W-P             | R/W-P             | R/W-P             | R/W-P             | R/W-P             | R/W-P            | R/W-P            |

| 15:8         |                   |                   |                   | STNADDR6<         | :7:0>             |                   |                  |                  |

| 7.0          | R/W-P             | R/W-P             | R/W-P             | R/W-P             | R/W-P             | R/W-P             | R/W-P            | R/W-P            |

| 7:0          |                   |                   |                   | STNADDR5<         | :7:0>             |                   |                  |                  |

#### REGISTER 30-37: EMAC1SA0: ETHERNET CONTROLLER MAC STATION ADDRESS 0 REGISTER

| Legend:           |                  | P = Programmable bit   |                    |

|-------------------|------------------|------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, | read as '0'        |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared   | x = Bit is unknown |

bit 31-16 Unimplemented: Read as '0'

- bit 15-8 **STNADDR6<7:0>:** Station Address Octet 6 bits These bits hold the sixth transmitted octet of the station address.

- bit 7-0 **STNADDR5<7:0>:** Station Address Octet 5 bits These bits hold the fifth transmitted octet of the station address.

Note 1: Both 16-bit and 32-bit accesses are allowed to these registers (including the SET, CLR and INV registers). 8-bit accesses are not allowed and are ignored by the hardware.

2: This register is loaded at reset from the factory preprogrammed station address.

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|

| 24.24        | r-0               | r-1               | r-1               | r-1               | r-1               | r-1               | r-1              | r-1              |

| 31:24        | _                 | —                 | _                 | _                 | _                 | _                 | _                | —                |

| 22.10        | r-1               | r-1               | r-1               | r-1               | r-1               | r-1               | r-1              | r-1              |

| 23:16        | —                 | —                 | _                 | _                 | —                 | —                 | _                | —                |

| 45.0         | r-1               | r-1               | r-1               | r-1               | r-1               | r-1               | r-1              | r-1              |

| 15:8         | _                 | —                 | _                 | _                 | _                 | —                 | _                | —                |

| 7.0          | r-1               | r-1               | r-1               | r-1               | r-1               | r-1               | r-1              | r-1              |

| 7:0          | _                 | _                 | _                 | _                 | _                 | _                 | _                | _                |

#### REGISTER 34-1: DEVSIGN0/ADEVSIGN0: DEVICE SIGNATURE WORD 0 REGISTER

| Legend:           | r = Reserved bit |                          |                    |

|-------------------|------------------|--------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, r | ead as '0'         |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared     | x = Bit is unknown |

bit 31 Reserved: Write as '0'

bit 30-0 Reserved: Write as '1'

**Note:** The DEVSIGN1 through DEVSIGN3 and ADEVSIGN1 through ADEVSIGN3 registers are used for Quad Word programming operation when programming the DEVSIGN0/ADESIGN0 registers, and do not contain any valid information.

#### REGISTER 34-2: DEVCP0/ADEVCP0: DEVICE CODE-PROTECT 0 REGISTER

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|

| 24.24        | r-1               | r-1               | r-1               | R/P               | r-1               | r-1               | r-1              | r-1              |

| 31:24        | _                 | —                 | —                 | CP                | —                 | _                 | _                | _                |

| 00.40        | r-1               | r-1               | r-1               | r-1               | r-1               | r-1               | r-1              | r-1              |

| 23:16        | _                 | —                 | —                 | _                 | —                 | _                 | _                | —                |

| 45.0         | r-1               | r-1               | r-1               | r-1               | r-1               | r-1               | r-1              | r-1              |

| 15:8         | _                 | —                 | —                 | _                 | —                 | _                 | _                | _                |

| 7.0          | r-1               | r-1               | r-1               | r-1               | r-1               | r-1               | r-1              | r-1              |

| 7:0          | _                 | _                 | _                 | _                 | _                 | _                 | _                | _                |

| Legend:           | r = Reserved bit | P = Programmable bit |                    |

|-------------------|------------------|----------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented b  | it, read as '0'    |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared | x = Bit is unknown |

bit 31-29 Reserved: Write as '1'

bit 28 **CP:** Code-Protect bit

Prevents boot and program Flash memory from being read or modified by an external programming device. 1 = Protection is disabled

0 = Protection is enabled

bit 27-0 Reserved: Write as '1'

Note: The DEVCP1 through DEVCP3 and ADEVCP1 through ADEVCP3 registers are used for Quad Word programming operation when programming the DEVCP0/ADEVCP0 registers, and do not contain any valid information.

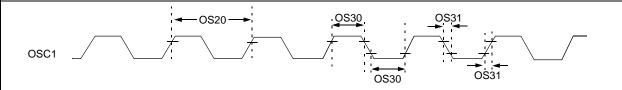

# FIGURE 37-2: EXTERNAL CLOCK TIMING

#### TABLE 37-17: EXTERNAL CLOCK TIMING REQUIREMENTS

| AC CHARACTERISTICS |               | $\begin{tabular}{lllllllllllllllllllllllllllllllllll$                                                  |              |                        |         | or Industrial |                                           |

|--------------------|---------------|--------------------------------------------------------------------------------------------------------|--------------|------------------------|---------|---------------|-------------------------------------------|

| Param.<br>No.      | Symbol        | Characteristics                                                                                        | Minimum      | Typical <sup>(1)</sup> | Maximum | Units         | Conditions                                |

| OS10               | Fosc          | External CLKI Frequency<br>(External clocks allowed only<br>in EC and ECPLL modes)                     | DC           |                        | 64      | MHz           | EC <b>(Note 2,3)</b>                      |

| OS13               |               | Oscillator Crystal Frequency                                                                           | 4            | —                      | 32      | MHz           | HS (Note 2,3)                             |

| OS15               |               |                                                                                                        | 32           | 32.768                 | 100     | kHz           | Sosc (Note 2)                             |

| OS20               | Tosc          | Tosc = 1/Fosc                                                                                          | _            |                        | —       | _             | See parameter<br>OS10 for Fosc<br>value   |

| OS30               | TosL,<br>TosH | External Clock In (OSC1)<br>High or Low Time                                                           | 0.375 x Tosc | —                      | _       | ns            | EC (Note 2)                               |

| OS31               | TosR,<br>TosF | External Clock In (OSC1)<br>Rise or Fall Time                                                          | —            | —                      | 7.5     | ns            | EC (Note 2)                               |

| OS40               | Тоѕт          | Oscillator Start-up Timer Period<br>(Only applies to HS, HSPLL,<br>and Sosc Clock Oscillator<br>modes) | _            | 1024                   | _       | Tosc          | (Note 2)                                  |

| OS41               | TFSCM         | Primary Clock Fail Safe<br>Time-out Period                                                             | —            | 2                      | _       | ms            | (Note 2)                                  |

| OS42               | Gм            | External Oscillator<br>Transconductance                                                                | —            | 400                    | _       | µA/V          | VDD = 3.3V,<br>TA = +25°C, HS<br>(Note 2) |

**Note 1:** Data in "Typical" column is at 3.3V, +25°C unless otherwise stated. Parameters are characterized but are not tested.

**2:** This parameter is characterized, but not tested in manufacturing.

3: See parameter OS50 for PLL input frequency limitations.

## **39.1 DC Characteristics**

TABLE 39-1: OPERATING MIPS VS. VOLTAGE

| Characteristic | VDD Range              | Temp. Range    | Max. Frequency     | Comment |  |

|----------------|------------------------|----------------|--------------------|---------|--|

|                | (in Volts)<br>(Note 1) | (in °C)        | PIC32MZ EF Devices |         |  |

| MDC5           | 2.1V-3.6V              | -40°C to +85°C | 252 MHz            |         |  |

**Note 1:** Overall functional device operation at VBORMIN < VDD < VDDMIN is guaranteed, but not characterized. All device Analog modules, such as ADC, etc., will function, but with degraded performance below VDDMIN. Refer to parameter BO10 in Table 37-5 for BOR values.

#### TABLE 39-2: DC CHARACTERISTICS: OPERATING CURRENT (IDD)

| DC CHARACTERISTICS                     |                        |                        | Standard Operating Conditions: 2.1V to 3.6V(unless otherwise stated)Operating temperature $-40^{\circ}C \le TA \le +85^{\circ}C$ for Industrial |                    |  |

|----------------------------------------|------------------------|------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------|--------------------|--|

| Parameter<br>No.                       | Typical <sup>(3)</sup> | Maximum <sup>(6)</sup> | Units Conditions                                                                                                                                |                    |  |

| Operating Current (IDD) <sup>(1)</sup> |                        |                        |                                                                                                                                                 |                    |  |

| MDC27a                                 | 156                    | 170                    | mA                                                                                                                                              | 252 MHz (Note 2)   |  |

| MDC27b                                 | 115                    | 135                    | mA                                                                                                                                              | 252 MHz (Note 4,5) |  |

**Note 1:** A device's IDD supply current is mainly a function of the operating voltage and frequency. Other factors, such as PBCLK (Peripheral Bus Clock) frequency, number of peripheral modules enabled, internal code execution pattern, I/O pin loading and switching rate, oscillator type, as well as temperature, can have an impact on the current consumption.

- **2:** The test conditions for IDD measurements are as follows:

- Oscillator mode is EC+PLL with OSC1 driven by external square wave from rail-to-rail, (OSC1 input clock input over/undershoot < 100 mV required)

- OSC2/CLKO is configured as an I/O input pin

- USB PLL is disabled (USBMD = 1), VUSB3V3 is connected to VSS

- CPU, Program Flash, and SRAM data memory are operational, Program Flash memory Wait states are equal to four

- L1 Cache and Prefetch modules are enabled

- No peripheral modules are operating, (ON bit = 0), and the associated PMD bit is set. All clocks are disabled ON bit (PBxDIV<15>) = 0 (x ≠ 1,7)

- WDT, DMT, Clock Switching, Fail-Safe Clock Monitor, and Secondary Oscillator are disabled

- All I/O pins are configured as inputs and pulled to Vss

- MCLR = VDD

- CPU executing while(1) statement from Flash

- RTCC and JTAG are disabled

- **3:** Data in "Typical" column is at 3.3V, +25°C at specified operating frequency unless otherwise stated. Parameters are for design guidance only and are not tested.

- 4: This parameter is characterized, but not tested in manufacturing.

- 5: Note 2 applies with the following exceptions: L1 Cache and Prefetch modules are disabled, Program Flash memory Wait states are equal to seven.

- **6:** Data in the "Maximum" column is at 3.3V, +85°C at specified operating frequency, unless otherwise stated. Parameters are for design guidance only and are not tested.

| DC CHARACTERISTICS                        | Standard Operating Conditions: 2.1V to 3.6V(unless otherwise stated)Operating temperature $-40^{\circ}C \le TA \le +85^{\circ}C$ for Industrial |       |            |  |  |

|-------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------|-------|------------|--|--|

| Required Flash Wait States <sup>(1)</sup> | SYSCLK                                                                                                                                          | Units | Conditions |  |  |

| With ECC:                                 |                                                                                                                                                 |       |            |  |  |

| 0 Wait states                             | 0 < SYSCLK ≤ 60                                                                                                                                 |       |            |  |  |

| 1 Wait state                              | 60 < SYSCLK ≤ 120                                                                                                                               | MHz   | —          |  |  |

| 2 Wait states                             | $120 < SYSCLK \le 200$                                                                                                                          |       |            |  |  |