#### Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XE

| Product Status             | Active                                                                            |

|----------------------------|-----------------------------------------------------------------------------------|

| Core Processor             | MIPS32® M-Class                                                                   |

| Core Size                  | 32-Bit Single-Core                                                                |

| Speed                      | 200MHz                                                                            |

| Connectivity               | EBI/EMI, Ethernet, I <sup>2</sup> C, PMP, SPI, SQI, UART/USART, USB OTG           |

| Peripherals                | Brown-out Detect/Reset, DMA, I <sup>2</sup> S, POR, PWM, WDT                      |

| Number of I/O              | 78                                                                                |

| Program Memory Size        | 512KB (512K x 8)                                                                  |

| Program Memory Type        | FLASH                                                                             |

| EEPROM Size                | -                                                                                 |

| RAM Size                   | 128K x 8                                                                          |

| Voltage - Supply (Vcc/Vdd) | 2.1V ~ 3.6V                                                                       |

| Data Converters            | A/D 40x12b                                                                        |

| Oscillator Type            | Internal                                                                          |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                                 |

| Mounting Type              | Surface Mount                                                                     |

| Package / Case             | 100-TQFP                                                                          |

| Supplier Device Package    | 100-TQFP (12x12)                                                                  |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic32mz0512efe100t-i-pt |

|                            |                                                                                   |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

## 2.9 Designing for High-Speed Peripherals

The PIC32MZ EF family devices have peripherals that operate at frequencies much higher than typical for an embedded environment. Table 2-1 lists the peripherals that produce high-speed signals on their external pins:

#### TABLE 2-1: PERIPHERALS THAT PRODUCE HS SIGNALS ON EXTERNAL PINS

| Peripheral | High-Speed<br>Signal Pins   | Maximum<br>Speed on<br>Signal Pin |

|------------|-----------------------------|-----------------------------------|

| EBI        | EBIAx,<br>EBIDx             | 50 MHz                            |

| SQI1       | SQICLK,<br>SQICSx,<br>SQIDx | 50 MHz                            |

| HS USB     | D+, D-                      | 480 MHz                           |

Due to these high-speed signals, it is important to consider several factors when designing a product that uses these peripherals, as well as the PCB on which these components will be placed. Adhering to these recommendations will help achieve the following goals:

- Minimize the effects of electromagnetic interference to the proper operation of the product

- Ensure signals arrive at their intended destination at the same time

- Minimize crosstalk

- Maintain signal integrity

- Reduce system noise

- Minimize ground bounce and power sag

## 2.9.1 SYSTEM DESIGN

## 2.9.1.1 Impedance Matching

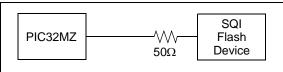

When selecting parts to place on high-speed buses, particularly the SQI bus, if the impedance of the peripheral device does not match the impedance of the pins on the PIC32MZ EF device to which it is connected, signal reflections could result, thereby degrading the quality of the signal.

If it is not possible to select a product that matches impedance, place a series resistor at the load to create the matching impedance. See Figure 2-4 for an example.

#### FIGURE 2-4: SERIES RESISTOR

## 2.9.1.2 PCB Layout Recommendations

The following list contains recommendations that will help ensure the PCB layout will promote the goals previously listed.

#### Component Placement

- Place bypass capacitors as close to their component power and ground pins as possible, and place them on the same side of the PCB

- Devices on the same bus that have larger setup times should be placed closer to the PIC32MZ EF device

#### • Power and Ground

- Multi-layer PCBs will allow separate power and ground planes

- Each ground pin should be connected to the ground plane individually

- Place bypass capacitor vias as close to the pad as possible (preferably inside the pad)

- If power and ground planes are not used, maximize width for power and ground traces

- Use low-ESR, surface-mount bypass capacitors

#### • Clocks and Oscillators

- Place crystals as close as possible to the PIC32MZ EF device OSC/SOSC pins

- Do not route high-speed signals near the clock or oscillator

- Avoid via usage and branches in clock lines (SQICLK)

- Place termination resistors at the end of clock lines

- Traces

- Higher-priority signals should have the shortest traces

- Match trace lengths for parallel buses (EBIAx, EBIDx, SQIDx)

- Avoid long run lengths on parallel traces to reduce coupling

- Make the clock traces as straight as possible

- Use rounded turns rather than right-angle turns

- Have traces on different layers intersect on right angles to minimize crosstalk

- Maximize the distance between traces, preferably no less than three times the trace width

- Power traces should be as short and as wide as possible

- High-speed traces should be placed close to the ground plane

| Register<br>Number | Register<br>Name | Function                                                                                                                                  |

|--------------------|------------------|-------------------------------------------------------------------------------------------------------------------------------------------|

| 12                 | Status           | Processor status and control.                                                                                                             |

|                    | IntCtl           | Interrupt control of vector spacing.                                                                                                      |

|                    | SRSCtl           | Shadow register set control.                                                                                                              |

|                    | SRSMap           | Shadow register mapping control.                                                                                                          |

|                    | View_IPL         | Allows the Priority Level to be read/written without                                                                                      |

|                    |                  | extracting or inserting that bit from/to the Status register.                                                                             |

|                    | SRSMAP2          | Contains two 4-bit fields that provide the mapping from a vector number to the shadow set number to use when servicing such an interrupt. |

| 13                 | Cause            | Describes the cause of the last exception.                                                                                                |

|                    | NestedExc        | Contains the error and exception level status bit values that existed prior to the current exception.                                     |

|                    | View_RIPL        | Enables read access to the RIPL bit that is available in the Cause register.                                                              |

| 14                 | EPC              | Program counter at last exception.                                                                                                        |

|                    | NestedEPC        | Contains the exception program counter that existed prior to the current exception.                                                       |

| 15                 | PRID             | Processor identification and revision                                                                                                     |

|                    | Ebase            | Exception base address of exception vectors.                                                                                              |

|                    | CDMMBase         | Common device memory map base.                                                                                                            |

| 16                 | Config           | Configuration register.                                                                                                                   |

|                    | Config1          | Configuration register 1.                                                                                                                 |

|                    | Config2          | Configuration register 2.                                                                                                                 |

|                    | Config3          | Configuration register 3.                                                                                                                 |

|                    | Config4          | Configuration register 4.                                                                                                                 |

|                    | Config5          | Configuration register 5.                                                                                                                 |

|                    | Config7          | Configuration register 7.                                                                                                                 |

| 17                 | LLAddr           | Load link address (MPU only).                                                                                                             |

| 18                 | WatchLo          | Low-order watchpoint address (MPU only).                                                                                                  |

| 19                 | WatchHi          | High-order watchpoint address (MPU only).                                                                                                 |

| 20-22              | Reserved         | Reserved in the PIC32 core.                                                                                                               |

| 23                 | Debug            | EJTAG debug register.                                                                                                                     |

|                    | TraceControl     | EJTAG trace control.                                                                                                                      |

|                    | TraceControl2    | EJTAG trace control 2.                                                                                                                    |

|                    | UserTraceData1   | EJTAG user trace data 1 register.                                                                                                         |

|                    | TraceBPC         | EJTAG trace breakpoint register.                                                                                                          |

|                    | Debug2           | Debug control/exception status 1.                                                                                                         |

| 24                 | DEPC             | Program counter at last debug exception.                                                                                                  |

|                    | UserTraceData2   |                                                                                                                                           |

| 25                 | PerfCtl0         | Performance counter 0 control.                                                                                                            |

|                    | PerfCnt0         | Performance counter 0.                                                                                                                    |

|                    | PerfCtl1         | Performance counter 1 control.                                                                                                            |

|                    | PerfCnt1         | Performance counter 1.                                                                                                                    |

| 26                 | ErrCtl           | Software test enable of way-select and data RAM arrays for I-Cache and D-Cache (MPU only).                                                |

| 27                 | Reserved         | Reserved in the PIC32 core.                                                                                                               |

| 28                 | TagLo/DataLo     | Low-order portion of cache tag interface (MPU only).                                                                                      |

| 29                 | Reserved         | Reserved in the PIC32 core.                                                                                                               |

| 30                 | ErrorEPC         | Program counter at last error exception.                                                                                                  |

| 31                 | DeSave           | Debug exception save.                                                                                                                     |

|                    |                  |                                                                                                                                           |

## TABLE 4-19: SYSTEM BUS TARGET 11 REGISTER MAP

| SSS                         |                  |           |             |       |       |          |          |       |       |      | Bits     |       |          |      |        |        |         |        |               |

|-----------------------------|------------------|-----------|-------------|-------|-------|----------|----------|-------|-------|------|----------|-------|----------|------|--------|--------|---------|--------|---------------|

| Virtual Address<br>(BF8F_#) | Register<br>Name | Bit Range | 31/15       | 30/14 | 29/13 | 28/12    | 27/11    | 26/10 | 25/9  | 24/8 | 23/7     | 22/6  | 21/5     | 20/4 | 19/3   | 18/2   | 17/1    | 16/0   | All<br>Resets |

| AC20                        |                  |           | 31:16 MULTI |       | —     | —        |          | CODE  | <3:0> |      | _        | —     |          |      | —      | —      | —       |        | 0000          |

| AC20                        | OZO OBTITELOGI   | 15:0      |             |       |       | INI      | ΓID<7:0> |       |       |      |          | REGIO | N<3:0>   |      | —      | C      | MD<2:0> |        | 0000          |

| AC24                        | AC24 SBT11ELOG2  | 31:16     | _           | -     | _     | —        | -        | -     | _     | -    | _        | -     |          |      | —      | -      | -       |        | 0000          |

| AC24                        | 3BTTTELOG2       | 15:0      | _           | -     | _     | —        | -        | -     | _     | -    | _        | -     |          |      | —      | -      | GROU    | P<1:0> | 0000          |

| AC28                        | SBT11ECON        | 31:16     | _           | -     | _     | —        | -        | -     | _     | ERRP | _        | -     |          |      | —      | -      | -       |        | 0000          |

| AC20                        | SBITTECON        | 15:0      | _           | -     | _     | —        | -        | -     | _     | -    | _        | -     |          |      | —      | -      | -       |        | 0000          |

| AC30                        | SBT11ECLRS       | 31:16     | —           | —     | —     | —        | —        | —     | —     | —    | _        | —     | _        | _    | —      | _      | —       | -      | 0000          |

| AC30                        | SBITTECERS       | 15:0      | —           | _     | —     | —        | —        | —     | —     | —    | _        | —     | _        | _    | —      | _      | —       | CLEAR  | 0000          |

| AC 38                       | SBT11ECLRM       | 31:16     | —           | _     | —     | —        | —        | —     | —     | —    | _        | —     | _        | _    | —      | _      | —       | _      | 0000          |

| AC30                        | SBITTECERM       | 15:0      | —           | -     | _     | —        | _        | _     | —     | _    | _        | —     | _        | _    | _      | —      | —       | CLEAR  | 0000          |

| AC40                        | SBT11REG0        | 31:16     |             |       |       |          |          |       |       | BA   | SE<21:6> |       |          |      |        | -      |         |        | xxxx          |

| 7040                        | SBITIKEGO        | 15:0      |             | _     | BA    | ASE<5:0> | -        | -     | PRI   | —    |          | -     | SIZE<4:0 | >    |        | —      | —       |        | xxxx          |

| AC50                        | SBT11RD0         | 31:16     | —           | —     | _     | _        | _        | _     | —     | _    | _        | _     | _        | _    | _      | _      | _       | _      | xxxx          |

| 7030                        | 30111120         | 15:0      | —           | —     | _     | _        | _        | _     | —     | _    | _        | _     | _        | _    | GROUP3 | GROUP2 | GROUP1  | GROUP0 | xxxx          |

| AC58                        | SBT11WR0         | 31:16     | —           | —     | —     | —        | —        | —     | —     | —    | —        | —     | _        |      | —      | —      | —       |        | xxxx          |

| //000                       | OBIIII           | 15:0      | —           | —     | —     | —        | —        | —     | —     | —    | —        | —     | —        | _    | GROUP3 | GROUP2 | GROUP1  | GROUP0 | xxxx          |

| AC60                        | SBT11REG1        | 31:16     |             |       |       |          |          |       |       | BA   | SE<21:6> |       |          |      |        |        |         |        | xxxx          |

| //000                       | OBTINEOT         | 15:0      |             |       | BA    | ASE<5:0> |          |       | PRI   |      |          |       | SIZE<4:0 | >    |        | _      | _       | _      | xxxx          |

| AC70                        | SBT11RD1         | 31:16     | —           | —     | —     | —        | —        | —     | —     | —    | —        | —     | _        | _    | —      | —      | —       | —      | xxxx          |

|                             | 55111151         | 15:0      | —           | —     | —     | —        | —        | —     | —     | —    | —        | —     | _        | _    | GROUP3 | GROUP2 | GROUP1  | GROUP0 | xxxx          |

| AC78                        | SBT11WR1         | 31:16     | —           | —     | —     | —        | —        | —     | —     | —    | —        | —     | _        | _    | —      | —      | —       | —      | xxxx          |

|                             | 021110101        | 15:0      | _           | —     | _     | —        | _        | _     | _     | _    | _        | _     | -        | -    | GROUP3 | GROUP2 | GROUP1  | GROUP0 | xxxx          |

Legend: x = unknown value on Reset; - = unimplemented, read as '0'. Reset values are shown in hexadecimal.

**Note:** For reset values listed as 'xxxx', please refer to Table 4-6 for the actual reset values.

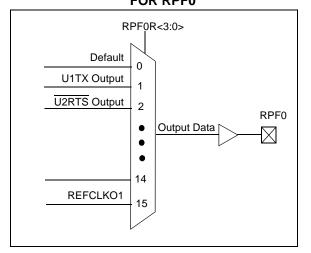

## 12.4.5 OUTPUT MAPPING

In contrast to inputs, the outputs of the PPS options are mapped on the basis of the pin. In this case, a control register associated with a particular pin dictates the peripheral output to be mapped. The RPnR registers (Register 12-2) are used to control output mapping. Like the [*pin name*]R registers, each register contains sets of 4 bit fields. The value of the bit field corresponds to one of the peripherals, and that peripheral's output is mapped to the pin (see Table 12-3 and Figure 12-3).

A null output is associated with the output register reset value of '0'. This is done to ensure that remappable outputs remain disconnected from all output pins by default.

#### FIGURE 12-3: EXAMPLE OF MULTIPLEXING OF REMAPPABLE OUTPUT FOR RPF0

## 12.4.6 CONTROLLING CONFIGURATION CHANGES

Because peripheral remapping can be changed during run time, some restrictions on peripheral remapping are needed to prevent accidental configuration changes. PIC32MZ EF devices include two features to prevent alterations to the peripheral map:

- Control register lock sequence

- Configuration bit select lock

## 12.4.6.1 Control Register Lock

Under normal operation, writes to the RPnR and [*pin name*]R registers are not allowed. Attempted writes appear to execute normally, but the contents of the registers remain unchanged. To change these registers, they must be unlocked in hardware. The register lock is controlled by the IOLOCK Configuration bit (CFGCON<13>). Setting IOLOCK prevents writes to the control registers; clearing IOLOCK allows writes.

To set or clear the IOLOCK bit, an unlock sequence must be executed. Refer to **Section 42. "Oscillators with Enhanced PLL"** in the *"PIC32 Family Reference Manual"* for details.

## 12.4.6.2 Configuration Bit Select Lock

As an additional level of safety, the device can be configured to prevent more than one write session to the RPnR and [*pin name*]R registers. The IOL1WAY Configuration bit (DEVCFG3<29>) blocks the IOL0CK bit from being cleared after it has been set once. If IOLOCK remains set, the register unlock procedure does not execute, and the PPS control registers cannot be written to. The only way to clear the bit and reenable peripheral remapping is to perform a device Reset.

In the default (unprogrammed) state, IOL1WAY is set, restricting users to one write session.

## 18.1 Output Compare Control Registers

## TABLE 18-2: OUTPUT COMPARE 1 THROUGH OUTPUT COMPARE 9 REGISTER MAP

| ess                         |                                 |               |         |             |           |       |       |       |      | Bi    | ts     |      |              |            |             |      |               |      |              |

|-----------------------------|---------------------------------|---------------|---------|-------------|-----------|-------|-------|-------|------|-------|--------|------|--------------|------------|-------------|------|---------------|------|--------------|

| Virtual Address<br>(BF84_#) | Register<br>Name <sup>(1)</sup> | Bit Range     | 31/15   | 30/14       | 29/13     | 28/12 | 27/11 | 26/10 | 25/9 | 24/8  | 23/7   | 22/6 | 21/5         | 20/4       | 19/3        | 18/2 | 17/1          | 16/0 | All Resets   |

|                             | OC1CON                          | 31:16<br>15:0 | –<br>ON |             | —<br>SIDL | _     |       |       |      |       |        | _    | —<br>OC32    | —<br>OCFLT | —<br>OCTSEL |      | —<br>OCM<2:0> | —    | 0000         |

| 4010                        | OC1R                            | 31:16<br>15:0 | ÖN      | OC1R<31:0>  |           |       |       |       |      |       |        |      |              | xxxx       |             |      |               |      |              |

| 4020                        | OC1RS                           | 31:16<br>15:0 |         | OC1RS<31:0> |           |       |       |       |      |       |        |      | xxxx<br>xxxx |            |             |      |               |      |              |

| 4200                        | OC2CON                          | 31:16<br>15:0 | —<br>ON |             | —<br>SIDL | —     |       | -     |      |       |        |      | —<br>OC32    | —<br>OCFLT | -<br>OCTSEL |      | —<br>OCM<2:0> | —    | 0000         |

| 4210                        | OC2R                            | 31:16<br>15:0 | -       | OC2R<31:0>  |           |       |       |       |      |       |        |      | xxxx<br>xxxx |            |             |      |               |      |              |

| 4220                        | OC2RS                           | 31:16<br>15:0 |         |             |           |       |       |       |      | OC2RS | <31:0> |      |              |            |             |      |               |      | xxxx<br>xxxx |

| 4400                        | OC3CON                          | 31:16<br>15:0 | ON      |             | —<br>SIDL | _     |       | _     | _    | _     | _      |      | —<br>OC32    | —<br>OCFLT | —<br>OCTSEL | _    | —<br>OCM<2:0> | _    | 0000         |

| 4410                        | OC3R                            | 31:16<br>15:0 |         |             | •         |       |       |       |      | OC3R- | <31:0> |      | •            | •          |             |      |               |      | xxxx<br>xxxx |

| 4420                        | OC3RS                           | 31:16<br>15:0 |         |             |           |       |       |       |      | OC3RS | <31:0> |      |              |            |             |      |               |      | xxxx<br>xxxx |

| 4600                        | OC4CON                          | 31:16<br>15:0 | –<br>ON |             | —<br>SIDL | _     |       | _     | -    | _     | -      | _    | —<br>OC32    | —<br>OCFLT | —<br>OCTSEL | —    | —<br>OCM<2:0> | _    | 0000         |

| 4610                        | OC4R                            | 31:16<br>15:0 |         |             |           |       |       |       |      | OC4R  | <31:0> |      |              |            |             |      |               |      | xxxx<br>xxxx |

| 4620                        | OC4RS                           | 31:16<br>15:0 |         |             |           |       |       |       |      | OC4RS | <31:0> |      |              |            |             |      |               |      | xxxx<br>xxxx |

| 4800                        | OC5CON                          | 31:16<br>15:0 | –<br>ON |             | —<br>SIDL |       |       |       |      | -     |        |      | —<br>OC32    | —<br>OCFLT | —<br>OCTSEL | —    | —<br>OCM<2:0> | _    | 0000         |

| 4810                        | OC5R                            | 31:16<br>15:0 |         |             |           |       |       |       |      | OC5R  | <31:0> |      |              |            |             |      |               |      | xxxx<br>xxxx |

| 4820                        | OC5RS                           | 31:16<br>15:0 |         |             |           |       |       |       |      | OC5RS | <31:0> |      |              |            |             |      |               |      | xxxx<br>xxxx |

Legend: x = unknown value on Reset; - = unimplemented, read as '0'. Reset values are shown in hexadecimal.

Note 1: All registers in this table have corresponding CLR, SET and INV registers at their virtual addresses, plus offsets of 0x4, 0x8 and 0xC, respectively. See Section 12.3 "CLR, SET, and INV Registers" for more information.

| Name      |       | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |  |  |  |

|-----------|-------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|--|--|--|

| SA_ENCIV1 | 31:24 |                   |                   |                   | ENCIV<31          | :24>              |                   |                  |                  |  |  |  |

|           | 23:16 | ENCIV<23:16>      |                   |                   |                   |                   |                   |                  |                  |  |  |  |

|           | 15:8  |                   | ENCIV<15:8>       |                   |                   |                   |                   |                  |                  |  |  |  |

|           | 7:0   |                   |                   |                   | ENCIV<7           | :0>               |                   |                  |                  |  |  |  |

| SA_ENCIV2 | 31:24 |                   |                   |                   | ENCIV<31          | :24>              |                   |                  |                  |  |  |  |

|           | 23:16 |                   | ENCIV<23:16>      |                   |                   |                   |                   |                  |                  |  |  |  |

|           | 15:8  |                   | ENCIV<15:8>       |                   |                   |                   |                   |                  |                  |  |  |  |

|           | 7:0   | ENCIV<7:0>        |                   |                   |                   |                   |                   |                  |                  |  |  |  |

| SA_ENCIV3 | 31:24 |                   |                   |                   | ENCIV<31          | :24>              |                   |                  |                  |  |  |  |

|           | 23:16 |                   |                   |                   | ENCIV<23          | :16>              |                   |                  |                  |  |  |  |

|           | 15:8  |                   |                   |                   | ENCIV<1           | 5:8>              |                   |                  |                  |  |  |  |

|           | 7:0   |                   |                   |                   | ENCIV<7           | :0>               |                   |                  |                  |  |  |  |

| SA_ENCIV4 | 31:24 |                   |                   |                   | ENCIV<31          | :24>              |                   |                  |                  |  |  |  |

|           | 23:16 |                   |                   |                   | ENCIV<23          | :16>              |                   |                  |                  |  |  |  |

|           | 15:8  |                   |                   |                   | ENCIV<1           | 5:8>              |                   |                  |                  |  |  |  |

|           | 7:0   |                   |                   |                   | ENCIV<7           | :0>               |                   |                  |                  |  |  |  |

## TABLE 26-4: CRYPTO ENGINE SECURITY ASSOCIATION STRUCTURE (CONTINUED)

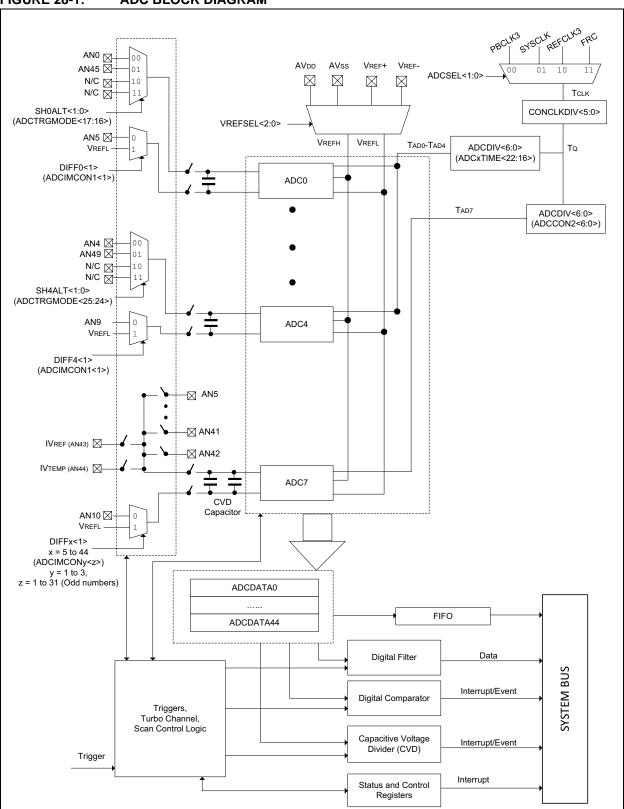

## FIGURE 28-1: ADC BLOCK DIAGRAM

| Bit<br>Range          | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |  |  |

|-----------------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|--|--|

| 04.04                 | U-0               | U-0               | U-0               | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |  |

| 31:24 — — — TRGSRC3<4 |                   |                   |                   |                   |                   |                   | )>               |                  |  |  |

| 00.40                 | U-0               | U-0               | U-0               | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |  |

| 23:16                 | _                 | _                 | —                 | TRGSRC2<4:0>      |                   |                   |                  |                  |  |  |

| 45.0                  | U-0               | U-0               | U-0               | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |  |

| 15:8                  | —                 | —                 | —                 |                   | Т                 | RGSRC1<4:0        | )>               |                  |  |  |

| 7.0                   | U-0               | U-0               | U-0               | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |  |

| 7:0                   | _                 | _                 | _                 |                   | Т                 | RGSRC0<4:0        | )>               |                  |  |  |

## REGISTER 28-17: ADCTRG1: ADC TRIGGER SOURCE 1 REGISTER

#### Legend:

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, read as '0'      |

|-------------------|------------------|-----------------------------------------|

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared x = Bit is unknown |

#### bit 31-29 Unimplemented: Read as '0'

- bit 28-24 TRGSRC3<4:0>: Trigger Source for Conversion of Analog Input AN3 Select bits

- 11111 = Reserved . . 01101 = Reserved 01100 = Comparator 2 (COUT) 01011 = Comparator 1 (COUT) 01010 = OCMP5 01001 = OCMP3 01000 = OCMP1 00111 = TMR5 match 00100 = TMR3 match 00101 = TMR1 match 00100 = INT0 External interrupt 00011 = STRIG 00010 = Global level software trigger (GLSWTRG) 00001 = Global software edge Trigger (GSWTRG) 00000 = No Trigger

For STRIG, in addition to setting the trigger, it also requires programming of the STRGSRC<4:0> bits (ADCCON1<20:16>) to select the trigger source, and requires the appropriate CSS bits to be set in the ADCCSSx registers.

- bit 23-21 Unimplemented: Read as '0'

- bit 20-16 **TRGSRC2<4:0>:** Trigger Source for Conversion of Analog Input AN2 Select bits See bits 28-24 for bit value definitions.

- bit 15-13 Unimplemented: Read as '0'

- bit 12-8 **TRGSRC1<4:0>:** Trigger Source for Conversion of Analog Input AN1 Select bits See bits 28-24 for bit value definitions.

- bit 7-5 Unimplemented: Read as '0'

- bit 4-0 **TRGSRC0<4:0>:** Trigger Source for Conversion of Analog Input AN0 Select bits See bits 28-24 for bit value definitions.

| Bit Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |  |  |  |  |

|-----------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|--|--|--|--|

| 24.24     | R-0               | R-0               | R-0               | R-0               | R-0               | R-0               | R-0              | R-0              |  |  |  |  |

| 31:24     | DATA<31:24>       |                   |                   |                   |                   |                   |                  |                  |  |  |  |  |

| 00.40     | R-0               | R-0               | R-0               | R-0               | R-0               | R-0               | R-0              | R-0              |  |  |  |  |

| 23:16     | DATA<23:16>       |                   |                   |                   |                   |                   |                  |                  |  |  |  |  |

| 45.0      | R-0               | R-0               | R-0               | R-0               | R-0               | R-0               | R-0              | R-0              |  |  |  |  |

| 15:8      |                   |                   | DATA<15:8>        |                   |                   |                   |                  |                  |  |  |  |  |

| 7.0       | R-0               | R-0               | R-0               | R-0               | R-0               | R-0               | R-0              | R-0              |  |  |  |  |

| 7:0       |                   | DATA<7:0>         |                   |                   |                   |                   |                  |                  |  |  |  |  |

## **REGISTER 28-25:** ADCDATAX: ADC OUTPUT DATA REGISTER ('x' = 0 THROUGH 44)

## Legend:

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, read as '0'      |

|-------------------|------------------|-----------------------------------------|

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared x = Bit is unknown |

bit 31-0 DATA<31:0>: ADC Converted Data Output bits.

- **Note 1:** The registers, ADCDATA19 through ADCDATA34, are not available on 64-pin devices.

- 2: The registers, ADCDATA35 through ADCDATA42, are not available on 64-pin and 100-pin devices.

- **3:** When an alternate input is used as the input source for a dedicated ADC module, the data output is still read from the Primary input Data Output Register.

- 4: Reading the ADCDATAx register value after changing the FRACT bit converts the data into the format specified by FRACT bit.

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |  |  |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|--|--|

| 04.04        | U-0               | U-0               | U-0               | U-0               | S/HC-0            | R/W-1             | R/W-0            | R/W-0            |  |  |

| 31:24        | —                 | —                 | _                 | —                 | ABAT              | REQOP<2:0>        |                  |                  |  |  |

| 00.40        | R-1               | R-0               | R-0               | R/W-0             | U-0               | U-0               | U-0              | U-0              |  |  |

| 23:16        | C                 | OPMOD<2:0>        |                   | CANCAP            | —                 | _                 | —                | —                |  |  |

| 45.0         | R/W-0             | U-0               | R/W-0             | U-0               | R-0               | U-0               | U-0              | U-0              |  |  |

| 15:8         | 0N <sup>(1)</sup> | —                 | SIDLE             | —                 | CANBUSY           | _                 | —                | —                |  |  |

| 7.0          | U-0               | U-0               | U-0               | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |  |

| 7:0          |                   | _                 |                   |                   | l                 | DNCNT<4:0>        |                  |                  |  |  |

#### **REGISTER 29-1: CICON: CAN MODULE CONTROL REGISTER**

| Legend:              | HC = Hardware Clear        | S = Settable bit      |                  |  |

|----------------------|----------------------------|-----------------------|------------------|--|

| R = Readable bit     | W = Writable bit           | P = Programmable bit  | r = Reserved bit |  |

| U = Unimplemented bi | t -n = Bit Value at POR: ( | 0'. '1'. x = Unknown) |                  |  |

#### bit 31-28 Unimplemented: Read as '0'

#### bit 27 **ABAT:** Abort All Pending Transmissions bit

- 1 = Signal all transmit buffers to abort transmission

- 0 = Module will clear this bit when all transmissions aborted

#### bit 26-24 REQOP<2:0>: Request Operation Mode bits

- 111 = Set Listen All Messages mode

- 110 = Reserved Do not use

- 101 = Reserved Do not use

- 100 = Set Configuration mode

- 011 = Set Listen Only mode

- 010 = Set Loopback mode

- 001 = Set Disable mode

- 000 = Set Normal Operation mode

#### bit 23-21 OPMOD<2:0>: Operation Mode Status bits

- 111 = Module is in Listen All Messages mode

- 110 = Reserved

- 101 = Reserved

- 100 = Module is in Configuration mode

- 011 = Module is in Listen Only mode

- 010 = Module is in Loopback mode

- 001 = Module is in Disable mode

- 000 = Module is in Normal Operation mode

#### bit 20 CANCAP: CAN Message Receive Time Stamp Timer Capture Enable bit

- 1 = CANTMR value is stored on valid message reception and is stored with the message

- 0 = Disable CAN message receive time stamp timer capture and stop CANTMR to conserve power

- bit 19-16 Unimplemented: Read as '0'

- bit 15 **ON:** CAN On bit<sup>(1)</sup>

- 1 = CAN module is enabled

- 0 = CAN module is disabled

- bit 14 Unimplemented: Read as '0'

- **Note 1:** If the user application clears this bit, it may take a number of cycles before the CAN module completes the current transaction and responds to this request. The user application should poll the CANBUSY bit to verify that the request has been honored.

| bit 15 FLTEN29: Filter 29 Enable bit<br>1 = Filter is enabled<br>0 = Filter is disabled<br>bit 14-13 MSEL29<1:0>: Filter 29 Mask Select bits<br>11 = Acceptance Mask 3 selected<br>10 = Acceptance Mask 2 selected<br>01 = Acceptance Mask 0 selected<br>00 = Acceptance Mask 0 selected<br>bit 12-8 FSEL29<4:0>: FIFO Selection bits<br>11111 = Message matching filter is stored in FIFO buffer 31<br>11110 = Message matching filter is stored in FIFO buffer 1<br>00001 = Message matching filter is stored in FIFO buffer 1<br>00000 = Message matching filter is stored in FIFO buffer 1<br>00000 = Message matching filter is stored in FIFO buffer 0<br>bit 7 FLTEN28: Filter 28 Enable bit<br>1 = Filter is enabled<br>0 = Filter is disabled<br>bit 6-5 MSEL28<1:0>: Filter 28 Mask Select bits<br>11 = Acceptance Mask 3 selected<br>10 = Acceptance Mask 3 selected<br>11 = Acceptance Mask 3 selected<br>12 = Acceptance Mask 3 selected<br>13 = Acceptance Mask 3 selected<br>14-0 FSEL28<4:0>: FIFO Selection bits<br>11111 = Message matching filter is stored in FIFO buffer 31<br>11110 = Message matching filter is stored in FIFO buffer 31<br>11110 = Message matching filter is stored in FIFO buffer 31<br>11110 = Message matching filter is stored in FIFO buffer 1<br>00001 = Message matching filter is stored in FIFO buffer 1<br>00001 = Message matching filter is stored in FIFO buffer 1<br>00001 = Message matching filter is stored in FIFO buffer 1<br>00001 = Message matching filter is stored in FIFO buffer 1<br>00001 = Message matching filter is stored in FIFO buffer 0                                                                                                                                                                                                                                                                                                                                                                                                                                         | REGISTE   | ER 29-17: CIFLTCON7: CAN FILTER CONTROL REGISTER 7 (CONTINUED)                                         |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------|--------------------------------------------------------------------------------------------------------|

| 0 = Filter is disabled bit 14-13 MSEL29<1:D>: Filter 29 Mask Select bits 11 = Acceptance Mask 3 selected 10 = Acceptance Mask 1 selected 00 = Acceptance Mask 1 selected 00 = Acceptance Mask 0 selected bit 12-8 FSEL29<4:D>: FIFO Selection bits 11111 = Message matching filter is stored in FIFO buffer 31 11110 = Message matching filter is stored in FIFO buffer 1 00001 = Message matching filter is stored in FIFO buffer 0 bit 7 FLTEN28: Filter 28 Enable bit 1 = Filter is enabled 0 = Filter is disabled bit 6-5 MSEL28<1:D>: FIFC Selection bits 11 = Acceptance Mask 3 selected bit 4-0 FSEL28<1:D>: Filter 28 Mask Select bits 11 = Acceptance Mask 1 selected 00 = Acceptance Mask 3 selected 10 = Acceptance Mask 4 selected 10 = Acceptance Mask 4 selected 10 = Acceptance Mask 4 selected 10 = Acceptance Mask 1 selected 10 = Acceptance Mask 1 selected 10 = Acceptance Mask 1 selected 10 = Acceptance Mask 2 selected 11 = Acceptance Mask 1 selected 10 = Acceptance Mask 1 selected 11 = Acceptance Mask 1 selected 10 = Acceptance Mask 1 selected 11 = Acceptance Mask 1 selected 11 = Acceptance Mask 1 selected 11 = Acceptance Mask 1 selected 10 = Acceptance Mask 1 selected 11 = Acceptance Mask 1 selected 12 = Acceptance Mask 1 selected 13 = Acceptance Mask                                                                                                                                                                                                                                                                                                                                                                                                 | bit 15    | FLTEN29: Filter 29 Enable bit                                                                          |

| <pre>bit 14-13 MSEL29-1:0-: Filter 29 Mask Select bits 11 = Acceptance Mask 3 selected 10 = Acceptance Mask 2 selected 01 = Acceptance Mask 0 selected bit 12-3 FSEL29-4:0-: FIFO Selection bits 11111 = Message matching filter is stored in FIFO buffer 31 11110 = Message matching filter is stored in FIFO buffer 30</pre>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |           | 1 = Filter is enabled                                                                                  |

| <pre>11 = Acceptance Mask 3 selected<br/>10 = Acceptance Mask 2 selected<br/>01 = Acceptance Mask 0 selected<br/>bit 12-8 FSEL29-4:0&gt;: FIFO Selection bits<br/>11111 = Message matching filter is stored in FIFO buffer 31<br/>11110 = Message matching filter is stored in FIFO buffer 30<br/>•<br/>•<br/>•<br/>•<br/>•<br/>•<br/>•<br/>•<br/>•<br/>•<br/>•<br/>•<br/>•<br/>•<br/>•<br/>•<br/>•<br/>•<br/>•</pre>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |           | 0 = Filter is disabled                                                                                 |

| <pre>10 = Acceptance Mask 2 selected<br/>01 = Acceptance Mask 0 selected<br/>00 = Acceptance Mask 0 selected<br/>bit 12-8 FSEL29&lt;4:0&gt;: FIFO Selection bits<br/>11111 = Message matching filter is stored in FIFO buffer 31<br/>11110 = Message matching filter is stored in FIFO buffer 30<br/>•<br/>•<br/>•<br/>•<br/>•<br/>•<br/>•<br/>•<br/>•<br/>•<br/>•<br/>•<br/>•<br/>•<br/>•<br/>•<br/>•<br/>•<br/>•</pre>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | bit 14-13 | MSEL29<1:0>: Filter 29 Mask Select bits                                                                |

| <pre>01 = Acceptance Mask 1 selected<br/>00 = Acceptance Mask 0 selected<br/>bit 12-8 FSEL29&lt;4:0&gt;: FIFO Selection bits<br/>11111 = Message matching filter is stored in FIFO buffer 31<br/>11110 = Message matching filter is stored in FIFO buffer 30<br/>•<br/>•<br/>•<br/>•<br/>•<br/>•<br/>•<br/>•<br/>•<br/>•<br/>•<br/>•<br/>•<br/>•<br/>•<br/>•<br/>•<br/>•<br/>•</pre>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |           |                                                                                                        |

| 00 = Acceptance Mask 0 selected<br>bit 12-8 FSEL29<4:0>: FIFO Selection bits<br>11111 = Message matching filter is stored in FIFO buffer 31<br>11110 = Message matching filter is stored in FIFO buffer 30<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•<br>•                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |           |                                                                                                        |

| <pre>bit 12-8 FSEL29&lt;4:0&gt;: FIFO Selection bits 11111 = Message matching filter is stored in FIFO buffer 31 11110 = Message matching filter is stored in FIFO buffer 30</pre>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |           |                                                                                                        |

| <pre>11111 = Message matching filter is stored in FIFO buffer 31 11110 = Message matching filter is stored in FIFO buffer 30</pre>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | hit 12 8  |                                                                                                        |

| <pre>11110 = Message matching filter is stored in FIFO buffer 30</pre>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | DIL 12-0  |                                                                                                        |

| <ul> <li>00001 = Message matching filter is stored in FIFO buffer 1</li> <li>00000 = Message matching filter is stored in FIFO buffer 0</li> <li>bit 7 FLTEN28: Filter 28 Enable bit</li> <li>1 = Filter is enabled</li> <li>0 = Filter is disabled</li> <li>bit 6-5 MSEL28</li> <li>bit 6-5 MSEL28</li> <li>10 = Acceptance Mask 3 selected</li> <li>10 = Acceptance Mask 2 selected</li> <li>00 = Acceptance Mask 1 selected</li> <li>00 = Acceptance Mask 0 selected</li> <li>bit 4-0 FSEL28</li> <li>4-0 FSEL28</li> &lt;</ul>                              |           |                                                                                                        |

| <pre>00000 = Message matching filter is stored in FIFO buffer 0 bit 7 FLTEN28: Filter 28 Enable bit 1 = Filter is enabled 0 = Filter is disabled bit 6-5 MSEL28&lt;1:0&gt;: Filter 28 Mask Select bits 11 = Acceptance Mask 3 selected 10 = Acceptance Mask 1 selected 00 = Acceptance Mask 1 selected 00 = Acceptance Mask 0 selected bit 4-0 FSEL28&lt;4:0&gt;: FIFO Selection bits 11111 = Message matching filter is stored in FIFO buffer 31 11110 = Message matching filter is stored in FIFO buffer 30 • • • • • • • • • • • • • • • • • • •</pre>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |           |                                                                                                        |

| <pre>00000 = Message matching filter is stored in FIFO buffer 0 bit 7 FLTEN28: Filter 28 Enable bit 1 = Filter is enabled 0 = Filter is disabled bit 6-5 MSEL28&lt;1:0&gt;: Filter 28 Mask Select bits 11 = Acceptance Mask 3 selected 10 = Acceptance Mask 1 selected 00 = Acceptance Mask 1 selected 00 = Acceptance Mask 0 selected bit 4-0 FSEL28&lt;4:0&gt;: FIFO Selection bits 11111 = Message matching filter is stored in FIFO buffer 31 11110 = Message matching filter is stored in FIFO buffer 30 • • • • • • • • • • • • • • • • • • •</pre>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |           | •                                                                                                      |

| <pre>00000 = Message matching filter is stored in FIFO buffer 0 bit 7 FLTEN28: Filter 28 Enable bit 1 = Filter is enabled 0 = Filter is disabled bit 6-5 MSEL28&lt;1:0&gt;: Filter 28 Mask Select bits 11 = Acceptance Mask 3 selected 10 = Acceptance Mask 1 selected 00 = Acceptance Mask 1 selected 00 = Acceptance Mask 0 selected bit 4-0 FSEL28&lt;4:0&gt;: FIFO Selection bits 11111 = Message matching filter is stored in FIFO buffer 31 11110 = Message matching filter is stored in FIFO buffer 30 • • • • • • • • • • • • • • • • • • •</pre>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |           | •                                                                                                      |

| <pre>00000 = Message matching filter is stored in FIFO buffer 0 bit 7 FLTEN28: Filter 28 Enable bit 1 = Filter is enabled 0 = Filter is disabled bit 6-5 MSEL28&lt;1:0&gt;: Filter 28 Mask Select bits 11 = Acceptance Mask 3 selected 10 = Acceptance Mask 1 selected 00 = Acceptance Mask 1 selected 00 = Acceptance Mask 0 selected bit 4-0 FSEL28&lt;4:0&gt;: FIFO Selection bits 11111 = Message matching filter is stored in FIFO buffer 31 11110 = Message matching filter is stored in FIFO buffer 30 • • • • • • • • • • • • • • • • • • •</pre>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |           | 00001 = Message matching filter is stored in FIFO buffer 1                                             |

| <pre>1 = Filter is enabled<br/>0 = Filter is disabled<br/>bit 6-5 MSEL28&lt;1:0&gt;: Filter 28 Mask Select bits<br/>11 = Acceptance Mask 3 selected<br/>10 = Acceptance Mask 2 selected<br/>01 = Acceptance Mask 1 selected<br/>00 = Acceptance Mask 0 selected<br/>bit 4-0 FSEL28&lt;4:0&gt;: FIFO Selection bits<br/>11111 = Message matching filter is stored in FIFO buffer 31<br/>11110 = Message matching filter is stored in FIFO buffer 30<br/>•<br/>•<br/>•<br/>•<br/>•<br/>•<br/>•<br/>•<br/>•<br/>•<br/>•<br/>•<br/>•<br/>•<br/>•<br/>•<br/>•<br/>•<br/>•</pre>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |           |                                                                                                        |