Welcome to **E-XFL.COM**

What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded - Microcontrollers</u>"

| Details                    |                                                                                  |

|----------------------------|----------------------------------------------------------------------------------|

| Product Status             | Obsolete                                                                         |

| Core Processor             | MIPS32® M-Class                                                                  |

| Core Size                  | 32-Bit Single-Core                                                               |

| Speed                      | 180MHz                                                                           |

| Connectivity               | EBI/EMI, Ethernet, I <sup>2</sup> C, PMP, SPI, SQI, UART/USART, USB OTG          |

| Peripherals                | Brown-out Detect/Reset, DMA, I2S, POR, PWM, WDT                                  |

| Number of I/O              | 97                                                                               |

| Program Memory Size        | 512KB (512K x 8)                                                                 |

| Program Memory Type        | FLASH                                                                            |

| EEPROM Size                | -                                                                                |

| RAM Size                   | 128K x 8                                                                         |

| Voltage - Supply (Vcc/Vdd) | 2.1V ~ 3.6V                                                                      |

| Data Converters            | A/D 48x12b                                                                       |

| Oscillator Type            | Internal                                                                         |

| Operating Temperature      | -40°C ~ 125°C (TA)                                                               |

| Mounting Type              | Surface Mount                                                                    |

| Package / Case             | 124-VFTLA Dual Rows, Exposed Pad                                                 |

| Supplier Device Package    | 124-VTLA (9x9)                                                                   |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic32mz0512efe124-e-tl |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

### 1.0 DEVICE OVERVIEW

Note:

This data sheet summarizes the features of the PIC32MZ EF family of devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to the "PIC32 Family Reference Manual", which is available from the Microchip web site (www.microchip.com/PIC32).

This data sheet contains device-specific information for PIC32MZ EF devices.

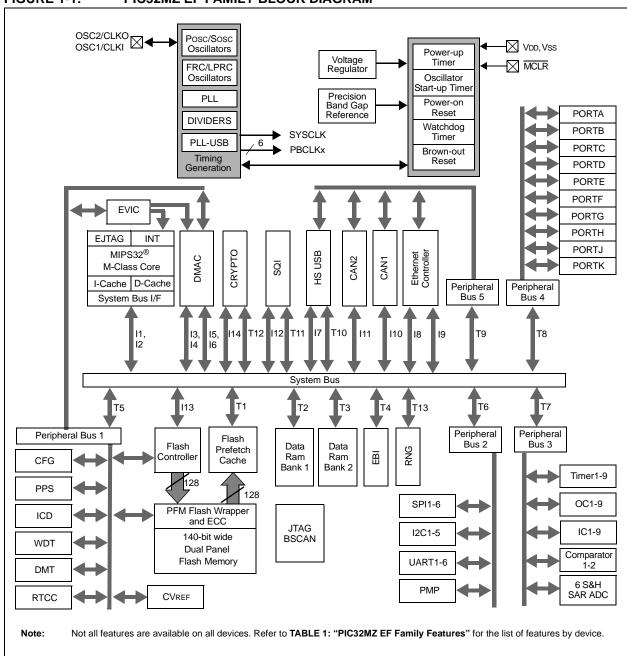

Figure 1-1 illustrates a general block diagram of the core and peripheral modules in the PIC32MZ EF family of devices.

Table 1-21 through Table 1-22 list the pinout I/O descriptions for the pins shown in the device pin tables (see Table 2 through Table 5).

FIGURE 1-1: PIC32MZ EF FAMILY BLOCK DIAGRAM

TABLE 1-6: PORTA THROUGH PORTK PINOUT I/O DESCRIPTIONS

|          |                        | Pin Nu          | mber            |                          |             |                |                                   |

|----------|------------------------|-----------------|-----------------|--------------------------|-------------|----------------|-----------------------------------|

| Pin Name | 64-pin<br>QFN/<br>TQFP | 100-pin<br>TQFP | 124-pin<br>VTLA | 144-pin<br>TQFP/<br>LQFP | Pin<br>Type | Buffer<br>Type | Description                       |

|          |                        |                 |                 |                          | PO          | RTA            |                                   |

| RA0      | _                      | 17              | A11             | 22                       | I/O         | ST             | PORTA is a bidirectional I/O port |

| RA1      | _                      | 38              | B21             | 56                       | I/O         | ST             |                                   |

| RA2      | _                      | 59              | A41             | 85                       | I/O         | ST             |                                   |

| RA3      | _                      | 60              | B34             | 86                       | I/O         | ST             |                                   |

| RA4      | _                      | 61              | A42             | 87                       | I/O         | ST             |                                   |

| RA5      | _                      | 2               | B1              | 2                        | I/O         | ST             |                                   |

| RA6      | _                      | 89              | A61             | 129                      | I/O         | ST             |                                   |

| RA7      | _                      | 90              | B51             | 130                      | I/O         | ST             |                                   |

| RA9      | _                      | 28              | B15             | 39                       | I/O         | ST             |                                   |

| RA10     | _                      | 29              | A20             | 40                       | I/O         | ST             |                                   |

| RA14     | _                      | 66              | B37             | 95                       | I/O         | ST             |                                   |

| RA15     | _                      | 67              | A45             | 96                       | I/O         | ST             |                                   |

|          | •                      | •               | •               |                          | PO          | RTB            |                                   |

| RB0      | 16                     | 25              | A18             | 36                       | I/O         | ST             | PORTB is a bidirectional I/O port |

| RB1      | 15                     | 24              | A17             | 35                       | I/O         | ST             |                                   |

| RB2      | 14                     | 23              | A16             | 34                       | I/O         | ST             |                                   |

| RB3      | 13                     | 22              | A14             | 31                       | I/O         | ST             |                                   |

| RB4      | 12                     | 21              | A13             | 26                       | I/O         | ST             |                                   |

| RB5      | 11                     | 20              | B11             | 25                       | I/O         | ST             |                                   |

| RB6      | 17                     | 26              | B14             | 37                       | I/O         | ST             |                                   |

| RB7      | 18                     | 27              | A19             | 38                       | I/O         | ST             |                                   |

| RB8      | 21                     | 32              | B18             | 47                       | I/O         | ST             |                                   |

| RB9      | 22                     | 33              | A23             | 48                       | I/O         | ST             |                                   |

| RB10     | 23                     | 34              | B19             | 49                       | I/O         | ST             |                                   |

| RB11     | 24                     | 35              | A24             | 50                       | I/O         | ST             |                                   |

| RB12     | 27                     | 41              | A27             | 59                       | I/O         | ST             |                                   |

| RB13     | 28                     | 42              | B23             | 60                       | I/O         | ST             | ]                                 |

| RB14     | 29                     | 43              | A28             | 61                       | I/O         | ST             |                                   |

| RB15     | 30                     | 44              | B24             | 62                       | I/O         | ST             |                                   |

|          |                        |                 |                 |                          | PO          | RTC            |                                   |

| RC1      | _                      | 6               | В3              | 6                        | I/O         | ST             | PORTC is a bidirectional I/O port |

| RC2      | _                      | 7               | A6              | 11                       | I/O         | ST             |                                   |

| RC3      | _                      | 8               | B5              | 12                       | I/O         | ST             | ]                                 |

| RC4      | _                      | 9               | A7              | 13                       | I/O         | ST             | ]                                 |

| RC12     | 31                     | 49              | B28             | 71                       | I/O         | ST             | ]                                 |

| RC13     | 47                     | 72              | B41             | 105                      | I/O         | ST             | ]                                 |

| RC14     | 48                     | 73              | A49             | 106                      | I/O         | ST             | 1                                 |

| RC15     | 32                     | 50              | A33             | 72                       | I/O         | ST             | 1                                 |

|          | CMOC C                 | MOC some        |                 |                          |             | A I            | Analog input D. Dower             |

**Legend:** CMOS = CMOS-compatible input or output ST = Schmitt Trigger input with CMOS levels

ST = Schmitt Trigger input with CMOS levels TTL = Transistor-transistor Logic input buffer Analog = Analog input

O = Output

PPS = Peripheral Pin Select

P = Power I = Input

**I2C1 THROUGH I2C5 PINOUT I/O DESCRIPTIONS TABLE 1-10:**

|          |                        | Pin Nu          | mber            |                          |             |                |                                            |

|----------|------------------------|-----------------|-----------------|--------------------------|-------------|----------------|--------------------------------------------|

| Pin Name | 64-pin<br>QFN/<br>TQFP | 100-pin<br>TQFP | 124-pin<br>VTLA | 144-pin<br>TQFP/<br>LQFP | Pin<br>Type | Buffer<br>Type | Description                                |

|          |                        |                 |                 | Inte                     | er-Integr   | ated Circui    | t 1                                        |

| SCL1     | 44                     | 66              | B37             | 95                       | I/O         | ST             | I2C1 Synchronous Serial Clock Input/Output |

| SDA1     | 43                     | 67              | A45             | 96                       | I/O         | ST             | I2C1 Synchronous Serial Data Input/Output  |

|          |                        |                 |                 | Inte                     | er-Integra  | ated Circui    | t 2                                        |

| SCL2     | _                      | 59              | A41             | 85                       | I/O         | ST             | I2C2 Synchronous Serial Clock Input/Output |

| SDA2     | _                      | 60              | B34             | 86                       | I/O         | ST             | I2C2 Synchronous Serial Data Input/Output  |

|          |                        |                 |                 | Inte                     | er-Integra  | ated Circui    | t 3                                        |

| SCL3     | 51                     | 58              | A39             | 80                       | I/O         | ST             | I2C3 Synchronous Serial Clock Input/Output |

| SDA3     | 50                     | 57              | B31             | 79                       | I/O         | ST             | I2C3 Synchronous Serial Data Input/Output  |

|          |                        |                 |                 | Inte                     | er-Integra  | ated Circui    | t 4                                        |

| SCL4     | 6                      | 12              | В7              | 16                       | I/O         | ST             | I2C4 Synchronous Serial Clock Input/Output |

| SDA4     | 5                      | 11              | A8              | 15                       | I/O         | ST             | I2C4 Synchronous Serial Data Input/Output  |

|          | •                      | •               | •               | Inte                     | er-Integra  | ated Circui    | t 5                                        |

| SCL5     | 42                     | 65              | A44             | 91                       | I/O         | ST             | I2C5 Synchronous Serial Clock Input/Output |

| SDA5     | 41                     | 64              | B36             | 90                       | I/O         | ST             | I2C5 Synchronous Serial Data Input/Output  |

Legend: CMOS = CMOS-compatible input or output Analog = Analog input

P = Power I = Input

ST = Schmitt Trigger input with CMOS levels TTL = Transistor-transistor Logic input buffer

O = Output

PPS = Peripheral Pin Select

**TABLE 1-11: COMPARATOR 1, COMPARATOR 2 AND CVREF PINOUT I/O DESCRIPTIONS**

|          |                        | Pin Nu          | mber            |                          |             |                |                                           |

|----------|------------------------|-----------------|-----------------|--------------------------|-------------|----------------|-------------------------------------------|

| Pin Name | 64-pin<br>QFN/<br>TQFP | 100-pin<br>TQFP | 124-pin<br>VTLA | 144-pin<br>TQFP/<br>LQFP | Pin<br>Type | Buffer<br>Type | Description                               |

|          |                        |                 |                 | Comp                     | arator Vo   | Itage Refe     | erence                                    |

| CVREF+   | 16                     | 29              | A20             | 40                       | I           | Analog         | Comparator Voltage Reference (High) Input |

| CVREF-   | 15                     | 28              | B15             | 39                       | I           | Analog         | Comparator Voltage Reference (Low) Input  |

| CVREFOUT | 23                     | 34              | B19             | 49                       | 0           | Analog         | Comparator Voltage Reference Output       |

|          |                        |                 |                 |                          | Comp        | arator 1       |                                           |

| C1INA    | 11                     | 20              | B11             | 25                       | I           | Analog         | Comparator 1 Positive Input               |

| C1INB    | 12                     | 21              | A13             | 26                       | I           | Analog         | Comparator 1 Selectable Negative Input    |

| C1INC    | 5                      | 11              | A8              | 15                       | I           | Analog         |                                           |

| C1IND    | 4                      | 10              | B6              | 14                       | I           | Analog         |                                           |

| C1OUT    | PPS                    | PPS             | PPS             | PPS                      | 0           | _              | Comparator 1 Output                       |

|          |                        | •               | •               | •                        | Comp        | arator 2       |                                           |

| C2INA    | 13                     | 22              | A14             | 31                       | I           | Analog         | Comparator 2 Positive Input               |

| C2INB    | 14                     | 23              | A16             | 34                       | I           | Analog         | Comparator 2 Selectable Negative Input    |

| C2INC    | 10                     | 16              | В9              | 21                       | I           | Analog         | 1                                         |

| C2IND    | 6                      | 12              | В7              | 16                       | I           | Analog         | 1                                         |

| C2OUT    | PPS                    | PPS             | PPS             | PPS                      | 0           | _              | Comparator 2 Output                       |

CMOS = CMOS-compatible input or output ST = Schmitt Trigger input with CMOS levels Analog = Analog input

P = Power I = Input

TTL = Transistor-transistor Logic input buffer

O = Output

PPS = Peripheral Pin Select

## 3.7 M-Class Core Configuration

Register 3-1 through Register 3-4 show the default configuration of the M-Class core, which is included on the PIC32MZ EF family of devices.

REGISTER 3-1: CONFIG: CONFIGURATION REGISTER; CP0 REGISTER 16, SELECT 0

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|

| 31:24        | r-1               | U-0               | U-0               | -0 U-0 U-0        |                   | U-0 U-0           |                  | R-0              |

| 31.24        | _                 | _                 | _                 | _                 | _                 |                   |                  |                  |

| 22.46        | R-0               | R-0               | R-1               | R-0               | U-0               | R-1               | R-0              | R-0              |

| 23:16        | DSP               | UDI               | SB                | MDU               | _                 | MM<               | 1:0>             | BM               |

| 15.0         | R-0               | R-0               | R-0               | R-0               | R-0               | R-1               | R-0              | R-0              |

| 15:8         | BE                | AT<               | 1:0>              |                   | AR<2:0>           |                   | MT<              | 2:1>             |

| 7.0          | R-1               | U-0               | U-0               | U-0               | U-0               | R/W-0             | R/W-1            | R/W-0            |

| 7:0          | MT<0>             | _                 | _                 | _                 | _                 |                   | K0<2:0>          |                  |

| Legend:           | r = Reserved bit |                      |                    |

|-------------------|------------------|----------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented b  | it, read as '0'    |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared | x = Bit is unknown |

bit 31 Reserved: This bit is hardwired to '1' to indicate the presence of the Config1 register.

bit 30-25 Unimplemented: Read as '0'

bit 24 ISP: Instruction Scratch Pad RAM bit

0 = Instruction Scratch Pad RAM is not implemented

bit 23 DSP: Data Scratch Pad RAM bit

0 = Data Scratch Pad RAM is not implemented

bit 22 **UDI:** User-defined bit

0 = CorExtend User-Defined Instructions are not implemented

bit 21 SB: SimpleBE bit

1 = Only Simple Byte Enables are allowed on the internal bus interface

bit 20 MDU: Multiply/Divide Unit bit

0 = Fast, high-performance MDU

bit 19 Unimplemented: Read as '0'

bit 18-17 MM<1:0>: Merge Mode bits

10 = Merging is allowed

bit 16 BM: Burst Mode bit

0 = Burst order is sequential

bit 15 BE: Endian Mode bit

0 = Little-endian

bit 14-13 AT<1:0>: Architecture Type bits

00 = MIPS32

bit 12-10 AR<2:0>: Architecture Revision Level bits

001 = MIPS32 Release 2

bit 9-7 MT<2:0>: MMU Type bits

001 = M-Class MPU Microprocessor core uses a TLB-based MMU

bit 6-3 Unimplemented: Read as '0'

bit 2-0 K0<2:0>: Kseg0 Coherency Algorithm bits

011 = Cacheable, non-coherent, write-back, write allocate

010 = Uncached

001 = Cacheable, non-coherent, write-through, write allocate

000 = Cacheable, non-coherent, write-through, no write allocate

All other values are not used and mapped to other values. 100, 101, and 110 are mapped to 010. 111 is mapped to 010.

## REGISTER 3-10: FCSR: FLOATING POINT CONTROL AND STATUS REGISTER; CP1 REGISTER 31

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |  |  |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|--|--|

| 24.24        | R/W-x             | R/W-x             | R/W-x             | R/W-x             | R/W-x             | R/W-x             | R/W-x            | R/W-x            |  |  |

| 31:24        | FCC<7:1>          |                   |                   |                   |                   |                   |                  |                  |  |  |

| 00:40        | R/W-x             | R/W-x             | R/W-x             | R-0               | R-1               | R-1               | R/W-x            | R/W-x            |  |  |

| 23:16        | FCC<0>            | FO                | FN                | MAC2008           | ABS2008           | NAN2008           | CAUS             | E<5:4>           |  |  |

|              | R/W-x R/W-x       |                   | R/W-x             | R/W-x             | R/W-x             | R/W-x             | R/W-x            | R/W-x            |  |  |

| 15:8         |                   | CAUSE             | -210-             |                   |                   | S<4:1>            |                  |                  |  |  |

|              |                   | CAUSE             | <3.0>             |                   | V                 | Z                 | 0                | U                |  |  |

|              | R/W-x R/W-x       |                   | R/W-x R/W-x       |                   | R/W-x R/W-x       |                   | R/W-x            | R/W-x            |  |  |

| 7:0          | ENABLES<0>        |                   | •                 | FLAGS<4:0>        | •                 |                   | PM-              | -1:0>            |  |  |

|              | I                 | V                 | Z                 | 0                 | U                 | I                 |                  | l<1:0>           |  |  |

### Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

-n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown

### bit 31-25 FCC<7:1>: Floating Point Condition Code bits

These bits record the results of floating point compares and are tested for floating point conditional branches and conditional moves.

- bit 24 FS: Flush to Zero control bit

- 1 = Denormal input operands are flushed to zero. Tiny results are flushed to either zero or the applied format's smallest normalized number (MinNorm) depending on the rounding mode settings.

- 0 = Denormal input operands result in an Unimplemented Operation exception.

- bit 23 FCC<0>: Floating Point Condition Code bits

These bits record the results of floating point compares and are tested for floating point conditional branches and conditional moves.

- bit 22 FO: Flush Override Control bit

- 1 = The intermediate result is kept in an internal format, which can be perceived as having the usual mantissa precision but with unlimited exponent precision and without forcing to a specific value or taking an exception.

- 0 = Handling of Tiny Result values depends on setting of the FS bit.

- bit 21 FN: Flush to Nearest Control bit

- 1 = Final result is rounded to either zero or 2E\_min (MinNorm), whichever is closest when in Round to Nearest (RN) rounding mode. For other rounding modes, a final result is given as if FS was set to 1.

- 0 = Handling of Tiny Result values depends on setting of the FS bit.

- bit 20 MAC2008: Fused Multiply Add mode control bit

- 0 = Unfused multiply-add. Intermediary multiplication results are rounded to the destination format.

- bit 19 ABS2008: Absolute value format control bit

- 1 = ABS.fmt and NEG.fmt instructions compliant with IEEE Standard 754-2008. The ABS and NEG functions accept QNAN inputs without trapping.

- bit 18 NAN2008: NaN Encoding control bit

- 1 = Quiet and signaling NaN encodings recommended by the IEEE Standard 754-2008. A quiet NaN is encoded with the first bit of the fraction being 1 and a signaling NaN is encoded with the first bit of the fraction being 0.

- bit 17-12 CAUSE<5:0>: FPU Exception Cause bits

These bits indicated the exception conditions that arise during execution of an FPU arithmetic instruction.

### REGISTER 8-8: CLKSTAT: OSCILLATOR CLOCK STATUS REGISTER

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|

| 04:04        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 31:24        | _                 | _                 | _                 | _                 | _                 | _                 | _                | _                |

| 00.40        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 23:16        | _                 | _                 | _                 | _                 | _                 | _                 | _                | _                |

| 45.0         | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 15:8         | _                 | _                 | _                 | _                 | _                 | _                 | _                | _                |

| 7.0          | U-0               | U-0               | R-0               | R-0               | U-0               | R-0               | R-0              | R-0              |

| 7:0          | _                 | _                 | LPRCRDY           | SOSCRDY           | _                 | POSCRDY           | DIVSPLLRDY       | FRCRDY           |

Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

-n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown

bit 31-6 Unimplemented: Read as '0'

bit 5 LPRCRDY: Low-Power RC (LPRC) Oscillator Ready Status bit

1 = LPRC is stable and ready

0 = LPRC is disabled or not operating

bit 4 SOSCRDY: Secondary Oscillator (Sosc) Ready Status bit

1 = Sosc is stable and ready

0 = Sosc is disabled or not operating

bit 3 Unimplemented: Read as '0'

bit 2 POSCRDY: Primary Oscillator (Posc) Ready Status bit

1 = Posc is stable and ready

0 = Posc is disabled or not operating

bit 1 DIVSPLLRDY: Divided System PLL Ready Status bit

1 = Divided System PLL is ready0 = Divided System PLL is not ready

bit 0 FRCRDY: Fast RC (FRC) Oscillator Ready Status bit

1 = FRC is stable and ready

0 = FRC is disabled for not operating

| C32MZ Embed | Ctivity with | 1 1 loating | T OILL OILL | (Er / r anni) |

|-------------|--------------|-------------|-------------|---------------|

| OTES:       |              |             |             |               |

|             |              |             |             |               |

|             |              |             |             |               |

|             |              |             |             |               |

|             |              |             |             |               |

|             |              |             |             |               |

|             |              |             |             |               |

|             |              |             |             |               |

|             |              |             |             |               |

|             |              |             |             |               |

|             |              |             |             |               |

|             |              |             |             |               |

|             |              |             |             |               |

|             |              |             |             |               |

|             |              |             |             |               |

|             |              |             |             |               |

|             |              |             |             |               |

|             |              |             |             |               |

|             |              |             |             |               |

## REGISTER 14-1: TxCON: TYPE B TIMER CONTROL REGISTER ('x' = 2-9) (CONTINUED)

bit 2 Unimplemented: Read as '0'

bit 1 TCS: Timer Clock Source Select bit<sup>(1)</sup>

1 = External clock from TxCK pin

0 = Internal peripheral clock

bit 0 **Unimplemented:** Read as '0'

- **Note 1:** While operating in 32-bit mode, this bit has no effect for odd numbered timers (Timer1, Timer3, Timer5, Timer7, and Timer9). All timer functions are set through the even numbered timers.

- 2: While operating in 32-bit mode, this bit must be cleared on odd numbered timers to enable the 32-bit timer in Idle mode.

- **3:** This bit is available only on even numbered timers (Timer2, Timer4, Timer6, and Timer8).

### REGISTER 19-1: SPIXCON: SPI CONTROL REGISTER (CONTINUED)

- bit 5 MSTEN: Master Mode Enable bit

- 1 = Master mode

- 0 = Slave mode

- bit 4 **DISSDI:** Disable SDI bit<sup>(4)</sup>

- 1 = SDI pin is not used by the SPI module (pin is controlled by PORT function)

- 0 = SDI pin is controlled by the SPI module

- bit 3-2 **STXISEL<1:0>:** SPI Transmit Buffer Empty Interrupt Mode bits

- 11 = Interrupt is generated when the buffer is not full (has one or more empty elements)

- 10 = Interrupt is generated when the buffer is empty by one-half or more

- 01 = Interrupt is generated when the buffer is completely empty

- 00 = Interrupt is generated when the last transfer is shifted out of SPISR and transmit operations are complete

- bit 1-0 SRXISEL<1:0>: SPI Receive Buffer Full Interrupt Mode bits

- 11 = Interrupt is generated when the buffer is full

- 10 = Interrupt is generated when the buffer is full by one-half or more

- 01 = Interrupt is generated when the buffer is not empty

- 00 = Interrupt is generated when the last word in the receive buffer is read (i.e., buffer is empty)

- Note 1: This bit can only be written when the ON bit = 0. Refer to Section 37.0 "Electrical Characteristics" for maximum clock frequency requirements.

- 2: This bit is not used in the Framed SPI mode. The user should program this bit to '0' for the Framed SPI mode (FRMEN = 1).

- 3: When AUDEN = 1, the SPI/I<sup>2</sup>S module functions as if the CKP bit is equal to '1', regardless of the actual value of the CKP bit.

- 4: This bit present for legacy compatibility and is superseded by PPS functionality on these devices (see Section 12.4 "Peripheral Pin Select (PPS)" for more information).

# REGISTER 28-15: ADCCMPx: ADC DIGITAL COMPARATOR 'x' LIMIT VALUE REGISTER ('x' = 1 THROUGH 6)

| Bit Range | Bit<br>31/23/15/7                               | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |  |  |  |  |  |

|-----------|-------------------------------------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|--|--|--|--|--|

| 04:04     | R/W-0                                           | R/W-0             | R/W-0             | R/W-0<br>DCMPHI<  | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |  |  |  |  |

| 31:24     |                                                 |                   |                   |                   |                   |                   |                  |                  |  |  |  |  |  |

| 22:16     | R/W-0 R/W-0 R/W-0 R/W-0 R/W-0 R/W-0 R/W-0 R/W-0 |                   |                   |                   |                   |                   |                  |                  |  |  |  |  |  |

| 23:16     | DCMPHI<7:0>(1,2,3)                              |                   |                   |                   |                   |                   |                  |                  |  |  |  |  |  |

| 45.0      | R/W-0                                           | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |  |  |  |  |

| 15:8      | DCMPLO<15:8>(1,2,3)                             |                   |                   |                   |                   |                   |                  |                  |  |  |  |  |  |

| 7.0       | R/W-0                                           | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |  |  |  |  |

| 7:0       |                                                 | •                 | •                 | DCMPLO<           | 7:0>(1,2,3)       |                   |                  | •                |  |  |  |  |  |

Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

-n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown

bit 31-16 **DCMPHI<15:0>:** Digital Comparator 'x' High Limit Value bits<sup>(1,2,3)</sup>

These bits store the high limit value, which is used by digital comparator for comparisons with ADC converted data.

bit 15-0 **DCMPLO<15:0>:** Digital Comparator 'x' Low Limit Value bits (1,2,3)

These bits store the low limit value, which is used by digital comparator for comparisons with ADC converted data.

- **Note 1:** Changing theses bits while the Digital Comparator is enabled (ENDCMP = 1) can result in unpredictable behavior.

- 2: The format of the limit values should match the format of the ADC converted value in terms of sign and fractional settings.

- 3: For Digital Comparator 0 used in CVD mode, the DCMPHI<15:0> and DCMPLO<15:0> bits must always be specified in signed format, as the CVD output data is differential and is always signed.

### REGISTER 28-16: ADCFLTRx: ADC DIGITAL FILTER 'x' REGISTER ('x' = 1 THROUGH 6)

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |  |  |  |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|--|--|--|

| 04.04        | R/W-0             | R/W-0             | R/W-0 R/W-0       |                   | R/W-0 R/W-0       |                   | R/W-0            | R-0, HS, HC      |  |  |  |

| 31:24        | AFEN              | DATA16EN          | DFMODE            | 0                 | VRSAM<2:0         | >                 | AFGIEN           | AFRDY            |  |  |  |

| 00:40        | U-0               | U-0               | U-0               | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |  |  |

| 23:16        | _                 | — — CHNLID<4:0>   |                   |                   |                   |                   |                  |                  |  |  |  |

| 45.0         | R-0, HS, HC       | R-0, HS, HC      | R-0, HS, HC      |  |  |  |

| 15:8         |                   |                   |                   | FLTRDATA          | \<15:8>           |                   |                  |                  |  |  |  |

| 7.0          | R-0, HS, HC       | R-0, HS, HC      | R-0, HS, HC      |  |  |  |

| 7:0          |                   |                   |                   | FLTRDAT           | A<7:0>            |                   |                  |                  |  |  |  |

Legend:HS = Hardware SetHC = Hardware ClearedR = Readable bitW = Writable bitU = Unimplemented bit, read as '0'-n = Value at POR'1' = Bit is set'0' = Bit is clearedx = Bit is unknown

bit 31 AFEN: Digital Filter 'x' Enable bit

1 = Digital filter is enabled

0 = Digital filter is disabled and the AFRDY status bit is cleared

bit 30 DATA16EN: Filter Significant Data Length bit

1 = All 16 bits of the filter output data are significant

0 = Only the first 12 bits are significant, followed by four zeros

Note: This bit is significant only if DFMODE = 1 (Averaging Mode) and FRACT (ADCCON1<23>) = 1

(Fractional Output Mode).

bit **DFMODE:** ADC Filter Mode bit

1 = Filter 'x' works in Averaging mode

0 = Filter 'x' works in Oversampling Filter mode (default)

bit 28-26 OVRSAM<2:0>: Oversampling Filter Ratio bits

If DFMODE is '0':

111 = 128 samples (shift sum 3 bits to right, output data is in 15.1 format)

110 = 32 samples (shift sum 2 bits to right, output data is in 14.1 format)

101 = 8 samples (shift sum 1 bit to right, output data is in 13.1 format)

100 = 2 samples (shift sum 0 bits to right, output data is in 12.1 format)

011 = 256 samples (shift sum 4 bits to right, output data is 16 bits)

010 = 64 samples (shift sum 3 bits to right, output data is 15 bits)

001 = 16 samples (shift sum 2 bits to right, output data is 14 bits)

000 = 4 samples (shift sum 1 bit to right, output data is 13 bits)

### If DFMODE is '1':

111 = 256 samples (256 samples to be averaged)

110 = 128 samples (128 samples to be averaged)

101 = 64 samples (64 samples to be averaged)

100 = 32 samples (32 samples to be averaged)

011 = 16 samples (16 samples to be averaged)

010 = 8 samples (8 samples to be averaged) 001 = 4 samples (4 samples to be averaged)

000 = 2 samples (2 samples to be averaged)

bit 25 **AFGIEN:** Digital Filter 'x' Interrupt Enable bit

1 = Digital filter interrupt is enabled and is generated by the AFRDY status bit

0 = Digital filter is disabled

### 29.1 **CAN Control Registers**

Note: The 'i' shown in register names denotes

CAN1 or CAN2.

#### CAN1 REGISTER SUMMARY FOR PIC32MZXXXXECF AND PIC32MZXXXXECH DEVICES **TABLE 29-1:**

| SSe                         |                                 |           |          |                                                                      |          |           |          |            |           | Bit       | s        |           |          |          |          |            |           |          |            |

|-----------------------------|---------------------------------|-----------|----------|----------------------------------------------------------------------|----------|-----------|----------|------------|-----------|-----------|----------|-----------|----------|----------|----------|------------|-----------|----------|------------|

| Virtual Address<br>(BF88_#) | Register<br>Name <sup>(1)</sup> | Bit Range | 31/15    | 30/14                                                                | 29/13    | 28/12     | 27/11    | 26/10      | 25/9      | 24/8      | 23/7     | 22/6      | 21/5     | 20/4     | 19/3     | 18/2       | 17/1      | 16/0     | All Resets |

|                             | 04001                           | 31:16     | _        | _                                                                    | _        | _         | ABAT     |            | REQOP<2:0 | >         | (        | DPMOD<2:0 | >        | CANCAP   | _        | _          | _         | _        | 0480       |

| 0000                        | C1CON                           | 15:0      | ON       | _                                                                    | SIDLE    | -         | CANBUSY  | _          | _         | _         | _        | _         | _        |          | D        | NCNT<4:0>  |           | •        | 0000       |

| 0010                        | C1CFG                           | 31:16     | I        |                                                                      | _        | ı         | _        |            | _         | ı         | _        | WAKFIL    | _        | _        | _        | SI         | EG2PH<2:0 | >        | 0000       |

| 0010                        | CICFG                           | 15:0      | SEG2PHTS | SAM                                                                  | S        | EG1PH<2:0 | >        |            | PRSEG<2:0 | >         | SJW      | <1:0>     |          |          | BRP<     | 5:0>       |           |          | 0000       |

| 0020                        | C1INT                           | 31:16     | IVRIE    | WAKIE                                                                | CERRIE   | SERRIE    | RBOVIE   | _          | _         | _         | _        | _         | _        | _        | MODIE    | CTMRIE     | RBIE      | TBIE     | 0000       |

| 0020                        | CINT                            | 15:0      | IVRIF    | WAKIF                                                                | CERRIF   | SERRIF    | RBOVIF   | _          | _         | _         | _        | _         | _        | _        | MODIF    | CTMRIF     | RBIF      | TBIF     | 0000       |

| 0030                        | C1VEC                           | 31:16     | _        |                                                                      | _        |           | _        | _          | _         | _         | _        | _         | _        | _        | _        | _          | _         | _        | 0000       |

| 0030                        | OTVLO                           | 15:0      | _        | FILHIT<4:0> _ ICODE<6:0>                                             |          |           |          |            |           |           |          |           |          |          | 0040     |            |           |          |            |

| 0040                        | C1TREC                          | 31:16     | _        | _                                                                    | _        | _         | _        | _          | _         | _         | _        | _         | TXBO     | TXBP     | RXBP     | TXWARN     | RXWARN    | EWARN    | 0000       |

| 0040                        | CTINEC                          | 15:0      |          | TERRCNT<7:0> RERRCNT<7:0>                                            |          |           |          |            |           |           |          |           |          | 0000     |          |            |           |          |            |

| 0050                        | C1FSTAT                         | 31:16     | FIFOIP31 | FIFOIP30                                                             | FIFOIP29 | FIFOIP28  |          | FIFOIP26   | FIFOIP25  | FIFOIP24  | FIFOIP23 | FIFOIP22  | FIFOIP21 | FIFOIP20 | FIFOIP19 |            |           | FIFOIP16 |            |

| 0000                        | OHOTAI                          | 15:0      | FIFOIP15 | FIFOIP14                                                             | FIFOIP13 | FIFOIP12  | FIFOIP11 | FIFOIP10   | FIFOIP9   | FIFOIP8   | FIFOIP7  | FIFOIP6   | FIFOIP5  | FIFOIP4  | FIFOIP3  | FIFOIP2    | FIFOIP1   | FIFOIP0  |            |

| 0060                        | C1RXOVF                         | 31:16     | RXOVF31  | RXOVF30                                                              | RXOVF29  | RXOVF28   | _        | RXOVF26    | RXOVF25   | RXOVF24   | RXOVF23  | RXOVF22   | RXOVF21  | RXOVF20  | RXOVF19  | RXOVF18    |           | RXOVF16  |            |

| 0000                        | 01101011                        | 15:0      | RXOVF15  | RXOVF14                                                              | RXOVF13  | RXOVF12   | RXOVF11  | RXOVF10    | RXOVF9    | RXOVF8    | RXOVF7   | RXOVF6    | RXOVF5   | RXOVF4   | RXOVF3   | RXOVF2     | RXOVF1    | RXOVF0   | 0000       |

| 0070                        | C1TMR                           | 31:16     |          |                                                                      |          |           |          |            |           | CANTS<    |          |           |          |          |          |            |           | ,        | 0000       |

| 0070                        | 01111111                        | 15:0      |          |                                                                      |          |           |          |            | CA        | NTSPRE<15 | :0>      |           |          |          |          |            |           |          | 0000       |

| 0080                        | C1RXM0                          | 31:16     |          |                                                                      |          |           |          | SID<10:0>  |           |           |          |           |          |          | MIDE     | _          | EID<1     | 7:16>    | xxxx       |

| 0000                        | OTTOWN                          | 15:0      |          |                                                                      |          |           |          |            |           | EID<1     | 5:0>     |           |          |          |          |            |           |          | xxxx       |

| 0090                        | C1RXM1                          | 31:16     |          |                                                                      |          |           |          | SID<10:0>  |           |           |          |           |          | -        | MIDE     | I          | EID<1     | 7:16>    | xxxx       |

| 0090                        | CTRXIVIT                        | 15:0      |          |                                                                      |          |           |          |            |           | EID<1     | 5:0>     |           |          |          |          |            |           |          | xxxx       |

| 00A0                        | C1RXM2                          | 31:16     |          |                                                                      |          |           |          | SID<10:0>  |           |           |          |           |          |          | MIDE     | _          | EID<1     | 7:16>    | xxxx       |

| UUAU                        | CIRXIVIZ                        | 15:0      |          |                                                                      |          |           |          |            |           | EID<1     | 5:0>     |           |          |          |          |            |           |          | xxxx       |

| 0000                        | C1RXM3                          | 31:16     |          |                                                                      |          |           |          | SID<10:0>  |           |           |          |           |          | _        | MIDE     | -          | EID<1     | 7:16>    | xxxx       |

| 00B0                        | CTRXIVIS                        | 15:0      |          |                                                                      |          |           |          |            |           | EID<1     | 5:0>     |           |          |          |          |            | •         |          | xxxx       |

| 0000                        | C1FLTCON0                       | 31:16     | FLTEN3   | FLTEN3 MSEL3<1:0> FSEL3<4:0> FLTEN2 MSEL2<1:0> FSEL2<4:0> 0          |          |           |          |            |           |           |          |           |          | 0000     |          |            |           |          |            |

| 0000                        | CIFLICONU                       | 15:0      | FLTEN1   | MSEL                                                                 | 1<1:0>   |           |          | FSEL1<4:0  | >         |           | FLTEN0   | MSEL      | 0<1:0>   |          | F        | SEL0<4:0>  |           |          | 0000       |

| 0000                        | C1FLTCON1                       | 31:16     | FLTEN7   | FLTEN7 MSEL7<1:0> FSEL7<4:0> FLTEN6 MSEL6<1:0> FSEL6<4:0> FSEL6<4:0> |          |           |          |            |           |           |          |           |          | 0000     |          |            |           |          |            |

| 0000                        | CIFLICONT                       | 15:0      | FLTEN5   | FLTEN5 MSEL5<1:0> FSEL5<4:0> FLTEN4 MSEL4<1:0> FSEL4<<4:0>           |          |           |          |            |           |           |          |           |          |          | 0000     |            |           |          |            |

| 0050                        | C1FLTCON2                       | 31:16     | FLTEN11  | MSEL <sup>2</sup>                                                    | 11<1:0>  |           |          | FSEL11<4:0 | )>        |           | FLTEN10  | MSEL1     | 10<1:0>  |          | F        | SEL10<4:0> |           |          | 0000       |

| UUEU                        | C IFLI CON2                     | 15:0      | FLTEN9   | MSEL                                                                 | 9<1:0>   |           |          | FSEL9<4:0  | >         |           | FLTEN8   | MSEL      | 8<1:0>   |          | F        | SEL8<4:0>  |           |          | 0000       |

PIC32MZ Embedded Connectivity with Floating Point Unit (EF) Family

Note

x = unknown value on Reset; — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

All registers in this table have corresponding CLR, SET and INV registers at their virtual addresses, plus offsets of 0x4, 0x8 and 0xC, respectively. See Section 12.3 "CLR, SET, and INV Registers" for more information. 1:

### **REGISTER 29-10: CIFLTCON0: CAN FILTER CONTROL REGISTER 0**

| Bit Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |

|-----------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|

| 31:24     | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |

| 31.24     | FLTEN3 MSEL3<1:0> |                   | FSEL3<4:0>        |                   |                   |                   |                  |                  |

| 00:40     | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |

| 23:16     | FLTEN2            | MSEL2<1:0>        |                   | FSEL2<4:0>        |                   |                   |                  |                  |

| 15:8      | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |

|           | FLTEN1            | MSEL              | 1<1:0>            |                   | F                 | SEL1<4:0>         |                  |                  |

| 7:0       | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |

|           | FLTEN0            | MSEL              | 0<1:0>            |                   | F                 | SEL0<4:0>         |                  |                  |

Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

-n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown

bit 31 FLTEN3: Filter 3 Enable bit

1 = Filter is enabled

0 = Filter is disabled

bit 30-29 MSEL3<1:0>: Filter 3 Mask Select bits

11 = Acceptance Mask 3 selected

10 = Acceptance Mask 2 selected

01 = Acceptance Mask 1 selected

00 = Acceptance Mask 0 selected

bit 28-24 FSEL3<4:0>: FIFO Selection bits

11111 = Message matching filter is stored in FIFO buffer 31

11110 = Message matching filter is stored in FIFO buffer 30

•

\_

00001 = Message matching filter is stored in FIFO buffer 1

00000 = Message matching filter is stored in FIFO buffer 0

bit 23 FLTEN2: Filter 2 Enable bit

1 = Filter is enabled

0 = Filter is disabled

bit 22-21 MSEL2<1:0>: Filter 2 Mask Select bits

11 = Acceptance Mask 3 selected

10 = Acceptance Mask 2 selected

01 = Acceptance Mask 1 selected

00 = Acceptance Mask 0 selected

bit 20-16 FSEL2<4:0>: FIFO Selection bits

11111 = Message matching filter is stored in FIFO buffer 31

11110 = Message matching filter is stored in FIFO buffer 30

•

•

•

00001 = Message matching filter is stored in FIFO buffer 1

00000 = Message matching filter is stored in FIFO buffer 0

Note: The bits in this register can only be modified if the corresponding filter enable (FLTENn) bit is '0'.

### REGISTER 34-6: DEVCFG3/ADEVCFG3: DEVICE CONFIGURATION WORD 3

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |  |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|--|

| 31:24        | r-1               | R/P               | R/P               | R/P               | R/P               | r-1               | R/P              | R/P              |  |

| 31.24        |                   | FUSBIDIO          | IOL1WAY           | PMDL1WAY          | PGL1WAY           |                   | FETHIO           | FMIIEN           |  |

| 22:16        | r-1               | r-1               | r-1               | r-1               | r-1               | r-1               | r-1              | r-1              |  |

| 23:16        | _                 | _                 | _                 | _                 | -                 | _                 | 1                | 1                |  |

| 45.0         | R/P               | R/P               | R/P               | R/P               | R/P               | R/P               | R/P              | R/P              |  |

| 15:8         | USERID<15:8>      |                   |                   |                   |                   |                   |                  |                  |  |

| 7.0          | R/P               | R/P               | R/P               | R/P               | R/P               | R/P               | R/P              | R/P              |  |

| 7:0          |                   |                   |                   | USERID<           | 7:0>              |                   |                  |                  |  |

Legend:r = Reserved bitP = Programmable bitR = Readable bitW = Writable bitU = Unimplemented bit, read as '0'-n = Value at POR'1' = Bit is set'0' = Bit is clearedx = Bit is unknown

bit 31 Reserved: Write as '1'

bit 30 FUSBIDIO: USB USBID Selection bit

1 = USBID pin is controlled by the USB module 0 = USBID pin is controlled by the port function If USBMD is '1', USBID reverts to port control.

bit 29 **IOL1WAY:** Peripheral Pin Select Configuration bit

1 = Allow only one reconfiguration0 = Allow multiple reconfigurations

bit 28 PMDL1WAY: Peripheral Module Disable Configuration bit

1 = Allow only one reconfiguration0 = Allow multiple reconfigurations

bit 27 **PGL1WAY:** Permission Group Lock One Way Configuration bit

1 = Allow only one reconfiguration0 = Allow multiple reconfigurations

bit 26 Reserved: Write as '1'

bit 25 FETHIO: Ethernet I/O Pin Selection Configuration bit

1 = Default Ethernet I/O pins0 = Alternate Ethernet I/O pins

This bit is ignored for devices that do not have an alternate Ethernet pin selection.

bit 24 FMIIEN: Ethernet MII Enable Configuration bit

1 = MII is enabled 0 = RMII is enabled

bit 23-16 Reserved: Write as '1'

bit 15-0 USERID<15:0>: This is a 16-bit value that is user-defined and is readable via ICSP™ and JTAG

REGISTER 34-9: CFGEBIC: EXTERNAL BUS INTERFACE CONTROL PIN CONFIGURATION REGISTER

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|

|              | R/W-0             | R/W-0             | R/W-0             | U-0               | R/W-0             | R/W-0             | R/W-0            | U-0              |

| 31:24        | EBI<br>RDYINV3    | EBI<br>RDYINV2    | EBI<br>RDYIN1     | _                 | EBI<br>RDYEN3     | EBI<br>RDYEN2     | EBI<br>RDYEN1    | 1                |

| 00.40        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | R/W-0            | R/W-0            |

| 23:16        | -                 | _                 | _                 | _                 | _                 |                   | EBIRDYLVL        | EBIRPEN          |

| 15:8         | U-0               | U-0               | R/W-0             | R/W-0             | U-0               | U-0               | R/W-0            | R/W-0            |

|              | _                 | _                 | EBIWEEN           | EBIOEEN           | _                 | _                 | EBIBSEN1         | EBIBSEN0         |

| 7:0          | R/W-0             | R/W-0             | R/W-0             | R/W-0             | U-0               | U-0               | R/W-0            | R/W-0            |

|              | EBICSEN3          | EBICSEN2          | EBICSEN1          | EBICSEN0          |                   | 1                 | EBIDEN1          | EBIDEN0          |

Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

-n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown

bit 31 EBIRDYINV3: EBIRDY3 Inversion Control bit

1 = Invert EBIRDY3 pin before use

0 = Do not invert EBIRDY3 pin before use

bit 30 EBIRDYINV2: EBIRDY2 Inversion Control bit

1 = Invert EBIRDY2 pin before use

0 = Do not invert EBIRDY2 pin before use

bit 29 EBIRDYINV1: EBIRDY1 Inversion Control bit

1 = Invert EBIRDY1 pin before use

0 = Do not invert EBIRDY1 pin before use

bit 28 Unimplemented: Read as '0'

bit 27 EBIRDYEN3: EBIRDY3 Pin Enable bit

1 = EBIRDY3 pin is enabled for use by the EBI module

0 = EBIRDY3 pin is available for general use

bit 26 EBIRDYEN2: EBIRDY2 Pin Enable bit

1 = EBIRDY2 pin is enabled for use by the EBI module

0 = EBIRDY2 pin is available for general use

bit 25 EBIRDYEN1: EBIRDY1 Pin Enable bit

1 = EBIRDY1 pin is enabled for use by the EBI module

0 = EBIRDY1 pin is available for general use

bit 24-18 Unimplemented: Read as '0'

bit 17 EBIRDYLVL: EBIRDYx Pin Sensitivity Control bit

1 = Use level detect for EBIRDYx pins

0 = Use edge detect for EBIRDYx pins

bit 16 EBIRPEN: EBIRP Pin Sensitivity Control bit

$1 = \overline{\mathsf{EBIRP}}$  pin is enabled for use by the EBI module

0 = EBIRP pin is available for general use

bit 15-14 Unimplemented: Read as '0'

bit 13 EBIWEEN: EBIWE Pin Enable bit

$1 = \overline{\mathsf{EBIWE}}$  pin is enabled for use by the EBI module

0 = EBIWE pin is available for general use

**Note:** When EBIMD = 1, the bits in this register are ignored and the pins are available for general use.

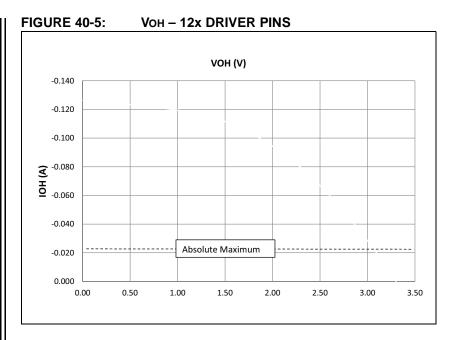

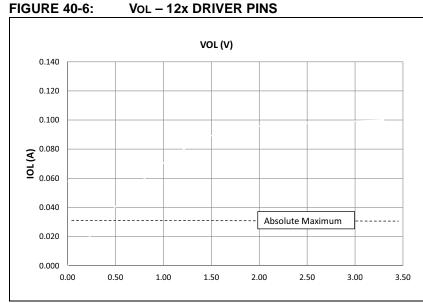

TABLE 37-11: DC CHARACTERISTICS: I/O PIN OUTPUT SPECIFICATIONS (CONTINUED)

| DC CHARACTERISTICS |      |                                                                                                                                                                                                                                                                           | Standard Operating Conditions: 2.1V to 3.6V (unless otherwise stated)  Operating temperature $-40^{\circ}\text{C} \le \text{TA} \le +85^{\circ}\text{C}$ for Industrial $-40^{\circ}\text{C} \le \text{TA} \le +125^{\circ}\text{C}$ for Extended |      |      |       |                                                      |  |

|--------------------|------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|------|-------|------------------------------------------------------|--|

| Param.             | Sym. | Characteristic                                                                                                                                                                                                                                                            | Min.                                                                                                                                                                                                                                              | Тур. | Max. | Units | Conditions <sup>(1)</sup>                            |  |

|                    |      | Output High Voltage I/O Pins:                                                                                                                                                                                                                                             | 1.5                                                                                                                                                                                                                                               | _    | _    | V     | $IOH \ge -14 \text{ mA}, \text{ VDD} = 3.3 \text{V}$ |  |

|                    |      | 4x Source Driver Pins -                                                                                                                                                                                                                                                   | 2.0                                                                                                                                                                                                                                               | _    | _    | V     | IOH $\geq$ -12 mA, VDD = 3.3V                        |  |

|                    |      | RA3, RA9, RA10, RA14, RA15<br>RB0-RB2, RB4, RB6-RB7, RB11, RB13<br>RC12-RC15<br>RD0, RD6-RD7, RD11, RD14<br>RE8, RE9<br>RF2, RF3, RF8<br>RG15<br>RH0, RH1, RH4-RH6, RH8-RH13<br>RJ0-RJ2, RJ8, RJ9, RJ11                                                                   | 3.0                                                                                                                                                                                                                                               |      | _    | V     | IOH $\geq$ -7 mA, VDD = 3.3V                         |  |

|                    |      | Output High Voltage I/O Pins:  8x Source Driver Pins - RA0-RA2, RA4, RA5 RB3, RB5, RB8-RB10, RB12, RB14, RB15 RC1-RC4 RD1-RD5, RD9, RD10, RD12, RD13, RD15 RE4-RE7 RF0, RF4, RF5, RF12, RF13 RG0, RG1, RG6-RG9 RH2, RH3, RH7, RH14, RH15 RJ3-RJ7, RJ10, RJ12-RJ15 RK0-RK7 | 1.5                                                                                                                                                                                                                                               | _    | _    | V     | IOH $\geq$ -22 mA, VDD = 3.3V                        |  |

|                    |      |                                                                                                                                                                                                                                                                           | 2.0                                                                                                                                                                                                                                               | _    | _    | V     | IOH ≥ -18 mA, VDD = 3.3V                             |  |

| DO20a \            | Von1 |                                                                                                                                                                                                                                                                           | 3.0                                                                                                                                                                                                                                               |      | _    | V     | IOH ≥ -10 mA, VDD = 3.3V                             |  |

|                    |      | Output High Voltage                                                                                                                                                                                                                                                       | 1.5                                                                                                                                                                                                                                               | _    | _    | V     | IOH $\geq$ -32 mA, VDD = 3.3V                        |  |

|                    |      | I/O Pins:<br>12x Source Driver Pins -<br>RA6, RA7<br>RE0-RE3<br>RF1<br>RG12-RG14                                                                                                                                                                                          | 2.0                                                                                                                                                                                                                                               | _    | _    | V     | IOH ≥ -25 mA, VDD = 3.3V                             |  |

|                    |      |                                                                                                                                                                                                                                                                           | 3.0                                                                                                                                                                                                                                               | _    | _    | V     | IOH ≥ -14 mA, VDD = 3.3V                             |  |

**Note 1:** Parameters are characterized, but not tested.

TABLE 37-33: SPIX MODULE SLAVE MODE (CKE = 1) TIMING REQUIREMENTS (CONTINUED)

| AC CHARACTERISTICS |                       |                                                    |      | Standard Operating Conditions: 2.1V to 3.6V (unless otherwise stated) Operating temperature -40°C $\leq$ TA $\leq$ +85°C for Industrial -40°C $\leq$ TA $\leq$ +125°C for Extended |      |       |            |  |

|--------------------|-----------------------|----------------------------------------------------|------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|-------|------------|--|

| Param.<br>No.      | Symbol                | Characteristics <sup>(1)</sup>                     | Min. | Typical <sup>(2)</sup>                                                                                                                                                             | Max. | Units | Conditions |  |

| SP50               | TssL2scH,<br>TssL2scL | SSx ↓ to SCKx ↓ or SCKx ↑ Input                    | 88   | _                                                                                                                                                                                  | 1    | ns    |            |  |

| SP51               | TssH2DoZ              | SSx ↑ to SDOx Output<br>High-Impedance<br>(Note 4) | 2.5  |                                                                                                                                                                                    | 12   | ns    | I          |  |

| SP52               | TscH2ssH<br>TscL2ssH  | SSx ↑ after SCKx Edge                              | 10   | _                                                                                                                                                                                  | _    | ns    |            |  |

| SP60               | TssL2DoV              | SDOx Data Output Valid after SSx Edge              | _    | _                                                                                                                                                                                  | 12.5 | ns    | _          |  |

Note 1: These parameters are characterized, but not tested in manufacturing.

- 3: The minimum clock period for SCKx is 20 ns.

- 4: Assumes 30 pF load on all SPIx pins.

<sup>2:</sup> Data in "Typical" column is at 3.3V, +25°C unless otherwise stated. Parameters are for design guidance only and are not tested.

TABLE A-10: PERIPHERAL DIFFERENCES (CONTINUED)

| PIC32MX5XX/6XX/7XX Feature                                                                                                                                                                                                                                                          | PIC32MZ EF Feature                                                                                                                                                                                                                                                                                                          |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Eth                                                                                                                                                                                                                                                                                 | ernet                                                                                                                                                                                                                                                                                                                       |

|                                                                                                                                                                                                                                                                                     | On PIC32MZ EF devices, the input clock divider for the Ethernet module has expanded options to accommodate the faster peripheral bus clock.                                                                                                                                                                                 |

| CLKSEL<3:0> (EMAC1MCFG<5:2>)  1000 = SYSCLK divided by 40  0111 = SYSCLK divided by 28  0110 = SYSCLK divided by 20  0101 = SYSCLK divided by 14  0100 = SYSCLK divided by 10  0011 = SYSCLK divided by 8  0010 = SYSCLK divided by 6  000x = SYSCLK divided by 4                   | CLKSEL<3:0> (EMAC1MCFG<5:2>)  1010 = PBCLK5 divided by 50  1001 = PBCLK5 divided by 48  1000 = PBCLK5 divided by 40  0111 = PBCLK5 divided by 28  0110 = PBCLK5 divided by 20  0101 = PBCLK5 divided by 14  0100 = PBCLK5 divided by 10  0011 = PBCLK5 divided by 8  0010 = PBCLK5 divided by 6  000x = PBCLK5 divided by 4 |

| Comparator/Compara                                                                                                                                                                                                                                                                  | ator Voltage Reference                                                                                                                                                                                                                                                                                                      |

| On PIC32MX devices, it was possible to select the VREF+ pin as the output to the CVREFOUT pin.                                                                                                                                                                                      | On PIC32MZ EF devices, the CVREFOUT pin must come from the resistor network.                                                                                                                                                                                                                                                |

| VREFSEL (CVRCON<10>)  1 = CVREF = VREF+  0 = CVREF is generated by the resistor network                                                                                                                                                                                             | This bit is not available.                                                                                                                                                                                                                                                                                                  |