Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFl

| Details                    |                                                                                  |

|----------------------------|----------------------------------------------------------------------------------|

| Product Status             | Active                                                                           |

| Core Processor             | MIPS32® M-Class                                                                  |

| Core Size                  | 32-Bit Single-Core                                                               |

| Speed                      | 200MHz                                                                           |

| Connectivity               | EBI/EMI, Ethernet, I <sup>2</sup> C, PMP, SPI, SQI, UART/USART, USB OTG          |

| Peripherals                | Brown-out Detect/Reset, DMA, I <sup>2</sup> S, POR, PWM, WDT                     |

| Number of I/O              | 120                                                                              |

| Program Memory Size        | 512KB (512K x 8)                                                                 |

| Program Memory Type        | FLASH                                                                            |

| EEPROM Size                | -                                                                                |

| RAM Size                   | 128K x 8                                                                         |

| Voltage - Supply (Vcc/Vdd) | 2.1V ~ 3.6V                                                                      |

| Data Converters            | A/D 48x12b                                                                       |

| Oscillator Type            | Internal                                                                         |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                                |

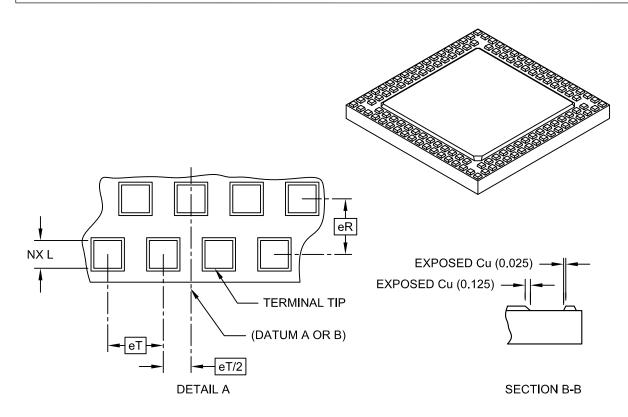

| Mounting Type              | Surface Mount                                                                    |

| Package / Case             | 144-TQFP                                                                         |

| Supplier Device Package    | 144-TQFP (16x16)                                                                 |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic32mz0512efe144-i-ph |

|                            |                                                                                  |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

## 1.0 DEVICE OVERVIEW

Note: This data sheet summarizes the features of the PIC32MZ EF family of devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to the *"PIC32 Family Reference Manual"*, which is available from the Microchip web site (www.microchip.com/PIC32). This data sheet contains device-specific information for PIC32MZ EF devices.

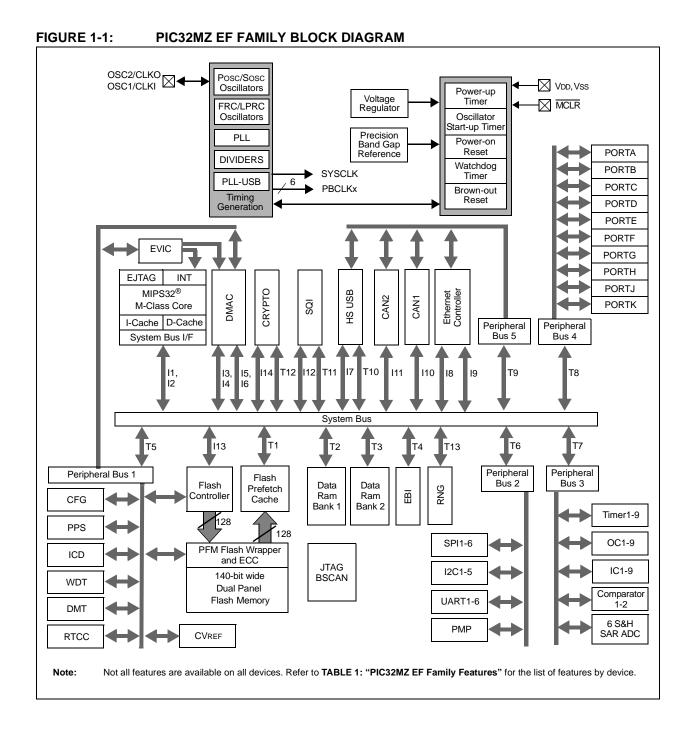

Figure 1-1 illustrates a general block diagram of the core and peripheral modules in the PIC32MZ EF family of devices.

Table 1-21 through Table 1-22 list the pinout I/O descriptions for the pins shown in the device pin tables (see Table 2 through Table 5).

|          |                        | Pin Nu          | mber            |                          |             |                |                        |

|----------|------------------------|-----------------|-----------------|--------------------------|-------------|----------------|------------------------|

| Pin Name | 64-pin<br>QFN/<br>TQFP | 100-pin<br>TQFP | 124-pin<br>VTLA | 144-pin<br>TQFP/<br>LQFP | Pin<br>Type | Buffer<br>Type | Description            |

| AN0      | 16                     | 25              | A18             | 36                       | I           | Analog         | Analog Input Channels  |

| AN1      | 15                     | 24              | A17             | 35                       | I           | Analog         |                        |

| AN2      | 14                     | 23              | A16             | 34                       | I           | Analog         |                        |

| AN3      | 13                     | 22              | A14             | 31                       | I           | Analog         |                        |

| AN4      | 12                     | 21              | A13             | 26                       | I           | Analog         |                        |

| AN5      | 23                     | 34              | B19             | 49                       | I           | Analog         |                        |

| AN6      | 24                     | 35              | A24             | 50                       | I           | Analog         |                        |

| AN7      | 27                     | 41              | A27             | 59                       | I           | Analog         |                        |

| AN8      | 28                     | 42              | B23             | 60                       | I           | Analog         |                        |

| AN9      | 29                     | 43              | A28             | 61                       | I           | Analog         | 1                      |

| AN10     | 30                     | 44              | B24             | 62                       | I           | Analog         |                        |

| AN11     | 10                     | 16              | B9              | 21                       | I           | Analog         |                        |

| AN12     | 6                      | 12              | B7              | 16                       | I           | Analog         |                        |

| AN13     | 5                      | 11              | A8              | 15                       | I           | Analog         |                        |

| AN14     | 4                      | 10              | B6              | 14                       | I           | Analog         |                        |

| AN15     | 3                      | 5               | A4              | 5                        | I           | Analog         |                        |

| AN16     | 2                      | 4               | B2              | 4                        | I           | Analog         |                        |

| AN17     | 1                      | 3               | A3              | 3                        | I           | Analog         |                        |

| AN18     | 64                     | 100             | A67             | 144                      | I           | Analog         |                        |

| AN19     | —                      | 9               | A7              | 13                       | I           | Analog         |                        |

| AN20     | —                      | 8               | B5              | 12                       | I           | Analog         |                        |

| AN21     | —                      | 7               | A6              | 11                       | I           | Analog         |                        |

| AN22     | —                      | 6               | B3              | 6                        | I           | Analog         |                        |

| AN23     | —                      | 1               | A2              | 1                        | I           | Analog         |                        |

| AN24     | —                      | 17              | A11             | 22                       | I           | Analog         |                        |

| AN25     | _                      | 18              | B10             | 23                       | I           | Analog         |                        |

| AN26     | —                      | 19              | A12             | 24                       | I           | Analog         |                        |

| AN27     | —                      | 28              | B15             | 39                       | I           | Analog         |                        |

| AN28     | —                      | 29              | A20             | 40                       | I           | Analog         | 1                      |

| AN29     | —                      | 38              | B21             | 56                       | I           | Analog         | 1                      |

| AN30     | —                      | 39              | A26             | 57                       | I           | Analog         | ]                      |

| AN31     | —                      | 40              | B22             | 58                       | I           | Analog         | 1                      |

| AN32     | —                      | 47              | B27             | 69                       | I           | Analog         | 1                      |

| AN33     | —                      | 48              | A32             | 70                       | I           | Analog         | 1                      |

| AN34     | — 2 B1 2               |                 | I               | Analog                   | 1           |                |                        |

| AN35     | —                      | —               | A5              | 7                        | I           | Analog         | 1                      |

| Legend:  | CMOS = C               | MOS-comp        | atible input    | or output                |             | Analog =       | Analog input P = Power |

## TABLE 1-1: ADC PINOUT I/O DESCRIPTIONS

egend: CMOS = CMOS-compatible input or output ST = Schmitt Trigger input with CMOS levels TTL = Transistor-transistor Logic input buffer

Analog = Analog input O = Output PPS = Peripheral Pin Select

I = Input

|          |                        | Pin Nu          | mber            |                          |             |                |                                   |

|----------|------------------------|-----------------|-----------------|--------------------------|-------------|----------------|-----------------------------------|

| Pin Name | 64-pin<br>QFN/<br>TQFP | 100-pin<br>TQFP | 124-pin<br>VTLA | 144-pin<br>TQFP/<br>LQFP | Pin<br>Type | Buffer<br>Type | Description                       |

|          | •                      | •               |                 | •                        | PO          | RTD            | ·                                 |

| RD0      | 46                     | 71              | A48             | 104                      | I/O         | ST             | PORTD is a bidirectional I/O port |

| RD1      | 49                     | 76              | A52             | 109                      | I/O         | ST             |                                   |

| RD2      | 50                     | 77              | B42             | 110                      | I/O         | ST             |                                   |

| RD3      | 51                     | 78              | A53             | 111                      | I/O         | ST             |                                   |

| RD4      | 52                     | 81              | A56             | 118                      | I/O         | ST             |                                   |

| RD5      | 53                     | 82              | B46             | 119                      | I/O         | ST             |                                   |

| RD6      | —                      | _               | A57             | 120                      | I/O         | ST             |                                   |

| RD7      | —                      | _               | B47             | 121                      | I/O         | ST             |                                   |

| RD9      | 43                     | 68              | B38             | 97                       | I/O         | ST             |                                   |

| RD10     | 44                     | 69              | A46             | 98                       | I/O         | ST             |                                   |

| RD11     | 45                     | 70              | B39             | 99                       | I/O         | ST             |                                   |

| RD12     | —                      | 79              | B43             | 112                      | I/O         | ST             |                                   |

| RD13     | —                      | 80              | A54             | 113                      | I/O         | ST             |                                   |

| RD14     | —                      | 47              | B27             | 69                       | I/O         | ST             |                                   |

| RD15     | —                      | 48              | A32             | 70                       | I/O         | ST             |                                   |

|          |                        |                 |                 |                          | PO          | RTE            |                                   |

| RE0      | 58                     | 91              | B52             | 135                      | I/O         | ST             | PORTE is a bidirectional I/O port |

| RE1      | 61                     | 94              | A64             | 138                      | I/O         | ST             |                                   |

| RE2      | 62                     | 98              | A66             | 142                      | I/O         | ST             |                                   |

| RE3      | 63                     | 99              | B56             | 143                      | I/O         | ST             |                                   |

| RE4      | 64                     | 100             | A67             | 144                      | I/O         | ST             |                                   |

| RE5      | 1                      | 3               | A3              | 3                        | I/O         | ST             |                                   |

| RE6      | 2                      | 4               | B2              | 4                        | I/O         | ST             |                                   |

| RE7      | 3                      | 5               | A4              | 5                        | I/O         | ST             |                                   |

| RE8      | —                      | 18              | B10             | 23                       | I/O         | ST             |                                   |

| RE9      |                        | 19              | A12             | 24                       | I/O         | ST             |                                   |

|          |                        |                 |                 |                          | PC          | RTF            |                                   |

| RF0      | 56                     | 85              | A59             | 124                      | I/O         | ST             | PORTF is a bidirectional I/O port |

| RF1      | 57                     | 86              | B49             | 125                      | I/O         | ST             |                                   |

| RF2      |                        | 57              | B31             | 79                       | I/O         | ST             |                                   |

| RF3      | 38                     | 56              | A38             | 78                       | I/O         | ST             |                                   |

| RF4      | 41                     | 64              | B36             | 90                       | I/O         | ST             |                                   |

| RF5      | 42                     | 65              | A44             | 91                       | I/O         | ST             |                                   |

| RF8      | _                      | 58              | A39             | 80                       | I/O         | ST             | ]                                 |

| RF12     | —                      | 40              | B22             | 58                       | I/O         | ST             |                                   |

| RF13     | —                      | 39              | A26             | 57                       | I/O         | ST             |                                   |

| Legend:  | CMOS = C               | MOS-comp        | atible input    | t or output              |             | Analog =       | Analog input P = Power            |

#### **TABLE 1-6:** PORTA THROUGH PORTK PINOUT I/O DESCRIPTIONS (CONTINUED)

CMOS = CMOS-compatible input or output ST = Schmitt Trigger input with CMOS levels TTL = Transistor-transistor Logic input buffer

Analog = Analog input O = Output PPS = Peripheral Pin Select P = Power I = Input

## 2.9 Designing for High-Speed Peripherals

The PIC32MZ EF family devices have peripherals that operate at frequencies much higher than typical for an embedded environment. Table 2-1 lists the peripherals that produce high-speed signals on their external pins:

## TABLE 2-1: PERIPHERALS THAT PRODUCE HS SIGNALS ON EXTERNAL PINS

| Peripheral | High-Speed<br>Signal Pins   | Maximum<br>Speed on<br>Signal Pin |  |  |  |

|------------|-----------------------------|-----------------------------------|--|--|--|

| EBI        | EBIAx,<br>EBIDx             | 50 MHz                            |  |  |  |

| SQI1       | SQICLK,<br>SQICSx,<br>SQIDx | 50 MHz                            |  |  |  |

| HS USB     | D+, D-                      | 480 MHz                           |  |  |  |

Due to these high-speed signals, it is important to consider several factors when designing a product that uses these peripherals, as well as the PCB on which these components will be placed. Adhering to these recommendations will help achieve the following goals:

- Minimize the effects of electromagnetic interference to the proper operation of the product

- Ensure signals arrive at their intended destination at the same time

- Minimize crosstalk

- Maintain signal integrity

- Reduce system noise

- Minimize ground bounce and power sag

## 2.9.1 SYSTEM DESIGN

## 2.9.1.1 Impedance Matching

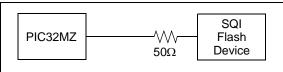

When selecting parts to place on high-speed buses, particularly the SQI bus, if the impedance of the peripheral device does not match the impedance of the pins on the PIC32MZ EF device to which it is connected, signal reflections could result, thereby degrading the quality of the signal.

If it is not possible to select a product that matches impedance, place a series resistor at the load to create the matching impedance. See Figure 2-4 for an example.

#### FIGURE 2-4: SERIES RESISTOR

## 2.9.1.2 PCB Layout Recommendations

The following list contains recommendations that will help ensure the PCB layout will promote the goals previously listed.

#### Component Placement

- Place bypass capacitors as close to their component power and ground pins as possible, and place them on the same side of the PCB

- Devices on the same bus that have larger setup times should be placed closer to the PIC32MZ EF device

#### • Power and Ground

- Multi-layer PCBs will allow separate power and ground planes

- Each ground pin should be connected to the ground plane individually

- Place bypass capacitor vias as close to the pad as possible (preferably inside the pad)

- If power and ground planes are not used, maximize width for power and ground traces

- Use low-ESR, surface-mount bypass capacitors

#### • Clocks and Oscillators

- Place crystals as close as possible to the PIC32MZ EF device OSC/SOSC pins

- Do not route high-speed signals near the clock or oscillator

- Avoid via usage and branches in clock lines (SQICLK)

- Place termination resistors at the end of clock lines

- Traces

- Higher-priority signals should have the shortest traces

- Match trace lengths for parallel buses (EBIAx, EBIDx, SQIDx)

- Avoid long run lengths on parallel traces to reduce coupling

- Make the clock traces as straight as possible

- Use rounded turns rather than right-angle turns

- Have traces on different layers intersect on right angles to minimize crosstalk

- Maximize the distance between traces, preferably no less than three times the trace width

- Power traces should be as short and as wide as possible

- High-speed traces should be placed close to the ground plane

## 3.1.4 FLOATING POINT UNIT (FPU)

The Floating Point Unit (FPU), Coprocessor (CP1), implements the MIPS Instruction Set Architecture for floating point computation. The implementation supports the ANSI/IEEE Standard 754 (IEEE for Binary Floating Point Arithmetic) for 32-bit and 64-bit floating point data formats. The FPU can be programmed to have thirty-two 32-bit or 64-bit floating point registers used for floating point operations.

The performance is optimized for 32-bit formats. Most instructions have one FPU cycle throughput and four FPU cycle latency. The FPU implements the multiply-add (MADD) and multiply-sub (MSUB) instructions with intermediate rounding after the multiply function. The result is guaranteed to be the same as executing a MUL and an ADD instruction separately, but the instruction latency, instruction fetch, dispatch bandwidth, and the total number of register accesses are improved.

IEEE denormalized input operands and results are supported by hardware for some instructions. IEEE denormalized results are not supported by hardware in general, but a fast flush-to-zero mode is provided to optimize performance. The fast flush-to-zero mode is enabled through the FCCR register, and use of this mode is recommended for best performance when denormalized results are generated.

The FPU has a separate pipeline for floating point instruction execution. This pipeline operates in parallel with the integer core pipeline and does not stall when the integer pipeline stalls. This allows long-running FPU operations, such as divide or square root, to be partially masked by system stalls and/or other integer unit instructions. Arithmetic instructions are always dispatched and completed in order, but loads and stores can complete out of order. The exception model is "precise" at all times.

Table 3-4 contains the floating point instruction latencies and repeat rates for the processor core. In this table, 'Latency' refers to the number of FPU cycles necessary for the first instruction to produce the result needed by the second instruction. The "Repeat Rate" refers to the maximum rate at which an instruction can be executed per FPU cycle.

#### TABLE 3-4: FPU INSTRUCTION LATENCIES AND REPEAT RATES

| Op code                                                                                                            | Latency<br>(FPU<br>Cycles) | Repeat<br>Rate<br>(FPU<br>Cycles) |

|--------------------------------------------------------------------------------------------------------------------|----------------------------|-----------------------------------|

| ABS.[S,D], NEG.[S,D],<br>ADD.[S,D], SUB.[S,D],<br>C.cond.[S,D], MUL.S                                              | 4                          | 1                                 |

| MADD.S, MSUB.S,<br>NMADD.S, NMSUB.S,<br>CABS.cond.[S,D]                                                            | 4                          | 1                                 |

| CVT.D.S, CVT.PS.PW,<br>CVT.[S,D].[W,L]                                                                             | 4                          | 1                                 |

| CVT.S.D,<br>CVT.[W,L].[S,D],<br>CEIL.[W,L].[S,D],<br>FLOOR.[W,L].[S,D],<br>ROUND.[W,L].[S,D],<br>TRUNC.[W,L].[S,D] | 4                          | 1                                 |

| MOV.[S,D], MOVF.[S,D],<br>MOVN.[S,D],<br>MOVT.[S,D], MOVZ.[S,D]                                                    | 4                          | 1                                 |

| MUL.D                                                                                                              | 5                          | 2                                 |

| MADD.D, MSUB.D,<br>NMADD.D, NMSUB.D                                                                                | 5                          | 2                                 |

| RECIP.S                                                                                                            | 13                         | 10                                |

| RECIP.D                                                                                                            | 26                         | 21                                |

| RSQRT.S                                                                                                            | 17                         | 14                                |

| RSQRT.D                                                                                                            | 36                         | 31                                |

| DIV.S, SQRT.S                                                                                                      | 17                         | 14                                |

| DIV.D, SQRT.D                                                                                                      | 32                         | 29                                |

| MTC1, DMTC1, LWC1,<br>LDC1, LDXC1, LUXC1,<br>LWXC1                                                                 | 4                          | 1                                 |

| MFC1, DMFC1, SWC1,<br>SDC1, SDXC1, SUXC1,<br>SWXC1                                                                 | 1                          | 1                                 |

Legend: S = Single (32-bit) D = Double (64-bit)W = Word (32-bit) L = Long word (64-bit)

## 4.0 MEMORY ORGANIZATION

| Note: | This data sheet summarizes the features<br>of the PIC32MZ EF family of devices. It is<br>not intended to be a comprehensive<br>reference source.For detailed<br>information, refer to <b>Section 48</b> . |

|-------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|       | "Memory Organization and<br>Permissions" in the "PIC32 Family<br>Reference Manual", which is available<br>from the Microchip web site<br>(www.microchip.com/PIC32).                                       |

PIC32MZ EF microcontrollers provide 4 GB of unified virtual memory address space. All memory regions, including program, data memory, SFRs and Configuration registers, reside in this address space at their respective unique addresses. The program and data memories can be optionally partitioned into user and kernel memories. In addition, PIC32MZ EF devices allow execution from data memory.

Key features include:

- 32-bit native data width

- Separate User (KUSEG) and Kernel (KSEG0/ KSEG1/KSEG2/KSEG3) mode address space

- Separate boot Flash memory for protected code

- Robust bus exception handling to intercept runaway code

- Cacheable (KSEG0/KSEG2) and non-cacheable (KSEG1/KSEG3) address regions

- Read/write permission access to predefined memory regions

## 4.1 Memory Layout

PIC32MZ EF microcontrollers implement two address schemes: virtual and physical. All hardware resources, such as program memory, data memory and peripherals, are located at their respective physical addresses. Virtual addresses are exclusively used by the CPU to fetch and execute instructions as well as access peripherals. Physical addresses are used by bus master peripherals, such as DMA and the Flash controller, that access memory independently of the CPU.

The main memory maps for the PIC32MZ EF devices are illustrated in Figure 4-1 through Figure 4-4. Figure 4-5 provides memory map information for boot Flash and boot alias. Table 4-1 provides memory map information for Special Function Registers (SFRs).

#### **TABLE 4-6:** SYSTEM BUS TARGETS AND ASSOCIATED PROTECTION REGISTERS (CONTINUED)

|                  |                                                                            |            |                                             | SBTxREC                      | Gy Register                                |                |                   |                   | SBTxRD   | y Register                                                      | SBTxWR   | y Register                                                       |

|------------------|----------------------------------------------------------------------------|------------|---------------------------------------------|------------------------------|--------------------------------------------|----------------|-------------------|-------------------|----------|-----------------------------------------------------------------|----------|------------------------------------------------------------------|

| Target<br>Number | Target Description <sup>(5)</sup>                                          | Name       | Region Base<br>(BASE<21:0>)<br>(see Note 2) | Physical<br>Start<br>Address | Region Size<br>(SIZE<4:0>)<br>(see Note 3) | Region<br>Size | Priority<br>(PRI) | Priority<br>Level | Name     | Read<br>Permission<br>(GROUP3,<br>GROUP2,<br>GROUP1,<br>GROUP0) | Name     | Write<br>Permission<br>(GROUP3,<br>GROUP2,<br>GROUP1,<br>GROUP0) |

|                  | Peripheral Set 2:                                                          | SBT6REG0   | R                                           | 0x1F820000                   | R                                          | 64 KB          | —                 | 0                 | SBT6RD0  | R/W <sup>(1)</sup>                                              | SBT6WR0  | R/W <sup>(1)</sup>                                               |

| 6                | SPI1-SPI6<br>I2C1-I2C5<br>UART1-UART6<br>PMP                               | SBT6REG1   | R/W                                         | R/W                          | R/W                                        | R/W            | _                 | 3                 | SBT6RD1  | R/W <sup>(1)</sup>                                              | SBT6WR1  | R/W <sup>(1)</sup>                                               |

|                  | Peripheral Set 3:                                                          | SBT7REG0   | R                                           | 0x1F840000                   | R                                          | 64 KB          | —                 | 0                 | SBT7RD0  | R/W <sup>(1)</sup>                                              | SBT7WR0  | R/W <sup>(1)</sup>                                               |

| 7                | Timer1-Timer9<br>IC1-IC9<br>OC1-OC9<br>ADC<br>Comparator 1<br>Comparator 2 | SBT7REG1   | R/W                                         | R/W                          | R/W                                        | R/W            | _                 | 3                 | SBT7RD1  | R/W <sup>(1)</sup>                                              | SBT7WR1  | R/W <sup>(1)</sup>                                               |

|                  | Peripheral Set 4:                                                          | SBT8REG0   | R                                           | 0x1F860000                   | R                                          | 64 KB          | —                 | 0                 | SBT8RD0  | R/W <sup>(1)</sup>                                              | SBT8WR0  | R/W <sup>(1)</sup>                                               |

| 8                | PORTA-PORTK                                                                | SBT8REG1   | R/W                                         | R/W                          | R/W                                        | R/W            | —                 | 3                 | SBT8RD1  | R/W <sup>(1)</sup>                                              | SBT8WR1  | R/W <sup>(1)</sup>                                               |

|                  | Peripheral Set 5:                                                          | SBT9REG0   | R                                           | 0x1F880000                   | R                                          | 64 KB          | —                 | 0                 | SBT9RD0  | R/W <sup>(1)</sup>                                              | SBT9WR0  | R/W <sup>(1)</sup>                                               |

| 9                | CAN1<br>CAN2<br>Ethernet Controller                                        | SBT9REG1   | R/W                                         | R/W                          | R/W                                        | R/W            | _                 | 3                 | SBT9RD1  | R/W <sup>(1)</sup>                                              | SBT9WR1  | R/W <sup>(1)</sup>                                               |

| 10               | Peripheral Set 6:<br>USB                                                   | SBT10REG0  | R                                           | 0x1F8E3000                   | R                                          | 4 KB           | _                 | 0                 | SBT10RD0 | R/W <sup>(1)</sup>                                              | SBT10WR0 | R/W <sup>(1)</sup>                                               |

| 11               | External Memory via SQI1 and                                               | SBT11REG0  | R                                           | 0x30000000                   | R                                          | 64 MB          | —                 | 0                 | SBT11RD0 | R/W <sup>(1)</sup>                                              | SBT11WR0 | R/W <sup>(1)</sup>                                               |

| 11               | SQI1 Module                                                                | SBT11REG1  | R                                           | 0x1F8E2000                   | R                                          | 4 KB           | _                 | 3                 | SBT11RD1 | R/W <sup>(1)</sup>                                              | SBT11WR1 | R/W <sup>(1)</sup>                                               |

| 12               | Peripheral Set 7:<br>Crypto Engine                                         | SBT12REG0  | R                                           | 0x1F8E5000                   | R                                          | 4 KB           | _                 | 0                 | SBT12RD0 | R/W <sup>(1)</sup>                                              | SBT12WR0 | R/W <sup>(1)</sup>                                               |

| 13               | Peripheral Set 8:<br>RNG Module                                            | SBT13REG0  | R                                           | 0x1F8E6000                   | R                                          | 4 KB           | _                 | 0                 | SBT13RD0 | R/W <sup>(1)</sup>                                              | SBT13WR0 | R/W <sup>(1)</sup>                                               |

| Legend:          | R = Read; $R/W = R$                                                        | ead/Write; | 'x' in a regist                             | er name = 0-13;              | 'y' ir                                     | a register na  | ame = 0-8.        |                   |          |                                                                 |          |                                                                  |

Reset values for these bits are '0', '1', '1', '1', respectively. Note 1:

2:

The BASE<21:0> bits must be set to the corresponding Physical Address and right shifted by 10 bits. For Read-only bits, this value is set by hardware on Reset. The SIZE<4:0> bits must be set to the corresponding Region Size, based on the following formula: Region Size = 2<sup>(SIZE-1)</sup> x 1024 bytes. For read-only bits, this value is set by hardware on Reset. 3:

Refer to the Device Memory Maps (Figure 4-1 through Figure 4-4) for specific device memory sizes and start addresses. 4:

5: See Table 4-1for information on specific target memory size and start addresses.

6: The SBTxREG1 SFRs are reserved, and therefore, are not listed in this table for this target.

## 7.0 CPU EXCEPTIONS AND INTERRUPT CONTROLLER

Note: This data sheet summarizes the features of the PIC32MZ EF family of devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to Section 8. "Interrupt Controller" (DS60001108) and Section 50. "CPU MIPS32<sup>®</sup> for Devices with microAptiv<sup>™</sup> and M-Class Cores" (DS60001192) of the "PIC32 Family Reference Manual", which is available from the Microchip web site (www.microchip.com/PIC32).

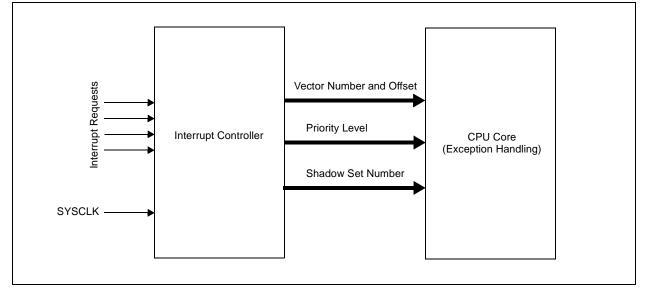

PIC32MZ EF devices generate interrupt requests in response to interrupt events from peripheral modules. The Interrupt Controller module exists outside of the CPU and prioritizes the interrupt events before presenting them to the CPU.

The CPU handles interrupt events as part of the exception handling mechanism, which is described in **Section 7.1 "CPU Exceptions"**.

The Interrupt Controller module includes the following features:

- Up to 213 interrupt sources and vectors with dedicated programmable offsets, eliminating the need for redirection

- · Single and multi-vector mode operations

- · Five external interrupts with edge polarity control

- Interrupt proximity timer

- Seven user-selectable priority levels for each vector

- Four user-selectable subpriority levels within each priority

- Seven shadow register sets that can be used for any priority level, eliminating software context switch and reducing interrupt latency

- Software can generate any interrupt

Figure 7-1 shows the block diagram for the Interrupt Controller and CPU exceptions.

## FIGURE 7-1: CPU EXCEPTIONS AND INTERRUPT CONTROLLER MODULE BLOCK DIAGRAM

|              |                   |                 |       |                   |                   |                   | -11 (7 - 0 10    | •)               |  |  |  |  |  |

|--------------|-------------------|-----------------|-------|-------------------|-------------------|-------------------|------------------|------------------|--|--|--|--|--|

| Bit<br>Range | Bit<br>31/23/15/7 |                 |       | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |  |  |  |  |  |

| 24.24        | U-0               | U-0             | U-0   | U-0               | U-0               | U-0               | U-0              | U-0              |  |  |  |  |  |

| 31:24        | —                 | —               | —     |                   | —                 | —                 | _                | —                |  |  |  |  |  |

| 22.16        | U-0               | U-0             | U-0   | U-0               | U-0               | U-0               | R/W-0            | R/W-0            |  |  |  |  |  |

| 23:16        | —                 | — — — — — VOFF< |       |                   |                   |                   |                  |                  |  |  |  |  |  |

| 15.0         | R/W-0             | R/W-0           | R/W-0 | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |  |  |  |  |

| 15:8         | VOFF<15:8>        |                 |       |                   |                   |                   |                  |                  |  |  |  |  |  |

| 7.0          | R/W-0             | R/W-0           | R/W-0 | R/W-0             | R/W-0             | R/W-0             | R/W-0            | U-0              |  |  |  |  |  |

| 7:0          |                   |                 |       | VOFF<7:1>         |                   |                   |                  | _                |  |  |  |  |  |

## **REGISTER 7-8:** OFFx: INTERRUPT VECTOR ADDRESS OFFSET REGISTER (x = 0-190)

| Legend:           |                  |                                    |                    |  |  |  |  |

|-------------------|------------------|------------------------------------|--------------------|--|--|--|--|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, read as '0' |                    |  |  |  |  |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared               | x = Bit is unknown |  |  |  |  |

bit 31-16 Unimplemented: Read as '0'

bit 17-1 VOFF<17:1>: Interrupt Vector 'x' Address Offset bits

bit 0 Unimplemented: Read as '0'

|              |                   | (ENDFOIN          | 1 1-7)            |                   |                   |                                                                                                  |                  |                  |  |  |  |  |  |  |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|--------------------------------------------------------------------------------------------------|------------------|------------------|--|--|--|--|--|--|

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2                                                                                | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |  |  |  |  |  |  |

|              | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0                                                                                            | R/W-0            | R/W-0            |  |  |  |  |  |  |

| 31:24        | AUTOSET           | ISO               | MODE              |                   | EPODATTO          |                                                                                                  | —                | —                |  |  |  |  |  |  |

|              | AUTOSET           |                   | NODE              | DIMAREQUI         | FREDATIG          | DIVIAREQIVID                                                                                     | DATAWEN          | DATATGGL         |  |  |  |  |  |  |

|              | R/W-0, HS         | R/W-0, HC         | R/W-0, HS         | R/W-0             | R/W-0             | R/W-0, HS                                                                                        | R/W-0            | R/W-0, HC        |  |  |  |  |  |  |

| 23:16        | INCOMPTX          | CLRDT             | SENTSTALL         | SENDSTALL         | FLUSH             | UNDERRUN                                                                                         | FIEONE           | עחסדאסעד         |  |  |  |  |  |  |

|              | NAKTMOUT          | GERDI             | RXSTALL           | SETUPPKT          | FLUSH             | TTG DMAREQMD DATAWEN DATATGGL<br>0 RW-0, HS RW-0 RW-0, HC<br>0 UNDERRUN<br>ERROR FIFONE TXPKTRDY |                  |                  |  |  |  |  |  |  |

| 15.0         | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0                                                                                            | R/W-0            | R/W-0            |  |  |  |  |  |  |

| 15:8         |                   |                   | MULT<4:0>         |                   |                   | T.                                                                                               | XMAXP<10:8       | >                |  |  |  |  |  |  |

| 7.0          | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0                                                                                            | R/W-0            | R/W-0            |  |  |  |  |  |  |

| 7:0          |                   | TXMAXP<7:0>       |                   |                   |                   |                                                                                                  |                  |                  |  |  |  |  |  |  |

## REGISTER 11-8: USBIENCSR0: USB INDEXED ENDPOINT CONTROL STATUS REGISTER 0 (ENDPOINT 1-7)

| Legend:           |                  |                            |                    |

|-------------------|------------------|----------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, rea | ad as '0'          |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared       | x = Bit is unknown |

#### bit 31 AUTOSET: Auto Set Control bit

- 1 = TXPKTRDY will be automatically set when data of the maximum packet size (value in TXMAXP) is loaded into the TX FIFO. If a packet of less than the maximum packet size is loaded, then TXPKTRDY will have to be set manually.

- 0 = TXPKTRDY must be set manually for all packet sizes

- **ISO:** Isochronous TX Endpoint Enable bit (Device mode)

- 1 = Enables the endpoint for Isochronous transfers

- 0 = Disables the endpoint for Isochronous transfers and enables it for Bulk or Interrupt transfers.

- This bit only has an effect in Device mode. In Host mode, it always returns zero.

- bit 29 MODE: Endpoint Direction Control bit

- 1 = Endpoint is TX

bit 30

0 = Endpoint is RX

This bit only has any effect where the same endpoint FIFO is used for both TX and RX transactions.

- bit 28 DMAREQEN: Endpoint DMA Request Enable bit

- 1 = DMA requests are enabled for this endpoint

- 0 = DMA requests are disabled for this endpoint

#### bit 27 **FRCDATTG:** Force Endpoint Data Toggle Control bit

- 1 = Forces the endpoint data toggle to switch and the data packet to be cleared from the FIFO, regardless of whether an ACK was received.

- 0 = No forced behavior

- bit 26 DMAREQMD: Endpoint DMA Request Mode Control bit

- 1 = DMA Request Mode 1

- 0 = DMA Request Mode 0

This bit must not be cleared either before or in the same cycle as the above DMAREQEN bit is cleared.

- bit 25 DATAWEN: Data Toggle Write Enable bit (Host mode)

- 1 = Enable the current state of the TX Endpoint data toggle (DATATGGL) to be written

- 0 = Disables writing the DATATGGL bit

- bit 24 **DATATGGL:** Data Toggle Control bit (Host mode)

When read, this bit indicates the current state of the TX Endpoint data toggle. If DATAWEN = 1, this bit may be written with the required setting of the data toggle. If DATAWEN = 0, any value written to this bit is ignored.

## REGISTER 11-8: USBIENCSR0: USB INDEXED ENDPOINT CONTROL STATUS REGISTER 0 (ENDPOINT 1-7) (CONTINUED)

- bit 23 **INCOMPTX:** Incomplete TX Status bit (Device mode)

- 1 = For high-bandwidth Isochronous endpoint, a large packet has been split into 2 or 3 packets for transmission but insufficient IN tokens have been received to send all the parts

- 0 = Normal operation

In anything other than isochronous transfers, this bit will always return 0.

#### NAKTMOUT: NAK Time-out status bit (Host mode)

- 1 = TX endpoint is halted following the receipt of NAK responses for longer than the NAKLIM setting

- 0 = Written by software to clear this bit

- bit 22 **CLRDT:** Clear Data Toggle Control bit

- 1 = Resets the endpoint data toggle to 0

- 0 = Do not clear the data toggle

- bit 21 **SENTSTALL:** STALL handshake transmission status bit (Device mode)

- 1 = STALL handshake is transmitted. The FIFO is flushed and the TXPKTRDY bit is cleared.

- 0 = Written by software to clear this bit

#### **RXSTALL:** STALL receipt bit (Host mode)

- 1 = STALL handshake is received. Any DMA request in progress is stopped, the FIFO is completely flushed and the TXPKTRDY bit is cleared.

- 0 = Written by software to clear this bit

- bit 20 SENDSTALL: STALL handshake transmission control bit (Device mode)

- 1 = Issue a STALL handshake to an IN token

- 0 = Terminate stall condition

This bit has no effect when the endpoint is being used for Isochronous transfers.

#### SETUPPKT: Definition bit (Host mode)

- 1 = When set at the same time as the TXPKTRDY bit is set, send a SETUP token instead of an OUT token for the transaction. This also clears the Data Toggle.

- 0 = Normal OUT token for the transaction

- bit 19 **FLUSH:** FIFO Flush control bit

- 1 = Flush the latest packet from the endpoint TX FIFO. The FIFO pointer is reset, TXPKTRDY is cleared and an interrupt is generated.

- 0 = Do not flush the FIFO

- bit 18 UNDERRUN: Underrun status bit (Device mode)

- 1 = An IN token has been received when TXPKTRDY is not set.

- 0 = Written by software to clear this bit.

**ERROR:** Handshake failure status bit (Host mode)

- 1 = Three attempts have been made to send a packet and no handshake packet has been received

- 0 = Written by software to clear this bit.

- bit 17 FIFONE: FIFO Not Empty status bit

- 1 = There is at least 1 packet in the TX FIFO

- 0 = TX FIFO is empty

- bit 16 TXPKTRDY: TX Packet Ready Control bit

The software sets this bit after loading a data packet into the FIFO. It is cleared automatically when a data packet has been transmitted. This bit is also automatically cleared prior to loading a second packet into a double-buffered FIFO.

## TABLE 12-11: PORTE REGISTER MAP FOR 100-PIN, 124-PIN, AND 144-PIN DEVICES ONLY

| ess                         |                                 |           |       |       |       |       |                |       |              | В            | its          |              |              |              |              |              |              |              |               |

|-----------------------------|---------------------------------|-----------|-------|-------|-------|-------|----------------|-------|--------------|--------------|--------------|--------------|--------------|--------------|--------------|--------------|--------------|--------------|---------------|

| Virtual Address<br>(BF86_#) | Register<br>Name <sup>(1)</sup> | Bit Range | 31/15 | 30/14 | 29/13 | 28/12 | 27/11          | 26/10 | 25/9         | 24/8         | 23/7         | 22/6         | 21/5         | 20/4         | 19/3         | 18/2         | 17/1         | 16/0         | All<br>Resets |

| 0400                        | ANSELE                          | 31:16     |       | _     |       |       | —              |       | _            | _            |              | _            | —            |              | _            | _            |              | _            | 0000          |

| 0400                        | ANOLLL                          | 15:0      | —     | _     |       |       | —              | _     | ANSE9        | ANSE8        | ANSE7        | ANSE6        | ANSE5        | ANSE4        | _            | _            | —            |              | 03F0          |

| 0410                        | TRISE                           | 31:16     | —     | —     | —     | —     | —              | _     | —            | —            | —            | —            | —            | -            | —            | —            | —            | —            | 0000          |

| 0110                        | HUGE                            | 15:0      | —     | -     | —     | —     | —              | -     | TRISE9       | TRISE8       | TRISE7       | TRISE6       | TRISE5       | TRISE4       | TRISE3       | TRISE2       | TRISE1       | TRISE0       | 03FF          |

| 0420                        | PORTE                           | 31:16     | —     | —     | —     | —     | —              |       | —            | —            | —            | —            | —            |              | —            | —            | —            | —            | 0000          |

| 0.20                        |                                 | 15:0      | —     | —     | —     | —     | —              |       | RE9          | RE8          | RE7          | RE6          | RE5          | RE4          | RE3          | RE2          | RE1          | RE0          | xxxx          |

| 0430                        | LATE                            | 31:16     | —     | —     | —     | —     | —              |       | —            | —            | —            | —            | —            |              | —            | —            | —            | —            | 0000          |

|                             |                                 | 15:0      | —     | _     | —     | —     | —              | _     | LATE9        | LATE8        | LATE7        | LATE6        | LATE5        | LATE4        | LATE3        | LATE2        | LATE1        | LATE0        | XXXX          |

| 0440                        | ODCE                            | 31:16     | _     | _     | —     | —     | —              | —     | —            | —            |              | —            | —            |              | —            | —            | —            | —            | 0000          |

|                             |                                 | 15:0      | —     | _     | —     | —     | _              | —     | ODCE9        | ODCE8        | ODCE7        | ODCE6        | ODCE5        | ODCE4        | ODCE3        | ODCE2        | ODCE1        | ODCE0        | 0000          |

| 0450                        | CNPUE                           | 31:16     | —     | _     | —     | —     | _              | —     | —            | —            | _            | —            | —            | —            | —            | —            | —            | —            | 0000          |

|                             |                                 | 15:0      | _     | _     | —     | _     | _              | _     | CNPUE9       | CNPUE8       | CNPUE7       | CNPUE6       | CNPUE5       | CNPUE4       | CNPUE3       | CNPUE2       | CNPUE1       | CNPUE0       | 0000          |

| 0460                        | CNPDE                           | 31:16     | _     | _     | —     | _     | _              | _     | —            | _            | _            | —            | —            | _            | —            | —            | —            | —            | 0000          |

|                             |                                 | 15:0      | _     | _     | _     | _     | _              |       | CNPDE9       | CNPDE8       | CNPDE7       | CNPDE6       | CNPDE5       | CNPDE4       | CNPDE3       | CNPDE2       | CNPDE1       | CNPDE0       | 0000          |

| 0470                        |                                 | 31:16     | _     | _     | _     | _     | -              | _     |              | _            | _            | _            | _            | _            | _            | _            | _            | _            | 0000          |

| 0470                        | CNCONE                          | 15:0      | ON    | _     | _     | _     | EDGE<br>DETECT | _     | —            | —            | -            | _            | —            | _            | _            | _            | _            | _            | 0000          |

| 0480                        | CNENE                           | 31:16     | —     | -     | —     | —     | —              | -     | —            | —            | —            | _            | —            |              | —            | _            | —            | _            | 0000          |

| 0.00                        | 0.12.12                         | 15:0      | _     | _     | —     | _     | _              | _     | CNENE9       | CNENE8       | CNENE7       | CNENE6       | CNENE5       | CNENE4       | CNENE3       | CNENE2       | CNENE1       | CNENE0       | 0000          |

|                             |                                 | 31:16     | —     | —     | —     | —     | —              |       | —            | —            | —            | —            | —            |              | —            | _            | —            | —            | 0000          |

| 0490                        | CNSTATE                         | 15:0      | _     | -     | —     | —     | —              | _     | CN<br>STATE9 | CN<br>STATE8 | CN<br>STATE7 | CN<br>STATE6 | CN<br>STATE5 | CN<br>STATE4 | CN<br>STATE3 | CN<br>STATE2 | CN<br>STATE1 | CN<br>STATE0 | 0000          |

| 04A0                        | CNNEE                           | 31:16     | _     |       | -     | _     | -              |       | _            |              | -            | I            | -            |              |              |              | _            |              | 0000          |

| 04A0                        | CININEL                         | 15:0      | _     |       |       |       | -              |       | CNNEE9       | CNNEE8       | CNNEE7       | CNNEE6       | CNNEE5       | CNNEE4       | CNNEE3       | CNNEE2       | CNNEE1       | CNNEE0       | 0000          |

| 04B0                        | CNFE                            | 31:16     | _     | _     | —     | _     | _              | _     | —            | _            | _            | -            | _            | -            | _            | -            | _            | -            | 0000          |

| 0400                        |                                 | 15:0      | _     |       | —     | —     | _              |       | CNFE9        | CNFE8        | CNFE7        | CNFE6        | CNFE5        | CNFE4        | CNFE3        | CNFE2        | CNFE1        | CNFE0        | 0000          |

| 04C0                        | SRCON0E                         | 31:16     | —     | _     | —     | —     | —              | _     | —            | —            | —            | _            | —            | —            | _            | _            | —            |              | 0000          |

| 0400                        | SILCONUL                        | 15:0      | _     |       | —     | —     | —              | _     | —            | —            | -            |              | —            | —            | SR0E3        | SR0E2        | SR0E1        | SR0E0        | 0000          |

| 04D0                        | SRCON1E                         | 31:16     | —     | _     | —     | —     | —              | _     | —            | —            | —            | _            | —            | —            | —            | _            | —            | —            | 0000          |

| 0400                        | SILCONTE                        | 15:0      | _     | -     | —     | _     | _              | _     | -            | —            | _            | -            | _            | —            | SR1E3        | SR1E2        | SR1E1        | SR1E0        | 0000          |

Legend:

x = Unknown value on Reset; — = Unimplemented, read as '0'; Reset values are shown in hexadecimal. All registers in this table have corresponding CLR, SET and INV registers at its virtual address, plus an offset of 0x4, 0x8 and 0xC, respectively. See Section 12.3 "CLR, SET, and INV Registers" for Note 1: more information.

## TABLE 12-15: PORTG REGISTER MAP FOR 100-PIN, 124-PIN, AND 144-PIN DEVICES ONLY

| ess                         |                                 |               |               |               |               |               |                |       |              | Bits         | 5            |              |      |      |      |      |              |              |               |

|-----------------------------|---------------------------------|---------------|---------------|---------------|---------------|---------------|----------------|-------|--------------|--------------|--------------|--------------|------|------|------|------|--------------|--------------|---------------|

| Virtual Address<br>(BF86_#) | Register<br>Name <sup>(1)</sup> | Bit Range     | 31/15         | 30/14         | 29/13         | 28/12         | 27/11          | 26/10 | 25/9         | 24/8         | 23/7         | 22/6         | 21/5 | 20/4 | 19/3 | 18/2 | 17/1         | 16/0         | All<br>Resets |

| 0600                        | ANSELG                          | 31:16         |               |               | —             |               |                | _     | —            | —            | _            | —            | —    |      |      | —    |              |              | 0000          |

|                             |                                 | 15:0          | ANSG15        | _             | —             | —             | —              | _     | ANSG9        | ANSG8        | ANSG7        | ANSG6        | —    | _    | _    | —    |              | —            | 83C0          |

| 0610                        | TRISG                           | 31:16         | -             | -             | —             | -             |                |       | -            | -            | -            | -            | _    | _    |      |      | -            | -            | 0000          |

|                             |                                 | 15:0          | TRISG15       | TRISG14       | TRISG13       | TRISG12       |                |       | TRISG9       | TRISG8       | TRISG7       | TRISG6       | _    |      |      |      | TRISG1       | TRISG0       | F3C3          |

| 0620                        | PORTG                           | 31:16<br>15:0 | <br>RG15      | —<br>RG14     | —<br>RG13     | —<br>RG12     |                |       | RG9          | RG8          | RG7          | RG6          | _    |      | _    |      | RG1          | RG0          | 0000          |

|                             |                                 | 31:16         | RGIS          | RG14          | RGI3          | RGIZ          |                |       | KG9          | KG8          | KG7          | RG0          |      |      |      |      |              | RGU          | xxxx<br>0000  |

| 0630                        | LATG                            | 15:0          | LATG15        | LATG14        | LATG13        | LATG12        |                |       | LATG9        | LATG8        | LATG7        | LATG6        |      |      |      |      | LATG1        | LATG0        |               |

|                             |                                 | 31:16         |               |               |               |               |                |       |              | -            | _            |              |      |      | _    | _    |              |              | xxxx<br>0000  |

| 0640                        | ODCG                            | 15:0          | ODCG15        | ODCG14        | ODCG13        | ODCG12        |                |       | ODCG9        | ODCG8        | ODCG7        | ODCG6        | _    | _    |      | _    | ODCG1        | ODCG0        | 0000          |

|                             |                                 | 31:16         | _             | _             | _             | _             | _              | _     | _            | _            | _            | _            | _    | _    | _    |      | _            | _            | 0000          |

| 0650                        | CNPUG                           | 15:0          | CNPUG15       | CNPUG14       | CNPUG13       | CNPUG12       | _              | _     | CNPUG9       | CNPUG8       | CNPUG7       | CNPUG6       | _    | _    | _    | _    | CNPUG1       | CNPUG0       | 0000          |

|                             | 01/22.0                         | 31:16         | _             | _             | _             | _             | _              | _     | _            | _            | _            | _            | _    | _    | _    | _    | _            | _            | 0000          |

| 0660                        | CNPDG                           | 15:0          | CNPDG15       | CNPDG14       | CNPDG13       | CNPDG12       | _              | _     | CNPDG9       | CNPDG8       | CNPDG7       | CNPDG6       | _    | _    | _    | _    | CNPDG1       | CNPDG0       | 0000          |

|                             |                                 | 31:16         |               | —             | —             | —             | —              | _     | —            | —            |              | —            | _    | _    |      |      | —            | —            | 0000          |

| 0670                        | CNCONG                          | 15:0          | ON            | _             | _             | _             | EDGE<br>DETECT | _     | _            | _            | _            | -            |      | _    | _    | _    | _            | _            | 0000          |

| 0680                        | CNENG                           | 31:16         |               | —             | —             | —             | —              | _     | —            | —            |              | —            | _    | _    |      |      | —            | _            | 0000          |

| 0000                        | CINEING                         | 15:0          | CNENG15       | CNENG14       | CNENG13       | CNENG12       | —              | _     | CNENG9       | CNENG8       | CNENG7       | CNENG6       | _    |      | -    | _    | CNENG1       | CNENG0       | 0000          |

|                             |                                 | 31:16         | —             | —             | —             | —             | —              |       | —            | —            | -            | —            | _    | -    |      | —    | —            | —            | 0000          |

| 0690                        | CNSTATG                         | 15:0          | CN<br>STATG15 | CN<br>STATG14 | CN<br>STATG13 | CN<br>STATG12 | —              | —     | CN<br>STATG9 | CN<br>STATG8 | CN<br>STATG7 | CN<br>STATG6 | —    | —    | —    | —    | CN<br>STATG1 | CN<br>STATG0 | 0000          |

| 06A0                        | CNNEG                           | 31:16         | _             | —             | —             | _             | —              | _     | —            | —            |              | —            | _    |      |      | _    | _            | _            | 0000          |

| UUAU                        | CININEG                         | 15:0          | CNNEG15       | CNNEG14       | CNNEG13       | CNNEG12       | _              |       | CNNEG9       | CNNEG8       | CNNEG7       | CNNEG6       | -    |      |      | _    | CNNEG1       | CNNEG0       | 0000          |

| 06B0                        | CNFG                            | 31:16         |               | —             |               | —             | —              | _     |              |              | _            | —            | —    | _    | _    | —    | _            |              | 0000          |

| 0020                        |                                 | 15:0          | CNFG15        | CNFG14        | CNFG13        | CNFG12        | _              | _     | CNFG9        | CNFG8        | CNFG7        | CNFG6        | —    | _    | _    | —    | CNFG1        | CNFG0        | 0000          |

| 06C0                        | SRCON0G                         | 31:16         | —             | —             | —             | —             | —              |       | —            | —            |              | —            | —    | —    |      | —    |              | —            | 0000          |

| 5000                        |                                 | 15:0          | _             | SR0G14        | SR0G13        | SR0G12        |                |       | SR0G9        |              |              | SR0G6        | _    | _    | _    | —    |              |              | 0000          |

| 06D0                        | SRCON1G                         | 31:16         | _             | —             | —             | —             |                | _     | —            | _            |              | -            | —    | _    | _    |      |              |              | 0000          |

|                             |                                 | 15:0          | —             | SR1G14        | SR1G13        | SR1G12        | _              | —     | SR1G9        | —            | —            | SR1G6        | —    | —    | —    | —    | —            | —            | 0000          |

PIC32MZ Embedded Connectivity with Floating Point Unit (EF) Family

Legend:

x = Unknown value on Reset; — = Unimplemented, read as '0'; Reset values are shown in hexadecimal. All registers in this table have corresponding CLR, SET and INV registers at its virtual address, plus an offset of 0x4, 0x8, and 0xC, respectively. See Section 12.3 "CLR, SET, and INV Registers" for Note 1: more information.

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|

| 24.24        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 31:24        | -                 | _                 | _                 | —                 | _                 |                   | _                | _                |

| 22.16        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 23:16        | -                 | _                 | —                 | —                 | _                 |                   | -                | _                |

| 15:8         | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 10.0         |                   | -                 |                   | —                 | _                 |                   |                  | _                |

| 7.0          | U-0               | U-0               | U-0               | U-0               | R/W-0             | R/W-0             | R/W-0            | R/W-0            |

| 7:0          | _                 | _                 | _                 | _                 |                   | [pin name         | e]R<3:0>         |                  |

#### **REGISTER 12-1:** [pin name]R: PERIPHERAL PIN SELECT INPUT REGISTER

#### Legend:

| R = Readable bit  | W = Writable bit | U = Unimplemented    | bit, read as '0'   |  |

|-------------------|------------------|----------------------|--------------------|--|

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared | x = Bit is unknown |  |

#### bit 31-4 Unimplemented: Read as '0'

bit 3-0 [*pin name*]R<3:0>: Peripheral Pin Select Input bits Where [*pin name*] refers to the pins that are used to configure peripheral input mapping. See Table 12-2 for input pin selection values.

**Note:** Register values can only be changed if the IOLOCK Configuration bit (CFGCON<13>) = 0.

#### REGISTER 12-2: RPnR: PERIPHERAL PIN SELECT OUTPUT REGISTER

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|

| 04.04        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 31:24        | —                 | _                 | _                 | _                 | _                 |                   | -                | —                |

| 23:16        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 23.10        | —                 | -                 | -                 |                   | _                 |                   |                  | —                |

| 45.0         | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 15:8         | —                 | _                 | _                 | _                 | _                 |                   | _                | —                |

| 7.0          | U-0               | U-0               | U-0               | U-0               | R/W-0             | R/W-0             | R/W-0            | R/W-0            |

| 7:0          |                   | _                 |                   |                   |                   | RPnR              | <3:0>            |                  |

## Legend:

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, re | ad as '0'          |

|-------------------|------------------|---------------------------|--------------------|

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared      | x = Bit is unknown |

bit 31-4 Unimplemented: Read as '0'

bit 3-0 **RPnR<3:0>:** Peripheral Pin Select Output bits See Table 12-3 for output pin selection values.

**Note:** Register values can only be changed if the IOLOCK Configuration bit (CFGCON<13>) = 0.

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|

| 31:24        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 31.24        | _                 | _                 |                   | —                 |                   |                   | _                | _                |

| 22.46        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 23:16        | —                 | _                 |                   | —                 | _                 |                   | _                | _                |

| 45.0         | U-0               | U-0               | U-0               | U-0               | R/W-0             | R/W-0             | R/W-0            | R/W-0            |

| 15:8         | —                 | —                 | —                 | —                 | DMAEIE            | PKTCOMPIE         | BDDONEIE         | CONTHRIE         |

| 7.0          | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |

| 7:0          | CONEMPTYIE        | CONFULLIE         | RXTHRIE           | RXFULLIE          | RXEMPTYIE         | TXTHRIE           | TXFULLIE         | TXEMPTYIE        |

U = Unimplemented bit, read as '0'

x = Bit is unknown

'0' = Bit is cleared

HS = Hardware Set

W = Writable bit

'1' = Bit is set

## REGISTER 20-8: SQI1INTEN: SQI INTERRUPT ENABLE REGISTER

| bit 31-12     | <b>Unimplemented:</b> Read as '0'                                     |

|---------------|-----------------------------------------------------------------------|

| bit 11        | DMAEIE: DMA Bus Error Interrupt Enable bit                            |

|               | 1 = Interrupt is enabled                                              |

|               | 0 = Interrupt is disabled                                             |

| bit 10        | PKTCOMPIE: DMA Buffer Descriptor Packet Complete Interrupt Enable bit |

|               | 1 = Interrupt is enabled                                              |

|               | 0 = Interrupt is disabled                                             |

| bit 9         | BDDONEIE: DMA Buffer Descriptor Done Interrupt Enable bit             |

|               | 1 = Interrupt is enabled                                              |

|               | 0 = Interrupt is disabled                                             |

| bit 8         | CONTHRIE: Control Buffer Threshold Interrupt Enable bit               |