Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFI

| Product Status             | Active                                                                           |

|----------------------------|----------------------------------------------------------------------------------|

| Core Processor             | MIPS32® M-Class                                                                  |

| Core Size                  | 32-Bit Single-Core                                                               |

| Speed                      | 180MHz                                                                           |

| Connectivity               | CANbus, EBI/EMI, Ethernet, I <sup>2</sup> C, PMP, SPI, SQI, UART/USART, USB OTG  |

| Peripherals                | Brown-out Detect/Reset, DMA, I <sup>2</sup> S, POR, PWM, WDT                     |

| Number of I/O              | 78                                                                               |

| Program Memory Size        | 512KB (512K x 8)                                                                 |

| Program Memory Type        | FLASH                                                                            |

| EEPROM Size                | -                                                                                |

| RAM Size                   | 128K x 8                                                                         |

| Voltage - Supply (Vcc/Vdd) | 2.1V ~ 3.6V                                                                      |

| Data Converters            | A/D 40x12b                                                                       |

| Oscillator Type            | Internal                                                                         |

| Operating Temperature      | -40°C ~ 125°C                                                                    |

| Mounting Type              | Surface Mount                                                                    |

| Package / Case             | 100-TQFP                                                                         |

| Supplier Device Package    | 100-TQFP (12x12)                                                                 |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic32mz0512eff100-e-pt |

|                            |                                                                                  |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

|                 |                        | Pin Nu          | mber            |                          |             |                |                                   |

|-----------------|------------------------|-----------------|-----------------|--------------------------|-------------|----------------|-----------------------------------|

| Pin Name        | 64-pin<br>QFN/<br>TQFP | 100-pin<br>TQFP | 124-pin<br>VTLA | 144-pin<br>TQFP/<br>LQFP | Pin<br>Type | Buffer<br>Type | Description                       |

|                 |                        |                 | •               |                          | PO          | RTA            | ·                                 |

| RA0             | _                      | 17              | A11             | 22                       | I/O         | ST             | PORTA is a bidirectional I/O port |

| RA1             | —                      | 38              | B21             | 56                       | I/O         | ST             |                                   |

| RA2             | —                      | 59              | A41             | 85                       | I/O         | ST             |                                   |

| RA3             | —                      | 60              | B34             | 86                       | I/O         | ST             |                                   |

| RA4             | —                      | 61              | A42             | 87                       | I/O         | ST             |                                   |

| RA5             | —                      | 2               | B1              | 2                        | I/O         | ST             |                                   |

| RA6             | —                      | 89              | A61             | 129                      | I/O         | ST             |                                   |

| RA7             | —                      | 90              | B51             | 130                      | I/O         | ST             |                                   |

| RA9             | —                      | 28              | B15             | 39                       | I/O         | ST             |                                   |

| RA10            | _                      | 29              | A20             | 40                       | I/O         | ST             | ]                                 |

| RA14            | _                      | 66              | B37             | 95                       | I/O         | ST             |                                   |

| RA15            | _                      | 67              | A45             | 96                       | I/O         | ST             |                                   |

|                 |                        |                 |                 |                          | PO          | RTB            |                                   |

| RB0             | 16                     | 25              | A18             | 36                       | I/O         | ST             | PORTB is a bidirectional I/O port |

| RB1             | 15                     | 24              | A17             | 35                       | I/O         | ST             |                                   |

| RB2             | 14                     | 23              | A16             | 34                       | I/O         | ST             |                                   |

| RB3             | 13                     | 22              | A14             | 31                       | I/O         | ST             |                                   |

| RB4             | 12                     | 21              | A13             | 26                       | I/O         | ST             |                                   |

| RB5             | 11                     | 20              | B11             | 25                       | I/O         | ST             |                                   |

| RB6             | 17                     | 26              | B14             | 37                       | I/O         | ST             |                                   |

| RB7             | 18                     | 27              | A19             | 38                       | I/O         | ST             |                                   |

| RB8             | 21                     | 32              | B18             | 47                       | I/O         | ST             |                                   |

| RB9             | 22                     | 33              | A23             | 48                       | I/O         | ST             |                                   |

| RB10            | 23                     | 34              | B19             | 49                       | I/O         | ST             | _                                 |

| RB11            | 24                     | 35              | A24             | 50                       | I/O         | ST             | _                                 |

| RB12            | 27                     | 41              | A27             | 59                       | I/O         | ST             | _                                 |

| RB13            | 28                     | 42              | B23             | 60                       | I/O         | ST             | -                                 |

| RB14            | 29                     | 43              | A28             | 61                       | I/O         | ST             | -                                 |

| RB15            | 30                     | 44              | B24             | 62                       | I/O         | ST             |                                   |

| <b>D</b> O1     |                        | -               |                 |                          |             | RTC            |                                   |

| RC1             | —                      | 6               | B3              | 6                        | I/O         | ST             | PORTC is a bidirectional I/O port |

| RC2             |                        | 7               | A6              | 11                       | I/O         | ST             | 4                                 |

| RC3             |                        | 8               | B5              | 12                       | I/O         | ST             | 4                                 |

| RC4             | -                      | 9               | A7              | 13                       | I/O         | ST             | 4                                 |

| RC12            | 31                     | 49              | B28             | 71                       | I/O         | ST             | 4                                 |

| RC13            | 47                     | 72              | B41             | 105                      | I/O         | ST             | 4                                 |

| RC14            | 48                     | 73              | A49             | 106                      | I/O         | ST             | 4                                 |

| RC15<br>Legend: | 32                     | 50<br>MOS-comp  | A33             | 72                       | I/O         | ST             | Analog input P = Power            |

#### **TABLE 1-6:** PORTA THROUGH PORTK PINOUT I/O DESCRIPTIONS

ST = Schmitt Trigger input with CMOS levels TTL = Transistor-transistor Logic input buffer

O = Output PPS = Peripheral Pin Select I = Input

|                            |                        | Pin Nu          | mber            |                          |             |                |                                            |  |

|----------------------------|------------------------|-----------------|-----------------|--------------------------|-------------|----------------|--------------------------------------------|--|

| Pin Name                   | 64-pin<br>QFN/<br>TQFP | 100-pin<br>TQFP | 124-pin<br>VTLA | 144-pin<br>TQFP/<br>LQFP | Pin<br>Type | Buffer<br>Type | Description                                |  |

|                            |                        |                 |                 | Inte                     | er-Integr   | ated Circui    | t 1                                        |  |

| SCL1                       | 44                     | 66              | B37             | 95                       | I/O         | ST             | I2C1 Synchronous Serial Clock Input/Output |  |

| SDA1                       | 43                     | 67              | A45             | 96                       | I/O         | ST             | I2C1 Synchronous Serial Data Input/Output  |  |

|                            |                        |                 |                 | Inte                     | er-Integr   | ated Circui    | t 2                                        |  |

| SCL2                       | —                      | 59              | A41             | 85                       | I/O         | ST             | I2C2 Synchronous Serial Clock Input/Output |  |

| SDA2                       | —                      | 60              | B34             | 86                       | I/O         | ST             | I2C2 Synchronous Serial Data Input/Output  |  |

|                            |                        |                 |                 | Inte                     | er-Integr   | ated Circui    | t 3                                        |  |

| SCL3                       | 51                     | 58              | A39             | 80                       | I/O         | ST             | I2C3 Synchronous Serial Clock Input/Output |  |

| SDA3                       | 50                     | 57              | B31             | 79                       | I/O         | ST             | I2C3 Synchronous Serial Data Input/Output  |  |

|                            |                        | •               | •               | Inte                     | er-Integr   | ated Circui    | t 4                                        |  |

| SCL4                       | 6                      | 12              | B7              | 16                       | I/O         | ST             | I2C4 Synchronous Serial Clock Input/Output |  |

| SDA4                       | 5                      | 11              | A8              | 15                       | I/O         | ST             | I2C4 Synchronous Serial Data Input/Output  |  |

| Inter-Integrated Circuit 5 |                        |                 |                 |                          |             |                |                                            |  |

| SCL5                       | 42                     | 65              | A44             | 91                       | I/O         | ST             | I2C5 Synchronous Serial Clock Input/Output |  |

| SDA5                       | 41                     | 64              | B36             | 90                       | I/O         | ST             | I2C5 Synchronous Serial Data Input/Output  |  |

| Legend:                    | CMOS = CI              | MOS-comp        | atible input    | or output                |             | Analog =       | Analog input P = Power                     |  |

#### TABLE 1-10: I2C1 THROUGH I2C5 PINOUT I/O DESCRIPTIONS

end: CMOS = CMOS-compatible input or output ST = Schmitt Trigger input with CMOS levels TTL = Transistor-transistor Logic input buffer

O = Output

PPS = Peripheral Pin Select

### TABLE 1-11: COMPARATOR 1, COMPARATOR 2 AND CVREF PINOUT I/O DESCRIPTIONS

|                                                                                                                  |                        | Pin Nu          | mber            |                          |             |                |                                           |

|------------------------------------------------------------------------------------------------------------------|------------------------|-----------------|-----------------|--------------------------|-------------|----------------|-------------------------------------------|

| Pin Name                                                                                                         | 64-pin<br>QFN/<br>TQFP | 100-pin<br>TQFP | 124-pin<br>VTLA | 144-pin<br>TQFP/<br>LQFP | Pin<br>Type | Buffer<br>Type | Description                               |

|                                                                                                                  |                        |                 |                 | Comp                     | arator Vo   | oltage Refe    | rence                                     |

| CVREF+                                                                                                           | 16                     | 29              | A20             | 40                       | Ι           | Analog         | Comparator Voltage Reference (High) Input |

| CVREF-                                                                                                           | 15                     | 28              | B15             | 39                       | I           | Analog         | Comparator Voltage Reference (Low) Input  |

| CVREFOUT                                                                                                         | 23                     | 34              | B19             | 49                       | 0           | Analog         | Comparator Voltage Reference Output       |

|                                                                                                                  | Comparator 1           |                 |                 |                          |             |                |                                           |

| C1INA                                                                                                            | 11                     | 20              | B11             | 25                       | Ι           | Analog         | Comparator 1 Positive Input               |

| C1INB                                                                                                            | 12                     | 21              | A13             | 26                       | I           | Analog         | Comparator 1 Selectable Negative Input    |

| C1INC                                                                                                            | 5                      | 11              | A8              | 15                       | I           | Analog         |                                           |

| C1IND                                                                                                            | 4                      | 10              | B6              | 14                       | I           | Analog         |                                           |

| C1OUT                                                                                                            | PPS                    | PPS             | PPS             | PPS                      | 0           | _              | Comparator 1 Output                       |

|                                                                                                                  | •                      |                 | •               | •                        | Comp        | arator 2       | ·                                         |

| C2INA                                                                                                            | 13                     | 22              | A14             | 31                       | I           | Analog         | Comparator 2 Positive Input               |

| C2INB                                                                                                            | 14                     | 23              | A16             | 34                       | I           | Analog         | Comparator 2 Selectable Negative Input    |

| C2INC                                                                                                            | 10                     | 16              | B9              | 21                       | I           | Analog         | ]                                         |

| C2IND                                                                                                            | 6                      | 12              | B7              | 16                       | I           | Analog         | ]                                         |

| C2OUT                                                                                                            | PPS                    | PPS             | PPS             | PPS                      | 0           | —              | Comparator 2 Output                       |

| Legend:                                                                                                          |                        | •               | •               | •                        |             | 0              | Analog input P = Power                    |

| C2IND         6         12         B7         16           C2OUT         PPS         PPS         PPS         PPS |                        |                 |                 |                          |             | Analog<br>—    | Analog input P = Power                    |

TTL = Transistor-transistor Logic input buffer

O = Output PPS = Peripheral Pin Select I = Input

#### **TABLE 7-3: INTERRUPT REGISTER MAP (CONTINUED)**

| ress<br>f)                  | <b>N</b> -1                     | e         |       |       |       |       |       |       |      | Bi         | ts   |      |      |      |      |      |       |        | Ś          |

|-----------------------------|---------------------------------|-----------|-------|-------|-------|-------|-------|-------|------|------------|------|------|------|------|------|------|-------|--------|------------|

| Virtual Address<br>(BF81_#) | Register<br>Name <sup>(1)</sup> | Bit Range | 31/15 | 30/14 | 29/13 | 28/12 | 27/11 | 26/10 | 25/9 | 24/8       | 23/7 | 22/6 | 21/5 | 20/4 | 19/3 | 18/2 | 17/1  | 16/0   | All Resets |

|                             | 055400                          | 31:16     | _     |       | _     | _     | _     | —     | —    | _          | _    | -    | _    | -    | _    | —    | VOFF< | 17:16> | 000        |

| 0768 (                      | OFF138                          | 15:0      |       |       |       |       |       | •     | •    | VOFF<15:1> |      |      |      | •    |      | •    |       | —      | 000        |

| 0760                        | OFF139                          | 31:16     | _     | _     | _     | —     | —     | —     | —    | _          | _    | _    | _    | -    | _    | —    | VOFF< | 17:16> | 000        |

| 07600                       | JFF 139                         | 15:0      |       |       |       |       |       |       |      | VOFF<15:1> |      |      |      |      |      |      |       | —      | 000        |

| 0770                        | OFF140                          | 31:16     | _     | _     | _     | _     |       | —     | —    | _          | _    | -    | _    | —    | _    | _    | VOFF< | 17:16> | 000        |

| 0//0                        | 011140                          | 15:0      |       |       |       |       |       |       |      | VOFF<15:1> |      |      |      |      |      |      |       | —      | 000        |

| 0774                        | OFF141                          | 31:16     | —     | _     | —     | —     | —     | —     | —    | —          | —    | —    | —    | —    | —    | _    | VOFF< | 17:16> | 000        |

| 0//4                        | 011141                          | 15:0      |       |       |       |       |       |       |      | VOFF<15:1> |      |      |      |      |      |      |       | —      | 000        |

| 0778                        | OFF142                          | 31:16     | —     | —     | —     | —     | —     |       | _    | —          | —    | —    | —    | —    | —    |      | VOFF< | 17:16> | 0000       |

| 0110                        | 011142                          | 15:0      |       |       | i     |       |       | i     | i    | VOFF<15:1> |      |      | i    |      | i    | i    | i     | —      | 0000       |

| 077C                        | OFF143                          | 31:16     | —     | —     | —     | —     | —     | —     | —    | —          | —    | —    | —    | —    | —    | _    | VOFF< | 17:16> | 0000       |

| 00                          | 011110                          | 15:0      |       |       |       |       |       |       |      | VOFF<15:1> |      |      |      |      |      |      | 1     | —      | 0000       |

| 0780                        | OFF144                          | 31:16     | —     | —     | —     | —     | —     | —     | —    | —          | —    | —    | —    | -    | —    | —    | VOFF< | 17:16> | 0000       |

|                             |                                 | 15:0      |       |       |       |       |       |       |      | VOFF<15:1> |      |      |      |      |      |      | 1     |        | 0000       |

| 0784                        | OFF145                          | 31:16     | —     | _     | —     | —     | —     | —     | —    | —          | _    | —    | —    | —    | —    | _    | VOFF< | 17:16> | 0000       |

|                             |                                 | 15:0      |       |       |       |       |       |       |      | VOFF<15:1> |      |      |      |      |      |      | 1     | —      | 0000       |

| 0788                        | OFF146                          | 31:16     | —     | _     | —     | —     | —     | —     | —    | —          | _    | —    | —    | —    | —    | _    | VOFF< | 17:16> | 0000       |

|                             |                                 | 15:0      |       |       |       |       |       |       |      | VOFF<15:1> |      |      |      |      |      |      | 1     | —      | 0000       |

| 078C                        | OFF147                          | 31:16     | —     | —     | —     | —     | —     | —     | —    |            | —    | —    | —    | —    | —    | —    | VOFF< | 17:16> | 0000       |

|                             | -                               | 15:0      |       |       |       |       |       |       |      | VOFF<15:1> |      |      |      | -    |      |      |       | —      | 0000       |

| 0790                        | OFF148 <sup>(2)</sup>           | 31:16     | —     | —     | —     | —     | —     | —     | —    |            | —    | —    | —    | —    | —    | —    | VOFF< | 17:16> | 0000       |

|                             |                                 | 15:0      |       |       |       |       |       |       |      | VOFF<15:1> |      |      |      | -    |      |      |       | —      | 0000       |

| 0794                        | OFF149 <sup>(2)</sup>           | 31:16     | —     | _     | —     | —     | —     | —     | —    | —          | —    | —    | —    | —    | —    | —    | VOFF< | 17:16> | 0000       |

|                             | -                               | 15:0      |       |       |       |       |       |       |      | VOFF<15:1> |      |      |      |      |      |      |       | —      | 0000       |

| 0798                        | OFF150 <sup>(2)</sup>           | 31:16     | —     |       | —     | —     | —     | —     | —    | —          | —    | —    | —    | —    | —    | —    | VOFF< |        | 0000       |

|                             |                                 | 15:0      |       |       |       |       |       |       |      | VOFF<15:1> |      |      |      |      |      |      |       | —      | 0000       |

| 079C                        | OFF151 <sup>(3)</sup>           | 31:16     | —     | —     | —     | —     | -     | —     | —    | —          | —    | —    | —    | —    | —    | —    | VOFF< |        | 0000       |

|                             | -                               | 15:0      |       |       |       |       |       |       |      | VOFF<15:1> |      |      |      |      |      |      |       | —      | 0000       |

| 07A0 (                      | OFF152 <sup>(3)</sup>           | 31:16     | —     | —     | —     | —     | —     | —     | —    | —          | —    | —    | —    | —    | —    | —    | VOFF< | 17:16> | 0000       |

|                             |                                 | 15:0      |       |       |       |       |       |       |      | VOFF<15:1> |      |      |      |      |      |      |       | —      | 0000       |

DS60001320D-page 140

All registers in this table with the exception of the OFFx registers, have corresponding CLR, SET, and INV registers at their virtual addresses, plus offsets of 0x4, 0x8 and 0xC, respectively. See Section 12.3 "CLR, SET, and INV Note 1: **Registers**" for more information. This bit or register is not available on 64-pin devices.

2:

3: This bit or register is not available on devices without a CAN module.

4: This bit or register is not available on 100-pin devices.

5: Bits 31 and 30 are not available on 64-pin and 100-pin devices; bits 29 through 14 are not available on 64-pin devices.

6: Bits 31, 30, 29, and bits 5 through 0 are not available on 64-pin and 100-pin devices; bit 31 is not available on 124-pin devices; bit 22 is not available on 64-pin devices.

7: This bit or register is not available on devices without a Crypto module.

This bit or register is not available on 124-pin devices. 8:

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|

| 24.24        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 31:24        | —                 |                   |                   |                   | _                 |                   |                  | —                |

| 22.46        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 23:16        | —                 | _                 | _                 | _                 | _                 | _                 | _                | —                |

| 45.0         | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |

| 15:8         |                   |                   |                   | CHSSIZ            | <15:8>            |                   |                  |                  |

| 7.0          | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |

| 7:0          |                   |                   |                   | CHSSIZ            | <7:0>             |                   |                  |                  |

#### REGISTER 10-12: DCHxSSIZ: DMA CHANNEL x SOURCE SIZE REGISTER

# Legend:

| Legena.           |                  |                          |                    |

|-------------------|------------------|--------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, r | read as '0'        |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared     | x = Bit is unknown |

#### bit 31-16 Unimplemented: Read as '0'

bit 15-0 CHSSIZ<15:0>: Channel Source Size bits

1111111111111111 = 65,535 byte source size

#### **REGISTER 10-13: DCHxDSIZ: DMA CHANNEL x DESTINATION SIZE REGISTER**

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|

| 31:24        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 31.24        | —                 | _                 | _                 | _                 | _                 | _                 | _                | —                |

| 00.40        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 23:16        | —                 |                   | —                 | —                 | _                 | —                 |                  | —                |

| 45.0         | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |

| 15:8         |                   |                   |                   | CHDSIZ            | <15:8>            |                   |                  |                  |

| 7.0          | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |

| 7:0          |                   |                   |                   | CHDSIZ            | <7:0>             |                   |                  |                  |

| Legend:           |                  |                          |                    |

|-------------------|------------------|--------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, r | ead as '0'         |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared     | x = Bit is unknown |

bit 15-0 **CHDSIZ<15:0>:** Channel Destination Size bits

111111111111111 = 65,535 byte destination size  $\ensuremath{\cdot}$

NOTES:

|          |                  |               |       |                                        |       |       |       |       | n    |               | Bits          |           | •    | •    |      |      |      |      |

|----------|------------------|---------------|-------|----------------------------------------|-------|-------|-------|-------|------|---------------|---------------|-----------|------|------|------|------|------|------|

| (BF8E_#) | Register<br>Name | Bit Range     | 31/15 | 30/14                                  | 29/13 | 28/12 | 27/11 | 26/10 | 25/9 | 24/8          | 23/7          | 22/6      | 21/5 | 20/4 | 19/3 | 18/2 | 17/1 | 16/0 |

| 28       | USB<br>E2CSR2    | 31:16<br>15:0 |       | •                                      |       | •     | •     |       | Inde | exed by the s | ame bits in U | SBIE2CSR2 | ·    | ·    |      |      | •    |      |

| 2C       | USB<br>E2CSR3    | 31:16<br>15:0 |       | Indexed by the same bits in USBIE2CSR3 |       |       |       |       |      |               |               |           |      |      |      |      |      |      |

| 30       | USB<br>E3CSR0    | 31:16<br>15:0 |       | Indexed by the same bits in USBIE3CSR0 |       |       |       |       |      |               |               |           |      |      |      |      |      |      |

| 34       | USB<br>E3CSR1    | 31:16<br>15:0 |       |                                        |       |       |       |       | Inde | exed by the s | ame bits in U | SBIE3CSR1 |      |      |      |      |      |      |

| 8        | USB<br>E3CSR2    | 31:16<br>15:0 |       |                                        |       |       |       |       | Inde | exed by the s | ame bits in U | SBIE3CSR2 |      |      |      |      |      |      |

| С        | USB<br>E3CSR3    | 31:16<br>15:0 |       |                                        |       |       |       |       | Inde | exed by the s | ame bits in U | SBIE3CSR3 |      |      |      |      |      |      |

| )        | USB<br>E4CSR0    | 31:16<br>15:0 |       |                                        |       |       |       |       | Inde | exed by the s | ame bits in U | SBIE4CSR0 |      |      |      |      |      |      |

| 4        | USB<br>E4CSR1    | 31:16<br>15:0 |       |                                        |       |       |       |       | Inde | exed by the s | ame bits in U | SBIE4CSR1 |      |      |      |      |      |      |

| 3        | USB<br>E4CSR2    | 31:16<br>15:0 |       |                                        |       |       |       |       | Inde | exed by the s | ame bits in U | SBIE4CSR2 |      |      |      |      |      |      |

| 2        | USB<br>E4CSR3    | 31:16<br>15:0 |       |                                        |       |       |       |       | Inde | exed by the s | ame bits in U | SBIE4CSR3 |      |      |      |      |      |      |

| )        | USB<br>E5CSR0    | 31:16<br>15:0 |       |                                        |       |       |       |       | Inde | exed by the s | ame bits in U | SBIE5CSR0 |      |      |      |      |      |      |

| 4        | USB<br>E5CSR1    | 31:16<br>15:0 |       |                                        |       |       |       |       | Inde | exed by the s | ame bits in U | SBIE5CSR1 |      |      |      |      |      |      |

| в        | USB<br>E5CSR2    | 31:16<br>15:0 |       |                                        |       |       |       |       | Inde | exed by the s | ame bits in U | SBIE5CSR2 |      |      |      |      |      |      |

| С        | USB<br>E5CSR3    | 31:16<br>15:0 |       |                                        |       |       |       |       | Inde | exed by the s | ame bits in U | SBIE5CSR3 |      |      |      |      |      |      |

| 0        | USB<br>E6CSR0    | 31:16<br>15:0 |       |                                        |       |       |       |       | Inde | exed by the s | ame bits in U | SBIE6CSR0 |      |      |      |      |      |      |

| 4        | USB<br>E6CSR1    | 31:16<br>15:0 |       |                                        |       |       |       |       | Inde | exed by the s | ame bits in U | SBIE6CSR1 |      |      |      |      |      |      |

| 3        | USB<br>E6CSR2    | 31:16<br>15:0 |       |                                        |       |       |       |       | Inde | exed by the s | ame bits in U | SBIE6CSR2 |      |      |      |      |      |      |

| С        | USB<br>E6CSR3    | 31:16<br>15:0 |       |                                        |       |       |       |       | Inde | exed by the s | ame bits in U | SBIE6CSR3 |      |      |      |      |      |      |

1: 2: 3: 4:

Device mode.

Host mode.

Definition for Endpoint 0 (ENDPOINT<3:0> (USBCSR<19:16>) = 0).

Definition for Endpoints 1-7 (ENDPOINT<3:0> (USBCSR<19:16>) = 1 through 7).

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|

| 31:24        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 31.24        |                   | —                 |                   |                   |                   |                   |                  |                  |

| 23:16        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 23.10        | —                 | —                 | —                 | —                 | —                 |                   | —                | —                |

| 15:8         | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 15.0         |                   | —                 |                   |                   |                   |                   |                  |                  |

| 7:0          | R/W-0, HS         | R/W-0, HS        | R/W-0, HS        |

| 7.0          | DMA8IF            | DMA7IF            | DMA6IF            | DMA5IF            | DMA4IF            | DMA3IF            | DMA2IF           | DMA1IF           |

#### REGISTER 11-20: USBDMAINT: USB DMA INTERRUPT REGISTER

#### Legend:

| 3                 |                  |                                    |                    |  |  |  |

|-------------------|------------------|------------------------------------|--------------------|--|--|--|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, read as '0' |                    |  |  |  |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared               | x = Bit is unknown |  |  |  |

bit 31-8 Unimplemented: Read as '0'

bit 7-0 **DMAxIF:** DMA Channel 'x' Interrupt bit

1 = The DMA channel has an interrupt event

0 = No interrupt event

All bits are cleared on a read of the register.

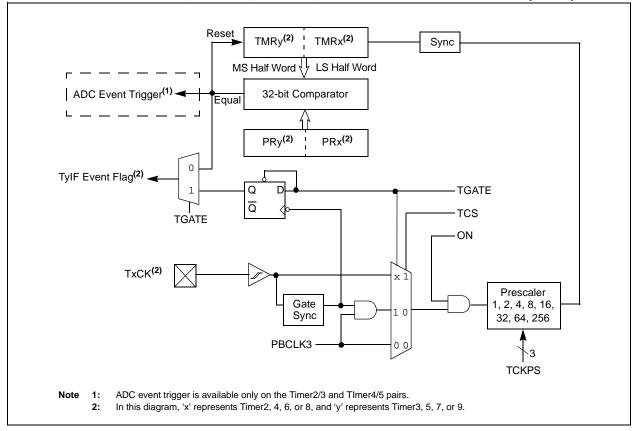

# FIGURE 14-2: TIMER2/3, TIMER4/5, TIMER6/7, AND TIMER8/9 BLOCK DIAGRAM (32-BIT)

| Bit<br>Range | Bit Bit<br>31/23/15/7 30/22/14/6 |                    | Bit<br>29/21/13/5 | Bit<br>28/20/12/4     | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0      |  |  |

|--------------|----------------------------------|--------------------|-------------------|-----------------------|-------------------|-------------------|------------------|-----------------------|--|--|

| 04.04        | R/W-0                            | R/W-0              | R/W-0             | R/W-0                 | R/W-0             | R/W-0             | R/W-0            | R/W-0                 |  |  |

| 31:24        | FRMEN                            | FRMSYNC            | FRMPOL            | MSSEN                 | FRMSYPW           | F                 | RMCNT<2:0        | RMCNT<2:0>            |  |  |

| 00.40        | R/W-0                            | U-0                | U-0               | U-0                   | U-0               | U-0               | R/W-0            | R/W-0                 |  |  |

| 23:16        | MCLKSEL <sup>(1)</sup>           | _                  |                   | —                     | _                 | _                 | SPIFE            | ENHBUF <sup>(1)</sup> |  |  |

| 45.0         | R/W-0                            | U-0                | R/W-0             | R/W-0                 | R/W-0             | R/W-0             | R/W-0            | R/W-0                 |  |  |

| 15:8         | ON                               | _                  | SIDL              | DISSDO <sup>(4)</sup> | MODE32            | MODE32 MODE16     |                  | CKE <sup>(2)</sup>    |  |  |

| 7.0          | R/W-0                            | R/W-0              | R/W-0             | R/W-0                 | R/W-0             | R/W-0             | R/W-0            | R/W-0                 |  |  |

| 7:0          | SSEN                             | CKP <sup>(3)</sup> | MSTEN             | DISSDI <sup>(4)</sup> | STXISE            | L<1:0>            | SRXISEL<1:0>     |                       |  |  |

#### REGISTER 19-1: SPIxCON: SPI CONTROL REGISTER

#### Legend:

| 0                 |                  |                                    |                    |  |  |  |  |

|-------------------|------------------|------------------------------------|--------------------|--|--|--|--|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, read as '0' |                    |  |  |  |  |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared               | x = Bit is unknown |  |  |  |  |

bit 31 FRMEN: Framed SPI Support bit

- 1 = Framed SPI support is enabled ( $\overline{SSx}$  pin used as FSYNC input/output)

- 0 = Framed SPI support is disabled

- bit 30 **FRMSYNC:** Frame Sync Pulse Direction Control on <u>SSx</u> pin bit (Framed SPI mode only)

- 1 = Frame sync pulse input (Slave mode)

- 0 = Frame sync pulse output (Master mode)

- bit 29 FRMPOL: Frame Sync Polarity bit (Framed SPI mode only)

- 1 = Frame pulse is active-high

- 0 = Frame pulse is active-low

- bit 28 MSSEN: Master Mode Slave Select Enable bit

- 1 = Slave select SPI support is enabled. The SS pin is automatically driven during transmission in Master mode. Polarity is determined by the FRMPOL bit.

- 0 = Slave select SPI support is disabled.

- bit 27 FRMSYPW: Frame Sync Pulse Width bit

- 1 = Frame sync pulse is one character wide

- 0 = Frame sync pulse is one clock wide

- bit 26-24 **FRMCNT<2:0>:** Frame Sync Pulse Counter bits. Controls the number of data characters transmitted per pulse. This bit is only valid in Framed mode.

- 111 = Reserved

- 110 = Reserved

- 101 = Generate a frame sync pulse on every 32 data characters

- 100 = Generate a frame sync pulse on every 16 data characters

- 011 = Generate a frame sync pulse on every 8 data characters

- 010 = Generate a frame sync pulse on every 4 data characters

- 001 = Generate a frame sync pulse on every 2 data characters

000 = Generate a frame sync pulse on every data character

- bit 23 MCLKSEL: Master Clock Enable bit<sup>(1)</sup>

- 1 = REFCLKO1 is used by the Baud Rate Generator

- 0 = PBCLK2 is used by the Baud Rate Generator

- bit 22-18 Unimplemented: Read as '0'

- **Note 1:** This bit can only be written when the ON bit = 0. Refer to **Section 37.0** "**Electrical Characteristics**" for maximum clock frequency requirements.

- 2: This bit is not used in the Framed SPI mode. The user should program this bit to '0' for the Framed SPI mode (FRMEN = 1).

- **3:** When AUDEN = 1, the SPI/I<sup>2</sup>S module functions as if the CKP bit is equal to '1', regardless of the actual value of the CKP bit.

- 4: This bit present for legacy compatibility and is superseded by PPS functionality on these devices (see Section 12.4 "Peripheral Pin Select (PPS)" for more information).

|              | IN 20-9. 0                  | GIIIIIIOIAI       | . Sel INTER            |                   |                   |                   |                  |                  |

|--------------|-----------------------------|-------------------|------------------------|-------------------|-------------------|-------------------|------------------|------------------|

| Bit<br>Range | Bit<br>31/23/15/7           | Bit<br>30/22/14/6 | Bit<br>29/21/13/5      | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |

| 24.24        | U-0                         | U-0               | U-0                    | U-0               | U-0               | U-0               | U-0              | U-0              |

| 31:24        | _                           | —                 | _                      | _                 | _                 | _                 | _                | _                |

| 22.10        | U-0                         | U-0               | U-0                    | U-0               | U-0 U-0           |                   | U-0              | U-0              |

| 23:16        | —                           | —                 | —                      | —                 | _                 | —                 | —                | —                |

|              | U-0                         | U-0               | U-0                    | U-0               | R/W-0, HS         | R/W-0, HS         | R/W-0, HS        | R/W-0, HS        |

| 15:8         | _                           | —                 | _                      | -                 | DMA<br>EIF        | PKT<br>COMPIF     | BD<br>DONEIF     | CON<br>THRIF     |

|              | R/W-1, HS                   | R/W-0, HS         | R/W-1, HS              | R/W-0, HS         | R/W-1, HS         | R/W-1, HS         | R/W-0, HS        | R/W-1, HS        |

| 7:0          | CON CON<br>EMPTYIF FULLIF R |                   | RXTHRIF <sup>(1)</sup> | RXFULLIF          | RX<br>EMPTYIF     | TXTHRIF           | TXFULLIF         | TX<br>EMPTYIF    |

#### **REGISTER 20-9:** SQI1INTSTAT: SQI INTERRUPT STATUS REGISTER

| Legend:           | HS = Hardware Set |                          |                    |

|-------------------|-------------------|--------------------------|--------------------|

| R = Readable bit  | W = Writable bit  | U = Unimplemented bit, r | ead as '0'         |

| -n = Value at POR | '1' = Bit is set  | '0' = Bit is cleared     | x = Bit is unknown |

#### b

| hit 21 12 | Unimplemented: Read as '0'                                                             |

|-----------|----------------------------------------------------------------------------------------|

|           | •                                                                                      |

| bit 11    | DMAEIF: DMA Bus Error Interrupt Flag bit                                               |

|           | 1 = DMA bus error has occurred                                                         |

|           | 0 = DMA bus error has not occurred                                                     |

| bit 10    | <b>PKTCOMPIF:</b> DMA Buffer Descriptor Processor Packet Completion Interrupt Flag bit |

|           | 1 = DMA BD packet is complete                                                          |

|           | 0 = DMA BD packet is in progress                                                       |

| bit 9     | BDDONEIF: DMA Buffer Descriptor Done Interrupt Flag bit                                |

|           | 1 = DMA BD process is done                                                             |

|           | 0 = DMA BD process is in progress                                                      |

| bit 8     | CONTHRIF: Control Buffer Threshold Interrupt Flag bit                                  |

|           | 1 = The control buffer has more than THRES words of space available                    |

|           | 0 = The control buffer has less than THRES words of space available                    |

| bit 7     | CONEMPTYIF: Control Buffer Empty Interrupt Flag bit                                    |

|           | 1 = Control buffer is empty                                                            |

|           | 0 = Control buffer is not empty                                                        |

| bit 6     | CONFULLIF: Control Buffer Full Interrupt Flag bit                                      |

|           | 1 = Control buffer is full                                                             |

|           | 0 = Control buffer is not full                                                         |

| bit 5     | RXTHRIF: Receive Buffer Threshold Interrupt Flag bit <sup>(1)</sup>                    |

|           | 1 = Receive buffer has more than RXINTTHR words of space available                     |

|           | 0 = Receive buffer has less than RXINTTHR words of space available                     |

| bit 4     | RXFULLIF: Receive Buffer Full Interrupt Flag bit                                       |

|           | 1 = Receive buffer is full                                                             |

|           | 0 = Receive buffer is not full                                                         |

- b

- bit 3 **RXEMPTYIF:** Receive Buffer Empty Interrupt Flag bit

- 1 = Receive buffer is empty

- 0 = Receive buffer is not empty

- Note 1: In Boot/XIP mode, the POR value of the receive buffer threshold is zero. Therefore, this bit will be set to a '1', immediately after a POR until a read request on the System Bus is received.

Note: The bits in the register are cleared by writing a '1' to the corresponding bit position.

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|

| 24.24        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 31:24        | _                 | —                 | _                 | _                 | _                 | -                 | -                | —                |

| 00.40        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 23:16        | _                 | —                 | _                 | _                 | —                 | -                 | -                | —                |

| 45.0         | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 15:8         | _                 | —                 | _                 | _                 | _                 | _                 | _                | —                |

| 7.0          | U-0               | U-0               | U-0               | U-0               | U-0               | R/W-0             | R/W-0            | R/W-0            |

| 7:0          |                   | _                 | _                 | _                 | _                 | START             | POLLEN           | DMAEN            |

#### REGISTER 20-14: SQI1BDCON: SQI BUFFER DESCRIPTOR CONTROL REGISTER

#### Legend:

bit 0

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, read as '0' |                    |  |  |  |

|-------------------|------------------|------------------------------------|--------------------|--|--|--|

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared               | x = Bit is unknown |  |  |  |

#### bit 31-3 Unimplemented: Read as '0'

- bit 2 START: Buffer Descriptor Processor Start bit

- 1 = Start the buffer descriptor processor

- 0 = Disable the buffer descriptor processor

- bit 1 **POLLEN:** Buffer Descriptor Poll Enable bit

- 1 = BDP poll is enabled

- 0 = BDP poll is not enabled

- DMAEN: DMA Enable bit

- 1 = DMA is enabled

- 0 = DMA is disabled

#### REGISTER 20-15: SQI1BDCURADD: SQI BUFFER DESCRIPTOR CURRENT ADDRESS REGISTER

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |  |  |  |  |  |  |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|--|--|--|--|--|--|

| 21.24        | R-0               | R-0               | R-0               | R-0               | R-0               | R-0               | R-0              | R-0              |  |  |  |  |  |  |

| 31:24        | BDCURRADDR<31:24> |                   |                   |                   |                   |                   |                  |                  |  |  |  |  |  |  |

| 00.40        | R-0               | R-0               | R-0               | R-0               | R-0               | R-0               | R-0              | R-0              |  |  |  |  |  |  |

| 23:16        | BDCURRADDR<23:16> |                   |                   |                   |                   |                   |                  |                  |  |  |  |  |  |  |

| 45.0         | R-0               | R-0               | R-0               | R-0               | R-0               | R-0               | R-0              | R-0              |  |  |  |  |  |  |

| 15:8         | BDCURRADDR<15:8>  |                   |                   |                   |                   |                   |                  |                  |  |  |  |  |  |  |

| 7.0          | R-0               | R-0               | R-0               | R-0               | R-0               | R-0               | R-0              | R-0              |  |  |  |  |  |  |

| 7:0          |                   |                   |                   | BDCURRAD          | DDR<7:0>          |                   |                  |                  |  |  |  |  |  |  |

| Legend:           |                  |                          |                    |

|-------------------|------------------|--------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, r | ead as '0'         |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared     | x = Bit is unknown |

#### bit 31-0 BDCURRADDR<31:0>: Current Buffer Descriptor Address bits

These bits contain the address of the current descriptor being processed by the Buffer Descriptor Processor.

# 21.1 I<sup>2</sup>C Control Registers

# TABLE 21-1: I2C1 THROUGH I2C5 REGISTER MAP

| ess                         |                                 |               |             |            |        |        |             |           |             | Bi         | ts         |               |               |               |               |              |              |             |            |

|-----------------------------|---------------------------------|---------------|-------------|------------|--------|--------|-------------|-----------|-------------|------------|------------|---------------|---------------|---------------|---------------|--------------|--------------|-------------|------------|

| Virtual Address<br>(BF82_#) | Register<br>Name <sup>(1)</sup> | Bit Range     | 31/15       | 30/14      | 29/13  | 28/12  | 27/11       | 26/10     | 25/9        | 24/8       | 23/7       | 22/6          | 21/5          | 20/4          | 19/3          | 18/2         | 17/1         | 16/0        | All Resets |

| 0000                        | I2C1CON                         | 31:16         | _           | _          | —      | —      | —           |           | _           |            |            | PCIE          | SCIE          | BOEN          | SDAHT         | SBCDE        | AHEN         | DHEN        | 0000       |

| 0000                        | 12010011                        | 15:0          | ON          |            | SIDL   | SCLREL | STRICT      | A10M      | DISSLW      | SMEN       | GCEN       | STREN         | ACKDT         | ACKEN         | RCEN          | PEN          | RSEN         | SEN         | 1000       |

| 0010                        | I2C1STAT                        | 31:16         |             | —          | —      | —      |             | -         | —           | _          | —          | —             | -             | _             | _             | —            | —            | -           | 0000       |

|                             |                                 | 15:0          | ACKSTAT     | TRSTAT     | ACKTIM | _      |             | BCL       | GCSTAT      | ADD10      | IWCOL      | I2COV         | D/A           | Р             | S             | R/W          | RBF          | TBF         | 0000       |

| 0020                        | I2C1ADD                         | 31:16         | _           | _          |        |        | _           |           |             | _          | _          | —             |               |               | —             | —            |              | —           | 0000       |

|                             |                                 | 15:0          | _           |            |        |        |             |           |             |            |            |               | Address       | Register      |               |              |              |             | 0000       |

| 0030                        | I2C1MSK                         | 31:16<br>15:0 |             |            | —      |        |             |           | —           | _          | _          | _             | - Address Mr  | ask Registe   |               | _            | —            | —           | 0000       |

|                             |                                 | 31:16         | _           |            |        |        |             |           |             |            |            |               | Address Ma    | ask Registe   |               |              |              | _           | 0000       |

| 0040                        | I2C1BRG                         | 15:0          |             |            | _      | _      | _           |           | Bau         | d Rate Gen | erator Reg | ister         | _             | _             | _             | _            | _            |             | 0000       |

|                             |                                 | 31:16         |             | _          | _      | _      |             | _         |             |            |            |               | _             | _             | _             | _            | _            | _           | 0000       |

| 0050                        | I2C1TRN                         | 15:0          | _           | _          | _      | _      |             | _         | _           | _          |            |               |               | Transmit      | Register      |              |              |             | 0000       |

|                             |                                 | 31:16         | _           | _          | _      | _      | _           | _         | _           | _          | _          | _             | _             |               | —             | _            | _            | _           | 0000       |

| 0060                        | I2C1RCV                         | 15:0          | _           | _          | _      | _      |             | _         | _           | _          |            |               |               | Receive       | Register      |              |              |             | 0000       |

|                             |                                 | 31:16         | _           | _          | _      | _      | _           | _         | _           | _          | _          | PCIE          | SCIE          | BOEN          | SDAHT         | SBCDE        | AHEN         | DHEN        | 0000       |

| 0200                        | 12C2CON <sup>(2)</sup>          | 15:0          | ON          | _          | SIDL   | SCLREL | STRICT      | A10M      | DISSLW      | SMEN       | GCEN       | STREN         | ACKDT         | ACKEN         | RCEN          | PEN          | RSEN         | SEN         | 1000       |

| 0040                        | 12C2STAT <sup>(2)</sup>         | 31:16         | _           |            | _      | —      | —           |           | _           | _          |            | _             | —             | —             | _             | _            | —            |             | 0000       |

| 0210                        | 12025TAT-                       | 15:0          | ACKSTAT     | TRSTAT     | ACKTIM | _      | —           | BCL       | GCSTAT      | ADD10      | IWCOL      | I2COV         | D/A           | Р             | S             | R/W          | RBF          | TBF         | 0000       |

| 0220                        | 12C2ADD(2)                      | 31:16         | _           |            | —      | _      | _           |           | —           | _          | -          | _             | -             | _             | _             | —            | -            |             | 0000       |

| 0220                        | IZCZADD.                        | 15:0          | _           | _          | _      | —      | _           | _         |             |            |            |               | Address       | Register      |               |              | -            |             | 0000       |

| 0230                        | 12C2MSK(2)                      | 31:16         | —           | —          | —      | —      | —           | -         | —           | —          | —          | —             | —             | —             | —             | —            | —            | —           | 0000       |

| 0200                        |                                 | 15:0          | _           |            |        | —      | _           |           |             |            |            |               | Address Ma    | ask Registe   | r             |              |              |             | 0000       |

| 0240                        | 12C2BRG(2)                      | 31:16         | —           | —          | —      | —      | _           | —         | —           | —          | _          | —             | —             | —             | —             | —            | —            | —           | 0000       |

|                             |                                 | 15:0          |             |            |        |        |             |           | Bau         | d Rate Gen | erator Reg | ister         |               |               |               |              |              |             | 0000       |

| 0250                        | 12C2TRN(2)                      | 31:16         | _           |            |        | _      | _           |           | _           | _          | _          | —             |               |               |               | _            |              | _           | 0000       |

|                             |                                 | 15:0          | _           |            |        |        | _           |           |             | _          |            |               |               | Transmit      | Register      |              |              |             | 0000       |

| 0260                        | I2C2RCV(2)                      | 31:16         | _           | _          | _      | _      |             | _         | _           | _          | -          |               | —             | -             | —             | —            | —            | —           | 0000       |

|                             |                                 | 15:0          | _           |            |        |        |             |           |             | _          |            | DOIE          | 0015          | Receive       |               | 00005        |              | DUEN        | 0000       |

| 0400                        | I2C3CON                         | 31:16<br>15:0 | ON          |            |        |        | —<br>STRICT | —<br>A10M | —<br>DISSLW | <br>SMEN   | —<br>GCEN  | PCIE<br>STREN | SCIE<br>ACKDT | BOEN<br>ACKEN | SDAHT<br>RCEN | SBCDE<br>PEN | AHEN<br>RSEN | DHEN<br>SEN | 0000       |

|                             |                                 | 31:16         |             |            | SIDL   | SULREL |             | A10M      | DISSLW      | SIMEIN     | GCEN       |               | ACKDI         | ACKEN         | RCEN          | PEN          | KSEN         | SEN<br>—    | 1000       |

| 0410                        | I2C3STAT                        | 15:0          | <br>ACKSTAT | <br>TRSTAT | ACKTIM | _      |             | BCL       | GCSTAT      | ADD10      |            | I2COV         | <br>D/A       | <br>P         |               | R/W          | <br>RBF      | <br>TBF     | 0000       |

|                             |                                 | 31:16         | -           |            |        |        | _           | BCL       | GCSTAT      |            |            | 12000         |               | г<br>         | 3             | R/W          |              |             | 0000       |

| 0420                        | I2C3ADD                         | 15:0          |             |            |        |        |             |           |             |            |            |               | Address       | <br>Register  |               |              |              |             | 0000       |

| Logon                       |                                 |               |             |            |        |        |             |           | chown in h  |            |            |               | /1001033      | register      |               |              |              |             | 0000       |

Legend: x = unknown value on Reset; — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

Note 1: All registers in this table except I2CxRCV have corresponding CLR, SET and INV registers at their virtual addresses, plus offsets of 0x4, 0x8 and 0xC, respectively. See Section 12.3 "CLR, SET, and INV Registers" for more information.

2: This register is not available on 64-pin devices.

### REGISTER 22-2: UxSTA: UARTx STATUS AND CONTROL REGISTER (CONTINUED)

| bit 7-6 | URXISEL<1:0>: Receive Interrupt Mode Selection bit<br>11 = Reserved                                                                                                                                                                                                                                         |

|---------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|         | <ul> <li>10 = Interrupt flag bit is asserted while receive buffer is 3/4 or more full</li> <li>01 = Interrupt flag bit is asserted while receive buffer is 1/2 or more full</li> <li>00 = Interrupt flag bit is asserted while receive buffer is not empty (i.e., has at least 1 data character)</li> </ul> |

| bit 5   | <ul> <li>ADDEN: Address Character Detect bit (bit 8 of received data = 1)</li> <li>1 = Address Detect mode is enabled. If 9-bit mode is not selected, this control bit has no effect</li> <li>0 = Address Detect mode is disabled</li> </ul>                                                                |

| bit 4   | RIDLE: Receiver Idle bit (read-only)<br>1 = Receiver is Idle<br>0 = Data is being received                                                                                                                                                                                                                  |

| bit 3   | <ul> <li>PERR: Parity Error Status bit (read-only)</li> <li>1 = Parity error has been detected for the current character</li> <li>0 = Parity error has not been detected</li> </ul>                                                                                                                         |

| bit 2   | <ul> <li>FERR: Framing Error Status bit (read-only)</li> <li>1 = Framing error has been detected for the current character</li> <li>0 = Framing error has not been detected</li> </ul>                                                                                                                      |

| bit 1   | OERR: Receive Buffer Overrun Error Status bit.                                                                                                                                                                                                                                                              |

|         | This bit is set in hardware and can only be cleared (= 0) in software. Clearing a previously set OERR bit resets the receiver buffer and RSR to empty state.                                                                                                                                                |

|         | <ul> <li>1 = Receive buffer has overflowed</li> <li>0 = Receive buffer has not overflowed</li> </ul>                                                                                                                                                                                                        |

| bit 0   | <ul> <li>URXDA: Receive Buffer Data Available bit (read-only)</li> <li>1 = Receive buffer has data, at least one more character can be read</li> <li>0 = Receive buffer is empty</li> </ul>                                                                                                                 |

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |  |  |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|--|--|

| 04.04        | R-0               | R-0               | R-0               | R-0               | R-0               | R-0               | R-0              | R-0              |  |  |

| 31:24        |                   |                   |                   | ID<15             | i:8>              |                   |                  |                  |  |  |

| 00.40        | R-0               | R-0               | R-0               | R-0               | R-0               | R-0               | R-0              | R-0              |  |  |

| 23:16        | ID<7:0>           |                   |                   |                   |                   |                   |                  |                  |  |  |

| 45.0         | R-0               | R-0               | R-0               | R-0               | R-0               | R-0               | R-0              | R-0              |  |  |

| 15:8         | VERSION<7:0>      |                   |                   |                   |                   |                   |                  |                  |  |  |

| 7.0          | R-0               | R-0               | R-0               | R-0               | R-0               | R-0               | R-0              | R-0              |  |  |

| 7:0          |                   |                   |                   | REVISIO           | N<7:0>            |                   |                  |                  |  |  |

# REGISTER 27-1: RNGVER: RANDOM NUMBER GENERATOR VERSION REGISTER

# Legend:

| Legena.           |                  |                        |                    |

|-------------------|------------------|------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, | read as '0'        |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared   | x = Bit is unknown |

bit 31-16 ID<15:0>: Block Identification bits

bit 15-8 VERSION<7:0>: Block Version bits

bit 7-0 REVISION<7:0>: Block Revision bits

Т

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|

| 31:24        | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |

| 31.24        | FLTEN7            | MSEL              | 7<1:0>            |                   | F                 | SEL7<4:0>         |                  |                  |

| 23:16        | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |

| 23.10        | FLTEN6            | MSEL6<1:0>        |                   | FSEL6<4:0>        |                   |                   |                  |                  |

| 15:8         | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |

| 10.0         | FLTEN5            | MSEL              | 5<1:0>            |                   | F                 | SEL5<4:0>         |                  |                  |

| 7:0          | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |

| 7:0          | FLTEN4            | MSEL              | 4<1:0>            |                   | F                 | SEL4<4:0>         |                  |                  |

### REGISTER 29-11: CIFLTCON1: CAN FILTER CONTROL REGISTER 1

### Legend:

| R = Readable bit  | W = Writable bit | able bit U = Unimplemented bit, read as '0' |                    |

|-------------------|------------------|---------------------------------------------|--------------------|

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared                        | x = Bit is unknown |

| bit 31    | FLTEN7: Filter 7 Enable bit                                        |

|-----------|--------------------------------------------------------------------|

|           | 1 = Filter is enabled                                              |

|           | 0 = Filter is disabled                                             |

| bit 30-29 | MSEL7<1:0>: Filter 7 Mask Select bits                              |

|           | 11 = Acceptance Mask 3 selected                                    |

|           | 10 = Acceptance Mask 2 selected<br>01 = Acceptance Mask 1 selected |

|           | 00 = Acceptance Mask 0 selected                                    |

| bit 28-24 | <b>FSEL7&lt;4:0&gt;:</b> FIFO Selection bits                       |

| 511 20 21 | 11111 = Message matching filter is stored in FIFO buffer 31        |