Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFl

| Product Status             | Active                                                                           |

|----------------------------|----------------------------------------------------------------------------------|

| Core Processor             | MIPS32® M-Class                                                                  |

| Core Size                  | 32-Bit Single-Core                                                               |

| Speed                      | 180MHz                                                                           |

| Connectivity               | CANbus, EBI/EMI, Ethernet, I <sup>2</sup> C, PMP, SPI, SQI, UART/USART, USB OTG  |

| Peripherals                | Brown-out Detect/Reset, DMA, I <sup>2</sup> S, POR, PWM, WDT                     |

| Number of I/O              | 120                                                                              |

| Program Memory Size        | 512KB (512K x 8)                                                                 |

| Program Memory Type        | FLASH                                                                            |

| EEPROM Size                |                                                                                  |

| RAM Size                   | 128K x 8                                                                         |

| Voltage - Supply (Vcc/Vdd) | 2.1V ~ 3.6V                                                                      |

| Data Converters            | A/D 48x12b                                                                       |

| Oscillator Type            | Internal                                                                         |

| Operating Temperature      | -40°C ~ 125°C (TA)                                                               |

| Mounting Type              | Surface Mount                                                                    |

| Package / Case             | 144-LQFP                                                                         |

| Supplier Device Package    | 144-LQFP (20x20)                                                                 |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic32mz0512eff144-e-pl |

|                            |                                                                                  |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

The System Bus arbitration scheme implements a nonprogrammable, Least Recently Serviced (LRS) priority, which provides Quality Of Service (QOS) for most initiators. However, some initiators can use Fixed High Priority (HIGH) arbitration to guarantee their access to data.

The arbitration scheme for the available initiators is shown in Table 4-5.

| ID | QOS                                                                     |

|----|-------------------------------------------------------------------------|

| 1  | LRS <sup>(1)</sup>                                                      |

| 2  | HIGH <sup>(1,2)</sup>                                                   |

| 3  | LRS <sup>(1)</sup>                                                      |

| 4  | HIGH <sup>(1,2)</sup>                                                   |

| 5  | LRS <sup>(1)</sup>                                                      |

| 6  | HIGH <sup>(1,2)</sup>                                                   |

| 7  | LRS                                                                     |

| 8  | LRS                                                                     |

| 9  | LRS                                                                     |

| 10 | LRS                                                                     |

| 11 | LRS                                                                     |

| 12 | LRS                                                                     |

| 13 | HIGH <sup>(2)</sup>                                                     |

| 14 | LRS                                                                     |

|    | 1<br>2<br>3<br>4<br>5<br>6<br>7<br>8<br>9<br>10<br>11<br>11<br>12<br>13 |

TABLE 4-5:INITIATOR ID AND QOS

- Note 1: When accessing SRAM, the DMAPRI bit (CFGCON<25>) and the CPUPRI bit (CFGCON<24>) provide arbitration control for the DMA and CPU (when servicing an interrupt (i.e., EXL = 1)), respectively, by selecting the use of LRS or HIGH When using HIGH, the DMA and CPU get arbitration preference over all initiators using LRS.

- 2: Using HIGH arbitration can have serious negative effects on other initiators. Therefore, it is recommended to not enable this type of arbitration for an initiator that uses significant system bandwidth. HIGH arbitration is intended to be used for low bandwidth applications that require low latency, such as LCC graphics applications.

# 4.3 Permission Access and System Bus Registers

The System Bus on PIC32MZ EF family of microcontrollers provides access control capabilities for the transaction initiators on the System Bus.

The System Bus divides the entire memory space into fourteen target regions and permits access to each target by initiators via permission groups. Four Permission Groups (0 through 3) can be assigned to each initiator. Each permission group is independent of the others and can have exclusive or shared access to a region.

Using the CFGPG register (see Register 34-10 in **Section 34.0 "Special Features"**), Boot firmware can assign a permission group to each initiator, which can make requests on the System Bus.

The available targets and their regions, as well as the associated control registers to assign protection, are described and listed in Table 4-6.

Register 4-2 through Register 4-10 are used for setting and controlling access permission groups and regions.

To change these registers, they must be unlocked in hardware. The register lock is controlled by the PGLOCK Configuration bit (CFGCON<11>). Setting PGLOCK prevents writes to the control registers; clearing PGLOCK allows writes.

To set or clear the PGLOCK bit, an unlock sequence must be executed. Refer to **Section 42. "Oscillators with Enhanced PLL"** in the *"PIC32 Family Reference Manual"* for details.

#### **TABLE 7-3**: **INTERRUPT REGISTER MAP (CONTINUED)**

| ress<br>f)                  | <b>b</b> -                      | Ð         |       |       |       |       |       |       |      | Bi         | ts   |      |      |      |      |      |       |        | Ś          |

|-----------------------------|---------------------------------|-----------|-------|-------|-------|-------|-------|-------|------|------------|------|------|------|------|------|------|-------|--------|------------|

| Virtual Address<br>(BF81_#) | Register<br>Name <sup>(1)</sup> | Bit Range | 31/15 | 30/14 | 29/13 | 28/12 | 27/11 | 26/10 | 25/9 | 24/8       | 23/7 | 22/6 | 21/5 | 20/4 | 19/3 | 18/2 | 17/1  | 16/0   | All Recete |

|                             | 055000                          | 31:16     | _     | _     | —     | _     | _     | _     | —    | _          |      | _    | _    | _    | —    | _    | VOFF< | 17:16> | 00         |

| 0548                        | OFF002                          | 15:0      |       |       |       |       |       |       |      | VOFF<15:1> |      |      |      |      |      |      |       | —      | 000        |

| 0540                        | OFF003                          | 31:16     | _     | _     | _     | _     | _     | _     | _    | —          | _    | _    | _    | _    | _    | _    | VOFF< | 17:16> | 000        |

| J54C                        | 0FF003                          | 15:0      |       |       |       |       |       |       |      | VOFF<15:1> |      |      |      |      |      |      |       | _      | 000        |

| 0550                        | OFF004                          | 31:16     | _     | _     | —     | —     |       | -     | _    | _          |      | _    |      | _    | _    | _    | VOFF< | 17:16> | 000        |

| 0550                        | 011004                          | 15:0      |       |       |       |       |       |       |      | VOFF<15:1> |      |      |      |      |      |      |       | —      | 000        |

| 0554                        | OFF005                          | 31:16     | _     | -     | —     | —     | -     | -     | —    | —          | _    | —    | -    | -    | —    | -    | VOFF< | 17:16> | 000        |

| 0554                        | 011005                          | 15:0      |       |       |       |       |       |       | -    | VOFF<15:1> |      |      |      |      | -    |      |       | —      | 00         |

| 0558                        | OFF006                          | 31:16     |       | _     | —     | —     | —     | —     | —    | —          | _    | —    | —    | _    | —    | _    | VOFF< | 17:16> | 000        |

| 0550                        | 011000                          | 15:0      |       |       |       |       |       |       |      | VOFF<15:1> |      |      |      |      |      |      |       | —      | 000        |

| 155C                        | OFF007                          | 31:16     |       | _     | —     | —     | —     | —     | —    | —          | _    | —    | —    | _    | —    | _    | VOFF< | 17:16> | 00         |

|                             | 011007                          | 15:0      |       |       |       |       |       |       |      | VOFF<15:1> |      |      |      |      |      |      |       | _      | 00         |

| 0560                        | OFF008                          | 31:16     | _     | -     | —     | —     | -     | -     | —    | —          | _    | —    | -    | -    | —    | -    | VOFF< | 17:16> | 00         |

| 0500                        | 011000                          | 15:0      |       |       |       |       |       |       | -    | VOFF<15:1> |      |      |      |      | -    |      |       | —      | 000        |

| 0564                        | OFF009                          | 31:16     |       | _     | —     | —     | —     | —     | —    | —          | _    | —    | —    | _    | —    | _    | VOFF< | 17:16> | 00         |

| 0004                        | 011005                          | 15:0      |       |       |       |       |       |       | -    | VOFF<15:1> |      |      |      |      | -    |      |       | —      | 00         |

| 0568                        | OFF010                          | 31:16     | —     | —     | —     | —     | —     | —     | —    | —          | —    | —    | —    | —    | —    | —    | VOFF< | 17:16> | 00         |

| 0000                        | 011010                          | 15:0      |       |       |       |       |       |       | -    | VOFF<15:1> |      |      |      |      | -    |      |       |        | 000        |

| 156C                        | OFF011                          | 31:16     |       | _     | —     | —     | —     | —     | —    | —          | _    | —    | —    | _    | —    | _    | VOFF< | 17:16> | 000        |

| 0000                        | onioni                          | 15:0      |       |       |       |       |       |       |      | VOFF<15:1> |      |      |      |      |      |      |       |        | 000        |

| 0570                        | OFF012                          | 31:16     | —     | —     | —     | —     | —     | —     |      | —          | —    | —    | _    | —    | —    | —    | VOFF< | 17:16> | 00         |

| 0010                        | 011012                          | 15:0      |       |       |       |       |       |       |      | VOFF<15:1> |      |      |      |      |      |      |       |        | 000        |

| 0574                        | OFF013                          | 31:16     | —     | —     | —     | —     | —     | —     | —    | —          |      | —    | —    | —    | —    | —    | VOFF< | 17:16> | 00         |

| 0374                        | 011013                          | 15:0      |       |       |       |       |       |       |      | VOFF<15:1> |      |      |      |      |      |      |       |        | 000        |

| 0578                        | OFF014                          | 31:16     | —     | —     | —     | —     | _     | _     | _    | —          |      | —    | —    | —    |      | —    | VOFF< | 17:16> | 000        |

| 0070                        | 011014                          | 15:0      |       |       |       |       |       |       |      | VOFF<15:1> |      |      |      |      |      |      |       |        | 000        |

| 0570                        | OFF015                          | 31:16     | —     | —     | —     | —     | —     | —     | —    | —          | —    | —    | —    | —    | —    | —    | VOFF< | 17:16> | 000        |

|                             | 0.7010                          | 15:0      |       |       |       |       |       |       |      | VOFF<15:1> |      |      |      |      |      |      |       |        | 000        |

| 0580                        | OFF016                          | 31:16     | _     | _     | —     | —     | —     | —     | —    | —          | —    | —    | —    | _    | —    | —    | VOFF< | 17:16> | 000        |

| 0000                        | 011010                          | 15:0      |       |       |       |       |       |       |      | VOFF<15:1> |      |      |      |      |      |      |       | _      | 000        |

© 2015-2016 Microchip Technology Inc.

Note 1: All registers in this table with the exception of the OFFx registers, have corresponding CLR, SET, and INV registers at their virtual addresses, plus offsets of 0x4, 0x8 and 0xC, respectively. See Section 12.3 "CLR, SET, and INV **Registers**" for more information. This bit or register is not available on 64-pin devices.

This bit or register is not available on devices without a CAN module. 3:

4: This bit or register is not available on 100-pin devices.

- Bits 31 and 30 are not available on 64-pin and 100-pin devices; bits 29 through 14 are not available on 64-pin devices. 5:

- Bits 31, 30, 29, and bits 5 through 0 are not available on 64-pin and 100-pin devices; bit 31 is not available on 124-pin devices; bit 22 is not available on 64-pin devices. 6:

7: This bit or register is not available on devices without a Crypto module.

This bit or register is not available on 124-pin devices. 8:

<sup>2:</sup>

#### **TABLE 7-3: INTERRUPT REGISTER MAP (CONTINUED)**

| ress<br>)                   |                                 | e         |       |       |       |       |       |       |      | Bi         | ts   |      |      |      |      |      |       |         | s          |

|-----------------------------|---------------------------------|-----------|-------|-------|-------|-------|-------|-------|------|------------|------|------|------|------|------|------|-------|---------|------------|

| Virtual Address<br>(BF81_#) | Register<br>Name <sup>(1)</sup> | Bit Range | 31/15 | 30/14 | 29/13 | 28/12 | 27/11 | 26/10 | 25/9 | 24/8       | 23/7 | 22/6 | 21/5 | 20/4 | 19/3 | 18/2 | 17/1  | 16/0    | All Resets |

|                             | OFF047                          | 31:16     | _     | _     | —     | _     | _     | —     | —    | _          | _    |      | —    | _    | —    | _    | VOFF< | :17:16> | 0000       |

| USFC                        | OFF047                          | 15:0      |       |       |       |       |       |       |      | VOFF<15:1> |      |      |      |      |      |      |       |         | 0000       |

| 0600                        | OFF048                          | 31:16     | _     | _     | —     | —     | _     | _     | _    | —          | _    | —    | -    | —    | —    | _    | VOFF< | :17:16> | 0000       |

| 0000                        | 011040                          | 15:0      |       |       |       |       |       | -     | -    | VOFF<15:1> |      |      | -    | -    |      |      |       |         | 0000       |

| 0604                        | OFF049                          | 31:16     | —     | _     | —     | —     | —     | —     | —    | —          | _    | —    | -    | —    | —    | —    | VOFF< | :17:16> | 0000       |

| 0004                        | 011043                          | 15:0      |       |       |       |       |       |       |      | VOFF<15:1> |      |      |      |      |      |      |       | _       | 0000       |

| 0608                        | OFF050                          | 31:16     | —     | _     | —     | —     | —     | —     | —    | —          |      | —    | —    |      | —    | _    | VOFF< | :17:16> | 0000       |

| 0000                        | 011030                          | 15:0      |       |       |       |       |       |       |      | VOFF<15:1> |      |      |      |      |      |      |       | —       | 0000       |

| 0600                        | OFF051                          | 31:16     | —     | —     | —     | —     | —     |       |      | —          | —    | —    | -    | —    | —    | —    | VOFF< | :17:16> | 0000       |

| 0000                        | 011001                          | 15:0      |       |       |       |       |       |       |      | VOFF<15:1> |      |      |      |      |      |      |       |         | 0000       |

| 0610                        | OFF052                          | 31:16     | —     | —     | —     | —     | —     |       |      | —          | —    | —    | -    | —    | —    | —    | VOFF< | :17:16> | 0000       |

| 0010                        | 011032                          | 15:0      |       |       |       |       |       | -     | -    | VOFF<15:1> |      |      | -    | -    |      |      |       | _       | 0000       |

| 0614                        | OFF053                          | 31:16     | —     | —     | —     | —     | _     | —     | —    | _          | —    | _    | —    | _    | —    | _    | VOFF< | :17:16> | 0000       |

| 0014                        | 011033                          | 15:0      |       |       |       |       |       | -     | -    | VOFF<15:1> |      |      | -    | -    |      |      |       | —       | 0000       |

| 0618                        | OFF054                          | 31:16     | —     | _     | —     | —     | —     | —     | —    | —          | _    | —    | -    | —    | —    | —    | VOFF< | :17:16> | 0000       |

| 0010                        | 011004                          | 15:0      |       |       |       |       |       |       |      | VOFF<15:1> |      |      |      |      |      |      |       | _       | 0000       |

| 0610                        | OFF055                          | 31:16     | —     | _     | —     | —     | —     | —     | —    | —          | _    | —    | -    | —    | —    | —    | VOFF< | :17:16> | 0000       |

| 0010                        | OFF035                          | 15:0      |       |       |       |       |       |       |      | VOFF<15:1> |      |      |      |      |      |      |       | _       | 0000       |

| 0620                        | OFF056                          | 31:16     | _     | _     | —     | —     | _     | _     | _    | —          | _    | —    | -    | —    | —    | _    | VOFF< | :17:16> | 0000       |

| 0020                        | OFF030                          | 15:0      |       |       |       |       |       |       |      | VOFF<15:1> |      |      |      |      |      |      |       | _       | 0000       |

| 0624                        | OFF057                          | 31:16     | _     | _     | —     | —     | _     | —     | _    | _          | _    | —    | —    | —    | _    | _    | VOFF< | :17:16> | 0000       |

| 0024                        | 011037                          | 15:0      |       |       |       |       |       |       |      | VOFF<15:1> |      |      |      |      |      |      |       | _       | 0000       |

| 0628                        | OFF058                          | 31:16     | —     | _     | —     | _     |       | —     | —    | —          | _    | —    | -    | —    | —    |      | VOFF< | :17:16> | 0000       |

| 0020                        | OFF036                          | 15:0      |       |       | •     |       | -     | -     | -    | VOFF<15:1> |      | -    | -    | -    | •    | -    | -     | _       | 0000       |

| 0620                        | OFF059                          | 31:16     | —     | _     | —     | —     | -     | —     | -    | -          | _    | —    | -    | —    | —    | —    | VOFF< | :17:16> | 0000       |

| 0020                        | 01 F039                         | 15:0      |       |       |       |       |       |       |      | VOFF<15:1> |      |      |      |      |      |      |       | _       | 0000       |

| 0630                        | OFF060                          | 31:16     | _     |       | _     | _     | _     | _     | _    | _          |      |      | _    | _    |      | _    | VOFF< | :17:16> | 0000       |

| 0630                        |                                 | 15:0      |       |       |       |       |       |       |      | VOFF<15:1> |      |      |      |      |      |      |       | _       | 0000       |

| 0624                        |                                 | 31:16     | _     | —     | —     | —     | _     | —     | —    | _          | _    | _    | —    | _    | _    | _    | VOFF< | :17:16> | 0000       |

| 0634                        | OFF061                          | 15:0      |       |       |       |       |       |       |      | VOFF<15:1> |      |      |      |      |      |      |       | _       | 0000       |

DS60001320D-page 134

All registers in this table with the exception of the OFFx registers, have corresponding CLR, SET, and INV registers at their virtual addresses, plus offsets of 0x4, 0x8 and 0xC, respectively. See Section 12.3 "CLR, SET, and INV Note 1: **Registers**" for more information. This bit or register is not available on 64-pin devices.

2:

3: This bit or register is not available on devices without a CAN module.

4: This bit or register is not available on 100-pin devices.

5: Bits 31 and 30 are not available on 64-pin and 100-pin devices; bits 29 through 14 are not available on 64-pin devices.

6: Bits 31, 30, 29, and bits 5 through 0 are not available on 64-pin and 100-pin devices; bit 31 is not available on 124-pin devices; bit 22 is not available on 64-pin devices.

7: This bit or register is not available on devices without a Crypto module.

This bit or register is not available on 124-pin devices. 8:

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5    | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1     | Bit<br>24/16/8/0 |

|--------------|-------------------|-------------------|----------------------|-------------------|-------------------|-------------------|----------------------|------------------|

| 04-04        | R/W-0             | R/W-0             | R/W-0                | R/W-0             | R/W-0             | R/W-0             | R/W-0                | R/W-0            |

| 31:24        |                   | PRI7SS            | <3:0> <sup>(1)</sup> |                   |                   | PRI6SS            | <3:0> <sup>(1)</sup> |                  |

| 00.40        | R/W-0             | R/W-0             | R/W-0                | R/W-0             | R/W-0             | R/W-0             | R/W-0                | R/W-0            |

| 23:16        |                   | PRI5SS            | <3:0> <sup>(1)</sup> |                   |                   | PRI4SS            | <3:0> <sup>(1)</sup> |                  |

| 45.0         | R/W-0             | R/W-0             | R/W-0                | R/W-0             | R/W-0             | R/W-0             | R/W-0                | R/W-0            |

| 15:8         |                   | PRI3S             | S<3:0>               |                   |                   | PRI2SS            | <3:0> <sup>(1)</sup> |                  |

| 7.0          | R/W-0             | R/W-0             | R/W-0                | R/W-0             | U-0               | U-0               | U-0                  | R/W-0            |

| 7:0          |                   | PRI1SS            | <3:0> <sup>(1)</sup> | •                 |                   |                   | _                    | SS0              |

# REGISTER 7-2: PRISS: PRIORITY SHADOW SELECT REGISTER

| Legend:           |                  |                      |                    |

|-------------------|------------------|----------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bi | t, read as '0'     |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared | x = Bit is unknown |

bit 31-28 **PRI7SS<3:0>:** Interrupt with Priority Level 7 Shadow Set bits<sup>(1)</sup>

1xxx = Reserved (by default, an interrupt with a priority level of 7 uses Shadow Set 0) 0111 = Interrupt with a priority level of 7 uses Shadow Set 7 0110 = Interrupt with a priority level of 7 uses Shadow Set 6 0001 = Interrupt with a priority level of 7 uses Shadow Set 1 0000 = Interrupt with a priority level of 7 uses Shadow Set 0 bit 27-24 **PRI6SS<3:0>:** Interrupt with Priority Level 6 Shadow Set bits<sup>(1)</sup> 1xxx = Reserved (by default, an interrupt with a priority level of 6 uses Shadow Set 0) 0111 = Interrupt with a priority level of 6 uses Shadow Set 7 0110 = Interrupt with a priority level of 6 uses Shadow Set 6 0001 = Interrupt with a priority level of 6 uses Shadow Set 1 0000 = Interrupt with a priority level of 6 uses Shadow Set 0 bit 23-20 PRI5SS<3:0>: Interrupt with Priority Level 5 Shadow Set bits<sup>(1)</sup>  $1 \times 1 \times 1 =$  Reserved (by default, an interrupt with a priority level of 5 uses Shadow Set 0) 0111 = Interrupt with a priority level of 5 uses Shadow Set 7 0110 = Interrupt with a priority level of 5 uses Shadow Set 6 0001 = Interrupt with a priority level of 5 uses Shadow Set 1 0000 = Interrupt with a priority level of 5 uses Shadow Set 0 bit 19-16 PRI4SS<3:0>: Interrupt with Priority Level 4 Shadow Set bits<sup>(1)</sup> 1xxx = Reserved (by default, an interrupt with a priority level of 4 uses Shadow Set 0) 0111 = Interrupt with a priority level of 4 uses Shadow Set 7 0110 = Interrupt with a priority level of 4 uses Shadow Set 6 0001 = Interrupt with a priority level of 4 uses Shadow Set 1 0000 = Interrupt with a priority level of 4 uses Shadow Set 0

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |  |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|--|

| 24.24        | U-0               | U-0               | U-0               | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |

| 31:24        | —                 | —                 | —                 |                   | IP3<2:0>          | IS3<              | IS3<1:0>         |                  |  |

| 23:16        | U-0               | U-0               | U-0               | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |

| 23.10        | _                 | —                 | _                 |                   | IP2<2:0>          | IS2<              | IS2<1:0>         |                  |  |

| 15:8         | U-0               | U-0               | U-0               | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |

| 15.0         | _                 | —                 | _                 |                   | IP1<2:0>          |                   | IS1<             | :1:0>            |  |

| 7:0          | U-0               | U-0               | U-0               | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |

| 7.0          | _                 | —                 | _                 |                   | IP0<2:0>          |                   | IS0<             | :1:0>            |  |

# REGISTER 7-7: IPCx: INTERRUPT PRIORITY CONTROL REGISTER

# Legend:

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, re | ead as '0'         |

|-------------------|------------------|---------------------------|--------------------|

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared      | x = Bit is unknown |

# bit 31-29 Unimplemented: Read as '0'

| bit 28-26 | IP3<2:0>: Interrupt Priority bits                                  |

|-----------|--------------------------------------------------------------------|

|           | 111 = Interrupt priority is 7                                      |

|           | •                                                                  |

|           | •                                                                  |

|           | 010 = Interrupt priority is 2                                      |

|           | 001 = Interrupt priority is 1                                      |

|           | 000 = Interrupt is disabled                                        |

| bit 25-24 | IS3<1:0>: Interrupt Subpriority bits                               |

|           | 11 = Interrupt subpriority is 3                                    |

|           | 10 = Interrupt subpriority is 2                                    |

|           | 01 = Interrupt subpriority is 1                                    |

|           | 00 = Interrupt subpriority is 0                                    |

| bit 23-21 |                                                                    |

| bit 20-18 | IP2<2:0>: Interrupt Priority bits                                  |

|           | 111 = Interrupt priority is 7                                      |

|           | •                                                                  |

|           | •                                                                  |

|           | 010 = Interrupt priority is 2                                      |

|           | 001 = Interrupt priority is 1                                      |

|           | 000 = Interrupt is disabled                                        |

| bit 17-16 | IS2<1:0>: Interrupt Subpriority bits                               |

|           | 11 = Interrupt subpriority is 3                                    |

|           | 10 = Interrupt subpriority is 2                                    |

|           | 01 = Interrupt subpriority is 1<br>00 = Interrupt subpriority is 0 |

| hit 15-13 | Unimplemented: Read as '0'                                         |

| 5115-15   | ommplemented. Read as 0                                            |

| Note:     | This register represents a generic defi                            |

|           |                                                                    |

Note: This register represents a generic definition of the IPCx register. Refer to Table 7-2 for the exact bit definitions.

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|

| 04.04        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 31:24        | -                 | —                 | _                 | -                 | —                 | _                 | _                | —                |

| 00.40        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 23:16        |                   | —                 | _                 |                   | —                 |                   |                  | —                |

| 45.0         | R/W-0             | U-0               | U-0               | R/W-0             | R/W-0             | U-0               | U-0              | U-0              |

| 15:8         | ON                | —                 | _                 | SUSPEND           | DMABUSY           | _                 | _                | _                |

| 7.0          | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 7:0          |                   | _                 |                   | _                 | _                 |                   |                  | _                |

## REGISTER 10-1: DMACON: DMA CONTROLLER CONTROL REGISTER

# Legend:

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, re | ad as '0'          |

|-------------------|------------------|---------------------------|--------------------|

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared      | x = Bit is unknown |

#### bit 31-16 Unimplemented: Read as '0'

- bit 15 **ON:** DMA On bit

- 1 = DMA module is enabled

- 0 = DMA module is disabled

- bit 14-13 Unimplemented: Read as '0'

- bit 12 SUSPEND: DMA Suspend bit

- 1 = DMA transfers are suspended to allow CPU uninterrupted access to data bus

- 0 = DMA operates normally

- bit 11 DMABUSY: DMA Module Busy bit

- 1 = DMA module is active and is transferring data

- 0 = DMA module is disabled and not actively transferring data

- bit 10-0 Unimplemented: Read as '0'

| Bit<br>Range | Bit<br>31/23/15/7          | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3    | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |  |  |  |

|--------------|----------------------------|-------------------|-------------------|-------------------|----------------------|-------------------|------------------|------------------|--|--|--|

| 31:24        | U-0                        | U-0               | U-0               | U-0               | U-0                  | U-0               | U-0              | U-0              |  |  |  |

| 31.24        | —                          |                   |                   | —                 | —                    | _                 |                  | —                |  |  |  |

| 00.40        | R/W-1                      | R/W-1             | R/W-1             | R/W-1             | R/W-1                | R/W-1             | R/W-1            | R/W-1            |  |  |  |

| 23:16        | CHAIRQ<7:0> <sup>(1)</sup> |                   |                   |                   |                      |                   |                  |                  |  |  |  |

| 45.0         | R/W-1                      | R/W-1             | R/W-1             | R/W-1             | R/W-1                | R/W-1             | R/W-1            | R/W-1            |  |  |  |

| 15:8         |                            |                   |                   | CHSIRQ<           | <7:0> <sup>(1)</sup> |                   |                  |                  |  |  |  |

| 7.0          | S-0                        | S-0               | R/W-0             | R/W-0             | R/W-0                | U-0               | U-0              | U-0              |  |  |  |

| 7:0          | CFORCE                     | CABORT            | PATEN             | SIRQEN            | AIRQEN               | _                 | _                | _                |  |  |  |

# REGISTER 10-8: DCHxECON: DMA CHANNEL x EVENT CONTROL REGISTER

| Legend:           | S = Settable bit |                      |                    |

|-------------------|------------------|----------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented b  | it, read as '0'    |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared | x = Bit is unknown |

and set CHAIF flag

# bit 31-24 Unimplemented: Read as '0'

| bit 23-16 | CHAIRQ<7:0>: Channel Transfer Abort IRQ bits <sup>(1)</sup>   |

|-----------|---------------------------------------------------------------|

|           | 11111111 = Interrupt 255 will abort any transfers in progress |

|           | •                                                             |

|           | •                                                             |

|           | •                                                             |

|           |                                                               |

00000001 = Interrupt 1 will abort any transfers in progress and set CHAIF flag 00000000 = Interrupt 0 will abort any transfers in progress and set CHAIF flag

# bit 15-8 CHSIRQ<7:0>: Channel Transfer Start IRQ bits<sup>(1)</sup>

11111111 = Interrupt 255 will initiate a DMA transfer

• 00000001 = Interrupt 1 will initiate a DMA transfer 00000000 = Interrupt 0 will initiate a DMA transfer

### bit 7 CFORCE: DMA Forced Transfer bit

1 = A DMA transfer is forced to begin when this bit is written to a '1'

0 = This bit always reads '0'

### bit 6 CABORT: DMA Abort Transfer bit

- 1 = A DMA transfer is aborted when this bit is written to a '1'

- 0 = This bit always reads '0'

# bit 5 **PATEN:** Channel Pattern Match Abort Enable bit

- 1 = Abort transfer and clear CHEN on pattern match

- 0 = Pattern match is disabled

- bit 4 SIRQEN: Channel Start IRQ Enable bit

- 1 = Start channel cell transfer if an interrupt matching CHSIRQ occurs

- 0 = Interrupt number CHSIRQ is ignored and does not start a transfer

- bit 3 AIRQEN: Channel Abort IRQ Enable bit

- 1 = Channel transfer is aborted if an interrupt matching CHAIRQ occurs

- 0 = Interrupt number CHAIRQ is ignored and does not terminate a transfer

- bit 2-0 Unimplemented: Read as '0'

- Note 1: See Table 7-2: "Interrupt IRQ, Vector, and Bit Location" for the list of available interrupt IRQ sources.

# REGISTER 11-29: USBLPMR2: USB LINK POWER MANAGEMENT CONTROL REGISTER 2

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|

| 31:24        | U-0               | U-0               | U-0 U-0           |                   | U-0               | U-0               | U-0              | U-0              |

| 31.24        | —                 | _                 |                   | _                 |                   | _                 | —                | _                |

| 23:16        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 23.10        | —                 | _                 |                   | _                 |                   | _                 | —                | _                |

| 45.0         | U-0               | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |

| 15:8         | —                 |                   |                   | LF                | PMFADDR<6:        | 0>                |                  |                  |

| 7:0          | U-0               | U-0               | R-0               | R-0, HS           | R-0, HS           | R-0, HS           | R-0, HS          | R-0, HS          |

| 7.0          | _                 |                   | LPMERRIF          | LPMRESIF          | LPMNCIF           | LPMACKIF          | LPMNYIF          | LPMSTIF          |

| Legend:           | HS = Hardware Set |                           |                    |

|-------------------|-------------------|---------------------------|--------------------|

| R = Readable bit  | W = Writable bit  | U = Unimplemented bit, re | ead as '0'         |

| -n = Value at POR | '1' = Bit is set  | '0' = Bit is cleared      | x = Bit is unknown |

bit 31-15 Unimplemented: Read as '0'

bit 14-8 LPMFADDR<6:0>: LPM Payload Function Address bits These bits contain the address of the LPM payload function.

bit 7-6 Unimplemented: Read as '0'

### bit 5 LPMERRIF: LPM Error Interrupt Flag bit (Device mode)

1 = An LPM transaction was received that had a LINKSTATE field that is not supported. The response will be a STALL.

0 =No error condition

#### bit 4 LPMRESIF: LPM Resume Interrupt Flag bit

- 1 = The USB module has resumed (for any reason)

- 0 = No Resume condition

- bit 3 LPMNCIF: LPM NC Interrupt Flag bit

### When in Device mode:

- 1 = The USB module received a LPM transaction and responded with a NYET due to data pending in the RX FIFOs.

- 0 = No NC interrupt condition

When in Host mode:

- 1 = A LPM transaction is transmitted and the device responded with an ACK

- 0 = No NC interrupt condition

### bit 2 LPMACKIF: LPM ACK Interrupt Flag bit

When in Device mode:

- 1 = A LPM transaction was received and the USB Module responded with an ACK

- 0 = No ACK interrupt condition

#### When in Host mode:

1 = The LPM transaction is transmitted and the device responds with an ACK

0 = No ACK interrupt condition

#### bit 1 LPMNYIF: LPM NYET Interrupt Flag bit

#### When in Device mode:

1 = A LPM transaction is received and the USB Module responded with a NYET

0 = No NYET interrupt flag

When in Host mode:

- 1 = A LPM transaction is transmitted and the device responded with an NYET

- 0 = No NYET interrupt flag

# TABLE 12-12: PORTE REGISTER MAP FOR 64-PIN DEVICES ONLY

| ess                         |                                 |           |       |       |       |       |                |       |      | I    | Bits         |              |              |              |              |              |              |              |               |

|-----------------------------|---------------------------------|-----------|-------|-------|-------|-------|----------------|-------|------|------|--------------|--------------|--------------|--------------|--------------|--------------|--------------|--------------|---------------|

| Virtual Address<br>(BF86_#) | Register<br>Name <sup>(1)</sup> | Bit Range | 31/15 | 30/14 | 29/13 | 28/12 | 27/11          | 26/10 | 25/9 | 24/8 | 23/7         | 22/6         | 21/5         | 20/4         | 19/3         | 18/2         | 17/1         | 16/0         | All<br>Resets |

| 0400                        | ANSELE                          | 31:16     | _     |       |       |       |                |       | —    | —    | —            | —            |              |              | —            | _            | —            | —            | 0000          |

| 0.00                        | /                               | 15:0      | _     | -     | —     | _     | —              | _     | —    | —    | ANSE7        | ANSE6        | ANSE5        | ANSE4        | —            | _            | —            | —            | 00F0          |

| 0410                        | TRISE                           | 31:16     | —     | _     | _     | _     | —              | _     | —    | —    | —            | _            | _            | _            | —            | —            | _            | —            | 0000          |

| 0110                        | HUGE                            | 15:0      | —     | —     | —     | _     | —              | _     | —    | —    | TRISE7       | TRISE6       | TRISE5       | TRISE4       | TRISE3       | TRISE2       | TRISE1       | TRISE0       | 00FF          |

| 0420                        | PORTE                           | 31:16     | —     | —     | —     | _     | —              | —     | —    | —    | —            | —            | —            | —            | —            | —            | —            | —            | 0000          |

| 0420                        | TORTE                           | 15:0      | —     | —     | —     | -     | —              | —     | —    | —    | RE7          | RE6          | RE5          | RE4          | RE3          | RE2          | RE1          | RE0          | xxxx          |

| 0430                        | LATE                            | 31:16     | —     | -     | —     | -     | —              | —     | —    | —    | —            | —            | _            | -            | —            | -            | —            | —            | 0000          |

| 0430                        | LAIL                            | 15:0      | Ι     |       | -     |       | -              | —     | —    | —    | LATE7        | LATE6        | LATE5        | LATE4        | LATE3        | LATE2        | LATE1        | LATE0        | xxxx          |

| 0440                        | ODCE                            | 31:16     |       | —     | —     | —     | —              | _     | _    | _    | _            | _            | —            | —            | —            | —            | _            | —            | 0000          |

| 0440                        | ODCE                            | 15:0      | Ι     | _     | —     | _     | —              | _     | _    | _    | ODCE7        | ODCE6        | ODCE5        | ODCE4        | ODCE3        | ODCE2        | ODCE1        | ODCE0        | 0000          |

| 0450                        |                                 | 31:16     | _     | _     | _     | _     | _              | _     | _    | _    | _            | _            | _            | _            | _            | _            | _            | _            | 0000          |

| 0450                        | CNPUE                           | 15:0      | _     |       | _     |       | _              | _     | _    | _    | CNPUE7       | CNPUE6       | CNPUE5       | CNPUE4       | CNPUE3       | CNPUE2       | CNPUE1       | CNPUE0       | 0000          |

| 0.400                       |                                 | 31:16     | _     | _     | _     | _     | _              | _     | _    | —    | _            | _            | _            | -            | —            | -            | —            | _            | 0000          |

| 0460                        | CNPDE                           | 15:0      | _     | _     | _     | _     | —              | _     | —    | —    | CNPDE7       | CNPDE6       | CNPDE5       | CNPDE4       | CNPDE3       | CNPDE2       | CNPDE1       | CNPDE0       | 0000          |

|                             |                                 | 31:16     | _     | _     | _     | _     | —              | _     | —    | —    | —            | —            | _            | _            | —            | _            | —            | —            | 0000          |

| 0470                        | CNCONE                          | 15:0      | ON    | 1     | -     | -     | EDGE<br>DETECT | _     | _    |      | _            | _            | -            | -            | _            | -            | _            | _            | 0000          |

| 0.400                       |                                 | 31:16     | _     |       | _     |       | _              | _     | _    | _    | —            | _            |              | -            | _            |              | _            | _            | 0000          |

| 0480                        | CNENE                           | 15:0      | _     | _     | _     | _     | _              | _     | _    | _    | CNENE7       | CNENE6       | CNENE5       | CNENE4       | CNENE3       | CNENE2       | CNENE1       | CNENE0       | 0000          |

|                             |                                 | 31:16     | _     | _     | _     | _     | —              | _     | _    | —    | —            | —            | _            | _            | —            | _            | —            | —            | 0000          |

| 0490                        | CNSTATE                         | 15:0      | _     |       | _     | _     | _              | _     | _    | _    | CN<br>STATE7 | CN<br>STATE6 | CN<br>STATE5 | CN<br>STATE4 | CN<br>STATE3 | CN<br>STATE2 | CN<br>STATE1 | CN<br>STATE0 | 0000          |

| 0440                        |                                 | 31:16     | _     | _     | _     | _     | _              | _     | _    | _    | _            | _            | _            | _            | _            | _            | _            | _            | 0000          |

| 04A0                        | CNNEE                           | 15:0      | _     | _     | _     | _     | _              | _     | _    | _    | CNNEE7       | CNNEE6       | CNNEE5       | CNNEE4       | CNNEE3       | CNNEE2       | CNNEE1       | CNNEE0       | 0000          |

| 0.450                       |                                 | 31:16     | _     | _     | _     | _     | _              | _     | _    | —    | _            | —            | —            | —            | —            |              | —            | —            | 0000          |

| 04B0                        | CNFE                            | 15:0      | _     | _     | _     | _     | _              | _     | _    | _    | CNFE7        | CNFE6        | CNFE5        | CNFE4        | CNFE3        | CNFE2        | CNFE1        | CNFE0        | 0000          |

| 0.400                       |                                 | 31:16     | _     | _     | _     | _     | _              | _     | _    | —    | _            |              | -            | -            | —            |              | —            | _            | 0000          |

| 04C0                        | SRCON0E                         | 15:0      | _     | _     | _     | _     | _              | _     | _    | _    | _            | _            | _            | _            | SR0E3        | SR0E2        | SR0E1        | SR0E0        | 0000          |

|                             |                                 | 31:16     | _     | _     | _     | _     |                | _     | _    |      | _            | _            | _            | _            |              | _            |              | —            | 0000          |

| 04D0                        | SRCON1E                         | 15:0      | _     | _     | _     | _     | _              | _     | _    | _    | _            | _            | _            | _            | SR1E3        | SR1E2        | SR1E1        | SR1E0        | 0000          |

Legend:

x = Unknown value on Reset; — = Unimplemented, read as '0'; Reset values are shown in hexadecimal. All registers in this table have corresponding CLR, SET and INV registers at its virtual address, plus an offset of 0x4, 0x8 and 0xC, respectively. See Section 12.3 "CLR, SET, and INV Registers" for Note 1: more information.

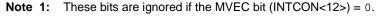

# 15.0 DEADMAN TIMER (DMT)

Note: This data sheet summarizes the features of the PIC32MZ EF family of devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to Section 9. "Watchdog, Deadman, and Power-up Timers" (DS60001114) in the "PIC32 Family Reference Manual", which is available from the Microchip web site (www.microchip.com/PIC32).

The primary function of the Deadman Timer (DMT) is to reset the processor in the event of a software malfunction. The DMT is a free-running instruction fetch timer, which is clocked whenever an instruction fetch occurs until a count match occurs. Instructions are not fetched when the processor is in Sleep mode. The DMT consists of a 32-bit counter with a time-out count match value as specified by the DMTCNT<3:0> bits in the DEVCFG1 Configuration register.

A Deadman Timer is typically used in mission critical and safety critical applications, where any single failure of the software functionality and sequencing must be detected.

Figure 15-1 shows a block diagram of the Deadman Timer module.

# FIGURE 15-1: DEADMAN TIMER BLOCK DIAGRAM

## REGISTER 20-1: SQI1XCON1: SQI XIP CONTROL REGISTER 1 (CONTINUED)

#### bit 5-4 TYPEMODE<1:0>: SQI Type Mode Enable bits

- The boot controller will send the mode in Single Lane, Dual Lane, or Quad Lane.

- 11 = Reserved

- 10 = Quad Lane mode is enabled

- 01 = Dual Lane mode is enabled

- 00 = Single Lane mode is enabled

- bit 3-2 TYPEADDR<1:0>: SQI Type Address Enable bits

The boot controller will send the address in Single Lane, Dual Lane, or Quad Lane.

- 11 = Reserved

- 10 = Quad Lane mode address is enabled

- 01 = Dual Lane mode address is enabled

- 00 = Single Lane mode address is enabled

## bit 1-0 TYPECMD<1:0>: SQI Type Command Enable bits

The boot controller will send the command in Single Lane, Dual Lane, or Quad Lane.

- 11 = Reserved

- 10 =Quad Lane mode command is enabled

- 01 = Dual Lane mode command is enabled

- 00 = Single Lane mode command is enabled

| Bit<br>1/23/15/7<br>U-0<br>U-0<br>U-0 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4                        | Bit<br>27/19/11/3<br>U-0                                                                                                        | Bit<br>26/18/10/2                       | Bit<br>25/17/9/1                                                  | Bit<br>24/16/8/0                                                                 |

|---------------------------------------|-------------------|-------------------|------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------|-------------------------------------------------------------------|----------------------------------------------------------------------------------|

| _                                     | _                 | U-0               | U-0                                      | U-0                                                                                                                             | U-0                                     | U-0                                                               | 11-0                                                                             |

| —<br>U-0                              | -                 | _                 |                                          |                                                                                                                                 |                                         | °                                                                 | 0-0                                                                              |

| U-0                                   | 11.0              |                   |                                          | —                                                                                                                               | —                                       | —                                                                 | —                                                                                |

|                                       | U-0               | U-0               | U-0 U-0 U-0                              |                                                                                                                                 | U-0                                     | U-0                                                               | U-0                                                                              |

| —                                     | _                 | —                 | —                                        | _                                                                                                                               | —                                       | —                                                                 | —                                                                                |

| U-0                                   | U-0               | U-0               | U-0                                      | R/W-0                                                                                                                           | R/W-0                                   | R/W-0                                                             | R/W-0                                                                            |

| —                                     |                   | —                 | —                                        | DMAEISE                                                                                                                         | PKT<br>DONEISE                          | BD<br>DONEISE                                                     | CON<br>THRISE                                                                    |

| R/W-0                                 | R/W-0             | R/W-0             | R/W-0                                    | R/W-0                                                                                                                           | R/W-0                                   | R/W-0                                                             | R/W-0                                                                            |

| CON<br>MPTYISE                        | CON<br>FULLISE    | RX<br>THRISE      | RX<br>FULLISE                            | RX<br>EMPTYISE                                                                                                                  | TX<br>THRISE                            | TX<br>FULLISE                                                     | TX<br>EMPTYISE                                                                   |

| Ν                                     | R/W-0<br>CON      | R/W-0R/W-0CONCON  | — — —<br>R/W-0 R/W-0 R/W-0<br>CON CON RX | -         -         -           R/W-0         R/W-0         R/W-0         R/W-0           CON         CON         RX         RX | DMAEISER/W-0R/W-0R/W-0R/W-0CONCONRXRXRX | DMAEISEPKT<br>DONEISER/W-0R/W-0R/W-0R/W-0R/W-0R/W-0CONCONRXRXRXRX | DMAEISEPKT<br>DONEISEBD<br>DONEISER/W-0R/W-0R/W-0R/W-0R/W-0R/W-0CONCONRXRXRXTXTX |

# REGISTER 20-22: SQI1INTSIGEN: SQI INTERRUPT SIGNAL ENABLE REGISTER

# Legend:

| R = Readable bit  | W = Writable bit | U = Unimplemented bi | d bit, read as '0' |  |  |  |  |

|-------------------|------------------|----------------------|--------------------|--|--|--|--|

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared | x = Bit is unknown |  |  |  |  |

### bit 31-12 Unimplemented: Read as '0'

| bit 11 | DMAEISE: DMA Bus Error Interrupt Signal Enable bit                                                       |

|--------|----------------------------------------------------------------------------------------------------------|

|        | 1 = Interrupt signal is enabled                                                                          |

|        | 0 = Interrupt signal is disabled                                                                         |

| bit 10 | PKTDONEISE: Receive Error Interrupt Signal Enable bit                                                    |

|        | 1 = Interrupt signal is enabled                                                                          |

|        | 0 = Interrupt signal is disabled                                                                         |

| bit 9  | BDDONEISE: Transmit Error Interrupt Signal Enable bit                                                    |

|        | <ol> <li>Interrupt signal is enabled</li> </ol>                                                          |

|        | 0 = Interrupt signal is disabled                                                                         |

| bit 8  | CONTHRISE: Control Buffer Threshold Interrupt Signal Enable bit                                          |

|        | 1 = Interrupt signal is enabled                                                                          |

|        | 0 = Interrupt signal is disabled                                                                         |

| bit 7  | CONEMPTYISE: Control Buffer Empty Interrupt Signal Enable bit                                            |

|        | 1 = Interrupt signal is enabled                                                                          |

| 1.11.0 | 0 = Interrupt signal is disabled                                                                         |

| bit 6  | CONFULLISE: Control Buffer Full Interrupt Signal Enable bit                                              |

|        | <ul> <li>1 = Interrupt signal is enabled</li> <li>0 = Interrupt signal is disabled</li> </ul>            |

| hit E  |                                                                                                          |

| bit 5  | <b>RXTHRISE:</b> Receive Buffer Threshold Interrupt Signal Enable bit<br>1 = Interrupt signal is enabled |

|        | 0 = Interrupt signal is disabled                                                                         |

| bit 4  | <b>RXFULLISE:</b> Receive Buffer Full Interrupt Signal Enable bit                                        |

|        | 1 = Interrupt signal is enabled                                                                          |

|        | 0 = Interrupt signal is disabled                                                                         |

| bit 3  | <b>RXEMPTYISE:</b> Receive Buffer Empty Interrupt Signal Enable bit                                      |

|        | 1 = Interrupt signal is enabled                                                                          |

|        | 0 = Interrupt signal is disabled                                                                         |

| bit 2  | TXTHRISE: Transmit Buffer Threshold Interrupt Signal Enable bit                                          |

|        | 1 = Interrupt signal is enabled                                                                          |

|        | 0 = Interrupt signal is disabled                                                                         |

| bit 1  | TXFULLISE: Transmit Buffer Full Interrupt Signal Enable bit                                              |

|        | 1 = Interrupt signal is enabled                                                                          |

|        | 0 = Interrupt signal is disabled                                                                         |

| bit 0  | TXEMPTYISE: Transmit Buffer Empty Interrupt Signal Enable bit                                            |

|        | 1 = Interrupt signal is enabled                                                                          |

|        | 0 = Interrupt signal is disabled                                                                         |

|        |                                                                                                          |

# 23.1 PMP Control Registers

# TABLE 23-1: PARALLEL MASTER PORT REGISTER MAP

| ess                         |                                 | ő             |        |                        |       |       |           |        |        | В      | its     |        |      |       |        |           |           |         | \$         |

|-----------------------------|---------------------------------|---------------|--------|------------------------|-------|-------|-----------|--------|--------|--------|---------|--------|------|-------|--------|-----------|-----------|---------|------------|

| Virtual Address<br>(BF82_#) | Register<br>Name <sup>(1)</sup> | Bit Range     | 31/15  | 30/14                  | 29/13 | 28/12 | 27/11     | 26/10  | 25/9   | 24/8   | 23/7    | 22/6   | 21/5 | 20/4  | 19/3   | 18/2      | 17/1      | 16/0    | All Resets |

| E000                        | PMCON                           | 31:16         |        | —                      | —     |       | —         | —      | —      |        | RDSTART |        | —    |       | _      |           | DUALBUF   | _       | 0000       |

| LUUU                        | FINCON                          | 15:0          | ON     | —                      | SIDL  | ADRMU | JX<1:0>   | PMPTTL | PTWREN | PTRDEN | CSF     | <1:0>  | ALP  | CS2P  | CS1P   |           | WRSP      | RDSP    | 0000       |

| E010                        | PMMODE                          | 31:16         | _      | —                      | —     | _     | —         | —      |        | _      |         | —      | —    | —     | —      | _         | —         | _       | 0000       |

| 2010                        | _                               | 15:0          | BUSY   | IRQM                   | <1:0> | INCM  | <1:0>     | MODE16 | MODE   | <1:0>  | WAITE   | 3<1:0> |      | WAITN | /<3:0> |           | WAITE     | <1:0>   | 0000       |

|                             |                                 | 31:16         | _      | —                      | —     | —     |           | —      | —      | —      | —       | —      | —    | —     | —      | —         | —         | _       | 0000       |

| E020                        | PMADDR                          | 15:0          | CS2    |                        |       |       |           |        |        |        |         | 0000   |      |       |        |           |           |         |            |

|                             |                                 |               | ADDR15 | ADDR14                 |       |       |           | -      |        |        |         |        |      |       |        |           |           |         | 0000       |

| E030                        | PMDOUT                          | 31:16         | _      | —                      | —     | —     | _         | —      | —      | —      |         | —      | _    | —     | —      | —         | —         | _       | 0000       |

|                             |                                 | 15:0          |        |                        |       |       |           |        |        |        | 0000    |        |      |       |        |           |           |         |            |

| E040                        | PMDIN                           | 31:16<br>15:0 | —      | —                      | _     | _     |           | _      | _      |        | -       | —      | _    | —     | —      | _         | —         | _       | 0000       |

|                             |                                 | 31:16         |        |                        |       |       |           |        |        | DATAI  | l<15:0> |        |      |       |        |           |           |         | 0000       |

| E050                        | PMAEN                           | 15:0          | -      | _                      | —     | _     | _         | —      | _      |        |         | _      | —    | —     | —      |           | —         | _       |            |

|                             |                                 |               |        |                        |       |       |           |        |        |        | <15:0>  |        |      |       |        |           |           |         | 0000       |

| E060                        | PMSTAT                          | 31:16<br>15:0 | IBF    | —<br>IBOV              | _     | _     | IB3F      | IB2F   | IB1F   | IB0F   |         |        |      | _     | OB3E   | —<br>OB2E | —<br>OB1E |         | 0000       |

|                             |                                 | 31:16         |        | <u>іво</u> у           |       |       | івэг<br>— |        |        |        |         |        |      |       |        |           |           | <u></u> | 008F       |

| E070                        | PMWADDR                         | 51.10         | WCS2   | WCS1                   |       |       |           |        | _      |        | _       |        |      |       |        |           | _         |         | 0000       |

| 2070                        |                                 | 15:0          |        |                        |       |       |           |        |        |        |         | 0000   |      |       |        |           |           |         |            |

|                             |                                 | 31:16         |        |                        |       | _     |           | _      | _      | _      |         | <13:0> | _    | _     | _      | _         | _         | _       | 0000       |

| E090                        | PMRADDR                         | 51.10         | RCS2   | RCS1                   |       |       |           |        |        |        |         |        |      |       |        |           | _         |         | 0000       |

| E080                        | FINIKADDR                       | 15:0          |        | RADDR14                |       |       |           |        |        |        | RADDF   |        |      |       |        |           |           |         | 0000       |

|                             |                                 | 31:16         | 31:16  |                        |       | _     | _         |        |        |        |         | <13:0> |      | _     |        | _         |           | _       | 0000       |

| E090                        | PMRDIN                          |               |        |                        |       |       |           |        |        |        |         |        |      |       |        |           |           |         |            |

|                             |                                 | 15:0          | 15:0   | 5:0 RDATAIN<15:0> 0000 |       |       |           |        |        |        |         |        |      |       |        |           |           |         |            |

Legend: x = unknown value on Reset; --- = unimplemented, read as '0'. Reset values are shown in hexadecimal.

Note 1: All registers in this table have corresponding CLR, SET and INV registers at their virtual addresses, plus offsets of 0x4, 0x8 and 0xC, respectively. See Section 12.3 "CLR, SET, and INV Registers" for more information.

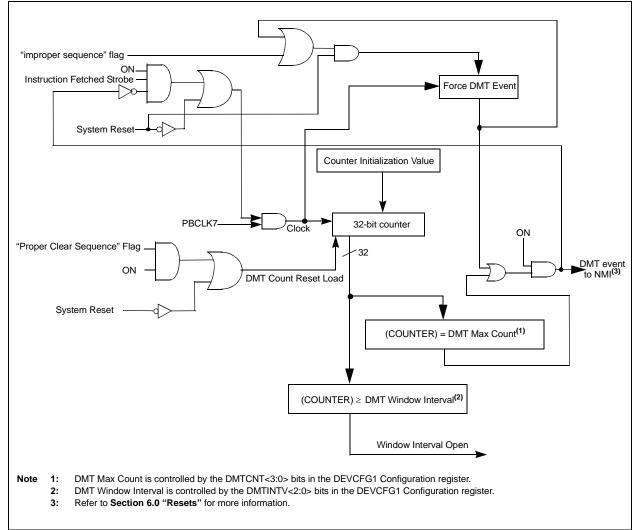

# 24.0 EXTERNAL BUS INTERFACE (EBI)

Note: This data sheet summarizes the features of the PIC32MZ EF family of devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to Section 47. "External Bus Interface (EBI)" (DS60001245) in the "PIC32 Family Reference Manual", which is available from the Microchip web site (www.microchip.com/PIC32).

The External Bus Interface (EBI) module provides a high-speed, convenient way to interface external parallel memory devices to the PIC32MZ EF family device.

With the EBI module, it is possible to connect asynchronous SRAM and NOR Flash devices, as well as non-memory devices such as camera sensors and LCDs.

The features of the EBI module depend on the pin count of the PIC32MZ EF device, as shown in Table 24-1.

Note: The EBI module is not available on 64-pin devices.

# TABLE 24-1: EBI MODULE FEATURES

| Feature                   | Num | Number of Device<br>Pins |     |  |  |  |  |  |

|---------------------------|-----|--------------------------|-----|--|--|--|--|--|

|                           | 100 | 124                      | 144 |  |  |  |  |  |

| Async SRAM                | Y   | Y                        | Y   |  |  |  |  |  |

| Async NOR Flash           | Y   | Y                        | Y   |  |  |  |  |  |

| Available address lines   | 20  | 20                       | 24  |  |  |  |  |  |

| 8-bit data bus support    | Y   | Y                        | Y   |  |  |  |  |  |

| 16-bit data bus support   | Y   | Y                        | Y   |  |  |  |  |  |

| Available Chip Selects    | 1   | 1                        | 4   |  |  |  |  |  |

| Timing mode sets          | 3   | 3                        | 3   |  |  |  |  |  |

| 8-bit R/W from 16-bit bus | N   | Ν                        | Y   |  |  |  |  |  |

| Non-memory device         | Y   | Y                        | Y   |  |  |  |  |  |

| LCD                       | Y   | Y                        | Y   |  |  |  |  |  |

Note: Once the EBI module is configured, external devices will be memory mapped and can be access from KSEG2 memory space (see Figure 4-1 through Figure 4-4 in Section 4.0 "Memory Organization" for more information). The MMU must be enabled and the TLB must be set up to access this memory (refer to Section 50. "CPU for Devices with MIPS32<sup>®</sup> microAptiv<sup>™</sup> and M-Class Cores" (DS60001192) of the *"PIC32 Family Reference Manual"* for more information).

# FIGURE 24-1: EBI SYSTEM BLOCK DIAGRAM

# 32.1 Comparator Voltage Reference Control Registers

# TABLE 32-1: COMPARATOR VOLTAGE REFERENCE REGISTER MAP

| ess                       |                                 | æ         |       | Bits  |       |       |       |       |      |      |      |       |      |       | s    |      |      |      |            |

|---------------------------|---------------------------------|-----------|-------|-------|-------|-------|-------|-------|------|------|------|-------|------|-------|------|------|------|------|------------|

| Virtual Addre<br>(BF80_#) | Register<br>Name <sup>(1)</sup> | Bit Range | 31/15 | 30/14 | 29/13 | 28/12 | 27/11 | 26/10 | 25/9 | 24/8 | 23/7 | 22/6  | 21/5 | 20/4  | 19/3 | 18/2 | 17/1 | 16/0 | All Resets |

| 0500                      | CVRCON                          | 31:16     | _     | —     | —     | —     | —     | -     | —    | —    | —    | —     | —    | —     | —    | —    | —    | _    | 0000       |

| UEUU                      | CVRCON                          | 15:0      | ON    | —     | _     | _     | —     | —     | _    | _    | —    | CVROE | CVRR | CVRSS |      | CVR< | 3:0> |      | 0000       |

Legend: x = unknown value on Reset; - = unimplemented, read as '0'. Reset values are shown in hexadecimal.

Note 1: The register in this table has corresponding CLR, SET and INV registers at their virtual addresses, plus offsets of 0x4, 0x8 and 0xC, respectively. See Section 12.3 "CLR, SET, and INV Registers" for more information.

| AC CHA        | RACTERISTI  | CS                              | $\begin{tabular}{lllllllllllllllllllllllllllllllllll$ |                     |            |     |                           |  |  |  |

|---------------|-------------|---------------------------------|-------------------------------------------------------|---------------------|------------|-----|---------------------------|--|--|--|

| Param.<br>No. | Symbol      | Characteristic <sup>(1,3)</sup> | Min.                                                  | Тур. <sup>(2)</sup> | Conditions |     |                           |  |  |  |

| SQ10          | FCLK        | Serial Clock Frequency (1/TsQI) | —                                                     | 66                  | _          | MHz | DMA mode Read, SPI mode 0 |  |  |  |

|               |             |                                 |                                                       | 33                  | _          | MHz | DMA mode Read, SPI mode 3 |  |  |  |

|               |             |                                 |                                                       | 100                 | _          | MHz | PIO mode Write            |  |  |  |

| SQ11          | Тѕскн       | Serial Clock High Time          | 5                                                     |                     | _          | ns  | —                         |  |  |  |

| SQ12          | TSCKL       | Serial Clock Low Time           | 5                                                     |                     | _          | ns  | _                         |  |  |  |

| SQ13          | TSCKR       | Serial Clock Rise Time          | _                                                     |                     | _          | ns  | See parameter DO31        |  |  |  |