Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFl

| Product Status             | Active                                                                           |

|----------------------------|----------------------------------------------------------------------------------|

| Core Processor             | MIPS32® M-Class                                                                  |

| Core Size                  | 32-Bit Single-Core                                                               |

| Speed                      | 200MHz                                                                           |

| Connectivity               | CANbus, EBI/EMI, Ethernet, I <sup>2</sup> C, PMP, SPI, SQI, UART/USART, USB OTG  |

| Peripherals                | Brown-out Detect/Reset, DMA, I <sup>2</sup> S, POR, PWM, WDT                     |

| Number of I/O              | 120                                                                              |

| Program Memory Size        | 512KB (512K x 8)                                                                 |

| Program Memory Type        | FLASH                                                                            |

| EEPROM Size                |                                                                                  |

| RAM Size                   | 128K x 8                                                                         |

| Voltage - Supply (Vcc/Vdd) | 2.1V ~ 3.6V                                                                      |

| Data Converters            | A/D 48x12b                                                                       |

| Oscillator Type            | Internal                                                                         |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                                |

| Mounting Type              | Surface Mount                                                                    |

| Package / Case             | 144-LQFP                                                                         |

| Supplier Device Package    | 144-LQFP (20x20)                                                                 |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic32mz0512eff144-i-pl |

|                            |                                                                                  |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

#### TABLE 5: **PIN NAMES FOR 144-PIN DEVICES (CONTINUED)**

#### 144-PIN LQFP AND TQFP (TOP VIEW)

#### PIC32MZ0512EF(E/F/K)144 PIC32MZ1024EF(G/H/M)144 PIC32MZ1024EF(E/F/K)144 PIC32MZ2048EF(G/H/M)144

144

|               |                             |               | 1                       |

|---------------|-----------------------------|---------------|-------------------------|

| Pin<br>Number | Full Pin Name               | Pin<br>Number | Full Pin Name           |

| 73            | VBUS                        | 109           | RPD1/SCK1/RD1           |

| 74            | VUSB3V3                     | 110           | EBID14/RPD2/PMD14/RD2   |

| 75            | Vss                         | 111           | EBID15/RPD3/PMD15/RD3   |

| 76            | D-                          | 112           | EBID12/RPD12/PMD12/RD12 |

| 77            | D+                          | 113           | EBID13/PMD13/RD13       |

| 78            | RPF3/USBID/RF3              | 114           | ETXERR/RJ0              |

| 79            | SDA3/RPF2/RF2               | 115           | EMDIO/RJ1               |

| 80            | SCL3/RPF8/RF8               | 116           | EBIRDY3/RJ2             |

| 81            | ERXD0/RH8                   | 117           | EBIA22/RJ3              |

| 82            | ERXD3/RH9                   | 118           | SQICS0/RPD4/RD4         |

| 83            | ECOL/RH10                   | 119           | SQICS1/RPD5/RD5         |

| 84            | EBIRDY2/RH11                | 120           | ETXEN/RPD6/RD6          |

| 85            | SCL2/RA2                    | 121           | ETXCLK/RPD7/RD7         |

| 86            | EBIRDY1/SDA2/RA3            | 122           | Vdd                     |

| 87            | EBIA14/PMCS1/PMA14/RA4      | 123           | Vss                     |

| 88            | Vdd                         | 124           | EBID11/RPF0/PMD11/RF0   |

| 89            | Vss                         | 125           | EBID10/RPF1/PMD10/RF1   |

| 90            | EBIA9/RPF4/SDA5/PMA9/RF4    | 126           | EBIA21/RK7              |

| 91            | EBIA8/RPF5/SCL5/PMA8/RF5    | 127           | EBID9/RPG1/PMD9/RG1     |

| 92            | EBIA18/RK4                  | 128           | EBID8/RPG0/PMD8/RG0     |

| 93            | EBIA19/RK5                  | 129           | TRCLK/SQICLK/RA6        |

| 94            | EBIA20/RK6                  | 130           | TRD3/SQID3/RA7          |

| 95            | RPA14/SCL1/RA14             | 131           | EBICS0/RJ4              |

| 96            | RPA15/SDA1/RA15             | 132           | EBICS1/RJ5              |

| 97            | EBIA15/RPD9/PMCS2/PMA15/RD9 | 133           | EBICS2/RJ6              |

| 98            | RPD10/SCK4/RD10             | 134           | EBICS3/RJ7              |

| 99            | EMDC/RPD11/RD11             | 135           | EBID0/PMD0/RE0          |

| 100           | ECRS/RH12                   | 136           | Vss                     |

| 101           | ERXDV/ECRSDV/RH13           | 137           | Vdd                     |

| 102           | RH14                        | 138           | EBID1/PMD1/RE1          |

| 103           | EBIA23/RH15                 | 139           | TRD2/SQID2/RG14         |

| 104           | RPD0/RTCC/INT0/RD0          | 140           | TRD1/SQID1/RG12         |

| 105           | SOSCI/RPC13/RC13            | 141           | TRD0/SQID0/RG13         |

| 106           | SOSCO/RPC14/T1CK/RC14       | 142           | EBID2/PMD2/RE2          |

| 107           | Vdd                         | 143           | EBID3/RPE3/PMD3/RE3     |

| 108           | Vss                         | 144           | EBID4/AN18/PMD4/RE4     |

Note 1: The RPn pins can be used by remappable peripherals. See Table 1 for the available peripherals and Section 12.4 "Peripheral Pin Select (PPS)" for restrictions.

2: Every I/O port pin (RAx-RKx) can be used as a change notification pin (CNAx-CNKx). See Section 12.0 "I/O Ports" for more information.

3: Shaded pins are 5V tolerant.

### TABLE 4-6: SYSTEM BUS TARGETS AND ASSOCIATED PROTECTION REGISTERS

|                  |                                                                        |          |                                             | SBTxREC                      | SBTxRD                                     | y Register       | SBTxWRy Register  |                   |         |                                                                 |         |                                                                  |

|------------------|------------------------------------------------------------------------|----------|---------------------------------------------|------------------------------|--------------------------------------------|------------------|-------------------|-------------------|---------|-----------------------------------------------------------------|---------|------------------------------------------------------------------|

| Target<br>Number | Target Description <sup>(5)</sup>                                      | Name     | Region Base<br>(BASE<21:0>)<br>(see Note 2) | Physical<br>Start<br>Address | Region Size<br>(SIZE<4:0>)<br>(see Note 3) | Region<br>Size   | Priority<br>(PRI) | Priority<br>Level | Name    | Read<br>Permission<br>(GROUP3,<br>GROUP2,<br>GROUP1,<br>GROUP0) | Name    | Write<br>Permissior<br>(GROUP3,<br>GROUP2,<br>GROUP1,<br>GROUP0) |

| <u>^</u>         | System Bus                                                             | SBT0REG0 | R                                           | 0x1F8F0000                   | R                                          | 64 KB            | —                 | 0                 | SBT0RD0 | R/W <sup>(1)</sup>                                              | SBT0WR0 | R/W <sup>(1)</sup>                                               |

| 0                |                                                                        | SBT0REG1 | R                                           | 0x1F8F8000                   | R                                          | 32 KB            | —                 | 3                 | SBT0RD1 | R/W <sup>(1)</sup>                                              | SBT0WR1 | R/W <sup>(1)</sup>                                               |

|                  | Flash Memory <sup>(6)</sup> :                                          | SBT1REG0 | R                                           | 0x1D000000                   | R <sup>(4)</sup>                           | R <sup>(4)</sup> | —                 | 0                 | SBT1RD0 | R/W <sup>(1)</sup>                                              | SBT1WR0 | 0, 0, 0, 0                                                       |

|                  | Program Flash<br>Boot Flash                                            | SBT1REG2 | R                                           | 0x1F8E0000                   | R                                          | 4 KB             | 1                 | 2                 | SBT1RD2 | R/W <sup>(1)</sup>                                              | SBT1WR2 | R/W <sup>(1)</sup>                                               |

|                  | Prefetch Module                                                        | SBT1REG3 | R/W                                         | R/W                          | R/W                                        | R/W              | 1                 | 2                 | SBT1RD3 | R/W <sup>(1)</sup>                                              | SBT1WR3 | 0, 0, 0, 0                                                       |

| 4                |                                                                        | SBT1REG4 | R/W                                         | R/W                          | R/W                                        | R/W              | 1                 | 2                 | SBT1RD4 | R/W <sup>(1)</sup>                                              | SBT1WR4 | 0, 0, 0, 0                                                       |

| 1                |                                                                        | SBT1REG5 | R/W                                         | R/W                          | R/W                                        | R/W              | 1                 | 2                 | SBT1RD5 | R/W <sup>(1)</sup>                                              | SBT1WR5 | 0, 0, 0, 0                                                       |

|                  |                                                                        | SBT1REG6 | R/W                                         | R/W                          | R/W                                        | R/W              | 1                 | 2                 | SBT1RD6 | R/W <sup>(1)</sup>                                              | SBT1WR6 | 0, 0, 0, 0                                                       |

|                  |                                                                        | SBT1REG7 | R/W                                         | R/W                          | R/W                                        | R/W              | 0                 | 1                 | SBT1RD7 | R/W <sup>(1)</sup>                                              | SBT1WR7 | 0, 0, 0, 0                                                       |

|                  |                                                                        | SBT1REG8 | R/W                                         | R/W                          | R/W                                        | R/W              | 0                 | 1                 | SBT1RD8 | R/W <sup>(1)</sup>                                              | SBT1WR8 | 0, 0, 0, 0                                                       |

|                  | RAM Bank 1 Memory                                                      | SBT2REG0 | R                                           | 0x00000000                   | R <sup>(4)</sup>                           | R <sup>(4)</sup> | _                 | 0                 | SBT2RD0 | R/W <sup>(1)</sup>                                              | SBT2WR0 | R/W <sup>(1)</sup>                                               |

| 2                |                                                                        | SBT2REG1 | R/W                                         | R/W                          | R/W                                        | R/W              | —                 | 3                 | SBT2RD1 | R/W <sup>(1)</sup>                                              | SBT2WR1 | R/W <sup>(1)</sup>                                               |

|                  |                                                                        | SBT2REG2 | R/W                                         | R/W                          | R/W                                        | R/W              | 0                 | 1                 | SBT2RD2 | R/W <sup>(1)</sup>                                              | SBT2WR2 | R/W <sup>(1)</sup>                                               |

|                  | RAM Bank 2 Memory                                                      | SBT3REG0 | R <sup>(4)</sup>                            | R <sup>(4)</sup>             | R <sup>(4)</sup>                           | R <sup>(4)</sup> | —                 | 0                 | SBT3RD0 | R/W <sup>(1)</sup>                                              | SBT3WR0 | R/W <sup>(1)</sup>                                               |

| 3                |                                                                        | SBT3REG1 | R/W                                         | R/W                          | R/W                                        | R/W              | —                 | 3                 | SBT3RD1 | R/W <sup>(1)</sup>                                              | SBT3WR1 | R/W <sup>(1)</sup>                                               |

|                  |                                                                        | SBT3REG2 | R/W                                         | R/W                          | R/W                                        | R/W              | 0                 | 1                 | SBT3RD2 | R/W <sup>(1)</sup>                                              | SBT3WR2 | R/W <sup>(1)</sup>                                               |

| 4                | External Memory via EBI and EBI Module <sup>(6)</sup>                  | SBT4REG0 | R                                           | 0x20000000                   | R                                          | 64 MB            | —                 | 0                 | SBT4RD0 | R/W <sup>(1)</sup>                                              | SBT4WR0 | R/W <sup>(1)</sup>                                               |

| 4                | Module                                                                 | SBT4REG2 | R                                           | 0x1F8E1000                   | R                                          | 4 KB             | 0                 | 1                 | SBT4RD2 | R/W <sup>(1)</sup>                                              | SBT4WR2 | R/W <sup>(1)</sup>                                               |

|                  | Peripheral Set 1:<br>System Control                                    | SBT5REG0 | R                                           | 0x1F800000                   | R                                          | 128 KB           | _                 | 0                 | SBT5RD0 | R/W <sup>(1)</sup>                                              | SBT5WR0 | R/W <sup>(1)</sup>                                               |

|                  | Flash Control                                                          | SBT5REG1 | R/W                                         | R/W                          | R/W                                        | R/W              | —                 | 3                 | SBT5RD1 | R/W <sup>(1)</sup>                                              | SBT5WR1 | R/W <sup>(1)</sup>                                               |

| 5                | DMT/WDT<br>RTCC<br>CVR<br>PPS Input<br>PPS Output<br>Interrupts<br>DMA | SBT5REG2 | R/W                                         | R/W                          | R/W                                        | R/W              | 0                 | 1                 | SBT5RD2 | R/W <sup>(1)</sup>                                              | SBT5WR2 | R/W <sup>(1)</sup>                                               |

**Note** 1: Reset values for these bits are '0', '1', '1', '1', respectively.

2: The BASE<21:0> bits must be set to the corresponding Physical Address and right shifted by 10 bits. For Read-only bits, this value is set by hardware on Reset.

3: The SIZE<4:0> bits must be set to the corresponding Region Size, based on the following formula: Region Size = 2<sup>(SIZE-1)</sup> x 1024 bytes. For read-only bits, this value is set by hardware on Reset.

4: Refer to the Device Memory Maps (Figure 4-1 through Figure 4-4) for specific device memory sizes and start addresses.

5: See Table 4-1for information on specific target memory size and start addresses.

6: The SBTxREG1 SFRs are reserved, and therefore, are not listed in this table for this target.

## 7.1 CPU Exceptions

CPU coprocessor 0 contains the logic for identifying and managing exceptions. Exceptions can be caused by a variety of sources, including boundary cases in data, external events or program errors. Table 7-1 lists the exception types in order of priority.

# TABLE 7-1: MIPS32<sup>®</sup> M-CLASS MICROPROCESSOR CORE EXCEPTION TYPES

| Exception Type<br>(In Order of<br>Priority) | Description                                                                                                                      | Branches to Bits Set              |                  | Debug Bits<br>Set | EXCCODE | XC32 Function Name         |

|---------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------|-----------------------------------|------------------|-------------------|---------|----------------------------|

|                                             |                                                                                                                                  | Highest Priority                  |                  |                   |         |                            |

| Reset                                       | Assertion MCLR or a Power-on Reset (POR).                                                                                        | 0xBFC0_0000                       | BEV, ERL         | —                 | _       | _on_reset                  |

| Soft Reset                                  | Assertion of a software Reset.                                                                                                   | 0xBFC0_0000                       | BEV, SR,<br>ERL  | —                 | —       | _on_reset                  |

| DSS                                         | EJTAG debug single step.                                                                                                         | 0xBFC0_0480                       | —                | DSS               | _       | —                          |

| DINT                                        | EJTAG debug interrupt. Caused by the assertion of the external EJ_DINT input or by setting the EjtagBrk bit in the ECR register. | 0xBFC0_0480                       | —                | DINT              | —       | _                          |

| NMI                                         | Assertion of NMI signal.                                                                                                         | 0xBFC0_0000                       | BEV, NMI,<br>ERL | —                 | —       | _nmi_handler               |

| Machine Check                               | TLB write that conflicts with an existing entry.                                                                                 | EBASE+0x180                       | MCHECK,<br>EXL   | —                 | 0x18    | _general_exception_handler |

| Interrupt                                   | Assertion of unmasked hardware or software inter-<br>rupt signal.                                                                | See Table 7-2.                    | IPL<2:0>         |                   | 0x00    | See Table 7-2.             |

| Deferred Watch                              | Deferred watch (unmasked by K DM=>!(K DM) transition).                                                                           | EBASE+0x180                       | WP, EXL          |                   | 0x17    | _general_exception_handler |

| DIB                                         | EJTAG debug hardware instruction break matched.                                                                                  | 0xBFC0_0480                       | —                | DIB               | _       |                            |

| WATCH                                       | A reference to an address that is in one of the Watch registers (fetch).                                                         | EBASE+0x180                       | EXL              | —                 | 0x17    | _general_exception_handler |

| AdEL                                        | Fetch address alignment error. Fetch reference to protected address.                                                             | EBASE+0x180                       | EXL              | —                 | 0x04    | _general_exception_handler |

| TLBL                                        | Fetch TLB miss or fetch TLB hit to page with $V = 0$ .                                                                           | EBASE if Status.EXL = 0           | _                | —                 | 0x02    | —                          |

|                                             |                                                                                                                                  | EBASE+0x180 if<br>Status.EXL == 1 | —                |                   | 0x02    | _general_exception_handler |

| TLBL Execute<br>Inhibit                     | An instruction fetch matched a valid TLB entry that had the XI bit set.                                                          | EBASE+0x180                       | EXL              | —                 | 0x14    | _general_exception_handler |

| IBE                                         | Instruction fetch bus error.                                                                                                     | EBASE+0x180                       | EXL              | —                 | 0x06    | _general_exception_handler |

## **REGISTER 7-2:** PRISS: PRIORITY SHADOW SELECT REGISTER (CONTINUED) bit 15-12 PRI3SS<3:0>: Interrupt with Priority Level 3 Shadow Set bits<sup>(1)</sup> 1xxx = Reserved (by default, an interrupt with a priority level of 3 uses Shadow Set 0) 0111 = Interrupt with a priority level of 3 uses Shadow Set 7 0110 = Interrupt with a priority level of 3 uses Shadow Set 6 0001 = Interrupt with a priority level of 3 uses Shadow Set 1 0000 = Interrupt with a priority level of 3 uses Shadow Set 0 bit 11-8 **PRI2SS<3:0>:** Interrupt with Priority Level 2 Shadow Set bits<sup>(1)</sup> 1xxx = Reserved (by default, an interrupt with a priority level of 2 uses Shadow Set 0) 0111 = Interrupt with a priority level of 2 uses Shadow Set 7 0110 = Interrupt with a priority level of 2 uses Shadow Set 6 0001 = Interrupt with a priority level of 2 uses Shadow Set 1 0000 = Interrupt with a priority level of 2 uses Shadow Set 0 PRI1SS<3:0>: Interrupt with Priority Level 1 Shadow Set bits<sup>(1)</sup> bit 7-4 1xxx = Reserved (by default, an interrupt with a priority level of 1 uses Shadow Set 0) 0111 = Interrupt with a priority level of 1 uses Shadow Set 7 0110 = Interrupt with a priority level of 1 uses Shadow Set 6 0001 = Interrupt with a priority level of 1 uses Shadow Set 1 0000 = Interrupt with a priority level of 1 uses Shadow Set 0 bit 3-1 Unimplemented: Read as '0' bit 0 SS0: Single Vector Shadow Register Set bit 1 = Single vector is presented with a shadow set 0 = Single vector is not presented with a shadow set

**Note 1:** These bits are ignored if the MVEC bit (INTCON<12>) = 0.

## 8.0 OSCILLATOR CONFIGURATION

| Note: | This data sheet summarizes the           |

|-------|------------------------------------------|

|       | features of the PIC32MZ EF family of     |

|       | devices. It is not intended to be a      |

|       | comprehensive reference source. To       |

|       | complement the information in this data  |

|       | sheet, refer to Section 42. "Oscillators |

|       | with Enhanced PLL" (DS60001250) in       |

|       | the "PIC32 Family Reference Manual",     |

|       | which is available from the Microchip    |

|       | web site (www.microchip.com/PIC32).      |

The PIC32MZ EF oscillator system has the following modules and features:

- A total of five external and internal oscillator options as clock sources

- On-Chip PLL with user-selectable input divider, multiplier and output divider to boost operating frequency on select internal and external oscillator sources

- On-Chip user-selectable divisor postscaler on select oscillator sources

- Software-controllable switching between various clock sources

- A Fail-Safe Clock Monitor (FSCM) that detects clock failure and permits safe application recovery or shutdown with dedicated Back-up FRC (BFRC)

- Dedicated On-Chip PLL for USB peripheral

- Flexible reference clock output

- Multiple clock branches for peripherals for better performance flexibility

- · Clock switch/slew control with output divider

A block diagram of the oscillator system is shown in Figure 8-1. The clock distribution is provided in Table 8-1.

Note: Devices that support 252 MHz operation should be configured for SYSCLK <= 200 MHz operation. Adjust the dividers of the PBCLKs, and then increase the SYSCLK to the desired speed.

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|

| 04.04        | R-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 31:24        | RDWR              | _                 | _                 | _                 | —                 | —                 | —                | —                |

| 23:16        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 23.10        | _                 | _                 |                   |                   | —                 |                   | —                | —                |

| 45.0         | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 15:8         | _                 | _                 | _                 | _                 | —                 | _                 | —                | —                |

| 7.0          | U-0               | U-0               | U-0               | U-0               | U-0               | R-0               | R-0              | R-0              |

| 7:0          |                   |                   |                   |                   |                   | [                 | DMACH<2:0>       | <b>&gt;</b>      |

#### REGISTER 10-2: DMASTAT: DMA STATUS REGISTER

## Legend:

| 0                 |                               |                      |                    |

|-------------------|-------------------------------|----------------------|--------------------|

| R = Readable bit  | Readable bit W = Writable bit |                      | ead as '0'         |

| -n = Value at POR | '1' = Bit is set              | '0' = Bit is cleared | x = Bit is unknown |

bit 31 RDWR: Read/Write Status bit

1 = Last DMA bus access when an error was detected was a read 0 = Last DMA bus access when an error was detected was a write

bit 30-3 Unimplemented: Read as '0'

bit 2-0 **DMACH<2:0>:** DMA Channel bits These bits contain the value of the most recent active DMA channel when an error was detected.

### REGISTER 10-3: DMAADDR: DMA ADDRESS REGISTER

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |  |  |  |  |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|--|--|--|--|

| 04-04        | R-0               | R-0               | R-0               | R-0               | R-0               | R-0               | R-0              | R-0              |  |  |  |  |

| 31:24        |                   |                   |                   | DMAADDR           | <31:24>           |                   |                  |                  |  |  |  |  |

| 00.40        | R-0               | R-0               | R-0               | R-0               | R-0               | R-0               | R-0              | R-0              |  |  |  |  |

| 23:16        | DMAADDR<23:16>    |                   |                   |                   |                   |                   |                  |                  |  |  |  |  |

| 45.0         | R-0               | R-0               | R-0               | R-0               | R-0               | R-0               | R-0              | R-0              |  |  |  |  |

| 15:8         |                   |                   |                   | DMAADDI           | R<15:8>           |                   |                  |                  |  |  |  |  |

| 7.0          | R-0               | R-0               | R-0               | R-0               | R-0               | R-0               | R-0              | R-0              |  |  |  |  |

| 7:0          |                   | DMAADDR<7:0>      |                   |                   |                   |                   |                  |                  |  |  |  |  |

## Legend:

| Logona.           |                  |                          |                    |

|-------------------|------------------|--------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, r | ead as '0'         |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared     | x = Bit is unknown |

#### bit 31-0 DMAADDR<31:0>: DMA Module Address bits

These bits contain the address of the most recent DMA access when an error was detected.

### TABLE 12-12: PORTE REGISTER MAP FOR 64-PIN DEVICES ONLY

| ess                         |                                 |           |       |       |       |       |                |       |      | I    | Bits         |              |              |              |              |              |              |              |               |

|-----------------------------|---------------------------------|-----------|-------|-------|-------|-------|----------------|-------|------|------|--------------|--------------|--------------|--------------|--------------|--------------|--------------|--------------|---------------|

| Virtual Address<br>(BF86_#) | Register<br>Name <sup>(1)</sup> | Bit Range | 31/15 | 30/14 | 29/13 | 28/12 | 27/11          | 26/10 | 25/9 | 24/8 | 23/7         | 22/6         | 21/5         | 20/4         | 19/3         | 18/2         | 17/1         | 16/0         | All<br>Resets |

| 0400                        | ANSELE                          | 31:16     | _     |       |       |       |                |       | —    | —    | —            | —            |              | -            | —            | _            | —            | —            | 0000          |

| 0.00                        | /                               | 15:0      | _     | -     | —     | _     | —              | _     | —    | —    | ANSE7        | ANSE6        | ANSE5        | ANSE4        | —            | _            | —            | -            | 00F0          |

| 0410                        | TRISE                           | 31:16     | —     | _     | _     | _     | —              | _     | —    | —    | —            | _            | _            | _            | —            | —            | _            | -            | 0000          |

| 0110                        | HUGE                            | 15:0      | —     | —     | —     | _     | —              | _     | —    | —    | TRISE7       | TRISE6       | TRISE5       | TRISE4       | TRISE3       | TRISE2       | TRISE1       | TRISE0       | 00FF          |

| 0420                        | PORTE                           | 31:16     | —     | —     | —     | _     | —              | —     | —    | —    | —            | —            | —            | —            | —            | —            | —            | —            | 0000          |

| 0420                        | TORTE                           | 15:0      | —     | —     | —     | -     | —              | —     | —    | —    | RE7          | RE6          | RE5          | RE4          | RE3          | RE2          | RE1          | RE0          | xxxx          |

| 0430                        | LATE                            | 31:16     | —     | -     | —     | -     | —              | —     | —    | —    | —            | —            | _            | -            | —            | -            | —            | —            | 0000          |

| 0430                        | LAIL                            | 15:0      | Ι     |       | -     |       | -              | —     | —    | _    | LATE7        | LATE6        | LATE5        | LATE4        | LATE3        | LATE2        | LATE1        | LATE0        | xxxx          |

| 0440                        | ODCE                            | 31:16     |       | —     | —     | —     | —              | _     | _    | _    | _            | _            | —            | —            | —            | —            | _            | —            | 0000          |

| 0440                        | ODCE                            | 15:0      | Ι     | _     | —     | _     | —              | _     | _    | _    | ODCE7        | ODCE6        | ODCE5        | ODCE4        | ODCE3        | ODCE2        | ODCE1        | ODCE0        | 0000          |

| 0450                        |                                 | 31:16     | _     | _     | _     | _     | _              | _     | _    | _    | _            | _            | _            | _            | _            | _            | _            | _            | 0000          |

| 0450                        | CNPUE                           | 15:0      | _     |       | _     |       | _              | _     | —    | _    | CNPUE7       | CNPUE6       | CNPUE5       | CNPUE4       | CNPUE3       | CNPUE2       | CNPUE1       | CNPUE0       | 0000          |

| 0.400                       |                                 | 31:16     | _     | _     | _     | _     | _              | _     | _    | —    | _            | _            | _            | -            | —            | -            | —            | _            | 0000          |

| 0460                        | CNPDE                           | 15:0      | _     | _     | _     | _     | —              | _     | —    | —    | CNPDE7       | CNPDE6       | CNPDE5       | CNPDE4       | CNPDE3       | CNPDE2       | CNPDE1       | CNPDE0       | 0000          |

|                             |                                 | 31:16     | _     | _     | _     | _     | —              | _     | —    | —    | —            | —            | _            | _            | —            | _            | —            | —            | 0000          |

| 0470                        | CNCONE                          | 15:0      | ON    | 1     |       | -     | EDGE<br>DETECT | _     | _    |      | _            | _            | -            | -            | _            | -            | _            | _            | 0000          |

| 0.400                       |                                 | 31:16     | _     |       | _     |       | _              | _     | —    | _    | —            | _            |              | -            | _            |              | _            | _            | 0000          |

| 0480                        | CNENE                           | 15:0      | _     | _     | _     | _     | _              | _     | _    | _    | CNENE7       | CNENE6       | CNENE5       | CNENE4       | CNENE3       | CNENE2       | CNENE1       | CNENE0       | 0000          |

|                             |                                 | 31:16     | _     | _     | _     | _     | —              | _     | —    | —    | —            | —            | _            | _            | —            | _            | —            | —            | 0000          |

| 0490                        | CNSTATE                         | 15:0      | _     |       | _     | _     | _              | _     | _    | _    | CN<br>STATE7 | CN<br>STATE6 | CN<br>STATE5 | CN<br>STATE4 | CN<br>STATE3 | CN<br>STATE2 | CN<br>STATE1 | CN<br>STATE0 | 0000          |

| 0440                        |                                 | 31:16     | _     | _     | _     | _     | _              | _     | _    | _    | _            | _            | _            | _            | _            | _            | _            | _            | 0000          |

| 04A0                        | CNNEE                           | 15:0      | _     | _     | _     | _     | _              | _     | _    | _    | CNNEE7       | CNNEE6       | CNNEE5       | CNNEE4       | CNNEE3       | CNNEE2       | CNNEE1       | CNNEE0       | 0000          |

| 0.450                       |                                 | 31:16     | _     | _     | _     | _     | _              | _     | _    | —    | _            | —            | —            | —            | —            | -            | —            | —            | 0000          |

| 04B0                        | CNFE                            | 15:0      | _     | _     | _     | _     | _              | _     | _    | _    | CNFE7        | CNFE6        | CNFE5        | CNFE4        | CNFE3        | CNFE2        | CNFE1        | CNFE0        | 0000          |

| 0.400                       |                                 | 31:16     | _     | _     | _     | _     | _              | _     | _    | —    | _            |              | -            | -            | —            | -            | —            | _            | 0000          |

| 04C0                        | SRCON0E                         | 15:0      | _     | _     | _     | _     | _              | _     | _    | _    | _            | _            | _            | _            | SR0E3        | SR0E2        | SR0E1        | SR0E0        | 0000          |

|                             |                                 | 31:16     | _     | _     | _     | _     |                | _     | _    |      | _            | _            | _            | _            |              | _            |              | —            | 0000          |

| 04D0                        | SRCON1E                         | 15:0      | _     | _     | _     | _     | _              | _     | _    | _    | _            | _            | _            | _            | SR1E3        | SR1E2        | SR1E1        | SR1E0        | 0000          |

Legend:

x = Unknown value on Reset; — = Unimplemented, read as '0'; Reset values are shown in hexadecimal. All registers in this table have corresponding CLR, SET and INV registers at its virtual address, plus an offset of 0x4, 0x8 and 0xC, respectively. See Section 12.3 "CLR, SET, and INV Registers" for Note 1: more information.

The timer source for each Output Compare module depends on the setting of the OCACLK bit in the CFG-CON register. The available configurations are shown in Table 18-1.

| TABLE 18-1: | TIMER SOURCE   |

|-------------|----------------|

|             | CONFIGURATIONS |

| Output<br>Compare<br>Module | Timerx                  | Timery      |  |  |  |  |  |  |

|-----------------------------|-------------------------|-------------|--|--|--|--|--|--|

| OCACLK (CFGCON<16>) = $0$   |                         |             |  |  |  |  |  |  |

| OC1                         | Timer2                  | Timer3      |  |  |  |  |  |  |

| •                           | •                       | •           |  |  |  |  |  |  |

| •                           | •                       | •           |  |  |  |  |  |  |

| •<br>OC9                    | •<br>Timer2             | •<br>Timer3 |  |  |  |  |  |  |

| OCACLK (CFGC                | OCACLK (CFGCON<16>) = 1 |             |  |  |  |  |  |  |

| OC1                         | Timer4                  | Timer5      |  |  |  |  |  |  |

| OC2                         | Timer4                  | Timer5      |  |  |  |  |  |  |

| OC3                         | Timer4                  | Timer5      |  |  |  |  |  |  |

| OC4                         | Timer2                  | Timer3      |  |  |  |  |  |  |

| OC5                         | Timer2                  | Timer3      |  |  |  |  |  |  |

| OC6                         | Timer2                  | Timer3      |  |  |  |  |  |  |

| OC7                         | Timer6                  | Timer7      |  |  |  |  |  |  |

| OC8                         | Timer6                  | Timer7      |  |  |  |  |  |  |

| OC9                         | Timer6                  | Timer7      |  |  |  |  |  |  |

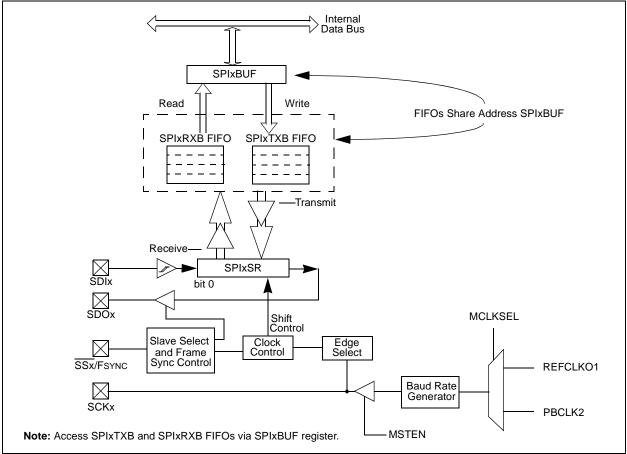

## 19.0 SERIAL PERIPHERAL INTERFACE (SPI) AND INTER-IC SOUND (I<sup>2</sup>S)

Note: This data sheet summarizes the features of the PIC32MZ EF family of devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to Section 23. "Serial Peripheral Interface (SPI)" (DS60001106) in the "PIC32 Family Reference Manual", which is available from the Microchip web site (www.microchip.com/ PIC32).

The SPI/I<sup>2</sup>S module is a synchronous serial interface that is useful for communicating with external peripherals and other microcontroller devices, as well as digital audio devices. These peripheral devices may be Serial EEPROMs, Shift registers, display drivers, Analog-to-Digital Converters, and so on.

The SPI/I<sup>2</sup>S module is compatible with Motorola<sup>®</sup> SPI and SIOP interfaces.

The following are key features of the SPI module:

- Master and Slave modes support

- · Four different clock formats

- Enhanced Framed SPI protocol support

- User-configurable 8-bit, 16-bit and 32-bit data width

- Separate SPI FIFO buffers for receive and transmit

FIFO buffers act as 4/8/16-level deep FIFOs based on 32/16/8-bit data width

- Programmable interrupt event on every 8-bit, 16-bit and 32-bit data transfer

- · Operation during Sleep and Idle modes

- Audio Codec Support:

- I<sup>2</sup>S protocol

- Left-justified

- Right-justified

- PCM

## FIGURE 19-1: SPI/I<sup>2</sup>S MODULE BLOCK DIAGRAM

#### **SQI Control Registers** 20.1

## TABLE 20-1: SERIAL QUADRATURE INTERFACE (SQI) REGISTER MAP

| ess                         |                   |               |       |                                                                                          |          |         |        |               |              | В            | its            |               |             |              |                |               |               |               | s          |

|-----------------------------|-------------------|---------------|-------|------------------------------------------------------------------------------------------|----------|---------|--------|---------------|--------------|--------------|----------------|---------------|-------------|--------------|----------------|---------------|---------------|---------------|------------|

| Virtual Address<br>(BF8E_#) | Register<br>Name  | Bit Range     | 31/15 | 30/14                                                                                    | 29/13    | 28/12   | 27/11  | 26/10         | 25/9         | 24/8         | 23/7           | 22/6          | 21/5        | 20/4         | 19/3           | 18/2          | 17/1          | 16/0          | All Resets |

| 2000                        | SQI1              | 31:16         | _     | —                                                                                        |          | —       | _      | —             | —            | —            | DUN            | IMYBYTES<     | :2:0>       | AD           | DRBYTES<2      | 2:0>          | READOPC       | CODE<7:6>     | 0000       |

| 2000                        | XCON1             | 15:0          |       | READOPCODE<5:0> TYPEDATA<1:0> TYPEDUMMY<1:0> TYPEMODE<1:0> TYPEADDR<1:0> TYPECMD<1:0> 00 |          |         |        |               | 0000         |              |                |               |             |              |                |               |               |               |            |

| 2004                        | SQI1              | 31:16         | _     | —                                                                                        | —        | —       | _      | —             | —            | —            | —              | —             | _           | —            | —              | —             | _             | —             | 0000       |

|                             | XCON2             | 15:0          | -     | _                                                                                        | _        | _       | DEVSE  | L<1:0>        | MODEBY       | TES<1:0>     |                |               |             | MODECO       | DDE<7:0>       |               |               |               | 0000       |

| 2008                        | SQI1CFG           | 31:16         | —     | _                                                                                        | _        | —       | _      | _             | CSEN         | l<1:0>       | SQIEN          | —             | DATAE       |              | CON<br>FIFORST | RXFIFO<br>RST | TXFIFO<br>RST | RESET         | 0000       |

|                             |                   | 15:0          | —     | —                                                                                        | —        | BURSTEN | _      | HOLD          | WP           | —            | —              | —             | LSBF        | CPOL         | CPHA           |               | MODE<2:0>     | •             | 0000       |

| 200C                        | SQI1CON           | 31:16         | —     | —                                                                                        | —        | -       | —      | —             | —            | SCHECK       | —              | DASSERT       | DEVSE       | L<1:0>       | LANEMC         | DE<1:0>       | CMDIN         | IT<1:0>       | 0000       |

|                             |                   | 15:0          |       |                                                                                          |          |         |        |               |              | TXRXCOL      | JNT<15:0>      |               |             |              |                |               |               |               | 0000       |

| 2010                        | SQI1              | 31:16         | —     | —                                                                                        | —        | -       | —      | —             | —            | —            | _              | _             | _           | _            | _              |               | LKDIV<10:8    |               | 0000       |

|                             | CLKCON            | 15:0          |       |                                                                                          |          | CLKDI   | V<7:0> |               |              |              | —              | —             | —           | _            | _              | —             | STABLE        | EN            | 0000       |

| 2014                        | SQI1              | 31:16         | —     | —                                                                                        |          | -       | —      | —             | —            | —            | _              | _             | —           | —            | —              | —             | —             | —             | 0000       |

|                             | CMDTHR            | 15:0          | _     |                                                                                          | <u> </u> |         |        |               |              |              | 0000           |               |             |              |                |               |               |               |            |

| 2018                        | SQI1              | 31:16         | _     | —                                                                                        | _        | -       |        | —             | _            | —            | —              | _             | _           | —            | —              | —             | -             | _             | 0000       |

|                             | INTTHR            | 15:0          |       |                                                                                          |          |         |        |               |              | 0000         |                |               |             |              |                |               |               |               |            |

| 201C                        | SQI1              | 31:16         | _     | _                                                                                        | _        | _       | _      | -             | -            | -            | -              | -             | —           | -            | -              | -             | —<br>—        | —<br>—        | 0000       |

| 2010                        | INTEN             | 15:0          | _     | _                                                                                        | _        | _       | DMAEIE | PKT<br>COMPIE | BD<br>DONEIE | CON<br>THRIE | CON<br>EMPTYIE | CON<br>FULLIE | RX<br>THRIE | RX<br>FULLIE | RX<br>EMPTYIE  | TX<br>THRIE   | TX<br>FULLIE  | TX<br>EMPTYIE | 0000       |

| 0000                        | SQI1              | 31:16         | —     | —                                                                                        | —        | _       | —      | —             | —            | —            | —              | —             | —           | —            | —              | —             | —             | —             | 0000       |

| 2020                        | INTSTAT           | 15:0          | —     | —                                                                                        | —        | -       | DMAEIF | PKT<br>COMPIF | BD<br>DONEIF | CON<br>THRIF | CON<br>EMPTYIF | CON<br>FULLIF | RX<br>THRIF | RX<br>FULLIF | RX<br>EMPTYIF  | TX<br>THRIF   | TX<br>FULLIF  | TX<br>EMPTYIF | 0000       |

| 2024                        | SQI1              | 31:16         |       |                                                                                          |          |         |        |               |              | TXDATA       |                |               |             |              |                |               |               |               | 0000       |

|                             | TXDATA            | 15:0          |       |                                                                                          |          |         |        |               |              | TXDAT        |                |               |             |              |                |               |               |               | 0000       |

| 2028                        | SQI1              | 31:16         |       |                                                                                          |          |         |        |               |              | RXDATA       |                |               |             |              |                |               |               |               | 0000       |

|                             | RXDATA            | 15:0          |       | i                                                                                        | i        |         |        | i             |              | RXDAT        | A<15:0>        |               |             |              |                |               |               |               | 0000       |

| 202C                        | SQI1<br>STAT1     | 31:16         | _     | _                                                                                        | _        |         | _      | _             | _            | _            |                |               |             |              | REE<7:0>       |               |               |               | 0000       |

|                             | -                 | 15:0          | _     | _                                                                                        | _        |         | _      | _             | _            | _            |                |               |             |              | CNT<7:0>       |               | 0,4507        |               | 0000       |

| 2030                        | SQI1<br>STAT2     | 31:16         | _     | —                                                                                        | _        |         | —      |               |              |              | —              |               | -           |              |                | _             |               | AT<1:0>       | 0000       |

|                             | -                 | 15:0<br>31:16 | _     | —                                                                                        |          | _       | _      |               | ONAVAIL<4:   |              |                | SDID3         | SDID2       | SDID1        | SDID0          | _             | RXUN          | TXOV          | 00x0       |

| 2034                        | SQI1<br>BDCON     | 31:16<br>15:0 | _     |                                                                                          | _        | _       | _      |               |              | _            | _              |               | _           |              |                | —<br>START    | POLLEN        |               | 0000       |

|                             |                   | 31:16         | _     | _                                                                                        | _        | _       | _      | _             | _            |              | <br>DDR<31:16> | _             | _           | —            | _              | SIARI         | POLLEN        | DIVIAEN       | 0000       |

| 2038                        | SQI1BD<br>CURADD  | 15:0          |       |                                                                                          |          |         |        |               |              |              | DDR<31:16>     |               |             |              |                |               |               |               | 0000       |

|                             |                   | 31:16         |       |                                                                                          |          |         |        |               |              |              | R<31:16>       |               |             |              |                |               |               |               | 0000       |

| 2040                        | SQI1BD<br>BASEADD | 15:0          |       |                                                                                          |          |         |        |               |              |              |                |               |             |              |                |               |               |               |            |

|                             |                   | 15.0          |       | BDADDR<15:0> 0000                                                                        |          |         |        |               |              |              |                |               |             |              |                |               |               |               |            |

## 27.1 RNG Control Registers

## TABLE 27-2: RANDOM NUMBER GENERATOR (RNG) REGISTER MAP

| ess                         |                  |           |       |               |       |       |          |       |        | Bits   | ;     |      |      |        |          |      |      |      |            |

|-----------------------------|------------------|-----------|-------|---------------|-------|-------|----------|-------|--------|--------|-------|------|------|--------|----------|------|------|------|------------|

| Virtual Address<br>(BF8E_#) | Register<br>Name | Bit Range | 31/15 | 30/14         | 29/13 | 28/12 | 27/11    | 26/10 | 25/9   | 24/8   | 23/7  | 22/6 | 21/5 | 20/4   | 19/3     | 18/2 | 17/1 | 16/0 | All Resets |

| 6000                        | RNGVER           | 31:16     |       | ID<15:0> xxxx |       |       |          |       |        |        | xxxx  |      |      |        |          |      |      |      |            |

| 0000                        | KINGVEIK         | 15:0      |       |               |       | VERS  | ION<7:0> |       |        |        |       |      |      | REVISI | ON<7:0>  |      |      |      | xxxx       |

| 6004                        | RNGCON           | 31:16     | —     | —             | —     | —     | —        | _     |        |        | —     | —    | —    | —      | —        | —    | —    | —    | 0000       |

| 0004                        | Rivecon          | 15:0      | —     | —             | —     | LOAD  | TRNGMODE | CONT  | PRNGEN | TRNGEN |       |      |      | PLE    | N<7:0>   |      |      |      | 0064       |

| 6008                        | RNGPOLY1         | 31:16     |       | POLY<31:0>    |       |       |          |       |        |        |       |      |      |        |          |      |      |      |            |

| 0000                        | KNOI OEI I       | 15:0      |       | 0000          |       |       |          |       |        |        |       |      |      |        |          |      |      |      |            |

| 600C                        | RNGPOLY2         | 31:16     |       | POLY<31:0>    |       |       |          |       |        | FFFF   |       |      |      |        |          |      |      |      |            |

| 0000                        |                  | 15:0      |       |               |       |       |          |       |        | TOLICO | 11.02 |      |      |        |          |      |      |      | 0000       |

| 6010                        | RNGNUMGEN1       | 31:16     |       |               |       |       |          |       |        | RNG<3  | 1.0>  |      |      |        |          |      |      |      | FFFF       |

| 0010                        | RIGHUNGEN        | 15:0      |       |               |       |       |          |       |        | NNO<0  | 1.02  |      |      |        |          |      |      |      | FFFF       |

| 6014                        | RNGNUMGEN2       | 31:16     |       |               |       |       |          |       |        | RNG<3  | 1.0>  |      |      |        |          |      |      |      | FFFF       |

| 0014                        | RINGINOWIGEINZ   | 15:0      |       |               |       |       |          |       |        | KNG<3  | 1.0>  |      |      |        |          |      |      |      | FFFF       |

| 6018                        | RNGSEED1         | 31:16     |       |               |       |       |          |       |        | SEED<3 | 21.0  |      |      |        |          |      |      |      | 0000       |

| 0010                        | RINGSEEDT        | 15:0      |       |               |       |       |          |       |        | SEED<3 | 51.0> |      |      |        |          |      |      |      | 0000       |

| 6010                        | RNGSEED2         | 31:16     |       |               |       |       |          |       |        |        | 1.0.  |      |      |        |          |      |      |      | 0000       |

| 601C                        | RINGSEED2        | 15:0      |       |               |       |       |          |       |        | SEED<3 | >1.0> |      |      |        |          |      |      |      | 0000       |

| 6020                        | DNCONT           | 31:16     | _     | —             | —     | —     | —        | _     | —      | —      | —     | —    | —    | —      | —        | —    | —    | —    | 0000       |

| 6020                        | RNGCNT           | 15:0      | _     | _             | _     | _     |          | _     | _      | _      | _     |      |      |        | RCNT<6:0 | >    | •    |      | 0000       |

Legend: x = unknown value on Reset; -- = unimplemented, read as '0'. Reset values are shown in hexadecimal.

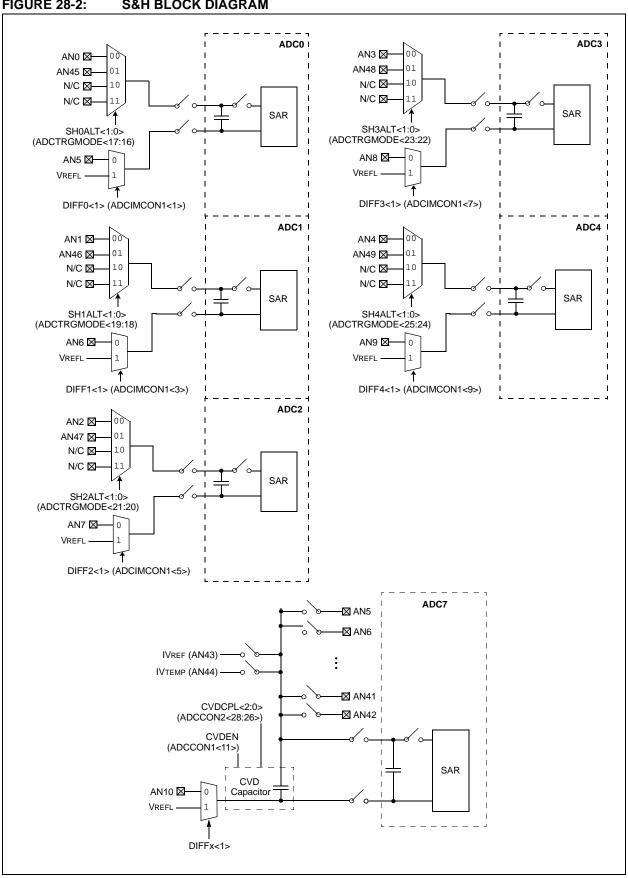

**FIGURE 28-2: S&H BLOCK DIAGRAM**

|              | -                 |                   |                   |                   |                   |                   |                  |                  |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |

| 31:24        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 31.24        | —                 |                   | -                 |                   |                   | —                 |                  | _                |

| 23:16        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 23.10        | —                 | _                 | _                 | _                 | _                 | —                 | _                | _                |

| 15:8         | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 10.0         | —                 | _                 | _                 | _                 | _                 | —                 | _                | _                |

| 7.0          | U-0               | R/W-0             | R/W-0             | R/W-1             | R/W-0             | R/W-0             | R/W-1            | R/W-0            |

| 7:0          | B2BIPKTGP<6:0>    |                   |                   |                   |                   |                   |                  |                  |

#### REGISTER 30-25: EMAC1IPGT: ETHERNET CONTROLLER MAC BACK-TO-BACK INTERPACKET GAP REGISTER

#### Legend:

| Legena.           |                  |                        |                    |

|-------------------|------------------|------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, | read as '0'        |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared   | x = Bit is unknown |

#### bit 31-7 Unimplemented: Read as '0'

#### bit 6-0 B2BIPKTGP<6:0>: Back-to-Back Interpacket Gap bits

This is a programmable field representing the nibble time offset of the minimum possible period between the end of any transmitted packet, to the beginning of the next. In Full-Duplex mode, the register value should be the desired period in nibble times minus 3. In Half-Duplex mode, the register value should be the desired period in nibble times minus 6. In Full-Duplex the recommended setting is 0x15 (21d), which represents the minimum IPG of 0.96  $\mu$ s (in 100 Mbps) or 9.6  $\mu$ s (in 10 Mbps). In Half-Duplex mode, the recommended setting is 0x12 (18d), which also represents the minimum IPG of 0.96  $\mu$ s (in 100 Mbps) or 9.6  $\mu$ s (in 100 Mbps) (in 100 Mbps) or 9.6  $\mu$ s (in 100 Mbps) (in 100 Mbps) (in 100 Mbps) or 9.6  $\mu$ s (in 100 Mbps) (in

**Note:** Both 16-bit and 32-bit accesses are allowed to these registers (including the SET, CLR and INV registers). 8-bit accesses are not allowed and are ignored by the hardware.

## 36.2 MPLAB XC Compilers

The MPLAB XC Compilers are complete ANSI C compilers for all of Microchip's 8, 16, and 32-bit MCU and DSC devices. These compilers provide powerful integration capabilities, superior code optimization and ease of use. MPLAB XC Compilers run on Windows, Linux or MAC OS X.

For easy source level debugging, the compilers provide debug information that is optimized to the MPLAB X IDE.

The free MPLAB XC Compiler editions support all devices and commands, with no time or memory restrictions, and offer sufficient code optimization for most applications.

MPLAB XC Compilers include an assembler, linker and utilities. The assembler generates relocatable object files that can then be archived or linked with other relocatable object files and archives to create an executable file. MPLAB XC Compiler uses the assembler to produce its object file. Notable features of the assembler include:

- Support for the entire device instruction set

- Support for fixed-point and floating-point data

- Command-line interface

- · Rich directive set

- Flexible macro language

- MPLAB X IDE compatibility

### 36.3 MPASM Assembler

The MPASM Assembler is a full-featured, universal macro assembler for PIC10/12/16/18 MCUs.

The MPASM Assembler generates relocatable object files for the MPLINK Object Linker, Intel<sup>®</sup> standard HEX files, MAP files to detail memory usage and symbol reference, absolute LST files that contain source lines and generated machine code, and COFF files for debugging.

The MPASM Assembler features include:

- Integration into MPLAB X IDE projects

- User-defined macros to streamline assembly code

- Conditional assembly for multipurpose source files

- Directives that allow complete control over the assembly process

## 36.4 MPLINK Object Linker/ MPLIB Object Librarian

The MPLINK Object Linker combines relocatable objects created by the MPASM Assembler. It can link relocatable objects from precompiled libraries, using directives from a linker script.

The MPLIB Object Librarian manages the creation and modification of library files of precompiled code. When a routine from a library is called from a source file, only the modules that contain that routine will be linked in with the application. This allows large libraries to be used efficiently in many different applications.

The object linker/library features include:

- Efficient linking of single libraries instead of many smaller files

- Enhanced code maintainability by grouping related modules together

- Flexible creation of libraries with easy module listing, replacement, deletion and extraction

## 36.5 MPLAB Assembler, Linker and Librarian for Various Device Families

MPLAB Assembler produces relocatable machine code from symbolic assembly language for PIC24, PIC32 and dsPIC DSC devices. MPLAB XC Compiler uses the assembler to produce its object file. The assembler generates relocatable object files that can then be archived or linked with other relocatable object files and archives to create an executable file. Notable features of the assembler include:

- · Support for the entire device instruction set

- · Support for fixed-point and floating-point data

- Command-line interface

- · Rich directive set

- Flexible macro language

- MPLAB X IDE compatibility

| TABLE 37-33: SPIx MODULE SLAVE MODE (CKE = 1) TIM | MING REQUIREMENTS (CONTINUED) |

|---------------------------------------------------|-------------------------------|

|---------------------------------------------------|-------------------------------|

| AC CHA        | RACTERIS              | TICS                                                                      | $\begin{array}{l} \mbox{Standard Operating Conditions: 2.1V to 3.6V} \\ \mbox{(unless otherwise stated)} \\ \mbox{Operating temperature -40°C} \leq TA \leq +85°C \mbox{ for Industrial} \\ \mbox{-40°C} \leq TA \leq +125°C \mbox{ for Extended} \end{array}$ |                        |      |       |            |  |  |

|---------------|-----------------------|---------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------|------|-------|------------|--|--|

| Param.<br>No. | Symbol                | Characteristics <sup>(1)</sup>                                            | Min.                                                                                                                                                                                                                                                           | Typical <sup>(2)</sup> | Max. | Units | Conditions |  |  |

| SP50          | TssL2scH,<br>TssL2scL | $\overline{SSx} \downarrow$ to SCKx $\downarrow$ or SCKx $\uparrow$ Input | 88                                                                                                                                                                                                                                                             | _                      |      | ns    | —          |  |  |

| SP51          | TssH2doZ              | SSx ↑ to SDOx Output<br>High-Impedance<br>(Note 4)                        | 2.5                                                                                                                                                                                                                                                            | _                      | 12   | ns    | _          |  |  |

| SP52          | TscH2ssH<br>TscL2ssH  | SSx ↑ after SCKx Edge                                                     | 10                                                                                                                                                                                                                                                             | _                      |      | ns    | _          |  |  |

| SP60          | TssL2doV              | SDOx Data Output Valid after<br>SSx Edge                                  | —                                                                                                                                                                                                                                                              | —                      | 12.5 | ns    |            |  |  |

Note 1: These parameters are characterized, but not tested in manufacturing.

2: Data in "Typical" column is at 3.3V, +25°C unless otherwise stated. Parameters are for design guidance only and are not tested.

3: The minimum clock period for SCKx is 20 ns.

4: Assumes 30 pF load on all SPIx pins.

|                 | I TPBCLK2 I TPBCLK2                          | TPBCLK2        | TPBCLK2 | TPBCLK2 | TPBCLK2         | TPBCLK2  | TPBCLK2  |

|-----------------|----------------------------------------------|----------------|---------|---------|-----------------|----------|----------|

| PBCLK2          |                                              | <br>_//        | ا<br>ہ  | <br>//  |                 | /        |          |

| PMA <x:0></x:0> | <u>                                     </u> | ↓↓<br>         | Address |         |                 |          |          |

|                 |                                              | ⊢ PM2 + PM3    | ·       |         |                 |          | <b> </b> |

| PMD <x:0></x:0> |                                              | Address<7:0>   | >¥      | /<br>\  | Data            | /        |          |

|                 |                                              |                | י<br>ל  | ✓ PM    | 112             | < PM13-► |          |

| PMRD_           |                                              | <b>↓</b>       |         | I       |                 |          |          |

| PMWR _          |                                              | <br>           | ا<br>ا  | ·<br>/  | <u>←</u> PM11-► |          | . I      |

|                 | I I                                          | <b>←</b> PM1 → | ļ       | I       | I               |          |          |

| PMALL/PMALH     | <u>   </u>                                   | <u> </u>       |         |         |                 |          |          |

|                 |                                              |                |         |         |                 |          |          |

| PMCSx           | I I/                                         | <u>}</u> }     |         |         |                 |          |          |

|                 |                                              |                |         |         |                 |          |          |

|                 |                                              |                | •       | •       |                 |          | ·        |

#### FIGURE 37-23: PARALLEL MASTER PORT WRITE TIMING DIAGRAM

### TABLE 37-44: PARALLEL MASTER PORT WRITE TIMING REQUIREMENTS

| AC CHA        | RACTERI | STICS                                                                     | $\begin{array}{l} \mbox{Standard Operating Conditions: 2.1V to 3.6V} \\ \mbox{(unless otherwise stated)} \\ \mbox{Operating temperature} & -40^\circ C \leq TA \leq +85^\circ C \mbox{ for Industrial} \\ & -40^\circ C \leq TA \leq +125^\circ C \mbox{ for Extended} \end{array}$ |           |      |       |            |  |  |

|---------------|---------|---------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------|------|-------|------------|--|--|

| Param.<br>No. | Symbol  | Characteristics <sup>(1)</sup>                                            | Min.                                                                                                                                                                                                                                                                                | Тур.      | Max. | Units | Conditions |  |  |

| PM11          | Twr     | PMWR Pulse Width                                                          |                                                                                                                                                                                                                                                                                     | 1 TPBCLK2 | —    | —     | —          |  |  |