Welcome to **E-XFL.COM**

What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded - Microcontrollers</u>"

| Details                   |                                                                                  |

|---------------------------|----------------------------------------------------------------------------------|

| roduct Status             | Active                                                                           |

| fore Processor            | MIPS32® M-Class                                                                  |

| Core Size                 | 32-Bit Single-Core                                                               |

| peed                      | 180MHz                                                                           |

| Connectivity              | CANbus, Ethernet, I <sup>2</sup> C, PMP, SPI, SQI, UART/USART, USB OTG           |

| eripherals                | Brown-out Detect/Reset, DMA, I <sup>2</sup> S, POR, PWM, WDT                     |

| lumber of I/O             | 46                                                                               |

| rogram Memory Size        | 512KB (512K x 8)                                                                 |

| rogram Memory Type        | FLASH                                                                            |

| EPROM Size                | -                                                                                |

| AM Size                   | 128K x 8                                                                         |

| oltage - Supply (Vcc/Vdd) | 2.1V ~ 3.6V                                                                      |

| ata Converters            | A/D 24x12b                                                                       |

| Scillator Type            | Internal                                                                         |

| perating Temperature      | -40°C ~ 125°C                                                                    |

| Nounting Type             | Surface Mount                                                                    |

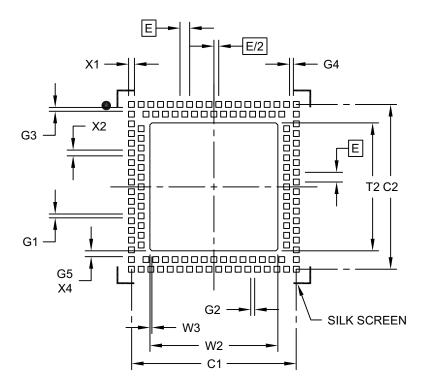

| ackage / Case             | 64-TQFP                                                                          |

| upplier Device Package    | 64-TQFP (10x10)                                                                  |

| urchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic32mz0512efk064-e-pt |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

**TABLE 1-8: UART1 THROUGH UART6 PINOUT I/O DESCRIPTIONS**

|          |                        | Pin Nu          | mber            |                          |             |                |                       |  |

|----------|------------------------|-----------------|-----------------|--------------------------|-------------|----------------|-----------------------|--|

| Pin Name | 64-pin<br>QFN/<br>TQFP | 100-pin<br>TQFP | 124-pin<br>VTLA | 144-pin<br>TQFP/<br>LQFP | Pin<br>Type | Buffer<br>Type | Description           |  |

|          |                        |                 | Unive           | ersal Asyr               | chronou     | ıs Receive     | r Transmitter 1       |  |

| U1RX     | PPS                    | PPS             | PPS             | PPS                      | I           | ST             | UART1 Receive         |  |

| U1TX     | PPS                    | PPS             | PPS             | PPS                      | 0           | _              | UART1 Transmit        |  |

| U1CTS    | PPS                    | PPS             | PPS             | PPS                      | I           | ST             | UART1 Clear to Send   |  |

| U1RTS    | PPS                    | PPS             | PPS             | PPS                      | 0           | _              | UART1 Ready to Send   |  |

|          |                        |                 | Unive           | rsal Asyr                | chronou     | s Receive      | r Transmitter 2       |  |

| U2RX     | PPS                    | PPS             | PPS             | PPS                      | I           | ST             | UART2 Receive         |  |

| U2TX     | PPS                    | PPS             | PPS             | PPS                      | 0           | _              | UART2 Transmit        |  |

| U2CTS    | PPS                    | PPS             | PPS             | PPS                      | I           | ST             | UART2 Clear To Send   |  |

| U2RTS    | PPS                    | PPS             | PPS             | PPS                      | 0           | _              | UART2 Ready To Send   |  |

|          |                        |                 | Unive           | rsal Asyr                | chronou     | s Receive      | r Transmitter 3       |  |

| U3RX     | PPS                    | PPS             | PPS             | PPS                      | I           | ST             | UART3 Receive         |  |

| U3TX     | PPS                    | PPS             | PPS             | PPS                      | 0           | _              | UART3 Transmit        |  |

| U3CTS    | PPS                    | PPS             | PPS             | PPS                      | I           | ST             | UART3 Clear to Send   |  |

| U3RTS    | PPS                    | PPS             | PPS             | PPS                      | 0           | _              | UART3 Ready to Send   |  |

|          |                        |                 | Unive           | rsal Asyr                | chronou     | s Receive      | r Transmitter 4       |  |

| U4RX     | PPS                    | PPS             | PPS             | PPS                      | I           | ST             | UART4 Receive         |  |

| U4TX     | PPS                    | PPS             | PPS             | PPS                      | 0           | _              | UART4 Transmit        |  |

| U4CTS    | PPS                    | PPS             | PPS             | PPS                      | I           | ST             | UART4 Clear to Send   |  |

| U4RTS    | PPS                    | PPS             | PPS             | PPS                      | 0           | _              | UART4 Ready to Send   |  |

|          |                        |                 | Unive           | rsal Asyr                | chronou     | s Receive      | r Transmitter 5       |  |

| U5RX     | PPS                    | PPS             | PPS             | PPS                      | I           | ST             | UART5 Receive         |  |

| U5TX     | PPS                    | PPS             | PPS             | PPS                      | 0           | _              | UART5 Transmit        |  |

| U5CTS    | PPS                    | PPS             | PPS             | PPS                      | I           | ST             | UART5 Clear to Send   |  |

| U5RTS    | PPS                    | PPS             | PPS             | PPS                      | 0           | _              | UART5 Ready to Send   |  |

|          | •                      | •               | Unive           | rsal Asyr                | chronou     | s Receive      | r Transmitter 6       |  |

| U6RX     | PPS                    | PPS             | PPS             | PPS                      | I           | ST             | UART6 Receive         |  |

| U6TX     | PPS                    | PPS             | PPS             | PPS                      | 0           | _              | UART6 Transmit        |  |

| U6CTS    | PPS                    | PPS             | PPS             | PPS                      | I           | ST             | T UART6 Clear to Send |  |

| U6RTS    | PPS                    | PPS             | PPS             | PPS                      | 0           | _              | UART6 Ready to Send   |  |

|          |                        |                 |                 |                          |             |                |                       |  |

CMOS = CMOS-compatible input or output ST = Schmitt Trigger input with CMOS levels Analog = Analog input O = Output

P = Power I = Input

TTL = Transistor-transistor Logic input buffer

PPS = Peripheral Pin Select

## REGISTER 3-10: FCSR: FLOATING POINT CONTROL AND STATUS REGISTER; CP1 REGISTER 31

- bit 16 V: Invalid Operation bit

- bit 15 Z: Divide-by-Zero bit

- bit 14 O: Overflow bit

- bit 13 U: Underflow bit

- bit 12 I: Inexact bit

#### bit 11-7 ENABLES<4:0>: FPU Exception Enable bits

These bits control whether or not a trap is taken when an IEEE exception condition occurs for any of the five conditions. The trap occurs when both an enable bit and its corresponding cause bit are set either during an FPU arithmetic operation or by moving a value to the FCSR or one of its alternative representations.

- bit 11 V: Invalid Operation bit

- bit 10 Z: Divide-by-Zero bit

- bit 9 O: Overflow bit

- bit 8 U: Underflow bit

- bit 7 I: Inexact bit

- bit 6-2 FLAGS<4:0>: FPU Flags bits

These bits show any exception conditions that have occurred for completed instructions since the flag was last reset by software.

- bit 6 V: Invalid Operation bit

- bit 5 **Z:** Divide-by-Zero bit

- bit 4 O: Overflow bit

- bit 3 U: Underflow bit

- bit 2 I: Inexact bit

- bit 1-0 RM<1:0>: Rounding Mode control bits

- 11 =Round towards Minus Infinity  $(-\infty)$

- 10 = Round towards Plus Infinity (+  $\infty$ )

- 01 = Round toward Zero (0)

- 00 = Round to Nearest

#### 4.0 MEMORY ORGANIZATION

Note:

This data sheet summarizes the features of the PIC32MZ EF family of devices. It is not intended to be a comprehensive reference source.For detailed information, refer to Section 48. "Memory Organization and Permissions" in the "PIC32 Family Reference Manual", which is available Microchip web site the (www.microchip.com/PIC32).

PIC32MZ EF microcontrollers provide 4 GB of unified virtual memory address space. All memory regions, including program, data memory, SFRs and Configuration registers, reside in this address space at their respective unique addresses. The program and data memories can be optionally partitioned into user and kernel memories. In addition, PIC32MZ EF devices allow execution from data memory.

Key features include:

- · 32-bit native data width

- Separate User (KUSEG) and Kernel (KSEG0/ KSEG1/KSEG2/KSEG3) mode address space

- Separate boot Flash memory for protected code

- Robust bus exception handling to intercept runaway code

- Cacheable (KSEG0/KSEG2) and non-cacheable (KSEG1/KSEG3) address regions

- Read/write permission access to predefined memory regions

## 4.1 Memory Layout

PIC32MZ EF microcontrollers implement two address schemes: virtual and physical. All hardware resources, such as program memory, data memory and peripherals, are located at their respective physical addresses. Virtual addresses are exclusively used by the CPU to fetch and execute instructions as well as access peripherals. Physical addresses are used by bus master peripherals, such as DMA and the Flash controller, that access memory independently of the CPU.

The main memory maps for the PIC32MZ EF devices are illustrated in Figure 4-1 through Figure 4-4. Figure 4-5 provides memory map information for boot Flash and boot alias. Table 4-1 provides memory map information for Special Function Registers (SFRs).

TABLE 10-3: DMA CHANNEL 0 THROUGH CHANNEL 7 REGISTER MAP (CONTINUED)

| 1170   DCHISSIZ   15:0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | SS                          |                                 |           |       |       |          |       |          |       |      | Bit     | s      | •      |        |        |        |        |        |         |            |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------|---------------------------------|-----------|-------|-------|----------|-------|----------|-------|------|---------|--------|--------|--------|--------|--------|--------|--------|---------|------------|

| 1170   DCH1SIZ   15:0   CHSSIZ-15:0>   D                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | Virtual Address<br>(BF81_#) | Register<br>Name <sup>(1)</sup> | Bit Range | 31/15 | 30/14 | 29/13    | 28/12 | 27/11    | 26/10 | 25/9 | 24/8    | 23/7   | 22/6   | 21/5   | 20/4   | 19/3   | 18/2   | 17/1   | 16/0    | All Resets |

| 180   CHIDSIZ   15:0   CHIDSIZ   15:0  | 1170                        | DCU10017                        | 31:16     | _     | _     | _        | _     | _        | I     | _    | _       | _      | _      | _      | 1      | _      | _      | _      | _       | 0000       |

| 189   DCH1051Z   15:0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 1170                        | DCHTSSIZ                        | 15:0      |       |       |          |       |          |       |      | CHSSIZ  | <15:0> |        |        |        |        |        |        |         | 0000       |

| 1190   DCHISPTR   15:0   CHISPTR   15: | 1180                        | DCH1DSI7                        | 31:16     | _     | _     | _        | _     | _        | _     | _    | _       | _      | _      | _      | _      | _      | _      | _      | _       | 0000       |

| 1190   DCH1SPT   15:0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 1100                        | DCHTD3IZ                        | 15:0      |       |       |          |       |          |       |      | CHDSIZ- | <15:0> |        |        |        |        |        |        |         | 0000       |

| 1140   DCH1OPTR   31:16                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 1100                        | DCH1SPTR                        | 31:16     | _     | _     | _        | _     | _        | _     | _    | _       | _      | _      | _      | _      | _      | _      | _      | _       | 0000       |

| 1140   DCHIDPTR   15.0   CHDPTR<  15.0   CHDPTR<  15.0   CHCSIZ   15.0   CHCCSIZ   15.0   CHCSIZ   15.0   CH | 1190                        | DOITIOI IIX                     | 15:0      |       |       |          |       |          |       |      | CHSPTR  | <15:0> |        |        |        |        |        |        |         | 0000       |

| 1150                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 1140                        | DCH1DPTR                        | 31:16     | _     | _     | _        | _     | _        | _     | _    |         | _      | _      | _      | _      | _      | _      | _      | _       | 0000       |

| 1160   DCH1CSIZ   15.0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 11710                       | DOITIDI TIX                     | 15:0      |       |       |          |       |          |       |      | CHDPTR  | <15:0> |        |        |        |        |        |        |         | 0000       |

| 150                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 11B0                        | DCH1CSIZ                        |           | _     | _     | _        | _     | _        | _     | _    |         | _      | _      | _      | _      | _      | _      | _      | _       | 0000       |

| 1100   DCH1DAT                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                             |                                 |           |       |       |          |       | 1        |       | ı    | CHCSIZ  | <15:0> | ı      |        |        | ı      | 1      |        | ı       | 0000       |

| 11D0   DCH1DAT   15:0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 11C0                        | DCH1CPTR                        |           | _     | _     | _        | _     | _        | _     | _    | _       | _      | _      | _      | _      | _      | _      |        | _       | 0000       |

| 11E0   DCH2CON   15:0   CHPIGN=7:0>   CHPIGN=7:0>   CHPIGN=7:0>   CHPIGN=7:0>   CHPIGN=7:0>   CHPIGN=7:0>   CHPIGN=7:0>   CHCHNS   CHEN   CHAED   CHCHN   CHAEN   CH |                             |                                 |           |       |       |          |       |          |       | ı    |         | <15:0> | ı      |        |        |        |        |        | 1       | 0000       |

| 11E0   DCH2CON   15:0   CHBUSY   — CHPIGNEN   — CHPATLEN   — CHCHNS   CHEN   CHAED   CHCHN   CHAEN   — CHAEN | 11D0                        | DCH1DAT                         |           | _     | _     | _        |       | _        | _     | _    |         | _      | _      | _      | _      | _      | _      | _      | _       | 0000       |

| 11E0   DCH2CON     15:0   CHBUSY                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                             | 15:0 CHPDAT<15:0>               |           |       |       |          |       |          |       | 0000 |         |        |        |        |        |        |        |        |         |            |

| 11F0   DCH2ECON     31:16                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 11E0                        | DCH2CON                         | _         |       |       |          | CHPIG |          |       | ı    | _       | _      |        |        | _      |        | _      |        |         | 0000       |

| 11F0   DCH2ECON   15:0   CHSIRQ<7:0>   CFORCE   CABORT   PATEN   SIRQEN   AIRQEN     -   F                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                             |                                 |           |       |       | CHPIGNEN |       | CHPATLEN |       | _    |         | CHEN   | CHAED  | CHCHN  |        |        | CHEDET | CHPR   | :l<1:0> | 0000       |

| 1200   DCH2INT   31:16                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 11F0                        | DCH2ECON                        |           | _     | _     | _        |       | _        | _     | _    | _       |        |        |        |        |        |        |        |         | 00FF       |

| 1210   DCH2SIA   15:0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                             |                                 | _         |       |       |          | CHSIR | Q<7:0>   |       |      |         |        |        |        |        |        |        |        |         | FF00       |

| 1210   DCH2SSA   31:16                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 1200                        | DCH2INT                         | _         |       |       | _        |       | _        |       | _    |         |        |        |        |        |        |        |        |         | 0000       |

| 1210   DCH2SSA   15:0     CHSSA   1220   DCH2DSA     15:0     CHDSA<31:0>   0   1230   DCH2SSIZ     31:16                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                             |                                 |           | _     |       | _        |       | _        |       | _    | _       | CHSDIF | CHSHIF | CHDDIF | CHDHIF | CHBCIF | CHCCIF | CHTAIF | CHERIF  | 0000       |

| 1220   DCH2DSA     15:0     CHDSA   1230   DCH2SSIZ   31:16   -                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 1210                        | DCH2SSA                         |           |       |       |          |       |          |       |      | CHSSA   | <31:0> |        |        |        |        |        |        |         | 0000       |

| 1230 DCH2SSIZ 31:16 — — — — — — — — — — — — — — — — — — —                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 1220                        | DCH2DSA                         |           |       |       |          |       |          |       |      | CHDSA   | <31:0> |        |        |        |        |        |        |         | 0000       |

| 1230   DCH2SSIZ                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                             |                                 |           | _     | _     | _        | _     | _        | _     | _    | _       | _      | _      | _      | _      | _      | _      | _      | _       | 0000       |

| 1240 DCH2DSIZ 31:16 — — — — — — — — — — — — — — — — — — —                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 1230                        | DCH2SSIZ                        | _         |       |       |          |       |          |       |      |         | <15:0> |        |        |        |        |        |        |         | 0000       |

| 1240   DCH2DSIZ                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                             |                                 |           | _     |       | _        | _     | _        | _     | _    |         | _      | _      | _      | _      | _      | _      | _      | _       | 0000       |

| 1250 DCH2SPTR 31:16 — — — — — — — — — — — — — — — — — — —                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 1240                        | DCH2DSIZ                        | _         |       |       |          |       |          |       |      | CHDSI7  | <15:0> |        |        |        |        |        |        |         | 0000       |

| 1250 DCH2SPTR 15:0 CHSPTR<15:0> 0 1260 DCH2DPTR 31:16 0 15:0 CHDPTR<15:0> 0 131:16 0 15:0 CHDPTR<15:0> 0 15:0 CHDPTR<15:0                                                            |                             |                                 |           | _     |       | _        | _     | _        | _     | _    | _       | _      | _      | _      | _      | _      | _      | _      | _       | 0000       |

| 1260 DCH2DPTR 31:16 — — — — — — — — — — — — — — — — — — —                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 1250                        | DCH2SPTR                        | _         |       |       |          |       |          |       |      | CHSPTR  | <15:0> |        |        |        |        |        |        |         | 0000       |

| 1260 DCH2DPTR 15:0 CHDPTR<15:0> 0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | l                           |                                 |           | _     | _     | _        | _     | _        | _     | _    |         | _      | _      | _      | _      | _      | _      | _      | _       | 0000       |

| 31:16 -   -   -   -   -   -   -   -   -   -                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 1260                        | DCH2DPTR                        |           |       |       |          |       |          |       |      | CHDPTR  | <15:0> |        |        |        |        |        |        |         | 0000       |

| 177/1111/197/1817                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 4076                        | DOI 1000:2                      | 31:16     | _     | _     | _        | _     | _        | _     | _    | _       | _      | _      | _      | _      | _      | _      | _      | _       | 0000       |