Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFl

| Product Status             | Active                                                                           |

|----------------------------|----------------------------------------------------------------------------------|

| Core Processor             | MIPS32® M-Class                                                                  |

| Core Size                  | 32-Bit Single-Core                                                               |

| Speed                      | 180MHz                                                                           |

| Connectivity               | CANbus, EBI/EMI, Ethernet, I <sup>2</sup> C, PMP, SPI, SQI, UART/USART, USB OTG  |

| Peripherals                | Brown-out Detect/Reset, DMA, I <sup>2</sup> S, POR, PWM, WDT                     |

| Number of I/O              | 120                                                                              |

| Program Memory Size        | 512KB (512K x 8)                                                                 |

| Program Memory Type        | FLASH                                                                            |

| EEPROM Size                |                                                                                  |

| RAM Size                   | 128K x 8                                                                         |

| Voltage - Supply (Vcc/Vdd) | 2.1V ~ 3.6V                                                                      |

| Data Converters            | A/D 48x12b                                                                       |

| Oscillator Type            | Internal                                                                         |

| Operating Temperature      | -40°C ~ 125°C (TA)                                                               |

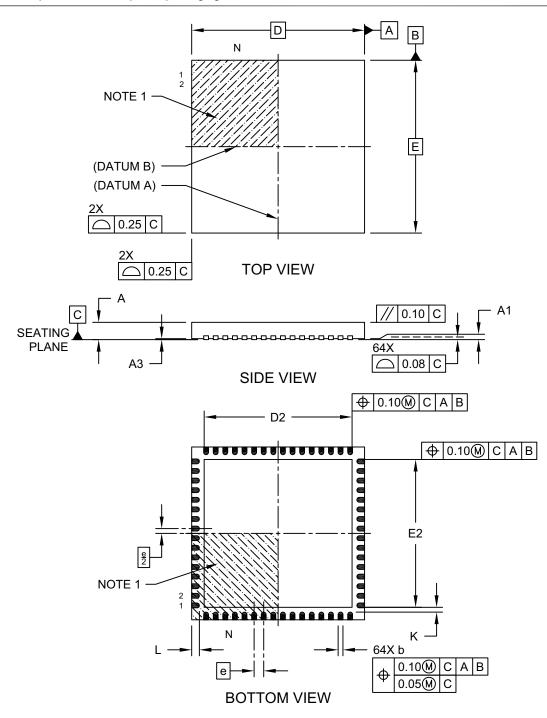

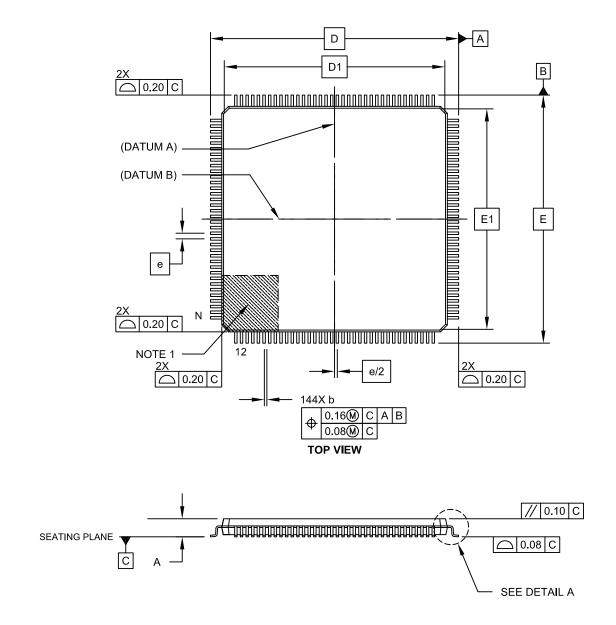

| Mounting Type              | Surface Mount                                                                    |

| Package / Case             | 144-LQFP                                                                         |

| Supplier Device Package    | 144-LQFP (20x20)                                                                 |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic32mz0512efk144-e-pl |

|                            |                                                                                  |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# **Referenced Sources**

This device data sheet is based on the following individual sections of the *"PIC32 Family Reference Manual"*. These documents should be considered as the general reference for the operation of a particular module or device feature.

| Note: | To access                               | the    | following | documents, |  |  |  |  |  |

|-------|-----------------------------------------|--------|-----------|------------|--|--|--|--|--|

|       | browse the documentation section of the |        |           |            |  |  |  |  |  |

|       | Microchip                               |        | web       | site       |  |  |  |  |  |

|       | (www.microo                             | chip.c | om).      |            |  |  |  |  |  |

- Section 1. "Introduction" (DS60001127)

- Section 7. "Resets" (DS60001118)

- Section 8. "Interrupt Controller" (DS60001108)

- Section 9. "Watchdog, Deadman, and Power-up Timers" (DS60001114)

- Section 10. "Power-Saving Features" (DS60001130)

- Section 12. "I/O Ports" (DS60001120)

- Section 13. "Parallel Master Port (PMP)" (DS60001128)

- Section 14. "Timers" (DS60001105)

- Section 15. "Input Capture" (DS60001122)

- Section 16. "Output Compare" (DS60001111)

- Section 19. "Comparator" (DS60001110)

- Section 20. "Comparator Voltage Reference (CVREF)" (DS60001109)

- Section 21. "Universal Asynchronous Receiver Transmitter (UART)" (DS60001107)

- Section 22. "12-bit High-Speed Successive Approximation Register (SAR) Analog-to-Digital Converter (ADC)" (DS60001344)

- Section 23. "Serial Peripheral Interface (SPI)" (DS60001106)

- Section 24. "Inter-Integrated Circuit (I<sup>2</sup>C)" (DS60001116)

- Section 29. "Real-Time Clock and Calendar (RTCC)" (DS60001125)

- Section 31. "Direct Memory Access (DMA) Controller" (DS60001117)

- Section 32. "Configuration" (DS60001124)

- Section 33. "Programming and Diagnostics" (DS60001129)

- Section 34. "Controller Area Network (CAN)" (DS60001154)

- Section 35. "Ethernet Controller" (DS60001155)

- Section 41. "Prefetch Module for Devices with L1 CPU Cache" (DS60001183)

- Section 42. "Oscillators with Enhanced PLL" (DS60001250)

- Section 46. "Serial Quad Interface (SQI)" (DS60001244)

- Section 47. "External Bus Interface (EBI)" (DS60001245)

- Section 48. "Memory Organization and Permissions" (DS60001214)

- Section 49. "Crypto Engine (CE) and Random Number Generator (RNG)" (DS60001246)

- Section 50. "CPU for Devices with MIPS32<sup>®</sup> microAptiv<sup>™</sup> and M-Class Cores" (DS60001192)

- Section 51. "Hi-Speed USB with On-The-Go (OTG)" (DS60001326)

- Section 52. "Flash Program Memory with Support for Live Update" (DS60001193)

| Register<br>Number | Register<br>Name | Function                                                                                                                                  |

|--------------------|------------------|-------------------------------------------------------------------------------------------------------------------------------------------|

| 12                 | Status           | Processor status and control.                                                                                                             |

|                    | IntCtl           | Interrupt control of vector spacing.                                                                                                      |

|                    | SRSCtl           | Shadow register set control.                                                                                                              |

|                    | SRSMap           | Shadow register mapping control.                                                                                                          |

|                    | View_IPL         | Allows the Priority Level to be read/written without                                                                                      |

|                    |                  | extracting or inserting that bit from/to the Status register.                                                                             |

|                    | SRSMAP2          | Contains two 4-bit fields that provide the mapping from a vector number to the shadow set number to use when servicing such an interrupt. |

| 13                 | Cause            | Describes the cause of the last exception.                                                                                                |

|                    | NestedExc        | Contains the error and exception level status bit values that existed prior to the current exception.                                     |

|                    | View_RIPL        | Enables read access to the RIPL bit that is available in the Cause register.                                                              |

| 14                 | EPC              | Program counter at last exception.                                                                                                        |

|                    | NestedEPC        | Contains the exception program counter that existed prior to the current exception.                                                       |

| 15                 | PRID             | Processor identification and revision                                                                                                     |

|                    | Ebase            | Exception base address of exception vectors.                                                                                              |

|                    | CDMMBase         | Common device memory map base.                                                                                                            |

| 16                 | Config           | Configuration register.                                                                                                                   |

|                    | Config1          | Configuration register 1.                                                                                                                 |

|                    | Config2          | Configuration register 2.                                                                                                                 |

|                    | Config3          | Configuration register 3.                                                                                                                 |

|                    | Config4          | Configuration register 4.                                                                                                                 |

|                    | Config5          | Configuration register 5.                                                                                                                 |

|                    | Config7          | Configuration register 7.                                                                                                                 |

| 17                 | LLAddr           | Load link address (MPU only).                                                                                                             |

| 18                 | WatchLo          | Low-order watchpoint address (MPU only).                                                                                                  |

| 19                 | WatchHi          | High-order watchpoint address (MPU only).                                                                                                 |

| 20-22              | Reserved         | Reserved in the PIC32 core.                                                                                                               |

| 23                 | Debug            | EJTAG debug register.                                                                                                                     |

|                    | TraceControl     | EJTAG trace control.                                                                                                                      |

|                    | TraceControl2    | EJTAG trace control 2.                                                                                                                    |

|                    | UserTraceData1   | EJTAG user trace data 1 register.                                                                                                         |

|                    | TraceBPC         | EJTAG trace breakpoint register.                                                                                                          |

|                    | Debug2           | Debug control/exception status 1.                                                                                                         |

| 24                 | DEPC             | Program counter at last debug exception.                                                                                                  |

|                    | UserTraceData2   |                                                                                                                                           |

| 25                 | PerfCtl0         | Performance counter 0 control.                                                                                                            |

|                    | PerfCnt0         | Performance counter 0.                                                                                                                    |

|                    | PerfCtl1         | Performance counter 1 control.                                                                                                            |

|                    | PerfCnt1         | Performance counter 1.                                                                                                                    |

| 26                 | ErrCtl           | Software test enable of way-select and data RAM arrays for I-Cache and D-Cache (MPU only).                                                |

| 27                 | Reserved         | Reserved in the PIC32 core.                                                                                                               |

| 28                 | TagLo/DataLo     | Low-order portion of cache tag interface (MPU only).                                                                                      |

| 29                 | Reserved         | Reserved in the PIC32 core.                                                                                                               |

| 30                 | ErrorEPC         | Program counter at last error exception.                                                                                                  |

| 31                 | DeSave           | Debug exception save.                                                                                                                     |

|                    |                  |                                                                                                                                           |

|              | I                 |                   | )(^ = '-')        |                   |                   |                   |                  |                  |  |  |  |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|--|--|--|

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |  |  |  |

| 24.24        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |  |  |  |

| 31:24        | —                 | —                 | —                 | —                 | —                 | —                 | —                | —                |  |  |  |

| 23:16        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |  |  |  |

| 23.10        |                   | —                 |                   | —                 | —                 | —                 |                  | —                |  |  |  |

| 15:8         | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |  |  |

| 15.6         | RQPKTCNT<15:8>    |                   |                   |                   |                   |                   |                  |                  |  |  |  |

| 7:0          | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |  |  |

| 7.0          | RQPKTCNT<7:0>     |                   |                   |                   |                   |                   |                  |                  |  |  |  |

# REGISTER 11-24: USBExRPC: USB ENDPOINT 'x' REQUEST PACKET COUNT REGISTER (HOST MODE ONLY) ('x' = 1-7)

### Legend:

| Logona.           |                  |                           |                    |

|-------------------|------------------|---------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, re | ead as '0'         |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared      | x = Bit is unknown |

bit 31-16 Unimplemented: Read as '0'

bit 15-0 **RQPKTCNT<15:0>:** Request Packet Count bits Sets the number of packets of size MAXP that are to be transferred in a block transfer. This register is only available in *Host mode* when AUTOREQ is set.

# REGISTER 11-25: USBDPBFD: USB DOUBLE PACKET BUFFER DISABLE REGISTER

| Bit<br>Range | Bit Bit<br>31/23/15/7 30/22/14/6 |        | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |

|--------------|----------------------------------|--------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|

| 31:24        | U-0                              | U-0    | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 31.24        | _                                | _      | _                 | _                 | _                 | _                 |                  | —                |

| 22:46        | R/W-0                            | R/W-0  | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | U-0              |

| 23:16        | EP7TXD                           | EP6TXD | EP5TXD            | EP4TXD            | EP3TXD            | EP2TXD            | EP1TXD           | —                |

| 15:8         | U-0                              | U-0    | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 10.0         |                                  | —      | _                 | _                 | _                 | _                 | —                | —                |

| 7:0          | R/W-0                            | R/W-0  | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | U-0              |

| 7.0          | EP7RXD                           | EP6RXD | EP5RXD            | EP4RXD            | EP3RXD            | EP2RXD            | EP1RXD           | _                |

| Legend:           |                  |                           |                    |

|-------------------|------------------|---------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, re | ead as '0'         |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared      | x = Bit is unknown |

bit 31-17 EP7TXD:EP1TXD: TX Endpoint 'x' Double Packet Buffer Disable bits

- 1 = TX double packet buffering is disabled for endpoint 'x'

- 0 = TX double packet buffering is enabled for endpoint 'x'

- bit 16 Unimplemented: Read as '0'

- bit 15-1 **EP7RXD:EP1RXD:** RX Endpoint 'x' Double Packet Buffer Disable bits

- 1 = RX double packet buffering is disabled for endpoint 'x'

- 0 = RX double packet buffering is enabled for endpoint 'x'

- bit 0 Unimplemented: Read as '0'

| TABLE 12-3: | <b>OUTPUT PIN SELECTION</b> |

|-------------|-----------------------------|

|-------------|-----------------------------|

| RPn Port Pin         | RPnR SFR              | RPnR bits                  | RPnR Value to Peripheral<br>Selection         |

|----------------------|-----------------------|----------------------------|-----------------------------------------------|

| RPD2                 | RPD2R                 | RPD2R<3:0>                 | 0000 = No Connect                             |

| RPG8                 | RPG8R                 | RPG8R<3:0>                 | 0001 = <u>U3TX</u>                            |

| RPF4                 | RPF4R                 | RPF4R<3:0>                 | 0010 = U4RTS                                  |

| RPD10                | RPD10R                | RPD10R<3:0>                | 0011 = Reserved<br>0100 = Reserved            |

| RPF1                 | RPF1R                 | RPF1R<3:0>                 | 0100 = Reserved<br>0101 = SDO1                |

| RPB9                 | RPB9R                 | RPB9R<3:0>                 | 0110 = SD02                                   |

| RPB10                | RPB10R                | RPB10R<3:0>                | 0111 = SDO3                                   |

| RPC14                | RPC14R                | RPC14R<3:0>                | 1000 = Reserved                               |

| RPB5                 | RPB5R                 | RPB5R<3:0>                 | $1001 = SDO5^{(1)}$                           |

| RPC1 <sup>(1)</sup>  | RPC1R <sup>(1)</sup>  | RPC1R<3:0> <sup>(1)</sup>  | $1010 = \overline{SS6}^{(1)}$                 |

| RPD14 <sup>(1)</sup> | RPD14R <sup>(1)</sup> | RPD14R<3:0> <sup>(1)</sup> | 1011 = OC3<br>1100 = OC6                      |

| RPG1 <sup>(1)</sup>  | RPG1R <sup>(1)</sup>  | RPG1R<3:0> <sup>(1)</sup>  | 1100 = 000<br>1101 = REFCLKO4                 |

| RPA14 <sup>(1)</sup> | RPA14R <sup>(1)</sup> | RPA14R<3:0> <sup>(1)</sup> | 1110 = C2OUT                                  |

| RPD6 <sup>(2)</sup>  | RPD6R <sup>(2)</sup>  | RPD6R<3:0> <sup>(2)</sup>  | 1111 = C1TX <sup>(3)</sup>                    |

| RPD3                 | RPD3R                 | RPD3R<3:0>                 | 0000 = No Connect                             |

| RPG7                 | RPG7R                 | RPG7R<3:0>                 | 0001 = <u>U1TX</u>                            |

| RPF5                 | RPF5R                 | RPF5R<3:0>                 | 0010 = U2RTS                                  |

| RPD11                | RPD11R                | RPD11R<3:0>                | - 0011 = U5TX                                 |

| RPF0                 | RPF0R                 | RPF0R<3:0>                 |                                               |

| RPB1                 | RPB1R                 | RPB1R<3:0>                 | 0110 = SD02                                   |

| RPE5                 | RPE5R                 | RPE5R<3:0>                 | 0111 = SDO3                                   |

| RPC13                | RPC13R                | RPC13R<3:0>                | 1000 = SDO4                                   |

| RPB3                 | RPB3R                 | RPB3R<3:0>                 | 1001 = SDO5 <sup>(1)</sup>                    |

| RPC4 <sup>(1)</sup>  | RPC4R <sup>(1)</sup>  | RPC4R<3:0> <sup>(1)</sup>  | 1010 = Reserved                               |

| RPD15 <sup>(1)</sup> | RPD15R <sup>(1)</sup> | RPD15R<3:0> <sup>(1)</sup> | 1011 = OC4<br>1100 = OC7                      |

| RPG0 <sup>(1)</sup>  | RPG0R <sup>(1)</sup>  | RPG0R<3:0> <sup>(1)</sup>  | 1100 = CC7                                    |

| RPA15 <sup>(1)</sup> | RPA15R <sup>(1)</sup> | RPA15R<3:0> <sup>(1)</sup> | 1110 = Reserved                               |

| RPD7 <sup>(2)</sup>  | RPD7R <sup>(2)</sup>  | RPD7R<3:0> <sup>(2)</sup>  | 1111 = REFCLKO1                               |

| RPD9                 | RPD9R                 | RPD9R<3:0>                 | 0000 = <u>No Connect</u>                      |

| RPG6                 | RPG6R                 | RPG6R<3:0>                 | 0001 = U3RTS                                  |

| RPB8                 | RPB8R                 | RPB8R<3:0>                 | 0010 = U4TX<br>0011 = Reserved                |

| RPB15                | RPB15R                | RPB15R<3:0>                | 0011 = Reserved<br>0100 = U6TX                |

| RPD4                 | RPD4R                 | RPD4R<3:0>                 | 0101 = SS1                                    |

| RPB0                 | RPB0R                 | RPB0R<3:0>                 | $0110 = \frac{\text{Reserved}}{200}$          |

| RPE3                 | RPE3R                 | RPE3R<3:0>                 | $ 0111 = \frac{SS3}{1000} = \frac{SS3}{SS4} $ |

| RPB7                 | RPB7R                 | RPB7R<3:0>                 | $1000 = \frac{334}{\text{SS5}^{(1)}}$         |

| RPF12 <sup>(1)</sup> | RPF12R <sup>(1)</sup> | RPF12R<3:0> <sup>(1)</sup> | 1010 = SDO6 <sup>(1)</sup>                    |

| RPD12 <sup>(1)</sup> | RPD12R <sup>(1)</sup> | RPD12R<3:0> <sup>(1)</sup> | 1011 = OC5                                    |

| RPF8 <sup>(1)</sup>  | RPF8R <sup>(1)</sup>  | RPF8R<3:0> <sup>(1)</sup>  |                                               |

| RPC3 <sup>(1)</sup>  | RPC3R <sup>(1)</sup>  | RPC3R<3:0> <sup>(1)</sup>  | 1110 = C1OUT                                  |

| RPE9 <sup>(1)</sup>  | RPE9R <sup>(1)</sup>  | RPE9R<3:0> <sup>(1)</sup>  | 1111 = REFCLKO3                               |

Note 1: This selection is not available on 64-pin devices.

2: This selection is not available on 64-pin or 100-pin devices.

3: This selection is not available on devices without a CAN module.

# TABLE 12-21: PORTK REGISTER MAP FOR 144-PIN DEVICES ONLY

| ess                         |                                 | ø         | Bits  |       |       |       |                |       |      |      |              |              |              |              |              |              |              |              |               |

|-----------------------------|---------------------------------|-----------|-------|-------|-------|-------|----------------|-------|------|------|--------------|--------------|--------------|--------------|--------------|--------------|--------------|--------------|---------------|

| Virtual Address<br>(BF86_#) | Register<br>Name <sup>(1)</sup> | Bit Range | 31/15 | 30/14 | 29/13 | 28/12 | 27/11          | 26/10 | 25/9 | 24/8 | 23/7         | 22/6         | 21/5         | 20/4         | 19/3         | 18/2         | 17/1         | 16/0         | All<br>Resets |

| 0910                        | TRISK                           | 31:16     | _     | -     | —     | —     | —              | _     | _    | —    | -            | —            | _            |              | —            | —            | —            | —            | 0000          |

| 0010                        | INION                           | 15:0      | —     | _     | —     | —     | —              | —     | —    | —    | TRISK7       | TRISK6       | TRISK5       | TRISK4       | TRISK3       | TRISK2       | TRISK1       | TRISK0       | OOFF          |

| 0920                        | PORTK                           | 31:16     | —     | _     | —     | —     | —              | —     | —    | _    | —            | —            | —            | —            | —            | —            | —            | —            | 0000          |

| 0020                        |                                 | 15:0      | —     | _     | —     | —     | —              | —     | —    | —    | RK7          | RK6          | RK5          | RK4          | RK3          | RK2          | RK1          | RK0          | xxxx          |

| 0930                        | LATK                            | 31:16     | —     | —     | —     | —     | —              | _     | —    | —    | —            | —            | —            | —            | —            | —            | —            | _            | 0000          |

|                             |                                 | 15:0      | _     | _     | —     | _     | —              | _     | _    | _    | LATK7        | LATK6        | LATK5        | LATK4        | LATK3        | LATK2        | LATK1        | LATK0        | XXXX          |

| 0940                        | ODCK                            | 31:16     | _     | _     | —     | _     | _              | _     | —    | —    | —            | —            | —            | —            | —            | —            | —            | —            | 0000          |

|                             |                                 | 15:0      | _     | _     | —     | _     | _              | _     | _    | _    | ODCK7        | ODCK6        | ODCK5        | ODCK4        | ODCK3        | ODCK2        | ODCK1        | ODCK0        | 0000          |

| 0950                        | CNPUK                           | 31:16     | _     | _     | _     | _     | _              | _     | _    | _    | -            | -            | -            | —            | -            | -            | -            | -            | 0000          |

|                             |                                 | 15:0      | _     | _     | _     | _     | _              | _     | _    | _    | CNPUK7       | CNPUK6       | CNPUK5       | CNPUK4       | CNPUK3       | CNPUK2       | CNPUK1       | CNPUK0       | 0000          |

| 0960                        | CNPDK                           | 31:16     |       |       | -     |       |                |       |      |      |              |              | -            |              |              |              |              |              | 0000          |

|                             |                                 | 15:0      | _     | _     | _     | _     | _              | _     |      | _    | CNPDK7       | CNPDK6       | CNPDK5       | CNPDK4       | CNPDK3       | CNPDK2       | CNPDK1       | CNPDK0       | 0000          |

| 0070                        | CNCONK                          | 31:16     | _     | _     | —     | —     | -              |       |      | _    |              | _            | _            | _            | _            |              |              |              | 0000          |

| 0070                        | onconin                         | 15:0      | ON    | —     | —     | —     | EDGE<br>DETECT | —     | —    | —    | —            | —            | —            | —            | —            | —            | —            | —            | 0000          |

| 0980                        | CNENK                           | 31:16     | -     |       | _     | _     | _              | _     | _    | _    | ١            | _            |              |              | -            | -            | -            | _            | 0000          |

| 0900                        | CINLINK                         | 15:0      | _     | _     | —     | —     | _              | _     | _    | _    | CNENK7       | CNENK6       | CNENK5       | CNENK4       | CNENK3       | CNENK2       | CNENK1       | CNENK0       | 0000          |

|                             |                                 | 31:16     | —     | —     | —     | —     | —              | —     | —    | —    | -            | —            | —            | -            | —            | —            | —            | _            | 0000          |

| 0990                        | CNSTATK                         | 15:0      | -     | _     | -     | -     | -              | -     | _    | —    | CN<br>STATK7 | CN<br>STATK6 | CN<br>STATK5 | CN<br>STATK4 | CN<br>STATK3 | CN<br>STATK2 | CN<br>STATK1 | CN<br>STATK0 | 0000          |

| 0040                        | CNNEK                           | 31:16     | —     | _     | —     | _     | _              | _     | _    | _    | _            | —            | _            | _            | _            | —            | _            | _            | 0000          |

| 09A0                        | CININER                         | 15:0      | _     |       |       |       |                |       |      |      | CNNEK7       | CNNEK6       | CNNEK5       | CNNEK4       | CNNEK3       | CNNEK2       | CNNEK1       | CNNEK0       | 0000          |

| 09B0                        | CNFK                            | 31:16     | _     | _     | —     | —     | _              | _     | _    | _    | _            | —            | _            |              |              | —            | —            | —            | 0000          |

| 0900                        | UNER                            | 15:0      | _     | -     | _     | _     | _              | _     | _    | _    | CNFK7        | CNFK6        | CNFK5        | CNFK4        | CNFK3        | CNFK2        | CNFK1        | CNFK0        | 0000          |

Legend:

x = Unknown value on Reset; — = Unimplemented, read as '0'; Reset values are shown in hexadecimal. All registers in this table have corresponding CLR, SET and INV registers at its virtual address, plus an offset of 0x4, 0x8, and 0xC, respectively. See Section 12.3 "CLR, SET, and INV Registers" for Note 1: more information.

| Bit Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |

|-----------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|

| 31:24     | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 31.24     | —                 | _                 | _                 | _                 | -                 | _                 |                  | —                |

| 22:16     | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 23:16     | —                 | _                 | _                 | _                 | -                 | _                 |                  | —                |

| 45.0      | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 15:8      | —                 | _                 | _                 | _                 | -                 | _                 |                  | —                |

| 7.0       | R-0, HC, HS       | R-0, HC, HS       | R-0, HC, HS       | U-0               | U-0               | U-0               | U-0              | R-0, HC, HS      |

| 7:0       | BAD1              | BAD2              | DMTEVENT          | _                 |                   | _                 | _                | WINOPN           |

## REGISTER 15-4: DMTSTAT: DEADMAN TIMER STATUS REGISTER

| Legend:           | HC = Hardware Cleared | HS = Hardware Set                |            |  |  |  |

|-------------------|-----------------------|----------------------------------|------------|--|--|--|

| R = Readable bit  | W = Writable bit      | U = Unimplemented bit, read as   | '0'        |  |  |  |

| -n = Value at POR | '1' = Bit is set      | 0' = Bit is cleared $x = Bit is$ | is unknown |  |  |  |

| bit 31-8 | Unimplemented: Read as '0'                                                                                                          |

|----------|-------------------------------------------------------------------------------------------------------------------------------------|

| bit 7    | BAD1: Bad STEP1<7:0> Value Detect bit                                                                                               |

|          | 1 = Incorrect STEP1<7:0> value was detected                                                                                         |

|          | 0 = Incorrect STEP1<7:0> value was not detected                                                                                     |

| bit 6    | BAD2: Bad STEP2<7:0> Value Detect bit                                                                                               |

|          | 1 = Incorrect STEP2<7:0> value was detected                                                                                         |

|          | 0 = Incorrect STEP2<7:0> value was not detected                                                                                     |

| bit 5    | DMTEVENT: Deadman Timer Event bit                                                                                                   |

|          | 1 = Deadman timer event was detected (counter expired or bad STEP1<7:0> or STEP2<7:0> value was entered prior to counter increment) |

|          | 0 = Deadman timer even was not detected                                                                                             |

| bit 4-1  | Unimplemented: Read as '0'                                                                                                          |

| bit 0    | WINOPN: Deadman Timer Clear Window bit                                                                                              |

|          | 1 = Deadman timer clear window is open                                                                                              |

|          | 0 = Deadman timer clear window is not open                                                                                          |

# REGISTER 20-3: SQI1CFG: SQI CONFIGURATION REGISTER (CONTINUED)

| bit 12  | BURSTEN: Burst Configuration bit <sup>(1)</sup>                                                                                                                                                                                   |

|---------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|         | 1 = Burst is enabled                                                                                                                                                                                                              |

|         | 0 = Burst is not enabled                                                                                                                                                                                                          |

| bit 11  | Reserved: Must be programmed as '0'                                                                                                                                                                                               |

| bit 10  | HOLD: Hold bit                                                                                                                                                                                                                    |

|         | In Single Lane or Dual Lane mode, this bit is used to drive the SQID3 pin, which can be used for devices with a HOLD input pin. The meaning of the values for this bit will depend on the device to which SQID3 is connected.     |

| bit 9   | WP: Write Protect bit                                                                                                                                                                                                             |

|         | In Single Lane or Dual Lane mode, this bit is used to drive the SQID2 pin, which can be used with devices with a write-protect pin. The meaning of the values for this bit will depend on the device to which SQID2 is connected. |

| bit 8-6 | Unimplemented: Read as '0'                                                                                                                                                                                                        |

| bit 5   | LSBF: Data Format Select bit                                                                                                                                                                                                      |

|         | <ul> <li>1 = LSB is sent or received first</li> <li>0 = MSB is sent or received first</li> </ul>                                                                                                                                  |

| bit 4   | CPOL: Clock Polarity Select bit                                                                                                                                                                                                   |

|         | <ul><li>1 = Active-low SQICLK (SQICLK high is the Idle state)</li><li>0 = Active-high SQICLK (SQICLK low is the Idle state)</li></ul>                                                                                             |

| bit 3   | CPHA: Clock Phase Select bit                                                                                                                                                                                                      |

|         | <ul> <li>1 = SQICLK starts toggling at the start of the first data bit</li> <li>0 = SQICLK starts toggling at the middle of the first data bit</li> </ul>                                                                         |

| bit 2-0 | MODE<2:0>: Mode Select bits                                                                                                                                                                                                       |

|         | 111 = Reserved                                                                                                                                                                                                                    |

|         | •                                                                                                                                                                                                                                 |

|         | •                                                                                                                                                                                                                                 |

|         | •                                                                                                                                                                                                                                 |

|         | 100 = Reserved                                                                                                                                                                                                                    |

|         | 011 = XIP mode is selected (when this mode is entered, the module behaves as if executing in place (XIP),<br>but uses the register data to control timing)                                                                        |

|         | 010 = DMA mode is selected                                                                                                                                                                                                        |

- 010 = DMA mode is selected

- 001 = CPU mode is selected (the module is controlled by the CPU in PIO mode. This mode is entered when leaving Boot or XIP mode)

- 000 = Reserved

- Note 1: This bit must be programmed as '1'.

|              | R                 | EGISTER           |                   |                   |                   |                   |                  |                  |  |  |  |  |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|--|--|--|--|

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |  |  |  |  |

| 24.24        | U-0               | U-0               | U-0               | R-x               | R-x               | R-x               | R-x              | U-0              |  |  |  |  |

| 31:24        |                   | _                 | —                 |                   | —                 |                   |                  |                  |  |  |  |  |

| 22:46        | U-0               | U-0               | U-0               | R-x               | R-x               | R-x               | R-x              | R-x              |  |  |  |  |

| 23:16        |                   |                   | —                 |                   | RX                | KBUFCNT<4:        | 0>               |                  |  |  |  |  |

| 45.0         | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |  |  |  |  |

| 15:8         |                   | _                 | —                 | _                 | —                 | _                 | —                | —                |  |  |  |  |

| 7.0          | R-x               | R-x               | R-x               | R-x               | R-x               | R-x               | R-x              | R-x              |  |  |  |  |

| 7:0          |                   | RXCURBUFLEN<7:0>  |                   |                   |                   |                   |                  |                  |  |  |  |  |

#### REGISTER 20-20: SQI1BDRXDSTAT: SQI BUFFER DESCRIPTOR DMA RECEIVE STATUS REGISTER

# Legend:

| Logonal           |                  |                          |                    |  |

|-------------------|------------------|--------------------------|--------------------|--|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, r | ead as '0'         |  |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared     | x = Bit is unknown |  |

bit 31-29 Unimplemented: Read as '0'

- bit 28-25 **RXSTATE<3:0>:** Current DMA Receive State Status bits These bits provide information on the current DMA receive states.

- bit 24-21 Unimplemented: Read as '0'

- bit 20-16 **RXBUFCNT<4:0>:** DMA Buffer Byte Count Status bits These bits provide information on the internal FIFO space.

- bit 15-8 Unimplemented: Read as '0'

- bit 7-0 **RXCURBUFLEN<7:0>:** Current DMA Receive Buffer Length Status bits These bits provide the length of the current DMA receive buffer.

#### REGISTER 20-21: SQI1THR: SQI THRESHOLD CONTROL REGISTER

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|

| 24.24        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 31:24        |                   | _                 | _                 | _                 | _                 | _                 | _                | —                |

| 22.46        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 23:16        |                   |                   |                   |                   | -                 |                   |                  | —                |

| 45.0         | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 15:8         |                   | _                 | _                 | _                 | _                 | _                 | _                | —                |

| 7.0          | U-0               | U-0               | U-0               | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |

| 7:0          |                   |                   |                   |                   |                   | THRES<4:0>        |                  |                  |

| Leaend | : |

|--------|---|

| Logona | • |

| Logona.           |                               |                      |                    |

|-------------------|-------------------------------|----------------------|--------------------|

| R = Readable bit  | Readable bit W = Writable bit |                      | read as '0'        |

| -n = Value at POR | '1' = Bit is set              | '0' = Bit is cleared | x = Bit is unknown |

bit 31-5 Unimplemented: Read as '0'

bit 4-0 THRES<4:0>: SQI Control Threshold Value bits

The SQI control threshold interrupt is asserted when the amount of space indicated by THRES<4:0> is available in the SQI control buffer.

# TABLE 28-1: ADC REGISTER MAP (CONTINUED)

| ress<br>(                   |                        | e         |       |              |       |       |       |       |      | Bit    | 5       |           |      |      |      |      |      |      |    |

|-----------------------------|------------------------|-----------|-------|--------------|-------|-------|-------|-------|------|--------|---------|-----------|------|------|------|------|------|------|----|

| Virtual Address<br>(BF84_#) | Register<br>Name       | Bit Range | 31/15 | 30/14        | 29/13 | 28/12 | 27/11 | 26/10 | 25/9 | 24/8   | 23/7    | 22/6      | 21/5 | 20/4 | 19/3 | 18/2 | 17/1 | 16/0 |    |

|                             | ADC2CFG <sup>(3)</sup> | 31:16     |       |              |       |       |       |       |      | ADCCFG | <31:16> |           |      |      |      |      |      | •    | 01 |

|                             |                        | 15:0      |       |              |       |       |       |       |      | ADCCFG | <15:0>  |           |      |      |      |      |      |      | 0  |

| 318C                        | ADC3CFG <sup>(3)</sup> | 31:16     |       |              |       |       |       |       |      | ADCCFG | <31:16> |           |      |      |      |      |      |      | C  |

|                             |                        | 15:0      |       | ADCCFG<15:0> |       |       |       |       |      |        |         |           |      |      | C    |      |      |      |    |

| B190                        | ADC4CFG <sup>(3)</sup> | 31:16     |       |              |       |       |       |       |      | ADCCFG | <31:16> |           |      |      |      |      |      |      | C  |

|                             |                        | 15:0      |       |              |       |       |       |       |      | ADCCFG | <15:0>  |           |      |      |      |      |      |      | (  |

| 319C                        | ADC7CFG <sup>(3)</sup> | 31:16     |       |              |       |       |       |       |      | ADCCFG | <31:16> |           |      |      |      |      |      |      | (  |

|                             |                        | 15:0      |       |              |       |       |       |       |      | ADCCFG | <15:0>  |           |      |      |      |      |      |      | C  |

| B1C0                        | ADCSYSCFG1             | 31:16     |       |              |       |       |       |       |      | AN<31  | :16>    |           |      |      |      |      |      |      | 2  |

|                             |                        | 15:0      |       |              |       |       |       |       |      | AN<1   | 5:0>    |           |      |      |      |      |      |      | F  |

| 31C4                        | ADCSYSCFG2             | 31:16     | —     | —            | —     | —     | —     | —     | —    | —      | —       | —         | —    | _    | —    | _    | _    | -    | (  |

|                             |                        | 15:0      | _     | _            | _     |       |       |       |      |        |         | AN<44:32> |      |      |      |      |      |      | 1  |

| 3200                        | ADCDATA0               | 31:16     |       |              |       |       |       |       |      | DATA<3 | 1:16>   |           |      |      |      |      |      |      |    |

|                             |                        | 15:0      |       |              |       |       |       |       |      | DATA<  | 15:0>   |           |      |      |      |      |      |      |    |

| 3204                        | ADCDATA1               | 31:16     |       |              |       |       |       |       |      | DATA<3 | 1:16>   |           |      |      |      |      |      |      |    |

|                             |                        | 15:0      |       |              |       |       |       |       |      | DATA<  | 15:0>   |           |      |      |      |      |      |      |    |

| B208                        | ADCDATA2               | 31:16     |       |              |       |       |       |       |      | DATA<3 | 1:16>   |           |      |      |      |      |      |      |    |

|                             |                        | 15:0      |       |              |       |       |       |       |      | DATA<  | 15:0>   |           |      |      |      |      |      |      |    |

| 320C                        | ADCDATA3               | 31:16     |       |              |       |       |       |       |      | DATA<3 | 1:16>   |           |      |      |      |      |      |      |    |

|                             |                        | 15:0      |       |              |       |       |       |       |      | DATA<  | 15:0>   |           |      |      |      |      |      |      |    |

| B210                        | ADCDATA4               | 31:16     |       |              |       |       |       |       |      | DATA<3 | 1:16>   |           |      |      |      |      |      |      |    |

|                             |                        | 15:0      |       |              |       |       |       |       |      | DATA<  | 15:0>   |           |      |      |      |      |      |      |    |

| B214                        | ADCDATA5               | 31:16     |       |              |       |       |       |       |      | DATA<3 | 1:16>   |           |      |      |      |      |      |      |    |

|                             |                        | 15:0      |       |              |       |       |       |       |      | DATA<  | 15:0>   |           |      |      |      |      |      |      | (  |

| B218                        | ADCDATA6               | 31:16     |       |              |       |       |       |       |      | DATA<3 | 1:16>   |           |      |      |      |      |      |      | (  |

|                             |                        | 15:0      |       |              |       |       |       |       |      | DATA<  | 15:0>   |           |      |      |      |      |      |      | (  |

| B21C                        | ADCDATA7               | 31:16     |       |              |       |       |       |       |      | DATA<3 | 1:16>   |           |      |      |      |      |      |      |    |

|                             |                        | 15:0      |       |              |       |       |       |       |      | DATA<  | 15:0>   |           |      |      |      |      |      |      |    |

| B220                        | ADCDATA8               | 31:16     |       |              |       |       |       |       |      | DATA<3 | 1:16>   |           |      |      |      |      |      |      |    |

|                             |                        | 15:0      |       |              |       |       |       |       |      | DATA<  | 15:0>   |           |      |      |      |      |      |      |    |

| B224                        | ADCDATA9               | 31:16     |       | DATA<31:16>  |       |       |       |       |      |        |         |           |      |      |      |      |      |      |    |

|                             |                        | 15:0      |       | DATA<15:0>   |       |       |       |       |      |        |         |           |      |      |      |      |      |      |    |

| B228                        | ADCDATA10              | 31:16     |       |              |       |       |       |       |      | DATA<3 |         |           |      |      |      |      |      |      | (  |

|                             |                        | 15:0      |       | DATA<15:0>   |       |       |       |       |      |        |         |           |      | (    |      |      |      |      |    |

| B22C                        | ADCDATA11              | 31:16     |       |              |       |       |       |       |      | DATA<3 | 1:16>   |           |      |      |      |      |      |      | -  |

|                             |                        | 15:0      |       |              |       |       |       |       |      | DATA<  |         |           |      |      |      |      |      |      | (  |

| B230                        | ADCDATA12              | 31:16     |       |              |       |       |       |       |      | DATA<3 |         |           |      |      |      |      |      |      | C  |

|                             |                        | 15:0      |       |              |       |       |       |       |      | DATA<  |         |           |      |      |      |      |      |      | C  |

1: 2: 3:

This bit or register is not available on 64-pin devices. This bit or register is not available on 64-pin and 100-pin devices. Before enabling the ADC, the user application must initialize the ADC calibration values by copying them from the factory-programmed DEVADCx Flash registers into the corresponding ADCxCFG registers.

# TABLE 28-1: ADC REGISTER MAP (CONTINUED)

| es                          |                          |               |       |  |  |  |  |  |  | Bit   | s     |  |      |  |            |  | s    |

|-----------------------------|--------------------------|---------------|-------|--|--|--|--|--|--|-------|-------|--|------|--|------------|--|------|

| Virtual Address<br>(BF84_#) | Register<br>Name         | Bit Range     | 31/15 |  |  |  |  |  |  |       |       |  |      |  | All Resets |  |      |

|                             | ADCDATA32 <sup>(1)</sup> | 31:16         |       |  |  |  |  |  |  | DATA< | 1:16> |  |      |  |            |  | 0000 |

|                             |                          | 15:0          |       |  |  |  |  |  |  | DATA< | 15:0> |  |      |  |            |  | 0000 |

| B284                        | ADCDATA33 <sup>(1)</sup> | 31:16         |       |  |  |  |  |  |  | DATA< | 1:16> |  |      |  |            |  | 0000 |

|                             |                          | 15:0          |       |  |  |  |  |  |  | DATA< | 15:0> |  |      |  |            |  | 0000 |

| B288                        | ADCDATA34 <sup>(1)</sup> | 31:16         |       |  |  |  |  |  |  | DATA< | 1:16> |  |      |  |            |  | 0000 |

|                             |                          | 15:0          |       |  |  |  |  |  |  | DATA< | 15:0> |  |      |  |            |  | 0000 |

| B28C                        | ADCDATA35 <sup>(2)</sup> | 31:16         |       |  |  |  |  |  |  | DATA< |       |  |      |  |            |  | 0000 |

|                             |                          | 15:0          |       |  |  |  |  |  |  | DATA< |       |  |      |  |            |  | 0000 |

| B290                        | ADCDATA36 <sup>(2)</sup> | 31:16         |       |  |  |  |  |  |  | DATA< |       |  |      |  |            |  | 0000 |

|                             | (2)                      | 15:0          |       |  |  |  |  |  |  | DATA< |       |  |      |  |            |  | 0000 |

| B294                        | ADCDATA37 <sup>(2)</sup> | 31:16         |       |  |  |  |  |  |  |       |       |  | 0000 |  |            |  |      |

|                             | (2)                      | 15:0          |       |  |  |  |  |  |  | DATA< |       |  |      |  |            |  | 0000 |

| B298                        | ADCDATA38 <sup>(2)</sup> | 31:16         |       |  |  |  |  |  |  | DATA< |       |  |      |  |            |  | 0000 |

|                             | (2)                      | 15:0          |       |  |  |  |  |  |  | DATA< |       |  |      |  |            |  | 0000 |

| B29C                        | ADCDATA39 <sup>(2)</sup> |               |       |  |  |  |  |  |  | DATA< |       |  |      |  |            |  | 0000 |

|                             |                          | 15:0          |       |  |  |  |  |  |  | DATA< |       |  |      |  |            |  | 0000 |

| B2A0                        | ADCDATA40 <sup>(2)</sup> | 31:16         |       |  |  |  |  |  |  | DATA< |       |  |      |  |            |  | 0000 |

| DO A A                      | ADCDATA41(2)             | 15:0          |       |  |  |  |  |  |  | DATA< |       |  |      |  |            |  | 0000 |

| BZA4                        | ADCDATA41-               | 31:16         |       |  |  |  |  |  |  |       |       |  | 0000 |  |            |  |      |

| DOAD                        | ADCDATA42 <sup>(2)</sup> | 15:0<br>31:16 |       |  |  |  |  |  |  |       |       |  | 0000 |  |            |  |      |

| DZA0                        | ADCDATA42                | 15:0          |       |  |  |  |  |  |  |       |       |  | 0000 |  |            |  |      |

| BOAC                        | ADCDATA43                | 31:16         |       |  |  |  |  |  |  |       |       |  | 0000 |  |            |  |      |

| DZAC                        | -DCDA1A43                | 15:0          |       |  |  |  |  |  |  |       |       |  | 0000 |  |            |  |      |

| B2B0                        | ADCDATA44                | 31:16         |       |  |  |  |  |  |  | DATA< |       |  |      |  |            |  | 0000 |

| 0200                        |                          | 15:0          |       |  |  |  |  |  |  | DATA< |       |  |      |  |            |  | 0000 |

1: 2: 3:

This bit or register is not available on 64-pin devices. This bit or register is not available on 64-pin and 100-pin devices. Before enabling the ADC, the user application must initialize the ADC calibration values by copying them from the factory-programmed DEVADCx Flash registers into the corresponding ADCxCFG registers.

Note

# REGISTER 28-7: ADCIMCON3: ADC INPUT MODE CONTROL REGISTER 3 (CONTINUED)

- bit 1 DIFF32: AN32 Mode bit<sup>(1)</sup>

- 1 = AN32 is using Differential mode

- 0 = AN32 is using Single-ended mode

- bit 0 SIGN32: AN32 Signed Data Mode bit<sup>(1)</sup>

- 1 = AN32 is using Signed Data mode

- 0 = AN32 is using Unsigned Data mode

- Note 1: This bit is not available on 64-pin devices.

- 2: This bit is not available on 64-pin and 100-pin devices.

# REGISTER 28-14: ADCCMPENX: ADC DIGITAL COMPARATOR 'x' ENABLE REGISTER ('x' = 1 THROUGH 6)

|              |                       | <b>(</b>              |                       |                       |                       |                       |                       |                       |

|--------------|-----------------------|-----------------------|-----------------------|-----------------------|-----------------------|-----------------------|-----------------------|-----------------------|

| Bit<br>Range | Bit<br>31/23/15/7     | Bit<br>30/22/14/6     | Bit<br>29/21/13/5     | Bit<br>28/20/12/4     | Bit<br>27/19/11/3     | Bit<br>26/18/10/2     | Bit<br>25/17/9/1      | Bit<br>24/16/8/0      |

| 24.24        | R/W-0                 |

| 31:24        | CMPE31 <sup>(1)</sup> | CMPE30 <sup>(1)</sup> | CMPE29 <sup>(1)</sup> | CMPE28 <sup>(1)</sup> | CMPE27 <sup>(1)</sup> | CMPE26 <sup>(1)</sup> | CMPE25 <sup>(1)</sup> | CMPE24 <sup>(1)</sup> |

| 00.40        | R/W-0                 |

| 23:16        | CMPE23 <sup>(1)</sup> | CMPE22 <sup>(1)</sup> | CMPE21 <sup>(1)</sup> | CMPE20 <sup>(1)</sup> | CMPE19 <sup>(1)</sup> | CMPE18                | CMPE17                | CMPE16                |

| 45.0         | R/W-0                 |

| 15:8         | CMPE15                | CMPE14                | CMPE13                | CMPE12                | CMPE11                | CMPE10                | CMPE9                 | CMPE8                 |

| 7.0          | R/W-0                 |

| 7:0          | CMPE7                 | CMPE6                 | CMPE5                 | CMPE4                 | CMPE3                 | CMPE2                 | CMPE1                 | CMPE0                 |

|              | -                     | •                     | •                     | •                     | -                     | -                     |                       | -                     |

#### Legend:

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, read as '0'              |

|-------------------|------------------|-------------------------------------------------|

| -n = Value at POR | '1' = Bit is set | $0^{\circ}$ = Bit is cleared x = Bit is unknown |

# bit 31-0 CMPE31:CMPE0: ADC Digital Comparator 'x' Enable bits<sup>(2,3)</sup>

These bits enable conversion results corresponding to the Analog Input to be processed by the Digital Comparator. CMPE0 enables AN0, CMPE1 enables AN1, and so on.

**Note 1:** This bit is not available on 64-pin devices.

- **2**: CMPEx = ANx, where 'x' = 0.31 (Digital Comparator inputs are limited to AN0 through AN31).

- **3:** Changing the bits in this register while the Digital Comparator is enabled (ENDCMP = 1) can result in unpredictable behavior.

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |  |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|--|

| 24.24        | R-0, HS, HC       | R-0, HS, HC      | R-0, HS, HC      |  |

| 31:24        | CVDDATA<15:8>     |                   |                   |                   |                   |                   |                  |                  |  |

| 23:16        | R-0, HS, HC       | R-0, HS, HC      | R-0, HS, HC      |  |

| 23.10        | CVDDATA<7:0>      |                   |                   |                   |                   |                   |                  |                  |  |

| 15.0         | U-0               | U-0               | R-0, HS, HC       | R-0, HS, HC       | R-0, HS, HC       | R-0, HS, HC       | R-0, HS, HC      | R-0, HS, HC      |  |

| 15:8         |                   | —                 |                   |                   | AINID             | <5:0>             |                  |                  |  |

| 7.0          | R/W-0             | R/W-0             | R-0, HS, HC       | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |

| 7:0          | ENDCMP            | DCMPGIEN          | DCMPED            | IEBTWN            | IEHIHI            | IEHILO            | IELOHI           | IELOLO           |  |

### REGISTER 28-20: ADCCMPCON1: ADC DIGITAL COMPARATOR 1 CONTROL REGISTER

| Legend:           | HS = Hardware Set | HC = Hardware Cleared                    |

|-------------------|-------------------|------------------------------------------|

| R = Readable bit  | W = Writable bit  | U = Unimplemented bit, read as '0'       |

| -n = Value at POR | '1' = Bit is set  | 0' = Bit is cleared $x = Bit is unknown$ |

#### bit 31-16 CVDDATA<15:0>: CVD Data Status bits

In CVD mode, these bits obtain the CVD differential output data (subtraction of CVD positive and negative measurement), whenever a Digital Comparator interrupt is generated. The value in these bits is compliant with the FRACT bit (ADCCON1<23>) and is always signed.

#### bit 15-14 Unimplemented: Read as '0'

## bit 13-8 AINID<5:0>: Digital Comparator 0 Analog Input Identification (ID) bits

When a digital comparator event occurs (DCMPED = 1), these bits identify the analog input being monitored by Digital Comparator 0.

**Note:** In normal ADC mode, only analog inputs <31:0> can be processed by the Digital Comparator 0. The Digital Comparator 0 also supports the CVD mode, in which all Class 2 and Class 3 analog inputs may be stored in the AINID<5:0> bits.

| 111111 = Reserved                                                                                                                                    |

|------------------------------------------------------------------------------------------------------------------------------------------------------|

| •                                                                                                                                                    |

|                                                                                                                                                      |

| 101101 = Reserved                                                                                                                                    |

| 101100 = AN44 is being monitored                                                                                                                     |

| 101001 = AN43 is being monitored                                                                                                                     |

|                                                                                                                                                      |

|                                                                                                                                                      |

| •                                                                                                                                                    |

| 000001 = AN1 is being monitored                                                                                                                      |

| 000000 = ANO is being monitored                                                                                                                      |

| ENDCMP: Digital Comparator 0 Enable bit                                                                                                              |

| 1 = Digital Comparator 0 is enabled                                                                                                                  |

| 0 = Digital Comparator 0 is not enabled, and the DCMPED status bit (ADCCMP0CON<5>) is cleared                                                        |

| DCMPGIEN: Digital Comparator 0 Global Interrupt Enable bit                                                                                           |

| 1 = A Digital Comparator 0 interrupt is generated when the DCMPED status bit (ADCCMP0CON<5>) is set 0 = A Digital Comparator 0 interrupt is disabled |

| <b>DCMPED:</b> Digital Comparator 0 "Output True" Event Status bit                                                                                   |

| The logical conditions under which the digital comparator gets "True" are defined by the IEBTWN, IEHIHI,                                             |

| IEHILO, IELOHI, and IELOLO bits.                                                                                                                     |

| <b>Note:</b> This bit is cleared by reading the AINID<5:0> bits or by disabling the Digital Comparator module (by setting ENDCMP to '0').            |

| 1 = Digital Comparator 0 output true event has occurred (output of Comparator is '1')                                                                |

| 0 = Digital Comparator 0 output is false (output of comparator is '0')                                                                               |

| IEBTWN: Between Low/High Digital Comparator 0 Event bit                                                                                              |

|                                                                                                                                                      |

| 1 = Generate a digital comparator event when DCMPLO<15:0> $\leq$ DATA<31:0> < DCMPHI<15:0>                                                           |

|                                                                                                                                                      |

| REGISTER 30-17: | ETHFRMTXOK: ETHERNET CONTROLLER FRAMES TRANSMITTED OK |

|-----------------|-------------------------------------------------------|

|                 | STATISTICS REGISTER                                   |

| Bit<br>Range                        | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |

|-------------------------------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|

| 31:24                               | U-0               | U-0 U-0 U-0       | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 31.24                               | —                 | —                 | —                 | —                 | —                 | _                 | —                | —                |

| 22.16                               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 23:16                               | —                 | —                 | —                 | —                 | —                 | _                 | _                | —                |

| 15.0                                | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |

| 15:8                                |                   |                   |                   | FRMTXOK           | CNT<15:8>         |                   |                  |                  |

| R/W-0 R/W-0 R/W-0 R/W-0 R/W-0 R/W-0 |                   |                   |                   | R/W-0             | R/W-0             | R/W-0             |                  |                  |

| 7:0                                 |                   |                   |                   | FRMTXOK           | (CNT<7:0>         |                   |                  |                  |

## Legend:

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, r | read as '0'        |

|-------------------|------------------|--------------------------|--------------------|

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared     | x = Bit is unknown |

#### bit 31-16 Unimplemented: Read as '0'

bit 15-0 **FRMTXOKCNT<15:0>:** Frame Transmitted OK Count bits Increment counter for frames successfully transmitted.

Note 1: This register is only used for TX operations.

2: This register is automatically cleared by hardware after a read operation, unless the byte enables for bytes 0/1 are '0'.

**3:** It is recommended to use the SET, CLR, or INV registers to set or clear any bit in this register. Setting or clearing any bits in this register should only be done for debug/test purposes.

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5     | Bit<br>28/20/12/4      | Bit<br>27/19/11/3     | Bit<br>26/18/10/2 | Bit<br>25/17/9/1      | Bit<br>24/16/8/0       |

|--------------|-------------------|-------------------|-----------------------|------------------------|-----------------------|-------------------|-----------------------|------------------------|

| 04-04        | U-0               | U-0               | U-0                   | U-0                    | U-0                   | U-0               | R/W-0                 | R/W-0                  |

| 31:24        | —                 | —                 | —                     | —                      | —                     | —                 | DMAPRI <sup>(1)</sup> | CPUPRI <sup>(1)</sup>  |

| 00.40        | U-0               | U-0               | U-0                   | U-0                    | U-0                   | U-0               | U-0 R/W-0             | R/W-0                  |