Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XF

| Product Status             | Active                                                                           |

|----------------------------|----------------------------------------------------------------------------------|

| Core Processor             | MIPS32® M-Class                                                                  |

| Core Size                  | 32-Bit Single-Core                                                               |

| Speed                      | 180MHz                                                                           |

| Connectivity               | Ethernet, I <sup>2</sup> C, PMP, SPI, SQI, UART/USART, USB OTG                   |

| Peripherals                | Brown-out Detect/Reset, DMA, I <sup>2</sup> S, POR, PWM, WDT                     |

| Number of I/O              | 46                                                                               |

| Program Memory Size        | 1MB (1M x 8)                                                                     |

| Program Memory Type        | FLASH                                                                            |

| EEPROM Size                | -                                                                                |

| RAM Size                   | 256K x 8                                                                         |

| Voltage - Supply (Vcc/Vdd) | 2.1V ~ 3.6V                                                                      |

| Data Converters            | A/D 24x12b                                                                       |

| Oscillator Type            | Internal                                                                         |

| Operating Temperature      | -40°C ~ 125°C                                                                    |

| Mounting Type              | Surface Mount                                                                    |

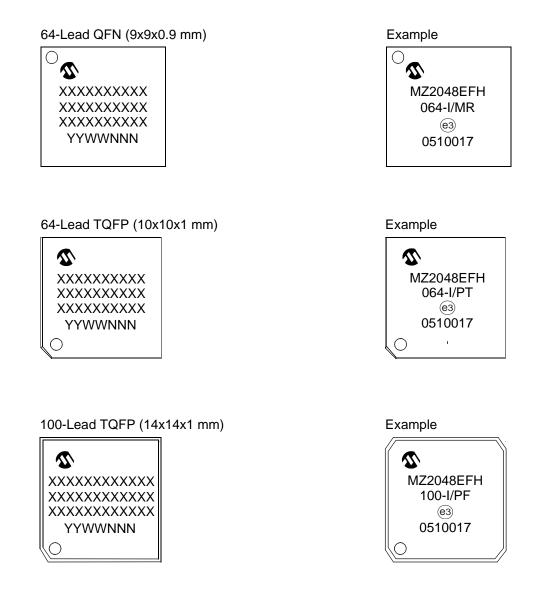

| Package / Case             | 64-VFQFN Exposed Pad                                                             |

| Supplier Device Package    | 64-QFN (9x9)                                                                     |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic32mz1024efe064-e-mr |

|                            |                                                                                  |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

| REGISTER 3-9: | FENR: FLOATING POINT EXCEPTIONS AND MODES ENABLE REGISTER; |

|---------------|------------------------------------------------------------|

|               | CP1 REGISTER 28                                            |

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |  |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|--|

| 24.24        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |  |

| 31:24        | —                 | —                 |                   |                   |                   |                   | _                | _                |  |

| 22:46        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |  |

| 23:16        | —                 | —                 | -                 | —                 | -                 | _                 | _                | _                |  |

|              | U-0               | U-0               | U-0               | U-0               | R/W-x             | R/W-x             | R/W-x            | R/W-x            |  |

| 15:8         |                   |                   |                   |                   | ENABLES<4:1>      |                   |                  |                  |  |

|              | _                 | _                 | _                 | _                 | V                 | Z                 | 0                | U                |  |

|              | R/W-x             | U-0               | U-0               | U-0               | U-0               | R-x               | R/W-x            | R/W-x            |  |

| 7:0          | ENABLES<0>        |                   |                   |                   |                   | FS                | DM               | .1.0             |  |

|              | I                 |                   |                   |                   |                   | гð                | RM<1:0>          |                  |  |

| Legend:           |                  |                          |                    |

|-------------------|------------------|--------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, r | read as '0'        |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared     | x = Bit is unknown |

#### bit 31-12 Unimplemented: Read as '0'

bit 11-7 ENABLES<4:0>: FPU Exception Enable bits

These bits control whether or not a trap is taken when an IEEE exception condition occurs for any of the five conditions. The trap occurs when both an enable bit and its corresponding cause bit are set either during an FPU arithmetic operation or by moving a value to the FCSR or one of its alternative representations.

- bit 11 V: Invalid Operation bit

- bit 10 Z: Divide-by-Zero bit

- bit 9 O: Overflow bit

- bit 8 **U:** Underflow bit

- bit 7 I: Inexact bit

- bit 6-3 Unimplemented: Read as '0'

- bit 2 FS: Flush to Zero control bit

1 = Denormal input operands are flushed to zero. Tiny results are flushed to either zero or the applied format's smallest normalized number (MinNorm) depending on the rounding mode settings.

0 = Denormal input operands result in an Unimplemented Operation exception.

- bit 1-0 RM<1:0>: Rounding Mode control bits

- 11 = Round towards Minus Infinity  $(-\infty)$

- 10 = Round towards Plus Infinity (+  $\infty$ )

- 01 = Round toward Zero (0)

- 00 = Round to Nearest

#### **TABLE 7-3: INTERRUPT REGISTER MAP (CONTINUED)**

| ress<br>()                  |                                 | Ð         |       |       |       |       |       |       |      | Bi         | ts   |      |      |      |      |      |       |        | s          |

|-----------------------------|---------------------------------|-----------|-------|-------|-------|-------|-------|-------|------|------------|------|------|------|------|------|------|-------|--------|------------|

| Virtual Address<br>(BF81_#) | Register<br>Name <sup>(1)</sup> | Bit Range | 31/15 | 30/14 | 29/13 | 28/12 | 27/11 | 26/10 | 25/9 | 24/8       | 23/7 | 22/6 | 21/5 | 20/4 | 19/3 | 18/2 | 17/1  | 16/0   | All Resets |

|                             | OFF032                          | 31:16     | _     | _     | -     | —     | -     | _     | -    | _          | _    | _    | —    | _    | —    | —    | VOFF< | 17:16> | 0000       |

| 0500                        | OFF032                          | 15:0      |       |       |       |       |       |       |      | VOFF<15:1> |      |      |      |      |      |      |       | —      | 0000       |

| 0504                        | OFF033                          | 31:16     | _     | _     | _     | _     | _     | _     | _    | _          | _    | _    | _    | _    | _    | _    | VOFF< | 17:16> | 0000       |

| 0504                        | 066033                          | 15:0      |       |       |       |       |       |       |      | VOFF<15:1> |      |      |      |      |      |      |       | _      | 0000       |

| 0500                        | OFF034                          | 31:16     | —     |       | —     | _     | _     | -     | _    |            | —    |      | _    | —    | —    | —    | VOFF< | 17:16> | 0000       |

| 0508                        | 0FF034                          | 15:0      |       |       |       |       |       |       |      | VOFF<15:1> |      |      |      |      |      |      |       | _      | 0000       |

| 0500                        | OFF035                          | 31:16     | —     |       | _     | _     |       |       |      | —          | _    |      | —    | _    | —    | _    | VOFF< | 17:16> | 0000       |

| 0500                        | 0FF035                          | 15:0      |       |       |       |       |       |       |      | VOFF<15:1> |      |      |      |      |      |      |       | _      | 0000       |

| 0500                        | OFF036                          | 31:16     | —     |       | —     | _     |       |       |      |            | —    |      | —    | —    | —    | —    | VOFF< | 17:16> | 0000       |

| 0500                        | 066030                          | 15:0      |       |       |       |       |       |       |      | VOFF<15:1> |      |      |      |      |      |      |       | _      | 0000       |

| 05D4                        | OFF037                          | 31:16     | —     |       | —     | _     |       |       |      | —          | —    |      | —    | —    | _    | _    | VOFF< | 17:16> | 0000       |

| 0304                        | 15:0 VOFF<15:1>                 |           |       |       |       |       |       |       | —    | 0000       |      |      |      |      |      |      |       |        |            |

| 0508                        | OFF038                          | 31:16     | _     | -     | —     | —     | -     | -     | -    | _          | _    | -    | —    | —    | —    | —    | VOFF< | 17:16> | 0000       |

| 0300                        | 011030                          | 15:0      |       |       | -     | -     |       |       |      | VOFF<15:1> |      |      |      |      | -    | -    | -     | —      | 0000       |

| 05DC                        | OFF039                          | 31:16     | _     | —     | -     | —     | _     | —     | _    | —          | _    | _    | —    | _    | —    | —    | VOFF< | 17:16> | 0000       |

| 0300                        | 011039                          | 15:0      |       |       |       |       |       |       |      | VOFF<15:1> |      |      |      |      |      |      |       | —      | 0000       |

| 0550                        | OFF040                          | 31:16     | _     | _     |       |       |       |       |      | —          | _    |      | —    | _    |      |      | VOFF< | 17:16> | 0000       |

| 0520                        | 011040                          | 15:0      |       |       | -     | -     |       |       |      | VOFF<15:1> |      |      |      |      | -    | -    | -     |        | 0000       |

| 05E4                        | OFF041                          | 31:16     | _     | —     | -     | —     | _     | —     | _    | —          | _    |      | —    | _    | —    | —    | VOFF< | 17:16> | 0000       |

| 0564                        | 011041                          | 15:0      |       |       |       |       |       |       |      | VOFF<15:1> |      |      |      |      |      |      |       |        | 0000       |

| 05E8                        | OFF042                          | 31:16     | _     | —     | -     | —     | _     | —     | _    | —          | _    |      | —    | _    | —    | —    | VOFF< | 17:16> | 0000       |

| 0520                        | 011042                          | 15:0      |       |       | -     | -     |       |       |      | VOFF<15:1> |      |      |      |      | -    | -    | -     |        | 0000       |

| 05EC                        | OFF043                          | 31:16     | —     | —     | —     | —     | —     | —     | —    | —          | —    | —    | —    | —    | —    | —    | VOFF< | 17:16> | 0000       |

| 0520                        | 011043                          | 15:0      |       |       |       |       |       |       |      | VOFF<15:1> |      |      |      |      |      |      |       |        | 0000       |

| 05E0                        | OFF044                          | 31:16     | —     | —     | —     | —     | —     | —     | —    | —          | —    | —    | —    | _    | —    | —    | VOFF< | 17:16> | 0000       |

| 001 0                       | 011044                          | 15:0      |       |       | -     | -     |       |       |      | VOFF<15:1> |      |      |      |      | -    | -    | -     | —      | 0000       |

| 05F4                        | OFF045                          | 31:16     | —     | —     | —     | _     | _     | _     | _    | —          | _    | —    | —    | _    | —    | —    | VOFF< | 17:16> | 0000       |

| 0014                        | 011040                          | 15:0      |       |       |       |       |       |       |      | VOFF<15:1> |      |      |      |      |      | -    | -     |        | 0000       |

| 0558                        | OFF046                          | 31:16     | —     | _     | -     |       | _     | _     | —    | —          | _    | _    | —    | _    | —    | —    | VOFF< | 17:16> | 0000       |

| 05-0                        |                                 | 15:0      |       |       |       |       |       |       |      | VOFF<15:1> |      |      |      |      |      |      |       | _      | 0000       |

© 2015-2016 Microchip Technology Inc.

Legend: x = unknown value on Reset; — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

Note 1: All registers in this table with the exception of the OFFx registers, have corresponding CLR, SET, and INV registers at their virtual addresses, plus offsets of 0x4, 0x8 and 0xC, respectively. See Section 12.3 "CLR, SET, and INV **Registers**" for more information. This bit or register is not available on 64-pin devices.

This bit or register is not available on devices without a CAN module. 3:

4: This bit or register is not available on 100-pin devices.

- Bits 31 and 30 are not available on 64-pin and 100-pin devices; bits 29 through 14 are not available on 64-pin devices. 5:

- Bits 31, 30, 29, and bits 5 through 0 are not available on 64-pin and 100-pin devices; bit 31 is not available on 124-pin devices; bit 22 is not available on 64-pin devices. 6:

7: This bit or register is not available on devices without a Crypto module.

This bit or register is not available on 124-pin devices. 8:

<sup>2:</sup>

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |  |  |  |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|--|--|--|

| 24.24        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |  |  |  |

| 31:24        | —                 | —                 | —                 |                   | —                 | —                 | _                | —                |  |  |  |

| 00.40        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | R/W-0            | R/W-0            |  |  |  |

| 23:16        | —                 | — — — — — VOFF<   |                   |                   |                   |                   |                  | 17:16>           |  |  |  |

| 15.0         | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |  |  |

| 15:8         | VOFF<15:8>        |                   |                   |                   |                   |                   |                  |                  |  |  |  |

| 7.0          | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | U-0              |  |  |  |

| 7:0          | VOFF<7:1>         |                   |                   |                   |                   |                   |                  |                  |  |  |  |

#### **REGISTER 7-8:** OFFx: INTERRUPT VECTOR ADDRESS OFFSET REGISTER (x = 0-190)

| Legend:           |                  |                      |                    |

|-------------------|------------------|----------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented b  | it, read as '0'    |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared | x = Bit is unknown |

bit 31-16 Unimplemented: Read as '0'

bit 17-1 VOFF<17:1>: Interrupt Vector 'x' Address Offset bits

bit 0 Unimplemented: Read as '0'

| ŝ                           |                  |               |                                |                                   |       |       |                     |              |          |        | Bits          |                    |          |          |                       |          |         |        |            |

|-----------------------------|------------------|---------------|--------------------------------|-----------------------------------|-------|-------|---------------------|--------------|----------|--------|---------------|--------------------|----------|----------|-----------------------|----------|---------|--------|------------|

| Virtual Address<br>(BF8E_#) | Register<br>Name | Bit Range     | 31/15                          | 30/14                             | 29/13 | 28/12 | 27/11               | 26/10        | 25/9     | 24/8   | 23/7          | 22/6               | 21/5     | 20/4     | 19/3                  | 18/2     | 17/1    | 16/0   | All Resets |

| 3028                        | USB              | 31:16         |                                |                                   |       |       |                     |              |          |        | ATA<31:16>    |                    |          |          |                       |          |         |        | 00         |

| 020                         | FIFO2            | 15:0          |                                |                                   |       |       |                     |              |          |        | ATA<15:0>     |                    |          |          |                       |          |         |        | 00         |

| 02C                         | USB<br>FIFO3     | 31:16         |                                |                                   |       |       |                     |              |          |        | ATA<31:16>    |                    |          |          |                       |          |         |        | 00         |

|                             |                  | 15:0          |                                | DATA<15:0> 000                    |       |       |                     |              |          |        |               |                    |          |          |                       |          |         |        |            |

| 8030                        | USB<br>FIFO4     | 31:16<br>15:0 |                                | DATA<31:16> 000 DATA<15:0> 000    |       |       |                     |              |          |        |               |                    |          |          |                       |          |         |        |            |

|                             | USB              | 31:16         |                                | DATA<31:16> 0000                  |       |       |                     |              |          |        |               |                    |          |          |                       |          |         |        |            |

| 3034                        | FIFO5            | 15:0          |                                | DATA<15:0> 000                    |       |       |                     |              |          |        |               |                    |          |          |                       |          |         |        |            |

|                             | USB              | 31:16         |                                | DATA<31:16> 0000                  |       |       |                     |              |          |        |               |                    |          |          |                       |          |         |        |            |

| 3038                        | FIFO6            | 15:0          |                                | DATA<31:16> 000<br>DATA<15:0> 000 |       |       |                     |              |          |        |               |                    |          |          |                       |          |         |        |            |

|                             | USB              | 31:16         | DATA<31:16> 000                |                                   |       |       |                     |              |          |        |               |                    |          |          |                       |          |         |        |            |

| 03C                         | FIF07            | 15:0          |                                |                                   |       |       |                     |              |          | D      | ATA<15:0>     |                    |          |          |                       |          |         |        | 00         |

|                             | USBOTO           | 31:16         | _                              | _                                 | _     | RXDPB |                     | RXFIFC       | )SZ<3:0> |        | _             | _                  | _        | TXDPB    |                       | TXFIFOSZ | <3:0>   |        | 0 (        |

| 8060                        | USBOTG           | 15:0          | _                              | _                                 | -     | —     | —                   | _            | TXEDMA   | RXEDMA | BDEV          | FSDEV              | LSDEV    | VBUS     | <1:0>                 | HOSTMODE | HOSTREQ | SESSIO | N 00       |

| 8064                        | USB              | 31:16         | RXFIFOAD<12:0> 00              |                                   |       |       |                     |              |          |        |               |                    |          |          |                       |          |         |        |            |

| 004                         | FIFOA            | 15:0          | —                              | -                                 | —     |       |                     |              |          |        |               | TXFIFOAD<1         | 2:0>     |          |                       |          |         |        | 00         |

| 806C                        | USB              | 31:16         | —                              |                                   | —     | _     | _                   | _            | —        | —      | —             | _                  | _        | —        | _                     | _        | —       | —      | 00         |

|                             | HWVER            | 15:0          | RC VERMAJOR<4:0> VERMINOR<9:0> |                                   |       |       |                     |              |          | 08     |               |                    |          |          |                       |          |         |        |            |

| 3078                        | USB              | 31:16         | VPLEN<7:0>                     |                                   |       |       |                     |              |          |        |               |                    | DN<3:0>  |          |                       | WTID<3   |         |        | 30         |

|                             | INFO             | 15:0          |                                | DMACHANS<3:0>                     |       |       |                     | RAMBITS<3:0> |          |        |               | RXEND              | PTS<3:0> |          |                       | TXENDPTS | <3:0>   |        | 8C         |

| 307C                        | USB<br>EOFRST    | 31:16         | —                              | _                                 | _     | -     |                     | -            | NRSTX    | NRST   |               |                    |          | LSEOF<7: |                       |          |         |        | 00         |

|                             |                  | 15:0          |                                |                                   |       | FSEOF | -<7:0><br>(HUBPRT<6 |              |          |        |               |                    |          | HSEOF<7: |                       |          |         |        | 77         |

| 3080                        | USB<br>E0TXA     | 31:16<br>15:0 |                                |                                   | _     |       |                     | >            | _        | _      | MULTTRAN      |                    |          |          | BADD<6:0><br>DDR<6:0> |          |         |        | 00         |

|                             |                  | 31:16         |                                | _                                 | _     |       | HUBPRT<6            |              | _        | _      | —<br>MULTTRAN |                    |          |          | BADD<6:0>             |          |         |        | 00         |

| 3084                        | USB<br>E0RXA     | 15:0          |                                |                                   | _     | _     |                     |              | _        | _      |               | _                  | _        | _        |                       | _        | _       | _      | 00         |

|                             | USB              | 31:16         | _                              |                                   |       | ТХ    | HUBPRT<6            | :0>          |          |        | MULTTRAN      |                    |          | TXHU     | BADD<6:0>             |          |         |        | 0.0        |

| 3088                        | E1TXA            | 15:0          | _                              | _                                 | _     | _     | _                   | _            |          | _      | _             |                    |          |          | DDR<6:0>              |          |         |        | 0.0        |

|                             | USB              | 31:16         | _                              |                                   |       | RX    | HUBPRT<6            | 6:0>         |          |        | MULTTRAN      |                    |          | RXHU     | BADD<6:0>             |          |         |        | 00         |

| 08C                         | E1RXA            | 15:0          | _                              |                                   | _     |       | _                   | _            | _        | _      | _             |                    |          | RXFA     | DDR<6:0>              |          |         |        | 0.0        |

| 0000                        | USB              | 31:16         | _                              |                                   | •     | ТХ    | HUBPRT<6            | :0>          |          |        | MULTTRAN      |                    |          | TXHU     | BADD<6:0>             |          |         |        | 0.0        |

| 3090                        | E2TXA            | 15:0          | _                              | _                                 | _     | _     | —                   | —            | _        | —      |               | - TXFADDR<6:0>     |          |          |                       |          |         | 0.0    |            |

| 3094                        | USB              | 31:16         | —                              |                                   |       | RX    | (HUBPRT<6           | 6:0>         |          |        | MULTTRAN      | TRAN RXHUBADD<6:0> |          |          |                       |          |         |        | 00         |

| JU 34                       | E2RXA            | 15:0          | —                              |                                   | —     | —     | —                   | -            | —        | _      | _             | - RXFADDR<6:0>     |          |          |                       |          |         |        | 00         |

| 3098                        | USB              | 31:16         | _                              |                                   |       | ТХ    | HUBPRT<6            | :0>          |          |        | MULTTRAN      |                    |          |          | BADD<6:0>             |          |         |        | 00         |

|                             | E3TXA            | 15:0          | _                              | _                                 | _     | _     |                     | _            | _        |        |               |                    |          | TXFA     | DDR<6:0>              |          |         |        | 00         |

#### TABLE 11-1: USB REGISTER MAP 1 (CONTINUED)

#### REGISTER 11-8: USBIENCSR0: USB INDEXED ENDPOINT CONTROL STATUS REGISTER 0 (ENDPOINT 1-7) (CONTINUED)

#### bit 15-11 MULT<4:0>: Multiplier Control bits

For Isochronous/Interrupt endpoints or of packet splitting on Bulk endpoints, multiplies TXMAXP by MULT+1 for the payload size.

For Bulk endpoints, MULT can be up to 32 and defines the number of "USB" packets of the specified payload into which a single data packet placed in the FIFO should be split, prior to transfer. The data packet is required to be an exact multiple of the payload specified by TXMAXP.

For Isochronous/Interrupts endpoints operating in Hi-Speed mode, MULT may be either 2 or 3 and specifies the maximum number of such transactions that can take place in a single microframe.

#### bit 10-0 TXMAXP<10:0>: Maximum TX Payload per transaction Control bits

This field sets the maximum payload (in bytes) transmitted in a single transaction. The value is subject to the constraints placed by the USB Specification on packet sizes for Bulk, Interrupt and Isochronous transfers in Full-Speed and Hi-Speed operations.

TXMAXP must be set to an even number of bytes for proper interrupt generation in DMA Mode 1.

#### TABLE 12-16: PORTG REGISTER MAP FOR 64-PIN DEVICES ONLY

| SSS                         |                                 |           |       |       |       |       |                |       |              | Bi           | ts           |              |      |      |      |      |      |      |               |

|-----------------------------|---------------------------------|-----------|-------|-------|-------|-------|----------------|-------|--------------|--------------|--------------|--------------|------|------|------|------|------|------|---------------|

| Virtual Address<br>(BF86_#) | Register<br>Name <sup>(1)</sup> | Bit Range | 31/15 | 30/14 | 29/13 | 28/12 | 27/11          | 26/10 | 25/9         | 24/8         | 23/7         | 22/6         | 21/5 | 20/4 | 19/3 | 18/2 | 17/1 | 16/0 | All<br>Resets |

| 0600                        | ANSELG                          | 31:16     | _     | —     | —     | -     | —              | —     | —            | —            | —            |              | -    | —    | -    | —    | _    | —    | 0000          |

| 0000                        | ANGLEG                          | 15:0      | _     | _     | _     | _     | _              | _     | ANSG9        | ANSG8        | ANSG7        | ANSG6        | _    | _    | _    | _    | _    | —    | 03C0          |

| 0610                        | TRISG                           | 31:16     | —     | _     | —     | _     | —              | _     | —            | _            | _            | _            | _    | —    | _    | _    |      | —    | 0000          |

| 0010                        | 11100                           | 15:0      | —     | _     | —     | _     | —              | _     | TRISG9       | TRISG8       | TRISG7       | TRISG6       | _    | —    | _    | —    |      | —    | 03C0          |

| 0620                        | PORTG                           | 31:16     | —     | _     | —     | _     | —              | _     | —            | _            | _            | _            | _    | —    | _    | _    |      | —    | 0000          |

| 0020                        | TOKIO                           | 15:0      | —     | _     | —     | _     | —              | _     | RG9          | RG8          | RG7          | RG6          | _    | —    | _    | —    |      | —    | xxxx          |

| 0630                        | LATG                            | 31:16     | —     | _     | —     | _     | —              | _     | —            | _            | _            | —            | _    | —    | _    | —    |      | —    | 0000          |

| 0000                        | DAIO                            | 15:0      | —     | _     | —     | _     | —              | _     | LATG9        | LATG8        | LATG7        | LATG6        | _    | —    | _    | —    | _    | —    | xxxx          |

| 0640                        | ODCG                            | 31:16     | —     | _     | —     | _     | —              | _     | —            |              |              | —            | _    | —    | _    | —    | _    | —    | 0000          |

| 0040                        | 0000                            | 15:0      | —     | _     | —     | _     | —              | _     | ODCG9        | ODCG8        | ODCG7        | ODCG6        | _    | —    | _    | —    | _    | —    | 0000          |

| 0650                        | CNPUG                           | 31:16     | —     | —     | —     | —     | —              | —     | —            | —            | —            | —            | —    | —    | —    | —    | _    | —    | 0000          |

| 0000                        |                                 | 15:0      | _     | _     | —     | —     | —              | _     | CNPUG9       | CNPUG8       | CNPUG7       | CNPUG6       | —    | —    | —    | —    | _    | —    | 0000          |

| 0660                        | CNPDG                           | 31:16     | _     | -     | —     | -     | —              | _     | —            | _            | _            |              | -    | —    | -    | —    | _    | -    | 0000          |

|                             | 0.1. 20                         | 15:0      | _     | -     | —     | -     | —              | _     | CNPDG9       | CNPDG8       | CNPDG7       | CNPDG6       | -    | —    | -    | —    | _    | -    | 0000          |

|                             |                                 | 31:16     | —     | -     | —     | -     | —              | _     | —            | _            | _            |              | -    | —    | -    | —    | _    | -    | 0000          |

| 0670                        | CNCONG                          | 15:0      | ON    | _     | _     |       | EDGE<br>DETECT | —     | —            | —            | —            | _            |      | —    | -    | —    | _    | _    | 0000          |

| 0680                        | CNENG                           | 31:16     | -     |       | _     |       | _              | _     | —            |              |              |              |      | _    |      | -    |      | —    | 0000          |

| 0000                        | CINEINO                         | 15:0      | _     | -     | _     | -     | —              | _     | CNENG9       | CNENG8       | CNENG7       | CNENG6       | -    | _    | _    | _    | _    | —    | 0000          |

|                             |                                 | 31:16     | —     | -     | —     | -     | —              | —     | —            | _            | _            | —            | -    | —    | -    | —    | -    | —    | 0000          |

| 0690                        | CNSTATG                         | 15:0      | —     | -     | _     | _     | —              | _     | CN<br>STATG9 | CN<br>STATG8 | CN<br>STATG7 | CN<br>STATG6 |      | —    |      | —    |      | —    | 0000          |

| 0640                        |                                 | 31:16     |       | _     | _     | _     | _              | _     | _            | _            | _            | _            | _    | _    | _    | _    | _    | —    | 0000          |

| 06A0                        | CNNEG                           | 15:0      | _     | _     | —     | _     | —              | _     | CNNEG9       | CNNEG8       | CNNEG7       | CNNEG6       | _    | _    |      | —    | _    | —    | 0000          |

| 06B0                        | CNFG                            | 31:16     | _     | _     |       |       |                |       | —            | —            | —            | —            |      | —    |      | —    |      | —    | 0000          |

| 0000                        | UNFG                            | 15:0      | _     | _     | _     | _     | —              | _     | CNFG9        | CNFG8        | CNFG7        | CNFG6        | _    | —    |      | _    | -    | —    | 0000          |

| 0600                        | SRCON0G                         | 31:16     | —     | _     | —     | _     | —              | _     | —            | _            | _            |              | _    | —    | _    | —    | _    | —    | 0000          |

|                             | GREUNUG                         | 15:0      | _     | _     | _     |       | —              | _     | SR0G9        | _            | _            | SR0G6        | _    | —    |      | —    | -    | —    | 0000          |

|                             | SRCON1G                         | 31:16     | _     | _     | —     | _     | —              | —     | -            | —            | —            |              | _    | —    | _    | —    | _    | —    | 0000          |

|                             | SILCONIG                        | 15:0      | _     | _     | _     | _     | _              | _     | SR1G9        | _            |              | SR1G6        | _    | _    | _    |      | _    | —    | 0000          |

Legend:

x = Unknown value on Reset; — = Unimplemented, read as '0'; Reset values are shown in hexadecimal. All registers in this table have corresponding CLR, SET and INV registers at its virtual address, plus an offset of 0x4, 0x8 and 0xC, respectively. See Section 12.3 "CLR, SET, and INV Registers" for Note 1: more information.

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |  |  |  |  |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|--|--|--|--|

| 24.24        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |  |  |  |  |

| 31:24        |                   | —                 | _                 | —                 | —                 | -                 | _                | —                |  |  |  |  |

| 22.16        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |  |  |  |  |

| 23:16        |                   | —                 |                   |                   |                   |                   |                  | —                |  |  |  |  |

| 45.0         | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |  |  |  |

| 15:8         | POLLCON<15:8>     |                   |                   |                   |                   |                   |                  |                  |  |  |  |  |

| 7.0          | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |  |  |  |

| 7:0          | POLLCON<7:0>      |                   |                   |                   |                   |                   |                  |                  |  |  |  |  |

#### REGISTER 20-18: SQI1BDPOLLCON: SQI BUFFER DESCRIPTOR POLL CONTROL REGISTER

## Legend:R = Readable bitW = Writable bitU = Unimplemented bit, read as '0'-n = Value at POR'1' = Bit is set'0' = Bit is clearedx = Bit is unknown

#### bit 31-16 Unimplemented: Read as '0'

bit 15-0 **POLLCON<15:0>:** Buffer Descriptor Processor Poll Status bits These bits indicate the number of cycles the BDP would wait before refetching the descriptor control word if the previous descriptor fetched was disabled.

### REGISTER 20-19: SQI1BDTXDSTAT: SQI BUFFER DESCRIPTOR DMA TRANSMIT STATUS REGISTER

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |  |  |  |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|--|--|--|

| 04.04        | U-0               | U-0               | U-0               | R-x R-x           |                   | R-x               | R-x              | U-0              |  |  |  |

| 31:24        |                   | —                 | _                 |                   | TXSTATE<3:0>      |                   |                  |                  |  |  |  |

| 00.40        | U-0               | U-0               | U-0               | R-x               | R-x               | R-x               | R-x              | R-x              |  |  |  |

| 23:16        | —                 | —                 | _                 |                   |                   |                   |                  |                  |  |  |  |

| 45.0         | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |  |  |  |

| 15:8         | —                 | —                 | _                 | _                 | —                 | —                 | _                | —                |  |  |  |

| 7.0          | R-x               | R-x               | R-x               | R-x               | R-x               | R-x               | R-x              | R-x              |  |  |  |

| 7:0          |                   |                   |                   | TXCURBUF          | LEN<7:0>          |                   |                  |                  |  |  |  |

| Legend:           |                  |                          |                    |

|-------------------|------------------|--------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, r | ead as '0'         |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared     | x = Bit is unknown |

bit 31-29 Unimplemented: Read as '0'

bit 28-25 **TXSTATE<3:0>:** Current DMA Transmit State Status bits These bits provide information on the current DMA receive states.

bit 24-21 Unimplemented: Read as '0'

bit 20-16 **TXBUFCNT<4:0>:** DMA Buffer Byte Count Status bits

These bits provide information on the internal FIFO space.

bit 15-8 **Unimplemented:** Read as '0'

bit 7-0 **TXCURBUFLEN<7:0>:** Current DMA Transmit Buffer Length Status bits These bits provide the length of the current DMA transmit buffer.

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0    |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|---------------------|

| 24.24        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0                 |

| 31:24        |                   | —                 | —                 | —                 | —                 | -                 | _                | —                   |

| 22.10        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0                 |

| 23:16        | —                 | —                 | —                 | -                 | —                 | -                 | _                | —                   |

| 45.0         | R/W-0             | U-0               | R/W-0             | R/W-0             | R/W-0             | U-0               | R/W-0            | R/W-0               |

| 15:8         | ON                | —                 | SIDL              | IREN              | RTSMD             | _                 | UEN<             | 1:0> <sup>(1)</sup> |

| 7.0          | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0               |

| 7:0          | WAKE              | LPBACK            | ABAUD             | RXINV             | BRGH              | PDSEL             | <1:0>            | STSEL               |

#### REGISTER 22-1: UXMODE: UARTX MODE REGISTER

#### Legend:

| Logona.           |                  |                                    |                    |  |  |  |

|-------------------|------------------|------------------------------------|--------------------|--|--|--|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, read as '0' |                    |  |  |  |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared               | x = Bit is unknown |  |  |  |

#### bit 31-16 Unimplemented: Read as '0'

- bit 15 ON: UARTx Enable bit

- 1 = UARTx is enabled. UARTx pins are controlled by UARTx as defined by UEN<1:0> and UTXEN control bits

- UARTx is disabled. All UARTx pins are controlled by corresponding bits in the PORTx, TRISx and LATx registers; UARTx power consumption is minimal

- bit 14 Unimplemented: Read as '0'

- bit 13 **SIDL:** Stop in Idle Mode bit

- 1 = Discontinue operation when device enters Idle mode

- 0 = Continue operation in Idle mode

- bit 12 IREN: IrDA Encoder and Decoder Enable bit

- 1 = IrDA is enabled

- 0 = IrDA is disabled

- bit 11 RTSMD: Mode Selection for UxRTS Pin bit

- $1 = \overline{\text{UxRTS}}$  pin is in Simplex mode

- $0 = \overline{\text{UxRTS}}$  pin is in Flow Control mode

- bit 10 Unimplemented: Read as '0'

#### bit 9-8 UEN<1:0>: UARTx Enable bits<sup>(1)</sup>

- 11 = UxTX, UxRX and UxBCLK pins are enabled and used; UxCTS pin is controlled by corresponding bits in the PORTx register

- 10 = UxTX, UxRX,  $\overline{\text{UxCTS}}$  and  $\overline{\text{UxRTS}}$  pins are enabled and used

- 01 = UxTX, UxRX and UxRTS pins are enabled and used; UxCTS pin is controlled by corresponding bits in the PORTx register

- 00 = UxTX and UxRX pins are enabled and used; UxCTS and UxRTS/UxBCLK pins are controlled by corresponding bits in the PORTx register

- bit 7 WAKE: Enable Wake-up on Start bit Detect During Sleep Mode bit

- 1 = Wake-up is enabled

- 0 = Wake-up is disabled

- bit 6 LPBACK: UARTx Loopback Mode Select bit

- 1 = Loopback mode is enabled

- 0 = Loopback mode is disabled

- Note 1: These bits are present for legacy compatibility, and are superseded by PPS functionality on these devices. For additional information, see Section 12.4 "Peripheral Pin Select (PPS)".

### 23.0 PARALLEL MASTER PORT (PMP)

| Note: | This data sheet summarizes the features<br>of the PIC32MZ EF family of devices. It is<br>not intended to be a comprehensive refer-<br>ence source. To complement the informa-<br>tion in this data sheet, refer to <b>Section 13</b> . |

|-------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|       | "Parallel Master Port (PMP)"                                                                                                                                                                                                           |

|       | (DS60001128) in the "PIC32 Family Ref-                                                                                                                                                                                                 |

|       | erence Manual", which is available from                                                                                                                                                                                                |

|       | the Microchip web site (www.micro-<br>chip.com/PIC32).                                                                                                                                                                                 |

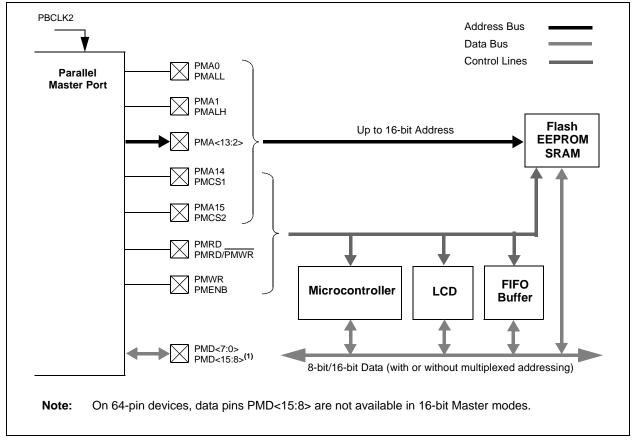

The PMP is a parallel 8-bit/16-bit input/output module specifically designed to communicate with a wide variety of parallel devices, such as communications peripherals, LCDs, external memory devices and microcontrollers. Because the interface to parallel peripherals varies significantly, the PMP module is highly configurable. The following are key features of the PMP module:

- 8-bit,16-bit interface

- Up to 16 programmable address lines

- Up to two Chip Select lines

- Programmable strobe options:

- Individual read and write strobes, or

- Read/write strobe with enable strobe

- Address auto-increment/auto-decrement

- Programmable address/data multiplexing

- Programmable polarity on control signals

- Parallel Slave Port support:

- Legacy addressable

- Address support

- 4-byte deep auto-incrementing buffer

- Programmable Wait states

- Operate during Sleep and Idle modes

- Separate configurable read/write registers or dual buffers for Master mode

- Fast bit manipulation using CLR, SET, and INV registers

Note: On 64-pin devices, data pins PMD<15:8> are not available in 16-bit Master modes.

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |  |  |  |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|--|--|--|

| 04-04        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |  |  |  |

| 31:24        |                   | —                 |                   | _                 |                   | —                 |                  |                  |  |  |  |

| 00.40        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |  |  |  |

| 23:16        |                   | —                 |                   | _                 |                   | —                 |                  |                  |  |  |  |

| 45.0         | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |  |  |

| 15:8         | DATAOUT<15:8>     |                   |                   |                   |                   |                   |                  |                  |  |  |  |

| 7:0          | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |  |  |

|              |                   | •                 | <7:0>             | •                 |                   | •                 |                  |                  |  |  |  |

#### REGISTER 23-4: PMDOUT: PARALLEL PORT OUTPUT DATA REGISTER

# Legend:R = Readable bitW = Writable bitU = Unimplemented bit, read as '0'-n = Value at POR'1' = Bit is set'0' = Bit is clearedx = Bit is unknown

#### bit 31-16 Unimplemented: Read as '0'

bit 15-0 DATAOUT<15:0>: Port Data Output bits

This register is used for Read operations in the Enhanced Parallel Slave mode and Write operations for Dual Buffer Master mode.

In Dual Buffer Master mode, the DUALBUF bit (PMPCON<17>) = 1, a write to the MSB triggers the transaction on the PMP port. When MODE16 = 1, MSB = DATAOUT<15:8>. When MODE16 = 0, MSB = DATAOUT<7:0>.

Note: In Master mode, a read will return the last value written to the register. In Slave mode, a read will return indeterminate results.

|              |                   |                   |                   |                   |                   | <b>_</b>          |                  |                  |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |

| 04.04        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 31:24        |                   | —                 | —                 |                   |                   | —                 | —                | —                |

| 00.40        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 23:16        |                   | —                 | —                 |                   |                   | —                 | —                | —                |

| 45.0         | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |

| 15:8         |                   |                   |                   | DATAIN<           | 15:8>             |                   |                  |                  |

| 7:0          | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |

|              |                   |                   |                   | DATAIN            | <7:0>             |                   |                  |                  |

#### REGISTER 23-5: PMDIN: PARALLEL PORT INPUT DATA REGISTER

| Legend:           |                  |                        |                    |

|-------------------|------------------|------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, | read as '0'        |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared   | x = Bit is unknown |

This register is not used in Dual Buffer Master mode (i.e., DUALBUF bit (PMPCON<17>) = 1).

#### bit 31-16 Unimplemented: Read as '0'

bit 15-0 DATAIN<15:0>: Port Data Input bits

This register is used for both Parallel Master Port mode and Enhanced Parallel Slave mode. In Parallel Master mode, a write to the MSB triggers the write transaction on the PMP port. Similarly, a read to the MSB triggers the read transaction on the PMP port. When MODE16 = 1, MSB = DATAIN<15:8>. When MODE16 = 0, MSB = DATAIN<7:0>.

Note:

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|

| 24.24        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 31:24        | —                 | _                 | _                 | —                 | _                 | _                 | _                | —                |

| 22.46        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 23:16        | —                 | _                 |                   |                   | _                 | _                 |                  | —                |

| 45.0         | R-0               | R/W-0, HS, SC     | U-0               | U-0               | R-0               | R-0               | R-0              | R-0              |

| 15:8         | IBF               | IBOV              | _                 | _                 | IB3F              | IB2F              | IB1F             | IB0F             |

| 7.0          | R-1               | R/W-0, HS, SC     | U-0               | U-0               | R-1               | R-1               | R-1              | R-1              |

| 7:0          | OBE               | OBUF              |                   |                   | OB3E              | OB2E              | OB1E             | OB0E             |

#### REGISTER 23-7: PMSTAT: PARALLEL PORT STATUS REGISTER (SLAVE MODES ONLY)

| Legend:           | HS = Hardware Set | SC = Software Cleared |                    |  |  |  |

|-------------------|-------------------|-----------------------|--------------------|--|--|--|

| R = Readable bit  | W = Writable bit  | U = Unimplemented bi  | t, read as '0'     |  |  |  |

| -n = Value at POR | '1' = Bit is set  | '0' = Bit is cleared  | x = Bit is unknown |  |  |  |

#### bit 31-16 Unimplemented: Read as '0'

- bit 15 **IBF:** Input Buffer Full Status bit

- 1 = All writable input buffer registers are full

- 0 = Some or all of the writable input buffer registers are empty

- bit 14 IBOV: Input Buffer Overflow Status bit

- 1 = A write attempt to a full input byte buffer is occurred (must be cleared in software)

- 0 = No overflow is occurred

#### bit 13-12 Unimplemented: Read as '0'

- bit 11-8 **IBxF:** Input Buffer x Status Full bits

- 1 = Input Buffer contains data that has not been read (reading buffer will clear this bit)

- 0 = Input Buffer does not contain any unread data

#### bit 7 **OBE:** Output Buffer Empty Status bit

- 1 = All readable output buffer registers are empty

- 0 = Some or all of the readable output buffer registers are full

#### bit 6 **OBUF:** Output Buffer Underflow Status bit

- 1 = A read occurred from an empty output byte buffer (must be cleared in software)

- 0 = No underflow is occurred

- bit 5-4 Unimplemented: Read as '0'

#### bit 3-0 **OBxE:** Output Buffer x Status Empty bits

- 1 = Output buffer is empty (writing data to the buffer will clear this bit)

- 0 = Output buffer contains data that has not been transmitted

NOTES:

#### 25.1 RTCC Control Registers

#### TABLE 25-1: RTCC REGISTER MAP

| ess                         |          |           |        |       |         |          |       |                   |          |        | Bits                  |          |        |       |         |         |         |       | 6          |

|-----------------------------|----------|-----------|--------|-------|---------|----------|-------|-------------------|----------|--------|-----------------------|----------|--------|-------|---------|---------|---------|-------|------------|

| Virtual Address<br>(BF80_#) | 3        | Bit Range | 31/15  | 30/14 | 29/13   | 28/12    | 27/11 | 26/10             | 25/9     | 24/8   | 23/7                  | 22/6     | 21/5   | 20/4  | 19/3    | 18/2    | 17/1    | 16/0  | All Resets |

| 0000                        | RTCCON   | 31:16     | _      | _     | _       | -        | -     | —                 |          |        |                       |          | CAL    | <9:0> |         |         |         |       | 0000       |

| 0000                        | RICCON   | 15:0      | ON     | -     | SIDL    | —        | —     | RTCCLK            | SEL<1:0> | RTCOUT | SEL<1:0>              | RTCCLKON | —      | —     | RTCWREN | RTCSYNC | HALFSEC | RTCOE | 0000       |

| 0010                        | RTCALRM  | 31:16     | —      | _     |         | —        | _     |                   |          |        | _                     |          | -      |       | —       | _       | _       |       | 0000       |

| 0010                        | RICALKI  | 15:0      | ALRMEN | CHIME | PIV     | ALRMSYNC |       | AMASI             | K<3:0>   |        |                       |          |        | ARP   | T<7:0>  |         |         |       | 0000       |

| 00.20                       | RTCTIME  | 31:16     |        | HR10  | 0<3:0>  |          |       | HR01              | <3:0>    |        | MIN10<3:0> MIN01<3:0> |          |        | <3:0> |         | xxxx    |         |       |            |

| 0020                        | RICTIVIL | 15:0      |        | SEC1  | 0<3:0>  |          |       | SEC0 <sup>2</sup> | 1<3:0>   |        |                       |          |        |       | —       | -       | _       |       | xx00       |

| 00.30                       | RTCDATE  | 31:16     |        | YEAR  | 10<3:0> |          |       | YEAR0             | 1<3:0>   |        |                       | MONTH    | 0<3:0> |       |         | MONTH   | 01<3:0> |       | xxxx       |

| 0030                        | RICDAIL  | 15:0      |        | DAY1  | 0<3:0>  |          |       | DAY0'             | 1<3:0>   |        |                       |          |        |       |         | WDAY0   | 1<3:0>  |       | xx00       |

| 0040                        | ALRMTIME | 31:16     |        | HR10  | 0<3:0>  |          |       | HR01              | <3:0>    |        |                       | MIN10    | <3:0>  |       |         | MIN01   | <3:0>   |       | xxxx       |

| 0040                        |          | 15:0      |        | SEC1  | 0<3:0>  |          |       | SEC0 <sup>2</sup> | 1<3:0>   |        |                       |          |        |       | —       | -       | _       |       | xx00       |

| 0050                        | ALRMDATE | 31:16     | _      | _     |         | —        |       |                   |          |        |                       | MONTH    | 0<3:0> |       |         | MONTH   | 01<3:0> |       | 00xx       |

| 0050                        |          | 15:0      |        | DAY1  | 0<3:0>  |          |       | DAY0'             | 1<3:0>   |        | _                     | _        | _      |       |         | WDAY0   | 1<3:0>  |       | xx0x       |

Legend: x = unknown value on Reset; - = unimplemented, read as '0'. Reset values are shown in hexadecimal.

Note 1: All registers in this table have corresponding CLR, SET and INV registers at its virtual address, plus an offset of 0x4, 0x8 and 0xC, respectively. See Section 12.3 "CLR, SET, and INV Registers" for more information.

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|

| 31:24        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | R/W-0            | R/W-0            |

| 31.24        | _                 | —                 | —                 | —                 | —                 |                   | SH4AL            | .T<1:0>          |

| 00.40        | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |

| 23:16        | SH3A              | LT<1:0>           | SH2AL             | .T<1:0>           | SH1AL             | T<1:0>            | SH0AL            | .T<1:0>          |

| 45.0         | U-0               | U-0               | U-0               | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |

| 15:8         | —                 | —                 |                   | STRGEN4           | STRGEN3           | STRGEN2           | STRGEN1          | STRGEN0          |

| 7.0          | U-0               | U-0               | U-0               | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |

| 7:0          |                   |                   | _                 | SSAMPEN4          | SSAMPEN3          | SSAMPEN2          | SSAMPEN1         | SSAMPEN0         |

#### REGISTER 28-4: ADCTRGMODE: ADC TRIGGERING MODE FOR DEDICATED ADC REGISTER

#### Legend:

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, | U = Unimplemented bit, read as '0' |  |  |  |  |

|-------------------|------------------|------------------------|------------------------------------|--|--|--|--|

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared   | x = Bit is unknown                 |  |  |  |  |

#### bit 31-26 Unimplemented: Read as '0'

bit 25-24 SH4ALT<1:0>: ADC4 Analog Input Select bit

- 11 = Reserved

- 10 = Reserved

- 01 = AN49

- 00 **=** AN4

#### bit 23-22 SH3ALT<1:0>: ADC3 Analog Input Select bit

- 11 = Reserved

- 10 = Reserved

- 01 = AN48

- 00 **= AN3**

bit 21-20 SH2ALT<1:0>: ADC2 Analog Input Select bit

- 11 = Reserved

- 10 = Reserved

- 01 = AN47

- 00 = AN2

#### bit 19-18 SH1ALT<1:0>: ADC1 Analog Input Select bit

- 11 = Reserved

- 10 = Reserved

- 01 = AN46

- 00 = AN1

- bit 17-16 SH0ALT<1:0>: ADC0 Analog Input Select bit

- 11 = Reserved

- 10 = Reserved

- 01 = AN45

- 00 = AN0

- bit 15-13 Unimplemented: Read as '0'

bit 12 **STRGEN4:** ADC4 Presynchronized Triggers bit 1 = ADC4 uses presynchronized triggers 0 = ADC4 does not use presynchronized triggers

- bit 11 STRGEN3: ADC3 Presynchronized Triggers bit 1 = ADC3 uses presynchronized triggers

- 0 = ADC3 does not use presynchronized triggers

- bit 10 **STRGEN2:** ADC2 Presynchronized Triggers bit 1 = ADC2 uses presynchronized triggers 0 = ADC2 does not use presynchronized triggers

- © 2015-2016 Microchip Technology Inc.

| Bit Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |

|-----------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|

| 31:24     | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 51.24     | _                 |                   |                   |                   |                   |                   |                  | _                |

| 22.40     | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 23:16     | -                 | _                 | _                 | _                 | _                 | _                 | _                | _                |

| 45.0      | U-0               | U-0               | U-0               | U-0               | R/W-0             | R/W-0             | R/W-0            | R/W-0            |

| 15:8      | _                 | _                 | —                 | _                 | LVL11             | LVL10             | LVL9             | LVL8             |

| 7.0       | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |

| 7:0       | LVL7              | LVL6              | LVL5              | LVL4              | LVL3              | LVL2              | LVL1             | LVL0             |

#### REGISTER 28-26: ADCTRGSNS: ADC TRIGGER LEVEL/EDGE SENSITIVITY REGISTER

#### Legend:

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, | read as '0'        |

|-------------------|------------------|------------------------|--------------------|

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared   | x = Bit is unknown |

#### bit 31-12 Unimplemented: Read as '0'

- bit 11 LVL11:LVL0: Trigger Level and Edge Sensitivity bits

- 1 = Analog input is sensitive to the high level of its trigger (level sensitivity implies retriggering as long as the trigger signal remains high)

- 0 = Analog input is sensitive to the positive edge of its trigger (this is the value after a reset)

#### Note 1: This register specifies the trigger level for analog inputs 0 to 31.

2: The higher analog input ID belongs to Class 3, and therefore, is only scan triggered. All Class 3 analog inputs use the Scan Trigger, for which the level/edge is defined by the STRGLVL bit (ADCCON1<3>).

| <ul> <li>bit 15 FLTEN25: Filter 25 Enable bit <ol> <li>= Filter is enabled</li> <li>= Filter is disabled</li> </ol> </li> <li>bit 14-13 MSEL25</li> <li>MSEL25</li> <li>= Acceptance Mask 3 selected</li> <li>= Acceptance Mask 3 selected</li> <li>= Acceptance Mask 1 selected</li> <li>= Acceptance Mask 0 selected</li> <li>= Acceptance Mask 0 selected</li> <li>= Acceptance Mask 0 selected</li> <li>bit 12-8 FSEL25</li> <li>FSEL25</li> <li># FIFO Selection bits</li> <li>1111 = Message matching filter is stored in FIFO buffer 31</li> <li>1110 = Message matching filter is stored in FIFO buffer 30</li> <li>.</li> <li>.</li> <li>00001 = Message matching filter is stored in FIFO buffer 1</li> <li>00000 = Message matching filter is stored in FIFO buffer 0</li> </ul> bit 7 FLTEN24: Filter 24 Enable bit <ul> <li>1 = Filter is enabled</li> <li>0 = Filter is disabled</li> </ul> bit 6-5 MSEL24<1:>: Filter 24 Mask Select bits <ul> <li>11 = Acceptance Mask 3 selected</li> <li>0 = Acceptance Mask 3 selected</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |         |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------|

| <ul> <li>a Filter is disabled</li> <li>bit 14-13 MSEL25&lt;1:0&gt;: Filter 25 Mask Select bits         <ol> <li>11 = Acceptance Mask 3 selected</li> <li>10 = Acceptance Mask 2 selected</li> <li>01 = Acceptance Mask 0 selected</li> <li>00 = Acceptance Mask 0 selected</li> </ol> </li> <li>bit 12-8 FSEL25&lt;4:0&gt;: FIFO Selection bits         <ol> <li>11111 = Message matching filter is stored in FIFO buffer 31</li> <li>11110 = Message matching filter is stored in FIFO buffer 30</li></ol></li></ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |         |