Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| 2 0 0 0 0 0                |                                                                                   |

|----------------------------|-----------------------------------------------------------------------------------|

| Product Status             | Active                                                                            |

| Core Processor             | MIPS32® M-Class                                                                   |

| Core Size                  | 32-Bit Single-Core                                                                |

| Speed                      | 200MHz                                                                            |

| Connectivity               | Ethernet, I <sup>2</sup> C, PMP, SPI, SQI, UART/USART, USB OTG                    |

| Peripherals                | Brown-out Detect/Reset, DMA, I <sup>2</sup> S, POR, PWM, WDT                      |

| Number of I/O              | 46                                                                                |

| Program Memory Size        | 1MB (1M x 8)                                                                      |

| Program Memory Type        | FLASH                                                                             |

| EEPROM Size                | -                                                                                 |

| RAM Size                   | 256K x 8                                                                          |

| Voltage - Supply (Vcc/Vdd) | 2.1V ~ 3.6V                                                                       |

| Data Converters            | A/D 24x12b                                                                        |

| Oscillator Type            | Internal                                                                          |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                                 |

| Mounting Type              | Surface Mount                                                                     |

| Package / Case             | 64-TQFP                                                                           |

| Supplier Device Package    | 64-TQFP (10x10)                                                                   |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic32mz1024efe064t-i-pt |

|                            |                                                                                   |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

|          |                        | Pin Nu          | mber            |                          | Pin<br>Type | Buffer<br>Type |                                   |  |

|----------|------------------------|-----------------|-----------------|--------------------------|-------------|----------------|-----------------------------------|--|

| Pin Name | 64-pin<br>QFN/<br>TQFP | 100-pin<br>TQFP | 124-pin<br>VTLA | 144-pin<br>TQFP/<br>LQFP |             |                | Description                       |  |

|          |                        |                 |                 |                          | PO          | RTK            |                                   |  |

| RK0      | —                      | _               | _               | 19                       | I/O         | ST             | PORTK is a bidirectional I/O port |  |

| RK1      | —                      | —               |                 | 51                       | I/O         | ST             |                                   |  |

| RK2      | —                      | _               |                 | 52                       | I/O         | ST             |                                   |  |

| RK3      | —                      | _               |                 | 53                       | I/O         | ST             |                                   |  |

| RK4      | —                      | —               |                 | 92                       | I/O         | ST             |                                   |  |

| RK5      | —                      | —               |                 | 93                       | I/O         | ST             |                                   |  |

| RK6      | —                      | —               |                 | 94                       | I/O         | ST             | ]                                 |  |

| RK7      | —                      | —               | —               | 126                      | I/O         | ST             | ]                                 |  |

| Legend:  | CMOS = C               | MOS-comp        | atible input    | t or output              |             | Analog =       | Analog input P = Power            |  |

## TABLE 1-6: PORTA THROUGH PORTK PINOUT I/O DESCRIPTIONS (CONTINUED)

d: CMOS = CMOS-compatible input or output ST = Schmitt Trigger input with CMOS levels TTL = Transistor-transistor Logic input buffer Analog = Analog input O = Output PPS = Peripheral Pin Select P = Power I = Input

i – mput

|          |                        | Pin Number      |                 |                          |             |                |                                      |  |

|----------|------------------------|-----------------|-----------------|--------------------------|-------------|----------------|--------------------------------------|--|

| Pin Name | 64-pin<br>QFN/<br>TQFP | 100-pin<br>TQFP | 124-pin<br>VTLA | 144-pin<br>TQFP/<br>LQFP | Pin<br>Type | Buffer<br>Type | Description                          |  |

|          |                        |                 |                 | Т                        | imer1 thr   | ough Timer     | 9                                    |  |

| T1CK     | 48                     | 73              | A49             | 106                      | Ι           | ST             | Timer1 External Clock Input          |  |

| T2CK     | PPS                    | PPS             | PPS             | PPS                      | I           | ST             | Timer2 External Clock Input          |  |

| T3CK     | PPS                    | PPS             | PPS             | PPS                      | I           | ST             | Timer3 External Clock Input          |  |

| T4CK     | PPS                    | PPS             | PPS             | PPS                      | I           | ST             | Timer4 External Clock Input          |  |

| T5CK     | PPS                    | PPS             | PPS             | PPS                      | I           | ST             | Timer5 External Clock Input          |  |

| T6CK     | PPS                    | PPS             | PPS             | PPS                      | I           | ST             | Timer6 External Clock Input          |  |

| T7CK     | PPS                    | PPS             | PPS             | PPS                      | I           | ST             | Timer7 External Clock Input          |  |

| T8CK     | PPS                    | PPS             | PPS             | PPS                      | I           | ST             | Timer8 External Clock Input          |  |

| T9CK     | PPS                    | PPS             | PPS             | PPS                      | I           | ST             | Timer9 External Clock Input          |  |

|          | •                      | •               | •               | Real-                    | Time Clo    | ck and Cale    | endar                                |  |

| RTCC     | 46                     | 71              | A48             | 104                      | 0           | —              | Real-Time Clock Alarm/Seconds Output |  |

| Legend:  | CMOS = C               | MOS-compa       | atible input    | or output                |             | Analog =       | Analog input P = Power               |  |

#### **TABLE 1-7:** TIMER1 THROUGH TIMER9 AND RTCC PINOUT I/O DESCRIPTIONS

ST = Schmitt Trigger input with CMOS levels

TTL = Transistor-transistor Logic input buffer

O = Output PPS = Peripheral Pin Select

I = Input

## 3.0 CPU

- Note 1: This data sheet summarizes the features of the PIC32MZ EF family of devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to Section 50. "CPU for Devices with MIPS32<sup>®</sup> microAptiv<sup>™</sup> and M-Class Cores" (DS60001192) of the "PIC32 Family Reference Manual", which is available from the Microchip web site (www.microchip.com/PIC32).

- 2: The Series 5 Warrior M-class CPU core resources are available at: www.imgtec.com.

The MIPS32<sup>®</sup> M-Class Core is the heart of the PIC32MZ EF family device processor. The CPU fetches instructions, decodes each instruction, fetches source operands, executes each instruction and writes the results of instruction execution to the proper destinations.

Key features include:

- 5-stage pipeline

- · 32-bit address and data paths

- MIPS32 Enhanced Architecture (Release 5):

- Multiply-accumulate and multiply-subtract instructions

- Targeted multiply instruction

- Zero/One detect instructions

- WAIT instruction

- Conditional move instructions (MOVN, MOVZ)

- Vectored interrupts

- Programmable exception vector base

- Atomic interrupt enable/disable

- GPR shadow registers to minimize latency for interrupt handlers

- Bit field manipulation instructions

- Virtual memory support

- microMIPS<sup>™</sup> compatible instruction set:

- Improves code size density over MIPS32, while maintaining MIPS32 performance.

- Supports all MIPS32 instructions (except branchlikely instructions)

- Fifteen additional 32-bit instructions and 39 16-bit instructions corresponding to commonly-used MIPS32 instructions

- Stack pointer implicit in instruction

- MIPS32 assembly and ABI compatible

- MMU with Translation Lookaside Buffer (TLB) mechanism:

- 16 dual-entry fully associative Joint TLB

- 4-entry fully associative Instruction and Data TLB

- 4 KB pages

- Separate L1 data and instruction caches:

- 16 KB 4-way Instruction Cache (I-Cache)

- 4 KB 4-way Data Cache (D-Cache)

- Autonomous Multiply/Divide Unit (MDU):

- Maximum issue rate of one 32x32 multiply per clock

- Early-in iterative divide. Minimum 12 and maximum 38 clock latency (dividend (*rs*) sign extension-dependent)

- Power Control:

- Minimum frequency: 0 MHz

- Low-Power mode (triggered by WAIT instruction)

- Extensive use of local gated clocks

- EJTAG Debug and Instruction Trace:

- Support for single stepping

- Virtual instruction and data address/value breakpoints

- Hardware breakpoint supports both address match and address range triggering.

- Eight instruction and four data complex breakpoints

- iFlowtrace<sup>®</sup> version 2.0 support:

- Real-time instruction program counter

- Special events trace capability

- Two performance counters with 34 userselectable countable events

- Disabled if the processor enters Debug mode

- Program Counter sampling

- Four Watch registers:

- Instruction, Data Read, Data Write options

- Address match masking options

- DSP ASE Extension:

- Native fractional format data type operations

- Register Single Instruction Multiple Data (SIMD) operations (add, subtract, multiply, shift)

- GPR-based shift

- Bit manipulation

- Compare-Pick

- DSP Control Access

- Indexed-Load

- Branch

- Multiplication of complex operands

- Variable bit insertion and extraction

- Virtual circular buffers

- Arithmetic saturation and overflow handling

- Zero-cycle overhead saturation and rounding operations

- Floating Point Unit (FPU):

- 1985 IEEE-754 compliant Floating Point Unit

- Supports single and double precision datatypes

- 2008 IEEE-754 compatibility control of NaN handling and Abs/Neg instructions

- Runs at 1:1 core/FPU clock ratio

The FPU implements a high-performance 7-stage pipeline:

- Decode, register read and unpack (FR stage)

- Multiply tree, double pumped for double (M1 stage)

- Multiply complete (M2 stage)

- Addition first step (A1 stage)

- Addition second and final step (A2 stage)

- Packing to IEEE format (FP stage)

- Register writeback (FW stage)

The FPU implements a bypass mechanism that allows the result of an operation to be forwarded directly to the instruction that needs it without having to write the result to the FPU register and then read it back.

Table 3-5 lists the Coprocessor 1 Registers for the FPU.

| Register<br>Number | Register<br>Name | Function                                                                                    |

|--------------------|------------------|---------------------------------------------------------------------------------------------|

| 0                  | FIR              | Floating Point implementation<br>register. Contains information<br>that identifies the FPU. |

| 25                 | FCCR             | Floating Point condition codes register.                                                    |

| 26                 | FEXR             | Floating Point exceptions register.                                                         |

| 28                 | FENR             | Floating Point enables register.                                                            |

| 31                 | FCSR             | Floating Point Control and Status register.                                                 |

TABLE 3-5: FPU (CP1) REGISTERS

## 3.2 Power Management

The processor core offers a number of power management features, including low-power design, active power management and power-down modes of operation. The core is a static design that supports slowing or halting the clocks, which reduces system power consumption during Idle periods.

#### 3.2.1 INSTRUCTION-CONTROLLED POWER MANAGEMENT

The mechanism for invoking Power-Down mode is through execution of the WAIT instruction. For more information on power management, see Section 33.0 "Power-Saving Features".

## 3.2.2 LOCAL CLOCK GATING

The majority of the power consumed by the processor core is in the clock tree and clocking registers. The PIC32MZ family makes extensive use of local gatedclocks to reduce this dynamic power consumption.

## 3.3 L1 Instruction and Data Caches

## 3.3.1 INSTRUCTION CACHE (I-CACHE)

The I-Cache is an on-core memory block of 16 Kbytes. Because the I-Cache is virtually indexed, the virtual-tophysical address translation occurs in parallel with the cache access rather than having to wait for the physical address translation. The tag holds 22 bits of physical address, a valid bit, and a lock bit. The LRU replacement bits are stored in a separate array.

The I-Cache block also contains and manages the instruction line fill buffer. Besides accumulating data to be written to the cache, instruction fetches that reference data in the line fill buffer are serviced either by a bypass of that data, or data coming from the external interface. The I-Cache control logic controls the bypass function.

The processor core supports I-Cache locking. Cache locking allows critical code or data segments to be locked into the cache on a per-line basis, enabling the system programmer to maximize the efficiency of the system cache.

The cache locking function is always available on all I-Cache entries. Entries can then be marked as locked or unlocked on a per entry basis using the CACHE instruction.

## 3.3.2 DATA CACHE (D-CACHE)

The D-Cache is an on-core memory block of 4 Kbytes. This virtually indexed, physically tagged cache is protected. Because the D-Cache is virtually indexed, the virtual-to-physical address translation occurs in parallel with the cache access. The tag holds 22 bits of physical address, a valid bit, and a lock bit. There is an additional array holding dirty bits and LRU replacement algorithm bits for each set of the cache.

In addition to I-Cache locking, the processor core also supports a D-Cache locking mechanism identical to the I-Cache. Critical data segments are locked into the cache on a per-line basis. The locked contents can be updated on a store hit, but cannot be selected for replacement on a cache miss.

The D-Cache locking function is always available on all D-Cache entries. Entries can then be marked as locked or unlocked on a per-entry basis using the CACHE instruction.

#### 3.3.3 ATTRIBUTES

The processor core I-Cache and D-Cache attributes are listed in the Configuration registers (see Register 3-1 through Register 3-4).

## 3.4 EJTAG Debug Support

The processor core provides for an Enhanced JTAG (EJTAG) interface for use in the software debug of application and kernel code. In addition to standard User mode and Kernel modes of operation, the processor core provides a Debug mode that is entered after a debug exception (derived from a hardware breakpoint, single-step exception, etc.) is taken and continues until a Debug Exception Return (DERET) instruction is executed. During this time, the processor executes the debug exception handler routine.

The EJTAG interface operates through the Test Access Port (TAP), a serial communication port used for transferring test data in and out of the core. In addition to the standard JTAG instructions, special instructions defined in the EJTAG specification specify which registers are selected and how they are used.

## 3.5 MIPS DSP ASE Extension

The MIPS DSP Application-Specific Extension Revision 2 is an extension to the MIPS32 architecture. This extension comprises new integer instructions and states that include new HI/LO accumulator register pairs and a DSP control register. This extension is crucial in a wide range of DSP, multimedia, and DSPlike algorithms covering Audio and Video processing applications. The extension supports native fractional format data type operations, register Single Instruction Multiple Data (SIMD) operations, such as add, subtract, multiply, and shift. In addition, the extension includes the following features that are essential in making DSP algorithms computationally efficient:

- · Support for multiplication of complex operands

- · Variable bit insertion and extraction

- Implementation and use of virtual circular buffers

- Arithmetic saturation and overflow handling support

- Zero cycle overhead saturation and rounding operations

#### 3.6 microMIPS ISA

The processor core supports the microMIPS ISA, which contains all MIPS32 ISA instructions (except for branch-likely instructions) in a new 32-bit encoding scheme, with some of the commonly used instructions also available in 16-bit encoded format. This ISA improves code density through the additional 16-bit instructions while maintaining a performance similar to MIPS32 mode. In microMIPS mode, 16-bit or 32-bit instructions will be fetched and recoded to legacy MIPS32 instruction opcodes in the pipeline's I stage, so that the processor core can have the same microAptiv UP microarchitecture. Because the microMIPS instruction stream can be intermixed with 16-bit halfword or 32-bit word size instructions on halfword or word boundaries, additional logic is in place to address the misalignment word issues, thus minimizing performance loss.

|              |                   | ('x' = 0-13)      |                   |                   |                   |                   |                  |                  |  |  |  |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|--|--|--|

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |  |  |  |

| 04.04        | R/W-0, C          | U-0               | U-0               | U-0               | R/W-0, C          | R/W-0, C          | R/W-0, C         | R/W-0, C         |  |  |  |

| 31:24        | MULTI             | —                 | —                 | —                 |                   | CODE              | <3:0>            |                  |  |  |  |

| 00.40        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |  |  |  |

| 23:16        |                   |                   | —                 | —                 |                   | —                 |                  | _                |  |  |  |

| 45.0         | R-0               | R-0               | R-0               | R-0               | R-0               | R-0               | R-0              | R-0              |  |  |  |

| 15:8         |                   | INITID<7:0>       |                   |                   |                   |                   |                  |                  |  |  |  |

| 7.0          | R-0               | R-0               | R-0               | R-0               | U-0               | R-0               | R-0              | R-0              |  |  |  |

| 7:0          |                   | REGIO             | N<3:0>            |                   |                   |                   | CMD<2:0>         |                  |  |  |  |

## REGISTER 4-3: SBTxELOG1: SYSTEM BUS TARGET 'x' ERROR LOG REGISTER 1

| Legend:           | C = Clearable bit |                                    |

|-------------------|-------------------|------------------------------------|

| R = Readable bit  | W = Writable bit  | U = Unimplemented bit, read as '0' |

| -n = Value at POR | '1' = Bit is set  | '0' = Bit is cleared               |

bit 31 MULTI: Multiple Permission Violations Status bit

This bit is cleared by writing a '1'.

1 = Multiple errors have been detected

0 = No multiple errors have been detected

bit 30-28 Unimplemented: Read as '0'

bit 27-24 CODE<3:0>: Error Code bits

Indicates the type of error that was detected. These bits are cleared by writing a '1'.

- 1111 = Reserved

- 1101 = Reserved

- •

- •

- 0011 = Permission violation

- 0010 = Reserved

- 0001 = Reserved

- 0000 = No error

- bit 23-16 Unimplemented: Read as '0'

- bit 15-8 INITID<7:0>: Initiator ID of Requester bits

- 11111111 = Reserved

- 00001111 = Reserved 00001110 = Crypto Engine 00001101 = Flash Controller 00001100 = SQI1 00001011 = CAN2 00001010 = CAN1 00001001 = Ethernet Write 00001000 = Ethernet Read 00000111 = USB 00000110 = DMA Write (DMAPRI (CFGCON<25>) = 1) 00000101 = DMA Write (DMAPRI (CFGCON<25>) = 0) 00000100 = DMA Read (DMAPRI (CFGCON<25>) = 1) 00000011 = DMA Read (DMAPRI (CFGCON<25>) = 0) 00000010 = CPU (CPUPRI (CFGCON<24>) = 1) 00000001 = CPU (CPUPRI (CFGCON<25>) = 0) 00000000 = Reserved

#### Note: Refer to Table 4-6 for the list of available targets and their descriptions.

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0   |  |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|--------------------|--|

| 04.04        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0                |  |

| 31:24        | —                 | —                 | _                 | _                 | _                 | _                 | —                | _                  |  |

| 00.40        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0                |  |

| 23:16        | —                 | _                 | _                 | _                 | _                 | _                 | _                | _                  |  |

| 45.0         | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0                |  |

| 15:8         | —                 | _                 | _                 | _                 | -                 | _                 | _                |                    |  |

| 7.0          | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | R-0              | R-0                |  |

| 7:0          |                   |                   |                   | _                 |                   |                   | GROU             | <sup>D</sup> <1:0> |  |

#### **REGISTER 4-4:** SBTxELOG2: SYSTEM BUS TARGET 'x' ERROR LOG REGISTER 2 ('x' = 0-13)

#### Legend:

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, read as '0' |

|-------------------|------------------|------------------------------------|

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared               |

#### bit 31-3 Unimplemented: Read as '0'

- bit 1-0 GROUP<1:0>: Requested Permissions Group bits

- 11 = Group 3

- 10 = Group 2

- 01 = Group 1

- 00 = Group 0

Note: Refer to Table 4-6 for the list of available targets and their descriptions.

#### REGISTER 4-5: SBTxECON: SYSTEM BUS TARGET 'x' ERROR CONTROL REGISTER ('x' = 0-13)

|              |                   | x = 0 = 13        |                   |                   |                   |                   |                  |                  |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |

| 04.04        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | R/W-0            |

| 31:24        | —                 | —                 | _                 | _                 | -                 |                   | _                | ERRP             |

|              | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 23:16        | —                 | _                 | _                 | _                 | _                 | _                 | _                | —                |

| 45.0         | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 15:8         | —                 | _                 | _                 | _                 | -                 |                   | _                | —                |

| 7.0          | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 7:0          | —                 |                   |                   |                   |                   |                   |                  | —                |

| Legend:           |                  |                                    |

|-------------------|------------------|------------------------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, read as '0' |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared               |

bit 31-25 Unimplemented: Read as '0'

bit 24 ERRP: Error Control bit

1 = Report protection group violation errors

0 = Do not report protection group violation errors

bit 23-0 Unimplemented: Read as '0'

Note: Refer to Table 4-6 for the list of available targets and their descriptions.

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |  |  |  |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|--|--|--|

| 31:24        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |  |  |  |

| 31.24        | —                 | —                 | _                 |                   | -                 |                   | —                | —                |  |  |  |

| 22.10        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |  |  |  |

| 23:16        | —                 | —                 | _                 | _                 | _                 | _                 | —                | —                |  |  |  |

| 45.0         | R-0               | R-0               | R-0               | R-0               | R-0               | R-0               | R-0              | R-0              |  |  |  |

| 15:8         | CHSPTR<15:8>      |                   |                   |                   |                   |                   |                  |                  |  |  |  |

| 7.0          | R-0               | R-0               | R-0               | R-0               | R-0               | R-0               | R-0              | R-0              |  |  |  |

| 7:0          | CHSPTR<7:0>       |                   |                   |                   |                   |                   |                  |                  |  |  |  |

#### REGISTER 10-14: DCHxSPTR: DMA CHANNEL x SOURCE POINTER REGISTER

## Legend:

| Logona.           |                  |                                    |                    |  |

|-------------------|------------------|------------------------------------|--------------------|--|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, read as '0' |                    |  |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared               | x = Bit is unknown |  |

bit 31-16 Unimplemented: Read as '0'

bit 15-0 CHSPTR<15:0>: Channel Source Pointer bits

111111111111111 = Points to byte 65,535 of the source

Note: When in Pattern Detect mode, this register is reset on a pattern detect.

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |  |  |  |  |  |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|--|--|--|--|--|

| 24.24        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |  |  |  |  |  |

| 31:24        |                   |                   | _                 |                   | —                 |                   |                  | —                |  |  |  |  |  |

| 00.40        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |  |  |  |  |  |

| 23:16        | _                 | —                 | —                 | —                 | —                 | —                 | _                | —                |  |  |  |  |  |

| 45.0         | R-0               | R-0               | R-0               | R-0               | R-0               | R-0               | R-0              | R-0              |  |  |  |  |  |

| 15:8         | CHDPTR<15:8>      |                   |                   |                   |                   |                   |                  |                  |  |  |  |  |  |

| 7.0          | R-0               | R-0               | R-0               | R-0               | R-0               | R-0               | R-0              | R-0              |  |  |  |  |  |

| 7:0          | CHDPTR<7:0>       |                   |                   |                   |                   |                   |                  |                  |  |  |  |  |  |

#### **REGISTER 10-15: DCHxDPTR: DMA CHANNEL x DESTINATION POINTER REGISTER**

| Legend:           |                  |                        |                    |

|-------------------|------------------|------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, | read as '0'        |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared   | x = Bit is unknown |

bit 31-16 Unimplemented: Read as '0'

bit 15-0 CHDPTR<15:0>: Channel Destination Pointer bits

111111111111111 = Points to byte 65,535 of the destination

### REGISTER 11-29: USBLPMR2: USB LINK POWER MANAGEMENT CONTROL REGISTER 2

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|

| 31:24        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 31.24        | —                 | _                 |                   |                   |                   |                   | —                | _                |

| 23:16        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 23.10        | —                 | _                 |                   | _                 |                   | _                 | —                | _                |

| 45.0         | U-0 R/W-0         |                   | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |

| 15:8         | —                 |                   |                   | LF                | PMFADDR<6:        | 0>                |                  |                  |

| 7:0          | U-0 U-0           |                   | R-0               | R-0, HS           | R-0, HS           | R-0, HS           | R-0, HS          | R-0, HS          |

| 7.0          | _                 |                   | LPMERRIF          | LPMRESIF          | LPMNCIF           | LPMACKIF          | LPMNYIF          | LPMSTIF          |

| Legend:           | HS = Hardware Set |                           |                    |

|-------------------|-------------------|---------------------------|--------------------|

| R = Readable bit  | W = Writable bit  | U = Unimplemented bit, re | ead as '0'         |

| -n = Value at POR | '1' = Bit is set  | '0' = Bit is cleared      | x = Bit is unknown |

bit 31-15 Unimplemented: Read as '0'

bit 14-8 LPMFADDR<6:0>: LPM Payload Function Address bits These bits contain the address of the LPM payload function.

bit 7-6 Unimplemented: Read as '0'

#### bit 5 LPMERRIF: LPM Error Interrupt Flag bit (Device mode)

1 = An LPM transaction was received that had a LINKSTATE field that is not supported. The response will be a STALL.

0 =No error condition

#### bit 4 LPMRESIF: LPM Resume Interrupt Flag bit

- 1 = The USB module has resumed (for any reason)

- 0 = No Resume condition

- bit 3 LPMNCIF: LPM NC Interrupt Flag bit

#### When in Device mode:

- 1 = The USB module received a LPM transaction and responded with a NYET due to data pending in the RX FIFOs.

- 0 = No NC interrupt condition

When in Host mode:

- 1 = A LPM transaction is transmitted and the device responded with an ACK

- 0 = No NC interrupt condition

#### bit 2 LPMACKIF: LPM ACK Interrupt Flag bit

When in Device mode:

- 1 = A LPM transaction was received and the USB Module responded with an ACK

- 0 = No ACK interrupt condition

#### When in Host mode:

1 = The LPM transaction is transmitted and the device responds with an ACK

0 = No ACK interrupt condition

#### bit 1 LPMNYIF: LPM NYET Interrupt Flag bit

#### When in Device mode:

1 = A LPM transaction is received and the USB Module responded with a NYET

0 = No NYET interrupt flag

When in Host mode:

- 1 = A LPM transaction is transmitted and the device responded with an NYET

- 0 = No NYET interrupt flag

## TABLE 12-6: PORTC REGISTER MAP FOR 100-PIN, 124-PIN, AND 144-PIN DEVICES ONLY

| ess                         |                                 |           |           |           |           |           |                |       |      | Bits |      |      |      |          |          |          |          |      |               |

|-----------------------------|---------------------------------|-----------|-----------|-----------|-----------|-----------|----------------|-------|------|------|------|------|------|----------|----------|----------|----------|------|---------------|

| Virtual Address<br>(BF86_#) | Register<br>Name <sup>(1)</sup> | Bit Range | 31/15     | 30/14     | 29/13     | 28/12     | 27/11          | 26/10 | 25/9 | 24/8 | 23/7 | 22/6 | 21/5 | 20/4     | 19/3     | 18/2     | 17/1     | 16/0 | All<br>Resets |

| 0200                        | ANSELC                          | 31:16     | —         | —         | —         | _         | —              | _     | _    | _    | _    | _    | —    | _        | —        | —        | —        | _    | 0000          |

| 0200                        | ANGLEO                          | 15:0      | _         | _         |           | _         | —              |       |      | _    | —    | —    |      | ANSC4    | ANSC3    | ANSC2    | ANSC1    |      | 001E          |

| 0210                        | TRISC                           | 31:16     | _         |           |           |           | —              |       | _    | _    | —    | —    |      | —        | _        |          | _        | _    | 0000          |

| 0210                        | TRIBO                           | 15:0      | TRISC15   | TRISC14   | TRISC13   | TRISC12   | —              |       |      | _    | —    | —    |      | TRISC4   | TRISC3   | TRISC2   | TRISC1   |      | F01E          |

| 0220                        | PORTC                           | 31:16     | —         | _         | —         |           | _              |       | _    | _    | —    | —    |      | _        | _        |          | —        | _    | 0000          |

| 0220                        | TOKIC                           | 15:0      | RC15      | RC14      | RC13      | RC12      | —              | _     | _    | _    | —    | —    | —    | RC4      | RC3      | RC2      | RC1      | -    | xxxx          |

| 0230                        | LATC                            | 31:16     | _         | _         | _         | -         | —              | _     | _    | _    | —    | —    | —    | —        | —        | —        | —        | -    | 0000          |

| 0230                        | LAIO                            | 15:0      | LATC15    | LATC14    | LATC13    | LATC12    | —              | _     | _    | _    | —    | —    | —    | LATC4    | LATC3    | LATC2    | LATC1    | -    | xxxx          |

| 0240                        | ODCC                            | 31:16     | _         | _         | _         | -         | —              | _     | _    | _    | —    | —    | —    | —        | —        | —        | —        | -    | 0000          |

| 0240                        |                                 | 15:0      | ODCC15    | ODCC14    | ODCC13    | ODCC12    | —              | _     | _    | _    | —    | —    | —    | ODCC4    | ODCC3    | ODCC2    | ODCC1    | -    | 0000          |

| 0250                        | CNPUC                           | 31:16     | _         | _         | _         | -         | —              | _     | _    | _    | —    | —    | —    | —        | —        | —        | —        | -    | 0000          |

| 0230                        | CINFUC                          | 15:0      | CNPUC15   | CNPUC14   | CNPUC13   | CNPUC12   | -              |       |      |      |      | _    | _    | CNPUC4   | CNPUC3   | CNPUC2   | CNPUC1   |      | 0000          |

| 0260                        | CNPDC                           | 31:16     | _         | _         | _         | -         | —              | _     | _    | _    | —    | —    | —    | —        | —        | —        | —        | -    | 0000          |

| 0200                        |                                 | 15:0      | CNPDC15   | CNPDC14   | CNPDC13   | CNPDC12   | —              | _     | _    | _    | —    | —    | —    | CNPDC4   | CNPDC3   | CNPDC2   | CNPDC1   | -    | 0000          |

|                             | 1                               | 31:16     | _         | _         |           | _         |                |       |      |      | —    | —    |      | —        | _        |          | —        |      | 0000          |

| 0270                        | CNCONC                          | 15:0      | ON        | —         | —         | —         | EDGE<br>DETECT | —     | —    | —    | —    | —    | —    | —        | —        | —        | —        | —    | 0000          |

| 0280                        | CNENC                           | 31:16     | _         | —         |           | —         | —              | —     | —    | —    |      | _    | —    | _        | —        | —        | —        | —    | 0000          |

| 0200                        | CNENC                           | 15:0      | CNENC15   | CNENC14   | CNENC13   | CNENC12   |                |       |      |      |      |      |      | CNENC4   | CNENC3   | CNENC2   | CNENC1   | _    | 0000          |

| 0200                        | CNSTATC                         | 31:16     | _         | —         | —         | —         | —              | —     | —    | —    |      | _    | —    | _        | —        | —        | —        | —    | 0000          |

| 0290                        | CINSTATC                        | 15:0      | CNSTATC15 | CNSTATC14 | CNSTATC13 | CNSTATC12 | _              | _     | _    | _    |      | _    | —    | CNSTATC4 | CNSTATC3 | CNSTATC2 | CNSTATC1 | _    | 0000          |

| 02A0                        | CNNEC                           | 31:16     | _         | —         |           |           | -              |       |      |      |      | _    | _    | _        | _        | _        |          |      | 0000          |

| 02A0                        | CININEC                         | 15:0      | CNNEC15   | CNNEC14   | CNNEC13   | CNNEC12   | —              |       |      |      | _    | —    | —    | CNNEC4   | CNNEC3   | CNNEC2   | CNNEC1   |      | 0000          |

| 02B0                        | CNFC                            | 31:16     | _         | -         | —         |           | -              |       |      |      | _    | _    | —    | _        | -        | -        | -        |      | 0000          |

| 0200                        | CINEC                           | 15:0      | CNFC15    | CNFC14    | CNFC13    | CNFC12    | _              |       | _    |      | _    | _    | —    | CNFC4    | CNFC3    | CNFC2    | CNFC1    |      | 0000          |

x = Unknown value on Reset; --- = Unimplemented, read as '0'; Reset values are shown in hexadecimal. Legend:

All registers in this table have corresponding CLR, SET and INV registers at its virtual address, plus an offset of 0x4, 0x8 and 0xC, respectively. See Section 12.3 "CLR, SET, and INV Registers" for more information. Note 1:

## TABLE 12-21: PORTK REGISTER MAP FOR 144-PIN DEVICES ONLY

| ess                         |                                 | ø         | Bits  |       |       |       |                |       |      |      |              |              |              |              |              |              |              |              |               |

|-----------------------------|---------------------------------|-----------|-------|-------|-------|-------|----------------|-------|------|------|--------------|--------------|--------------|--------------|--------------|--------------|--------------|--------------|---------------|

| Virtual Address<br>(BF86_#) | Register<br>Name <sup>(1)</sup> | Bit Range | 31/15 | 30/14 | 29/13 | 28/12 | 27/11          | 26/10 | 25/9 | 24/8 | 23/7         | 22/6         | 21/5         | 20/4         | 19/3         | 18/2         | 17/1         | 16/0         | All<br>Resets |

| 0910                        | TRISK                           | 31:16     | _     | -     | —     | —     | —              | _     | _    | —    | -            | —            | _            |              | —            | —            | —            | —            | 0000          |

| 0010                        | INION                           | 15:0      | —     | _     | —     | —     | —              | —     | —    | —    | TRISK7       | TRISK6       | TRISK5       | TRISK4       | TRISK3       | TRISK2       | TRISK1       | TRISK0       | OOFF          |

| 0920                        | PORTK                           | 31:16     | —     | _     | —     | —     | —              | —     | —    | _    | —            | —            | —            | —            | —            | —            | —            | —            | 0000          |

| 0020                        |                                 | 15:0      | —     | _     | —     | —     | —              | —     | —    | —    | RK7          | RK6          | RK5          | RK4          | RK3          | RK2          | RK1          | RK0          | xxxx          |

| 0930                        | LATK                            | 31:16     | —     | —     | —     | —     | —              | _     | —    | —    | —            | —            | —            | —            | —            | —            | —            | _            | 0000          |

|                             |                                 | 15:0      | _     | _     | —     | _     | —              | _     | _    | _    | LATK7        | LATK6        | LATK5        | LATK4        | LATK3        | LATK2        | LATK1        | LATK0        | XXXX          |

| 0940                        | ODCK                            | 31:16     | _     | _     | —     | _     | _              | _     | —    | —    | —            | —            | —            | —            | —            | —            | —            | —            | 0000          |

|                             |                                 | 15:0      | _     | _     | —     | _     | _              | _     | _    | _    | ODCK7        | ODCK6        | ODCK5        | ODCK4        | ODCK3        | ODCK2        | ODCK1        | ODCK0        | 0000          |

| 0950                        | CNPUK                           | 31:16     | _     | _     | _     | _     | _              | _     | _    | _    | -            | -            | -            | —            | -            | -            | -            | -            | 0000          |

|                             |                                 | 15:0      | _     | _     | _     | _     | _              | _     | _    | _    | CNPUK7       | CNPUK6       | CNPUK5       | CNPUK4       | CNPUK3       | CNPUK2       | CNPUK1       | CNPUK0       | 0000          |

| 0960                        | CNPDK                           | 31:16     |       |       | -     |       |                |       |      |      | -            |              |              |              |              |              |              |              | 0000          |

|                             |                                 | 15:0      | _     | _     | _     | _     | _              | _     |      | _    | CNPDK7       | CNPDK6       | CNPDK5       | CNPDK4       | CNPDK3       | CNPDK2       | CNPDK1       | CNPDK0       | 0000          |

| 0070                        | CNCONK                          | 31:16     | _     | _     | —     | —     | -              |       |      | _    |              | _            | _            | _            | _            |              |              |              | 0000          |

| 0070                        | onconin                         | 15:0      | ON    | —     | —     | —     | EDGE<br>DETECT | —     | —    | —    | —            | —            | —            | —            | —            | —            | —            | —            | 0000          |

| 0980                        | CNENK                           | 31:16     | -     |       | _     | _     | _              | _     | _    | _    | ١            | _            |              |              | -            | -            | -            | _            | 0000          |

| 0900                        | CINLINK                         | 15:0      | _     | _     | —     | —     | _              | _     | _    | _    | CNENK7       | CNENK6       | CNENK5       | CNENK4       | CNENK3       | CNENK2       | CNENK1       | CNENK0       | 0000          |

|                             |                                 | 31:16     | —     | —     | —     | —     | —              | —     | —    | —    | -            | —            | —            | -            | —            | —            | —            | _            | 0000          |

| 0990                        | CNSTATK                         | 15:0      | -     | _     | -     | -     | -              | -     | _    | —    | CN<br>STATK7 | CN<br>STATK6 | CN<br>STATK5 | CN<br>STATK4 | CN<br>STATK3 | CN<br>STATK2 | CN<br>STATK1 | CN<br>STATK0 | 0000          |

| 0040                        | CNNEK                           | 31:16     | _     | _     | —     | _     | _              | _     | _    | _    | _            | —            | _            | _            | _            | —            | _            | _            | 0000          |

| 09A0                        | CININER                         | 15:0      | _     |       |       |       |                |       |      |      | CNNEK7       | CNNEK6       | CNNEK5       | CNNEK4       | CNNEK3       | CNNEK2       | CNNEK1       | CNNEK0       | 0000          |

| 09B0                        | CNFK                            | 31:16     | _     | _     | —     | —     | _              | _     | _    | _    | _            | —            | _            |              |              | —            | —            |              | 0000          |

| 0900                        | UNER                            | 15:0      | _     | -     | _     | _     | _              | _     | _    | _    | CNFK7        | CNFK6        | CNFK5        | CNFK4        | CNFK3        | CNFK2        | CNFK1        | CNFK0        | 0000          |

Legend:

x = Unknown value on Reset; — = Unimplemented, read as '0'; Reset values are shown in hexadecimal. All registers in this table have corresponding CLR, SET and INV registers at its virtual address, plus an offset of 0x4, 0x8, and 0xC, respectively. See Section 12.3 "CLR, SET, and INV Registers" for Note 1: more information.

| REGISTER 20-13: | SQI1STAT2: SQI STATUS REGISTER 2 |

|-----------------|----------------------------------|

|-----------------|----------------------------------|

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|

| 31:24        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 31.24        | _                 | _                 | _                 | _                 | _                 | _                 | _                | —                |

| 00.40        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | R-0              | R-0              |

| 23:16        | —                 | _                 |                   | —                 | _                 | _                 | CMDST            | AT<1:0>          |

| 45.0         | U-0               | U-0               | U-0               | U-0               | R-0               | R-0               | R-0              | R-0              |

| 15:8         | —                 | —                 | —                 | —                 |                   | CONAVA            | \IL<4:1>         |                  |

| 7.0          | R-0               | R-0               | R-0               | R-0               | R-0               | U-0               | R-0              | R-0              |

| 7:0          | CONAVAIL<0>       | SQID3             | SQID2             | SQID1             | SQID0             |                   | RXUN             | TXOV             |

#### Legend:

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, read as '0' |                    |  |  |  |

|-------------------|------------------|------------------------------------|--------------------|--|--|--|

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared               | x = Bit is unknown |  |  |  |

bit 31-18 Unimplemented: Read as '0'

- bit 17-16 **CMDSTAT<1:0>:** Current Command Status bits These bits indicate the current command status.

- 11 = Reserved

- 10 = Receive

- 01 = Transmit

- 00 = Idle

- bit 15-12 Unimplemented: Read as '0'

bit 11-7 **CONAVAIL<4:0>:** Control FIFO Space Available bits These bits indicate the available control Word space. 11111 = 32 bytes are available 11110 = 31 bytes are available

- •

- 00001 = 1 byte is available

- 00000 = No bytes are available

## bit 6 SQID3: SQID3 Status bit

- 1 = Data is present on SQID3

- 0 = Data is not present on SQID3

- bit 5 SQID2: SQID2 Status bit

- 1 = Data is present on SQID2

- 0 = Data is not present on SQID2

# bit 4 **SQID1:** SQID1 Status bit

- 1 = Data is present on SQID1

0 = Data is not present on SQID1

- bit 3 **SQID0:** SQID0 Status bit

- 1 = Data is present on SQID0

- 0 = Data is not present on SQID0

- bit 2 Unimplemented: Read as '0'

- bit 1 RXUN: Receive FIFO Underflow Status bit

- 1 = Receive FIFO Underflow has occurred

- 0 = Receive FIFO underflow has not occurred

- bit 0 **TXOV:** Transmit FIFO Overflow Status bit

- 1 = Transmit FIFO overflow has occurred

- 0 = Transmit FIFO overflow has not occurred

## 23.1 PMP Control Registers

## TABLE 23-1: PARALLEL MASTER PORT REGISTER MAP

| ess                         |                                 | ő             |        | Bits         |       |       |           |        |        |        |            |        |      |       |        |           |           |         |            |

|-----------------------------|---------------------------------|---------------|--------|--------------|-------|-------|-----------|--------|--------|--------|------------|--------|------|-------|--------|-----------|-----------|---------|------------|

| Virtual Address<br>(BF82_#) | Register<br>Name <sup>(1)</sup> | Bit Range     | 31/15  | 30/14        | 29/13 | 28/12 | 27/11     | 26/10  | 25/9   | 24/8   | 23/7       | 22/6   | 21/5 | 20/4  | 19/3   | 18/2      | 17/1      | 16/0    | All Resets |

| E000                        | PMCON                           | 31:16         |        | —            | —     |       | —         | —      | —      |        | RDSTART    |        | —    |       | _      |           | DUALBUF   | _       | 0000       |

| LUUU                        | FINCON                          | 15:0          | ON     | —            | SIDL  | ADRMU | JX<1:0>   | PMPTTL | PTWREN | PTRDEN | CSF        | <1:0>  | ALP  | CS2P  | CS1P   |           | WRSP      | RDSP    | 0000       |

| E010                        | PMMODE                          | 31:16         | _      | —            | —     | _     | —         | —      |        | _      | —          | —      | —    | —     | —      | _         | —         | _       | 0000       |

| 2010                        | _                               | 15:0          | BUSY   | IRQM         | <1:0> | INCM  | <1:0>     | MODE16 | MODE   | <1:0>  | WAITE      | 3<1:0> |      | WAITN | /<3:0> |           | WAITE     | <1:0>   | 0000       |

|                             |                                 | 31:16         | _      | —            | —     | —     |           | —      | —      | —      | —          | —      | —    | —     | —      | —         | —         | _       | 0000       |

| E020                        | PMADDR                          | 15:0          | CS2    | CS1          |       |       |           |        |        |        | ADDR       | <13.0> |      |       |        |           |           |         | 0000       |

|                             |                                 |               | ADDR15 | ADDR14       |       |       |           | -      |        |        |            |        |      |       |        |           |           |         | 0000       |

| E030                        | PMDOUT                          | 31:16         | _      | —            | —     | —     | _         | —      | —      | —      |            | —      | —    | —     | _      | —         | —         | _       | 0000       |

|                             |                                 | 15:0          |        |              |       |       |           |        |        | DATAOL | JT<15:0>   |        |      |       |        |           |           |         | 0000       |

| E040                        | PMDIN                           | N 31:16       |        |              |       |       |           |        |        |        | _          | 0000   |      |       |        |           |           |         |            |

|                             |                                 | 31:16         |        |              |       |       |           |        |        | DATAI  |            |        |      |       |        |           |           |         | 0000       |

| E050                        | PMAEN                           | 15:0          | -      | —            | —     | _     | _         | —      | _      |        |            | _      | —    | —     | —      |           | —         | _       |            |

|                             |                                 |               |        |              |       |       |           |        |        |        | <15:0>     |        |      |       |        |           |           |         | 0000       |

| E060                        | PMSTAT                          | 31:16<br>15:0 | IBF    | —<br>IBOV    | _     | _     | IB3F      | IB2F   | IB1F   | IB0F   |            |        |      | _     | OB3E   | —<br>OB2E | —<br>OB1E |         | 0000       |

|                             |                                 | 31:16         |        | <u>іво</u> у |       |       | івэг<br>— |        |        |        |            |        |      |       |        |           |           | <u></u> | 008F       |

| E070                        | PMWADDR                         | 51.10         | WCS2   | WCS1         |       |       |           |        | _      |        | _          |        |      |       |        |           | _         |         | 0000       |

| 2070                        |                                 | 15:0          |        | WADDR14      |       |       |           |        |        |        | WADDF      |        |      |       |        |           |           |         | 0000       |

|                             |                                 | 31:16         |        |              |       | _     |           | _      | _      | _      |            | <13:0> | _    | _     | _      | _         | _         | _       | 0000       |

| E090                        | PMRADDR                         | 51.10         | RCS2   | RCS1         |       |       |           |        |        |        |            |        |      |       |        |           | _         |         | 0000       |

| E080                        | FINIKADDR                       | 15:0          |        | RADDR14      |       |       |           |        |        |        | RADDF      |        |      |       |        |           |           |         | 0000       |

|                             |                                 | 31:16         | 31:16  |              |       | _     | _         |        |        |        |            | <13:0> |      | _     |        | _         |           | _       | 0000       |

| E090                        | PMRDIN                          |               |        |              |       | _     |           | _      |        |        |            | -      |      | _     |        |           | _         | _       | _          |

|                             |                                 | 15:0          | 15:0   |              |       |       |           |        |        | RL     | DATAIN<15: | 0>     |      |       |        |           |           |         | 0000       |

Legend: x = unknown value on Reset; --- = unimplemented, read as '0'. Reset values are shown in hexadecimal.

Note 1: All registers in this table have corresponding CLR, SET and INV registers at their virtual addresses, plus offsets of 0x4, 0x8 and 0xC, respectively. See Section 12.3 "CLR, SET, and INV Registers" for more information.

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |  |  |  |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|--|--|--|

| 04.04        | R-0               | R-0               | R-0               | R-0               | R-0               | R-0               | R-0              | R-0              |  |  |  |

| 31:24        | EF                | RRMODE<2:0        | >                 |                   | ERROP<2:0>        | ERRPHA            | SE<1:0>          |                  |  |  |  |

| 22.16        | U-0 U-0           |                   | R-0               | R-0               | R-0               | R-0               | R-0              | R-0              |  |  |  |

| 23:16        | —                 | —                 |                   | BDSTAT            | FE<3:0>           | START             | ACTIVE           |                  |  |  |  |

| 15.0         | R-0               | R-0               | R-0               | R-0               | R-0               | R-0               | R-0              | R-0              |  |  |  |

| 15:8         |                   |                   |                   |                   |                   |                   |                  |                  |  |  |  |

| 7.0          | R-0               | R-0               | R-0               | R-0               | R-0               | R-0               | R-0              | R-0              |  |  |  |

| 7:0          | BDCTRL<7:0>       |                   |                   |                   |                   |                   |                  |                  |  |  |  |

#### **REGISTER 26-5: CESTAT: CRYPTO ENGINE STATUS REGISTER**

#### Legend:

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, read as '0' |                    |  |  |  |  |

|-------------------|------------------|------------------------------------|--------------------|--|--|--|--|

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared               | x = Bit is unknown |  |  |  |  |

bit 31-29 ERRMODE<2:0>: Internal Error Mode Status bits

- 111 = Reserved

- 110 = Reserved

- 101 = Reserved

- 100 = Reserved

- 011 = CEK operation

- 010 = KEK operation

- 001 = Preboot authentication

- 000 = Normal operation

#### bit 28-26 ERROP<2:0>: Internal Error Operation Status bits

- 111 = Reserved

- 110 = Reserved

- 101 = Reserved

- 100 = Authentication

- 011 = Reserved

- 010 = Decryption

- 001 = Encryption

- 000 = Reserved

#### bit 25-24 ERRPHASE<1:0>: Internal Error Phase of DMA Status bits

- 11 = Destination data

- 10 = Source data

- 01 = Security Association (SA) access

- 00 = Buffer Descriptor (BD) access

#### bit 23-22 Unimplemented: Read as '0'

#### bit 21-18 BDSTATE<3:0>: Buffer Descriptor Processor State Status bits

The current state of the BDP:

- 1111 = Reserved

- •

- 0111 = Reserved

- 0110 = SA fetch

- 0101 = Fetch BDP is disabled

- 0100 = Descriptor is done

- 0011 = Data phase

- 0010 = BDP is loading

- 0001 = Descriptor fetch request is pending

- 0000 = BDP is idle

- bit 17 START: DMA Start Status bit

- 1 = DMA start has occurred

- 0 = DMA start has not occurred

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|

| 31:24        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

|              |                   | _                 | _                 | —                 | _                 | -                 | _                | —                |

| 23:16        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

|              |                   | _                 | -                 |                   | _                 |                   |                  | —                |

| 45.0         | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 15:8         |                   | _                 | _                 | _                 | _                 | _                 | _                | —                |

| 7:0          | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |

|              | HDRLEN<7:0>       |                   |                   |                   |                   |                   |                  |                  |

### REGISTER 26-9: CEHDLEN: CRYPTO ENGINE HEADER LENGTH REGISTER

## Legend:

| Logona.                           |                  |                                    |                    |  |

|-----------------------------------|------------------|------------------------------------|--------------------|--|

| R = Readable bit W = Writable bit |                  | U = Unimplemented bit, read as '0' |                    |  |

| -n = Value at POR                 | '1' = Bit is set | '0' = Bit is cleared               | x = Bit is unknown |  |

bit 31-8 Unimplemented: Read as '0'

bit 7-0 **HDRLEN<7:0>:** DMA Header Length bits For every packet, skip this length of locations and start filling the data.

## REGISTER 26-10: CETRLLEN: CRYPTO ENGINE TRAILER LENGTH REGISTER

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|

| 31:24        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

|              | —                 | —                 | —                 | —                 | —                 | —                 | —                | —                |

| 22:16        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 23:16        |                   | _                 | _                 | —                 | —                 | _                 |                  | —                |

| 45.0         | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 15:8         |                   | _                 | _                 | —                 | —                 | _                 | _                | —                |

| 7:0          | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |

|              | TRLRLEN<7:0>      |                   |                   |                   |                   |                   |                  |                  |

| Legend:           |                  |                          |                    |

|-------------------|------------------|--------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, r | ead as '0'         |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared     | x = Bit is unknown |

## bit 31-8 Unimplemented: Read as '0'

bit 7-0 **TRLRLEN<7:0>:** DMA Trailer Length bits

For every packet, skip this length of locations at the end of the current packet and start putting the next packet.

| REGISTER 30-17: | ETHFRMTXOK: ETHERNET CONTROLLER FRAMES TRANSMITTED OK |

|-----------------|-------------------------------------------------------|

|                 | STATISTICS REGISTER                                   |

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|

| 31:24        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

|              | —                 | —                 | —                 | —                 | —                 | _                 | —                | —                |

| 23:16        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

|              | —                 | —                 | —                 | —                 | —                 | _                 | _                | —                |

| 15.0         | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |

| 15:8         | FRMTXOKCNT<15:8>  |                   |                   |                   |                   |                   |                  |                  |

| 7:0          | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |

|              | FRMTXOKCNT<7:0>   |                   |                   |                   |                   |                   |                  |                  |

### Legend:

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, r | nented bit, read as '0' |  |  |

|-------------------|------------------|--------------------------|-------------------------|--|--|

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared     | x = Bit is unknown      |  |  |

#### bit 31-16 Unimplemented: Read as '0'

bit 15-0 **FRMTXOKCNT<15:0>:** Frame Transmitted OK Count bits Increment counter for frames successfully transmitted.

Note 1: This register is only used for TX operations.

2: This register is automatically cleared by hardware after a read operation, unless the byte enables for bytes 0/1 are '0'.

**3:** It is recommended to use the SET, CLR, or INV registers to set or clear any bit in this register. Setting or clearing any bits in this register should only be done for debug/test purposes.

NOTES:

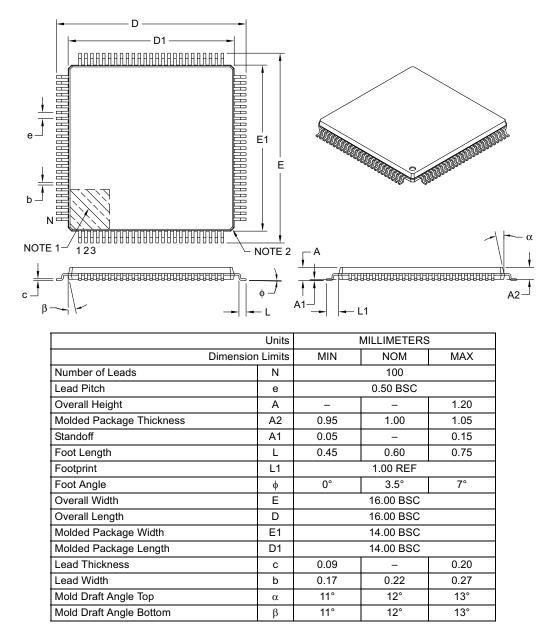

## PIC32MZ Embedded Connectivity with Floating Point Unit (EF) Family

## 100-Lead Plastic Thin Quad Flatpack (PF) – 14x14x1 mm Body, 2.00 mm [TQFP]

**Note:** For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

#### Notes:

1. Pin 1 visual index feature may vary, but must be located within the hatched area.

2. Chamfers at corners are optional; size may vary.

3. Dimensions D1 and E1 do not include mold flash or protrusions. Mold flash or protrusions shall not exceed 0.25 mm per side.

- 4. Dimensioning and tolerancing per ASME Y14.5M.

- BSC: Basic Dimension. Theoretically exact value shown without tolerances.

REF: Reference Dimension, usually without tolerance, for information purposes only.

Microchip Technology Drawing C04-110B

## B.10 Serial Quad Interface (SQI)

On PIC32MZ EF devices, the SQI module has been updated with the following features:

- FIFOs can be reset through the CONFIFORST (SQI1CFG<19>), RXFIFORST (SQI1CFG<18>), and TXFIFORST (SQI1CFG<17>) bits in Register 20-3

- A new Flash Status check is available, which will allow the SQI to automatically query the status of the external device during write/erase operations without software intervention. See the SCHECK bit (SQI1CON<24>) and the SQI1MEMSTAT register (Register 20-4 and Register 20-24, respectively).

- The SQI clock divider bits have been expanded, and can use an undivided clock. See the CLKDIV<10:0> bits (SQI1CLKCON<18:8>) in Register 20-5.

- A new DMA Bus Error Interrupt is available through the DMAEIE (SQI1INTEN<11>), DMAEIF (SQI1INTSTAT<11>), and DMAEISE (SQI1INTSIGEN<11>) bits in Register 20-8, Register 20-9, and Register 20-22, respectively

- The SQI1STAT2 register (see Register 20-13) has two new fields:

- CMDSTAT<1:0> (SQI1STAT2<17:16>) indicates the current command status

- CONAVAIL<4:0> (SQI1STAT<11:8>) indicates how many spaces are available in the Control FIFO.

- The TAP Controller within the SQI can be configured for various timing requirements via the SQI1TAPCON register (Register 20-23)

- Two new XIP mode registers (SQI1XCON3 and SQI1XCON4) have been added for additional command sequencing (see Register 20-25 and Register 20-26, respectively)

Refer to **20.0 "Serial Quad Interface (SQI)"** and **Section 46. "Serial Quad Interface (SQI)"** (DS60001128) for more information.

## B.11 PMP

On PIC32MZ EF devices, the PMP features the ability to buffer reads and writes in both directions, and can read and write from different addresses. Refer to **23.0 "Parallel Master Port (PMP)"** and **Section 43. "Parallel Master Port"** (DS60001346) for information.