Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XF

| Product Status             | Active                                                                           |

|----------------------------|----------------------------------------------------------------------------------|

| Core Processor             | MIPS32® M-Class                                                                  |

| Core Size                  | 32-Bit Single-Core                                                               |

| Speed                      | 180MHz                                                                           |

| Connectivity               | CANbus, Ethernet, I <sup>2</sup> C, PMP, SPI, SQI, UART/USART, USB OTG           |

| Peripherals                | Brown-out Detect/Reset, DMA, I <sup>2</sup> S, POR, PWM, WDT                     |

| Number of I/O              | 46                                                                               |

| Program Memory Size        | 1MB (1M x 8)                                                                     |

| Program Memory Type        | FLASH                                                                            |

| EEPROM Size                | -                                                                                |

| RAM Size                   | 256K x 8                                                                         |

| Voltage - Supply (Vcc/Vdd) | 2.1V ~ 3.6V                                                                      |

| Data Converters            | A/D 24x12b                                                                       |

| Oscillator Type            | Internal                                                                         |

| Operating Temperature      | -40°C ~ 125°C                                                                    |

| Mounting Type              | Surface Mount                                                                    |

| Package / Case             | 64-VFQFN Exposed Pad                                                             |

| Supplier Device Package    | 64-QFN (9x9)                                                                     |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic32mz1024eff064-e-mr |

|                            |                                                                                  |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

#### TABLE 5: PIN NAMES FOR 144-PIN DEVICES

#### 144-PIN LQFP AND TQFP (TOP VIEW)

#### PIC32MZ0512EF(E/F/K)144 PIC32MZ1024EF(G/H/M)144 PIC32MZ1024EF(E/F/K)144 PIC32MZ2048EF(G/H/M)144

144

1

| Pin<br>Number | Full Pin Name                  |     | Pin<br>Number | Full Pin Name              |

|---------------|--------------------------------|-----|---------------|----------------------------|

| 1             | AN23/RG15                      |     | 37            | PGEC2/AN46/RPB6/RB6        |

| 2             | EBIA5/AN34/PMA5/RA5            | 1 1 | 38            | PGED2/AN47/RPB7/RB7        |

| 3             | EBID5/AN17/RPE5/PMD5/RE5       | 1 1 | 39            | VREF-/CVREF-/AN27/RA9      |

| 4             | EBID6/AN16/PMD6/RE6            | 1 1 | 40            | VREF+/CVREF+/AN28/RA10     |

| 5             | EBID7/AN15/PMD7/RE7            | 1 1 | 41            | AVdd                       |

| 6             | EBIA6/AN22/RPC1/PMA6/RC1       | 1 1 | 42            | AVss                       |

| 7             | AN35/ETXD0/RJ8                 | 1   | 43            | AN38/ETXD2/RH0             |

| 8             | AN36/ETXD1/RJ9                 | 1 1 | 44            | AN39/ETXD3/RH1             |

| 9             | EBIBS0/RJ12                    | 1 [ | 45            | EBIRP/RH2                  |

| 10            | EBIBS1/RJ10                    | 1 1 | 46            | RH3                        |

| 11            | EBIA12/AN21/RPC2/PMA12/RC2     | 1 1 | 47            | EBIA10/AN48/RPB8/PMA10/RB8 |

| 12            | EBIWE/AN20/RPC3/PMWR/RC3       | 1 1 | 48            | EBIA7/AN49/RPB9/PMA7/RB9   |

| 13            | EBIOE/AN19/RPC4/PMRD/RC4       | 1   | 49            | CVREFOUT/AN5/RPB10/RB10    |

| 14            | AN14/C1IND/RPG6/SCK2/RG6       |     | 50            | AN6/RB11                   |

| 15            | AN13/C1INC/RPG7/SDA4/RG7       | 1 1 | 51            | EBIA1/PMA1/RK1             |

| 16            | AN12/C2IND/RPG8/SCL4/RG8       |     | 52            | EBIA3/PMA3/RK2             |

| 17            | Vss                            | 1 1 | 53            | EBIA17/RK3                 |

| 18            | Vdd                            |     | 54            | Vss                        |

| 19            | EBIA16/RK0                     | 1   | 55            | VDD                        |

| 20            | MCLR                           |     | 56            | TCK/AN29/RA1               |

| 21            | EBIA2/AN11/C2INC/RPG9/PMA2/RG9 | 1 1 | 57            | TDI/AN30/RPF13/SCK5/RF13   |

| 22            | TMS/AN24/RA0                   |     | 58            | TDO/AN31/RPF12/RF12        |

| 23            | AN25/RPE8/RE8                  |     | 59            | AN7/RB12                   |

| 24            | AN26/RPE9/RE9                  |     | 60            | AN8/RB13                   |

| 25            | AN45/C1INA/RPB5/RB5            |     | 61            | AN9/RPB14/SCK3/RB14        |

| 26            | AN4/C1INB/RB4                  |     | 62            | AN10/RPB15/OCFB/RB15       |

| 27            | AN37/ERXCLK/EREFCLK/RJ11       |     | 63            | Vss                        |

| 28            | EBIA13/PMA13/RJ13              |     | 64            | VDD                        |

| 29            | EBIA11/PMA11/RJ14              |     | 65            | AN40/ERXERR/RH4            |

| 30            | EBIA0/PMA0/RJ15                |     | 66            | AN41/ERXD1/RH5             |

| 31            | AN3/C2INA/RPB3/RB3             |     | 67            | AN42/ERXD2/RH6             |

| 32            | Vss                            |     | 68            | EBIA4/PMA4/RH7             |

| 33            | VDD                            |     | 69            | AN32/RPD14/RD14            |

| 34            | AN2/C2INB/RPB2/RB2             |     | 70            | AN33/RPD15/SCK6/RD15       |

| 35            | PGEC1/AN1/RPB1/RB1             |     | 71            | OSC1/CLKI/RC12             |

| 36            | PGED1/AN0/RPB0/RB0             | l l | 72            | OSC2/CLKO/RC15             |

Note 1: The RPn pins can be used by remappable peripherals. See Table 1 for the available peripherals and Section 12.4 "Peripheral Pin Select (PPS)" for restrictions.

2: Every I/O port pin (RAx-RKx) can be used as a change notification pin (CNAx-CNKx). See Section 12.0 "I/O Ports" for more information.

3: Shaded pins are 5V tolerant.

|          |                        | Pin Number      |                 |                          |             |                |                                          |

|----------|------------------------|-----------------|-----------------|--------------------------|-------------|----------------|------------------------------------------|

| Pin Name | 64-pin<br>QFN/<br>TQFP | 100-pin<br>TQFP | 124-pin<br>VTLA | 144-pin<br>TQFP/<br>LQFP | Pin<br>Type | Buffer<br>Type | Description                              |

| AERXD0   | - 1                    | 18              | _               | —                        | Ι           | ST             | Alternate Ethernet Receive Data 0        |

| AERXD1   | —                      | 19              | _               | —                        | Ι           | ST             | Alternate Ethernet Receive Data 1        |

| AERXD2   | —                      | 28              | _               | —                        | Ι           | ST             | Alternate Ethernet Receive Data 2        |

| AERXD3   | —                      | 29              | —               | —                        | I           | ST             | Alternate Ethernet Receive Data 3        |

| AERXERR  | —                      | 1               | —               | —                        | I           | ST             | Alternate Ethernet Receive Error Input   |

| AERXDV   | —                      | 12              | —               | —                        | I           | ST             | Alternate Ethernet Receive Data Valid    |

| AERXCLK  | —                      | 16              | —               | —                        | I           | ST             | Alternate Ethernet Receive Clock         |

| AETXD0   | —                      | 47              | —               | —                        | 0           | —              | Alternate Ethernet Transmit Data 0       |

| AETXD1   | —                      | 48              | —               | —                        | 0           | —              | Alternate Ethernet Transmit Data 1       |

| AETXD2   | —                      | 44              | —               | —                        | 0           | —              | Alternate Ethernet Transmit Data 2       |

| AETXD3   | —                      | 43              | —               | —                        | 0           | —              | Alternate Ethernet Transmit Data 3       |

| AETXERR  | —                      | 35              | —               | —                        | 0           | —              | Alternate Ethernet Transmit Error        |

| AECOL    | —                      | 42              | —               | —                        | I           | ST             | Alternate Ethernet Collision Detect      |

| AECRS    | —                      | 41              | —               | —                        | I           | ST             | Alternate Ethernet Carrier Sense         |

| AETXCLK  | —                      | 66              | —               | —                        | I           | ST             | Alternate Ethernet Transmit Clock        |

| AEMDC    | —                      | 70              | —               | —                        | 0           | —              | Alternate Ethernet Management Data Clock |

| AEMDIO   | —                      | 71              | _               | —                        | I/O         | —              | Alternate Ethernet Management Data       |

| AETXEN   | —                      | 67              | —               | —                        | 0           | —              | Alternate Ethernet Transmit Enable       |

| Legend:  | CMOS = CN              | MOS-compa       | atible input    | or output                |             | Analog =       | Analog input P = Power                   |

**TABLE 1-18: ALTERNATE ETHERNET MII PINOUT I/O DESCRIPTIONS**

CMOS = CMOS-compatible input or output ST = Schmitt Trigger input with CMOS levels TTL = Transistor-transistor Logic input buffer

Analog = Analog input O = Output

I = Input

PPS = Peripheral Pin Select

#### **TABLE 1-19: ALTERNATE ETHERNET RMII PINOUT I/O DESCRIPTIONS**

|                        | Pin Nu                                                             | mber                                                                                                                                                                                                                                                                  |                                                                                                                                                                                                                                                                                             |                                                                                                                                                                                                                                                                                                                                                |                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |  |  |

|------------------------|--------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| 64-pin<br>QFN/<br>TQFP | 100-pin<br>TQFP                                                    | 124-pin<br>VTLA                                                                                                                                                                                                                                                       | 144-pin<br>TQFP/<br>LQFP                                                                                                                                                                                                                                                                    | Pin<br>Type                                                                                                                                                                                                                                                                                                                                    | Buffer<br>Type                                                                                                                                                                                                                                                                                                                                                                                                                                        | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |  |  |

| 43                     | 18                                                                 | -                                                                                                                                                                                                                                                                     | _                                                                                                                                                                                                                                                                                           | Ι                                                                                                                                                                                                                                                                                                                                              | ST                                                                                                                                                                                                                                                                                                                                                                                                                                                    | Alternate Ethernet Receive Data 0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |  |  |

| 46                     | 19                                                                 |                                                                                                                                                                                                                                                                       | —                                                                                                                                                                                                                                                                                           | I                                                                                                                                                                                                                                                                                                                                              | ST                                                                                                                                                                                                                                                                                                                                                                                                                                                    | Alternate Ethernet Receive Data 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |  |  |

| 51                     | 1                                                                  |                                                                                                                                                                                                                                                                       | —                                                                                                                                                                                                                                                                                           | I                                                                                                                                                                                                                                                                                                                                              | ST                                                                                                                                                                                                                                                                                                                                                                                                                                                    | Alternate Ethernet Receive Error Input                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |  |  |

| 57                     | 47                                                                 |                                                                                                                                                                                                                                                                       | —                                                                                                                                                                                                                                                                                           | 0                                                                                                                                                                                                                                                                                                                                              |                                                                                                                                                                                                                                                                                                                                                                                                                                                       | Alternate Ethernet Transmit Data 0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |  |  |

| 56                     | 48                                                                 |                                                                                                                                                                                                                                                                       | —                                                                                                                                                                                                                                                                                           | 0                                                                                                                                                                                                                                                                                                                                              |                                                                                                                                                                                                                                                                                                                                                                                                                                                       | Alternate Ethernet Transmit Data 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |  |  |

| 30                     | 70                                                                 |                                                                                                                                                                                                                                                                       | —                                                                                                                                                                                                                                                                                           | 0                                                                                                                                                                                                                                                                                                                                              |                                                                                                                                                                                                                                                                                                                                                                                                                                                       | Alternate Ethernet Management Data Clock                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |  |  |

| 49                     | 71                                                                 |                                                                                                                                                                                                                                                                       | —                                                                                                                                                                                                                                                                                           | I/O                                                                                                                                                                                                                                                                                                                                            |                                                                                                                                                                                                                                                                                                                                                                                                                                                       | Alternate Ethernet Management Data                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |  |  |

| 50                     | 67                                                                 |                                                                                                                                                                                                                                                                       | —                                                                                                                                                                                                                                                                                           | 0                                                                                                                                                                                                                                                                                                                                              |                                                                                                                                                                                                                                                                                                                                                                                                                                                       | Alternate Ethernet Transmit Enable                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |  |  |

| 45                     | 16                                                                 | —                                                                                                                                                                                                                                                                     | —                                                                                                                                                                                                                                                                                           | Ι                                                                                                                                                                                                                                                                                                                                              | ST                                                                                                                                                                                                                                                                                                                                                                                                                                                    | Alternate Ethernet Reference Clock                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |  |  |

| 62                     | 12                                                                 | _                                                                                                                                                                                                                                                                     | —                                                                                                                                                                                                                                                                                           | I                                                                                                                                                                                                                                                                                                                                              | ST                                                                                                                                                                                                                                                                                                                                                                                                                                                    | Alternate Ethernet Carrier Sense Data Valid                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |  |  |

|                        | QFN/<br>TQFP<br>43<br>46<br>51<br>57<br>56<br>30<br>49<br>50<br>45 | 64-pin<br>QFN/<br>TQFP         100-pin<br>TQFP           43         18           46         19           51         1           57         47           56         48           30         70           49         71           50         67           45         16 | QFN/<br>TQFP         100-pin<br>TQFP         124-pin<br>VTLA           43         18            46         19            51         1            57         47            56         48            30         70            49         71            50         67            45         16 | 64-pin<br>QFN/<br>TQFP         100-pin<br>TQFP         124-pin<br>VTLA         144-pin<br>TQFP/<br>LQFP           43         18             46         19             51         1             57         47             56         48             30         70             49         71             50         67             45         16 | 64-pin<br>QFN/<br>TQFP         100-pin<br>TQFP         124-pin<br>VTLA         144-pin<br>TQFP/<br>LQFP         Pin<br>Type           43         18          1           46         19          1           51         1          1           57         47          0           56         48          0           30         70          0           49         71          0           50         67          0           45         16          1 | 64-pin<br>QFN/<br>TQFP         100-pin<br>TQFP         124-pin<br>VTLA         144-pin<br>TQFP/<br>LQFP         Pin<br>TQFP/<br>LQFP         Buffer<br>Type           43         18          1         ST           46         19          1         ST           51         1           I         ST           57         47          0            56         48          0            30         70          0            49         71          N/O            50         67          0            45         16           I         ST |  |  |

CMOS = CMOS-compatible input or output Legend: ST = Schmitt Trigger input with CMOS levels TTL = Transistor-transistor Logic input buffer

Analog = Analog input O = Output PPS = Peripheral Pin Select

P = Power I = Input

#### 7.3 **Interrupt Control Registers**

#### **TABLE 7-3:** INTERRUPT REGISTER MAP

| ress<br>()                  |                                 | e         |                      |               |             |                 |                       |                         |                       | B                     | its                   |                        |                        |                        |          |                         |                         |                        | s          |

|-----------------------------|---------------------------------|-----------|----------------------|---------------|-------------|-----------------|-----------------------|-------------------------|-----------------------|-----------------------|-----------------------|------------------------|------------------------|------------------------|----------|-------------------------|-------------------------|------------------------|------------|

| Virtual Address<br>(BF81_#) | Register<br>Name <sup>(1)</sup> | Bit Range | 31/15                | 30/14         | 29/13       | 28/12           | 27/11                 | 26/10                   | 25/9                  | 24/8                  | 23/7                  | 22/6                   | 21/5                   | 20/4                   | 19/3     | 18/2                    | 17/1                    | 16/0                   | All Resets |

|                             |                                 | 31:16     |                      |               |             | NMIK            | EY<7:0>               |                         |                       |                       | —                     | —                      | _                      | _                      | _        | _                       | —                       | _                      | 0000       |

| 0000                        | INTCON                          | 15:0      | _                    | _             | _           | MVEC            | _                     |                         | TPC<2:0>              |                       | —                     | _                      | _                      | INT4EP                 | INT3EP   | INT2EP                  | INT1EP                  | INT0EP                 | 0000       |

| 0010                        |                                 | 31:16     |                      | PRI7S         | S<3:0>      |                 |                       | PRI6SS<3:0>             |                       |                       |                       | PRI5S                  | S<3:0>                 |                        |          | PRI4S                   | S<3:0>                  |                        | 0000       |

| 0010                        | PRISS                           | 15:0      |                      | PRI3SS        | S<3:0>      |                 |                       | PRI2SS                  | 8<3:0>                |                       |                       | PRI1S                  | S<3:0>                 |                        | _        | -                       | —                       | SS0                    | 0000       |

| 0020                        | INTSTAT                         | 31:16     | _                    |               | _           | _               |                       | -                       |                       | _                     | _                     | _                      |                        | _                      | _        |                         | _                       | —                      | 0000       |

| 0020                        |                                 | 15:0      | _                    | _             | —           | —               | _                     |                         | SRIPL<2:0>            |                       |                       |                        |                        | SIR                    | Q<7:0>   |                         |                         |                        | 0000       |

| 0030                        | IPTMR                           | 31:16     |                      |               |             |                 |                       |                         |                       | IPTMR                 | <31.0>                |                        |                        |                        |          |                         |                         |                        | 0000       |

| 0000                        |                                 | 15:0      |                      |               |             |                 |                       |                         |                       |                       |                       |                        |                        | 1                      |          |                         |                         | T                      | 0000       |

| 0040                        | IFS0                            | 31:16     | OC6IF                | IC6IF         | IC6EIF      | T6IF            | OC5IF                 | IC5IF                   | IC5EIF                | T5IF                  | INT4IF                | OC4IF                  | IC4IF                  | IC4EIF                 | T4IF     | INT3IF                  | OC3IF                   | IC3IF                  | 0000       |

| 00.0                        |                                 | 15:0      | IC3EIF               | T3IF          | INT2IF      | OC2IF           | IC2IF                 | IC2EIF                  | T2IF                  | INT1IF                | OC1IF                 | IC1IF                  | IC1EIF                 | T1IF                   | INT0IF   | CS1IF                   | CS0IF                   | CTIF                   | 0000       |

| 0050                        | IFS1                            | 31:16     | ADCD4IF              | ADCD3IF       | ADCD2IF     | ADCD1IF         | ADCD0IF               | ADCFLTIF                | ADCDF6IF              | ADCDF5IF              | ADCDF4IF              | ADCDF3IF               | ADCDF2IF               | ADCDF1IF               | ADCDC6IF | ADCDC5IF                | ADCDC4IF                | ADCDC3IF               |            |

|                             |                                 | 15:0      | ADCDC2IF             |               | ADCFIFOIF   | ADCIF           | OC9IF                 | IC9IF                   | IC9EIF                | T9IF                  | OC8IF                 | IC8IF                  | IC8EIF                 | T8IF                   | OC7IF    | IC7IF                   | IC7EIF                  | T7IF                   | 0000       |

| 0060                        | IFS2 <sup>(5)</sup>             | 31:16     | ADCD36IF             | ADCD35IF      | ADCD34IF    | ADCD33IF        | ADCD32IF              | ADCD31IF                | ADCD30IF              | ADCD29IF              | ADCD28IF              | ADCD27IF               | ADCD26IF               | ADCD25IF               | ADCD24IF | ADCD23IF                | ADCD22IF                | ADCD21IF               | -          |

|                             |                                 | 15:0      | ADCD20IF             | ADCD19IF      | ADCD18IF    | ADCD17IF        | ADCD16IF              | ADCD15IF                | ADCD14IF              | ADCD13IF              | ADCD12IF              | ADCD11IF               | ADCD10IF               | ADCD9IF                | ADCD8IF  | ADCD7IF                 | ADCD6IF                 | ADCD5IF                | 0000       |

| 0070                        | IFS3 <sup>(6)</sup>             | 31:16     | CNKIF <sup>(8)</sup> | CNJIF         | CNHIF       | CNGIF           | CNFIF                 | CNEIF                   | CNDIF                 | CNCIF                 | CNBIF                 | CNAIF                  | I2C1MIF                | I2C1SIF                | I2C1BIF  | U1TXIF                  | U1RXIF                  | U1EIF                  | 0000       |

|                             |                                 | 15:0      | SPI1TXIF             | SPI1RXIF      | SPI1EIF     | —               | CRPTIF <sup>(7)</sup> | SBIF                    | CFDCIF                | CPCIF                 | ADCD44IF              | ADCD43IF               | ADCD42IF               | ADCD41IF               | ADCD40IF | ADCD39IF                | ADCD38IF                | ADCD37IF               |            |

| 0080                        | IFS4                            | 31:16     | <b>U3TXIF</b>        | U3RXIF        | U3EIF       | <b>SPI3TXIF</b> | <b>SPI3RXIF</b>       | SPI3EIF                 | ETHIF                 | CAN2IF <sup>(3)</sup> | CAN1IF <sup>(3)</sup> | I2C2MIF <sup>(2)</sup> | 12C2SIF <sup>(2)</sup> | I2C2BIF <sup>(2)</sup> | U2TXIF   | U2RXIF                  | U2EIF                   | SPI2TXIF               | 0000       |

|                             |                                 | 15:0      | SPI2RXIF             | SPI2EIF       | DMA7IF      | DMA6IF          | DMA5IF                | DMA4IF                  | DMA3IF                | DMA2IF                | DMA1IF                | DMA0IF                 | USBDMAIF               | USBIF                  | CMP2IF   | CMP1IF                  | PMPEIF                  | PMPIF                  | 0000       |

| 0090                        | IFS5                            | 31:16     | —                    | U6TXIF        | U6RXIF      | U6EIF           | SPI6TX <sup>(2)</sup> | SPI6RXIF <sup>(2)</sup> | SPI6IF <sup>(2)</sup> | I2C5MIF               | I2C5SIF               | I2C5BIF                | U5TXIF                 | U5RXIF                 | U5EIF    | SPI5TXIF <sup>(2)</sup> | SPI5RXIF <sup>(2)</sup> | SPI5EIF <sup>(2)</sup> |            |

|                             |                                 | 15:0      | I2C4MIF              | I2C4SIF       | I2C4BIF     | U4TXIF          | U4RXIF                | U4EIF                   | SQI1IF                | PREIF                 | FCEIF                 | RTCCIF                 | SPI4TXIF               | SPI4RXIF               | SPI4EIF  | I2C3MIF                 | I2C3SIF                 | I2C3BIF                | 0000       |

| 00A0                        | IFS6                            | 31:16     | _                    | -             | _           | _               | _                     | -                       | _                     | _                     |                       | _                      | ADC7WIF                | _                      | —        | ADC4WIF                 | ADC3WIF                 |                        | 0000       |

|                             |                                 | 15:0      | ADC1WIF              | ADC0WIF       | ADC7EIF     | —               | _                     | ADC4EIF                 | ADC3EIF               | ADC2EIF               | ADC1EIF               | ADC0EIF                | -                      | ADCGRPIF               | —        | ADCURDYIF               |                         | ADCEOSIF               | _          |

| 00C0                        | IEC0                            | 31:16     | OC6IE                | IC6IE         | IC6EIE      | T6IE            | OC5IE                 | IC5IE                   | IC5EIE                | T5IE                  | INT4IE                | OC4IE                  | IC4IE                  | IC4EIE                 | T4IE     | INT3IE                  | OC3IE                   | IC3IE                  | 0000       |

|                             |                                 | 15:0      | IC3EIE               | T3IE          | INT2IE      | OC2IE           | IC2IE                 | IC2EIE                  | T2IE                  | INT1IE                | OC1IE                 | IC1IE                  | IC1EIE                 | T1IE                   | INTOIE   | CS1IE                   | CS0IE                   | CTIE                   | 0000       |

| 00D0                        | IEC1                            | 31:16     | ADCD4IE              | ADCD3IE       | ADCD2IE     | ADCD1IE         | ADCD0IE               | ADCFLTIE                | ADCDF6IE              | ADCDF5IE              | ADCDF4IE              | ADCDF3IE               | ADCDF2IE               | ADCDF1IE               | ADCDC6IE | ADCDC5IE                | ADCDC4IE                | ADCDC3IE               | -          |

|                             |                                 | 15:0      | ADCDC2IE             |               | ADCFIFOIE   | ADCIE           | OC9IE                 | IC9IE                   | IC9EIE                | T9IE                  | OC8IE                 | IC8IE                  | IC8EIE                 | T8IE                   | OC7IE    | IC7IE                   | IC7EIE                  | T7IE                   | 0000       |

| 00E0                        | IEC2 <sup>(5)</sup>             | 31:16     |                      |               | ADCD34IE    | ADCD33IE        | ADCD32IE              | ADCD31IE                | ADCD30IE              | ADCD29IE              | ADCD28IE              | ADCD27IE               | ADCD26IE               | ADCD25IE               | ADCD24IE | ADCD23IE                | ADCD22IE                | ADCD21IE               |            |

|                             |                                 |           | ADCD20IE             | ADCD19IE      | ADCD18IE    | ADCD17IE        | ADCD16IE              | ADCD15IE                | ADCD14IE              | ADCD13IE              | ADCD12IE              | ADCD11IE               | ADCD10IE               | ADCD9IE                | ADCD8IE  | ADCD7IE                 | ADCD6IE                 | ADCD5IE                | 0000       |

| Legei                       | nd: x =                         | unknow    | n value on R         | teset; — = ur | nimplemente | d, read as '0'  | . Reset values        | s are shown ir          | n hexadecima          | l.                    |                       |                        |                        |                        |          |                         |                         |                        |            |

All registers in this table with the exception of the OFFx registers, have corresponding CLR, SET, and INV registers at their virtual addresses, plus offsets of 0x4, 0x8 and 0xC, respectively. See Section 12.3 "CLR, SET, and INV Note 1: Registers" for more information.

This bit or register is not available on 64-pin devices. 2:

3: This bit or register is not available on devices without a CAN module. This bit or register is not available on 100-pin devices.

4:

Bits 31 and 30 are not available on 64-pin and 100-pin devices; bits 29 through 14 are not available on 64-pin devices. 5:

Bits 31, 30, 29, and bits 5 through 0 are not available on 64-pin and 100-pin devices; bit 31 is not available on 124-pin devices; bit 22 is not available on 64-pin devices. This bit or register is not available on devices without a Crypto module. 6: 7:

8: This bit or register is not available on 124-pin devices.

## REGISTER 10-4: DCRCCON: DMA CRC CONTROL REGISTER (CONTINUED)

- bit 6 **CRCAPP:** CRC Append Mode bit<sup>(1)</sup>

- 1 = The DMA transfers data from the source into the CRC but NOT to the destination. When a block transfer completes the DMA writes the calculated CRC value to the location given by CHxDSA

- 0 = The DMA transfers data from the source through the CRC obeying WBO as it writes the data to the destination

- bit 5 CRCTYP: CRC Type Selection bit

- 1 = The CRC module will calculate an IP header checksum

- 0 = The CRC module will calculate a LFSR CRC

- bit 4-3 Unimplemented: Read as '0'

- bit 2-0 CRCCH<2:0>: CRC Channel Select bits

- 111 = CRC is assigned to Channel 7

- 110 = CRC is assigned to Channel 6

- 101 = CRC is assigned to Channel 5

- 100 = CRC is assigned to Channel 4

- 011 = CRC is assigned to Channel 3

- 010 = CRC is assigned to Channel 2

- 001 = CRC is assigned to Channel 1

- 000 = CRC is assigned to Channel 0

- **Note 1:** When WBO = 1, unaligned transfers are not supported and the CRCAPP bit cannot be set.

| ŝ                           |                  |               |                                                           |                                 |         |       |                     |        |          |        | Bits                   |            |          |          |                       |          |         |        |            |

|-----------------------------|------------------|---------------|-----------------------------------------------------------|---------------------------------|---------|-------|---------------------|--------|----------|--------|------------------------|------------|----------|----------|-----------------------|----------|---------|--------|------------|

| Virtual Address<br>(BF8E_#) | Register<br>Name | Bit Range     | 31/15                                                     | 30/14                           | 29/13   | 28/12 | 27/11               | 26/10  | 25/9     | 24/8   | 23/7                   | 22/6       | 21/5     | 20/4     | 19/3                  | 18/2     | 17/1    | 16/0   | All Resets |

| 3028                        | USB              | 31:16         |                                                           |                                 |         |       |                     |        |          |        | ATA<31:16>             |            |          |          |                       |          |         |        | 00         |

| 020                         | FIFO2            | 15:0          |                                                           |                                 |         |       |                     |        |          |        | ATA<15:0>              |            |          |          |                       |          |         |        | 00         |

| 02C                         | USB<br>FIFO3     | 31:16         |                                                           |                                 |         |       |                     |        |          |        | ATA<31:16>             |            |          |          |                       |          |         |        | 00         |

|                             |                  | 15:0          |                                                           |                                 |         |       |                     |        |          |        | ATA<15:0>              |            |          |          |                       |          |         |        | 00         |

| 8030                        | USB<br>FIFO4     | 31:16<br>15:0 |                                                           | DATA<31:16> 00<br>DATA<15:0> 00 |         |       |                     |        |          |        |                        |            |          |          |                       |          |         |        |            |

|                             | USB              | 31:16         |                                                           | DATA<15:0> 00<br>DATA<31:16> 00 |         |       |                     |        |          |        |                        |            |          |          |                       |          |         |        |            |

| 3034                        | FIFO5            | 15:0          |                                                           |                                 |         |       |                     |        |          |        | ATA<15:0>              |            |          |          |                       |          |         |        | 00         |

|                             | USB              | 31:16         |                                                           |                                 |         |       |                     |        |          |        | ATA<31:16>             |            |          |          |                       |          |         |        | 00         |

| 3038                        | FIFO6            | 15:0          |                                                           |                                 |         |       |                     |        |          |        | ATA<15:0>              |            |          |          |                       |          |         |        | 00         |

|                             | USB              | 31:16         |                                                           |                                 |         |       |                     |        |          | D      | ATA<31:16>             |            |          |          |                       |          |         |        | 0(         |

| 03C                         | FIF07            | 15:0          |                                                           |                                 |         |       |                     |        |          | D      | ATA<15:0>              |            |          |          |                       |          |         |        | 00         |

|                             | USBOTO           | 31:16         | _                                                         | _                               | _       | RXDPB |                     | RXFIFC | )SZ<3:0> |        | _                      | _          | _        | TXDPB    |                       | TXFIFOSZ | <3:0>   |        | 0 (        |

| 8060                        | USBOTG           | 15:0          | _                                                         | _                               | -       | —     | _                   | _      | TXEDMA   | RXEDMA | BDEV                   | FSDEV      | LSDEV    | VBUS     | <1:0>                 | HOSTMODE | HOSTREQ | SESSIO | N 00       |

| 8064                        | USB              | 31:16         |                                                           |                                 |         |       |                     |        |          |        |                        |            |          |          |                       |          |         |        |            |

| 004                         | FIFOA            | 15:0          | —                                                         | -                               | —       |       |                     |        |          |        |                        | TXFIFOAD<1 | 2:0>     |          |                       |          |         |        | 00         |

| 806C                        | USB              | 31:16         | —                                                         |                                 | —       | _     | _                   | _      | —        | —      | —                      | _          | _        | —        | _                     | _        | —       | —      | 00         |

|                             | HWVER            | 15:0          | RC         VERMAJOR<4:0>         VERMINOR<9:0>         08 |                                 |         |       |                     |        |          |        |                        |            |          |          |                       |          |         |        |            |

| 3078                        | USB              | 31:16         |                                                           |                                 |         | VPLEN | l<7:0>              |        |          |        |                        |            | DN<3:0>  |          |                       | WTID<3   |         |        | 30         |

|                             | INFO             | 15:0          |                                                           | DMACHAN                         | IS<3:0> |       |                     | RAMBI  | TS<3:0>  | · · ·  |                        | RXEND      | PTS<3:0> |          |                       | TXENDPTS | <3:0>   |        | 8C         |

| 307C                        | USB<br>EOFRST    | 31:16         | —                                                         | _                               | _       | -     |                     | -      | NRSTX    | NRST   |                        |            |          | LSEOF<7: |                       |          |         |        | 00         |

|                             |                  | 15:0          |                                                           |                                 |         | FSEOF | -<7:0><br>(HUBPRT<6 |        |          |        |                        |            |          | HSEOF<7: |                       |          |         |        | 77         |

| 3080                        | USB<br>E0TXA     | 31:16<br>15:0 |                                                           |                                 | _       |       |                     | >      | _        | _      | MULTTRAN               |            |          |          | BADD<6:0><br>DDR<6:0> |          |         |        | 00         |

|                             |                  | 31:16         |                                                           | _                               | _       |       | HUBPRT<6            |        | _        | _      | —<br>MULTTRAN          |            |          |          | BADD<6:0>             |          |         |        | 00         |

| 3084                        | USB<br>E0RXA     | 15:0          |                                                           |                                 | _       |       |                     |        | _        | _      |                        | _          | _        | _        |                       | _        | _       | _      | 00         |

|                             | USB              | 31:16         | _                                                         |                                 |         | ТХ    | HUBPRT<6            | :0>    |          |        | MULTTRAN               |            |          | TXHU     | BADD<6:0>             |          |         |        | 0.0        |

| 3088                        | E1TXA            | 15:0          | _                                                         | _                               | _       | _     | _                   | _      | _        | _      | _                      |            |          |          | DDR<6:0>              |          |         |        | 0.0        |

|                             | USB              | 31:16         | _                                                         |                                 |         | RX    | HUBPRT<6            | 6:0>   |          |        | MULTTRAN               |            |          | RXHU     | BADD<6:0>             |          |         |        | 00         |

| 08C                         | E1RXA            | 15:0          | _                                                         |                                 | _       |       | _                   | _      | _        | _      | _                      |            |          | RXFA     | DDR<6:0>              |          |         |        | 0.0        |

| 0000                        | USB              | 31:16         | _                                                         |                                 | •       | ТХ    | HUBPRT<6            | :0>    |          |        | MULTTRAN               |            |          | TXHU     | BADD<6:0>             |          |         |        | 0.0        |

| 3090                        | E2TXA            | 15:0          | _                                                         | _                               | _       | _     | —                   | —      | _        | —      |                        |            |          | TXFA     | DDR<6:0>              |          |         |        | 0.0        |

| 3094                        | USB              | 31:16         | —                                                         |                                 |         | RX    | (HUBPRT<6           | 6:0>   |          |        | MULTTRAN RXHUBADD<6:0> |            |          |          |                       | 00       |         |        |            |

| -034                        | E2RXA            | 15:0          | —                                                         |                                 | _       | —     | —                   | -      | —        | _      | _                      |            |          |          | DDR<6:0>              |          |         |        | 00         |

| 3098                        | USB              | 31:16         | _                                                         |                                 |         | ТХ    | HUBPRT<6            | :0>    |          |        | MULTTRAN               |            |          |          | BADD<6:0>             |          |         |        | 00         |

|                             | E3TXA            | 15:0          | _                                                         | _                               | _       | _     |                     | _      | _        |        |                        |            |          | TXFA     | DDR<6:0>              |          |         |        | 00         |

#### TABLE 11-1: USB REGISTER MAP 1 (CONTINUED)

#### REGISTER 11-9: USBIENCSR1: USB INDEXED ENDPOINT CONTROL STATUS REGISTER 1 (ENDPOINT 1-7) (CONTINUED)

#### bit 18 **OVERRUN:** Data Overrun Status bit (*Device mode*)

- 1 = An OUT packet cannot be loaded into the RX FIFO.

- 0 = Written by software to clear this bit

This bit is only valid when the endpoint is operating in ISO mode. In Bulk mode, it always returns zero.

ERROR: No Data Packet Received Status bit (Host mode)

- 1 = Three attempts have been made to receive a packet and no data packet has been received. An interrupt is generated.

- 0 = Written by the software to clear this bit.

This bit is only valid when the RX endpoint is operating in Bulk or Interrupt mode. In ISO mode, it always returns zero.

- bit 17 FIFOFULL: FIFO Full Status bit

- 1 = No more packets can be loaded into the RX FIFO

- 0 = The RX FIFO has at least one free space

- bit 16 RXPKTRDY: Data Packet Reception Status bit

- 1 = A data packet has been received. An interrupt is generated.

- 0 = Written by software to clear this bit when the packet has been unloaded from the RX FIFO.

- bit 15-11 MULT<4:0>: Multiplier Control bits

For Isochronous/Interrupt endpoints or of packet splitting on Bulk endpoints, multiplies TXMAXP by MULT+1 for the payload size.

For Bulk endpoints, MULT can be up to 32 and defines the number of "USB" packets of the specified payload into which a single data packet placed in the FIFO should be split, prior to transfer. The data packet is required to be an exact multiple of the payload specified by TXMAXP.

For Isochronous/Interrupts endpoints operating in Hi-Speed mode, MULT may be either 2 or 3 and specifies the maximum number of such transactions that can take place in a single microframe.

#### bit 10-0 RXMAXP<10:0>: Maximum RX Payload Per Transaction Control bits

This field sets the maximum payload (in bytes) transmitted in a single transaction. The value is subject to the constraints placed by the USB Specification on packet sizes for Bulk, Interrupt and Isochronous transfers in Full-Speed and Hi-Speed operations.

RXMAXP must be set to an even number of bytes for proper interrupt generation in DMA Mode 1.

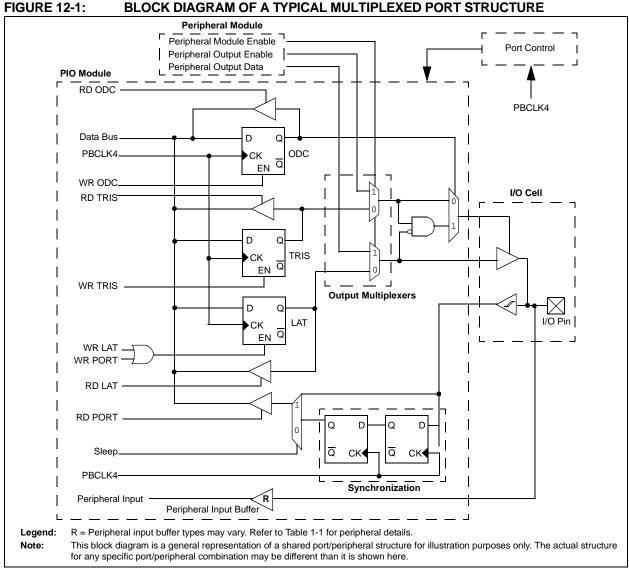

#### 12.0 I/O PORTS

Note: This data sheet summarizes the features of the PIC32MZ EF family of devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to Section 12. "I/O Ports" (DS60001120) in the "PIC32 Family Reference Manual", which is available from the Microchip web site (www.microchip.com/PIC32).

General purpose I/O pins are the simplest of peripherals. They allow the PIC32MZ EF family device to monitor and control other devices. To add flexibility and functionality, some pins are multiplexed with alternate function(s). These functions depend on which peripheral features are on the device. In general, when a peripheral is functioning, that pin may not be used as a general purpose I/O pin.

Some of the key features of the I/O ports are:

- Individual output pin open-drain enable/disable

- Individual input pin weak pull-up and pull-down

- · Monitor selective inputs and generate interrupt when change in pin state is detected

- · Operation during Sleep and Idle modes

- · Fast bit manipulation using CLR, SET and INV registers

Figure 12-1 illustrates a block diagram of a typical multiplexed I/O port.

BLOCK DIAGRAM OF A TYPICAL MULTIPLEXED PORT STRUCTURE

# 12.2 Registers for Slew Rate Control

Some I/O pins can be configured for various types of slew rate control on its associated port. This is controlled by the Slew Rate Control bits in the SRCON1x and SRCON0x registers that are associated with each I/O port. The slew rate control is configured using the corresponding bit in each register, as shown in Table 12-1.

As an example, writing 0x0001, 0x0000 to SRCON1A and SRCON0A, respectively, will enable slew rate control on the RA0 pin and sets the slew rate to the slow edge rate.

| SRCON1x | SRCON0x | Description                                                             |  |  |  |  |  |  |  |  |  |

|---------|---------|-------------------------------------------------------------------------|--|--|--|--|--|--|--|--|--|

| 1       | 1       | Slew rate control is enabled<br>and is set to the slowest<br>edge rate. |  |  |  |  |  |  |  |  |  |

| 1       | 0       | Slew rate control is enabled<br>and is set to the slow edge<br>rate.    |  |  |  |  |  |  |  |  |  |

| 0       | 1       | Slew rate control is enabled<br>and is set to the medium<br>edge rate.  |  |  |  |  |  |  |  |  |  |

| 0       | 0       | Slew rate control is disabled and is set to the fastest                 |  |  |  |  |  |  |  |  |  |

TABLE 12-1: SLEW RATE CONTROL BIT SETTINGS

**Note:** By default, all of the Port pins are set to the fastest edge rate.

edge rate.

# 12.3 CLR, SET, and INV Registers

Every I/O module register has a corresponding CLR (clear), SET (set) and INV (invert) register designed to provide fast atomic bit manipulations. As the name of the register implies, a value written to a SET, CLR or INV register effectively performs the implied operation, but only on the corresponding base register and only bits specified as '1' are modified. Bits specified as '0' are not modified.

Reading SET, CLR and INV registers returns undefined values. To see the affects of a write operation to a SET, CLR or INV register, the base register must be read.

# 12.4 Peripheral Pin Select (PPS)

A major challenge in general purpose devices is providing the largest possible set of peripheral features while minimizing the conflict of features on I/O pins. The challenge is even greater on low pin-count devices. In an application where more than one peripheral needs to be assigned to a single pin, inconvenient workarounds in application code or a complete redesign may be the only option. PPS configuration provides an alternative to these choices by enabling peripheral set selection and their placement on a wide range of I/O pins. By increasing the pinout options available on a particular device, users can better tailor the device to their entire application, rather than trimming the application to fit the device.

The PPS configuration feature operates over a fixed subset of digital I/O pins. Users may independently map the input and/or output of most digital peripherals to these I/O pins. PPS is performed in software and generally does not require the device to be reprogrammed. Hardware safeguards are included that prevent accidental or spurious changes to the peripheral mapping once it has been established.

#### 12.4.1 AVAILABLE PINS

The number of available pins is dependent on the particular device and its pin count. Pins that support the PPS feature include the designation "RPn" in their full pin designation, where "RP" designates a remappable peripheral and "n" is the remappable port number.

## 12.4.2 AVAILABLE PERIPHERALS

The peripherals managed by the PPS are all digitalonly peripherals. These include general serial communications (UART, SPI, and CAN), general purpose timer clock inputs, timer-related peripherals (input capture and output compare), interrupt-on-change inputs, and reference clocks (input and output).

In comparison, some digital-only peripheral modules are never included in the PPS feature. This is because the peripheral's function requires special I/O circuitry on a specific port and cannot be easily connected to multiple pins. These modules include I<sup>2</sup>C among others. A similar requirement excludes all modules with analog inputs, such as the Analog-to-Digital Converter (ADC).

A key difference between remappable and non-remappable peripherals is that remappable peripherals are not associated with a default I/O pin. The peripheral must always be assigned to a specific I/O pin before it can be used. In contrast, non-remappable peripherals are always available on a default pin, assuming that the peripheral is active and not conflicting with another peripheral.

When a remappable peripheral is active on a given I/O pin, it takes priority over all other digital I/O and digital communication peripherals associated with the pin. Priority is given regardless of the type of peripheral that is mapped. Remappable peripherals never take priority over any analog functions associated with the pin. NOTES:

| REGISTER 20-13: | SQI1STAT2: SQI STATUS REGISTER 2 |

|-----------------|----------------------------------|

|-----------------|----------------------------------|

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|

| 31:24        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 31.24        | _                 | _                 | _                 | _                 | _                 | _                 | _                | —                |

| 00.40        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | R-0              | R-0              |