Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFI

| Product Status             | Active                                                                           |

|----------------------------|----------------------------------------------------------------------------------|

| Core Processor             | MIPS32® M-Class                                                                  |

| Core Size                  | 32-Bit Single-Core                                                               |

| Speed                      | 200MHz                                                                           |

| Connectivity               | CANbus, Ethernet, I <sup>2</sup> C, PMP, SPI, SQI, UART/USART, USB OTG           |

| Peripherals                | Brown-out Detect/Reset, DMA, I <sup>2</sup> S, POR, PWM, WDT                     |

| Number of I/O              | 46                                                                               |

| Program Memory Size        | 1MB (1M x 8)                                                                     |

| Program Memory Type        | FLASH                                                                            |

| EEPROM Size                | -                                                                                |

| RAM Size                   | 256K x 8                                                                         |

| Voltage - Supply (Vcc/Vdd) | 2.1V ~ 3.6V                                                                      |

| Data Converters            | A/D 24x12b                                                                       |

| Oscillator Type            | Internal                                                                         |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                                |

| Mounting Type              | Surface Mount                                                                    |

| Package / Case             | 64-TQFP                                                                          |

| Supplier Device Package    | 64-TQFP (10x10)                                                                  |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic32mz1024eff064-i-pt |

|                            |                                                                                  |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

|          |                        | Pin Nu          | mber            |                          |             |                |                                   |

|----------|------------------------|-----------------|-----------------|--------------------------|-------------|----------------|-----------------------------------|

| Pin Name | 64-pin<br>QFN/<br>TQFP | 100-pin<br>TQFP | 124-pin<br>VTLA | 144-pin<br>TQFP/<br>LQFP | Pin<br>Type | Buffer<br>Type | Description                       |

|          |                        |                 |                 |                          | PO          | RTK            |                                   |

| RK0      | —                      | _               | _               | 19                       | I/O         | ST             | PORTK is a bidirectional I/O port |

| RK1      | _                      | —               |                 | 51                       | I/O         | ST             |                                   |

| RK2      | —                      | _               |                 | 52                       | I/O         | ST             |                                   |

| RK3      | —                      | _               |                 | 53                       | I/O         | ST             |                                   |

| RK4      | _                      | —               |                 | 92                       | I/O         | ST             |                                   |

| RK5      | _                      | —               |                 | 93                       | I/O         | ST             |                                   |

| RK6      | —                      | —               |                 | 94                       | I/O         | ST             | ]                                 |

| RK7      | —                      | —               | —               | 126                      | I/O         | ST             | ]                                 |

| Legend:  | CMOS = C               | MOS-comp        | atible input    | t or output              |             | Analog =       | Analog input P = Power            |

## TABLE 1-6: PORTA THROUGH PORTK PINOUT I/O DESCRIPTIONS (CONTINUED)

d: CMOS = CMOS-compatible input or output ST = Schmitt Trigger input with CMOS levels TTL = Transistor-transistor Logic input buffer Analog = Analog input O = Output PPS = Peripheral Pin Select P = Power I = Input

i – mput

| 1            |                   |                   |                   |                   |                   |                   |                  |                  |  |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|--|

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |  |

| 31:24        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |  |

| 31.24        | —                 | —                 | —                 | —                 | —                 |                   |                  | —                |  |

|              | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | R/W-x            | R/W-x            |  |

| 23:16        |                   |                   |                   | —                 | _                 | _                 | CAUS             | E<5:4>           |  |

|              | —                 | _                 | _                 |                   |                   |                   | E                | V                |  |

|              | R/W-x             | R/W-x             | R/W-x             | U-0               | U-0               | U-0               | U-0              | U-0              |  |

| 15:8         |                   | CAUSE             | <3:0>             |                   |                   |                   |                  |                  |  |

|              | Z                 | 0                 | U                 | I                 |                   | _                 | _                | _                |  |

|              | U-0               | R/W-x             | R/W-x             | R/W-x             | R/W-x             | R/W-x             | U-0              | U-0              |  |

| 7:0          |                   |                   |                   | FLAGS<4:0>        |                   |                   |                  |                  |  |

|              |                   | V                 | Z                 | 0                 | U                 | I                 |                  | _                |  |

### REGISTER 3-8: FEXR: FLOATING POINT EXCEPTIONS STATUS REGISTER; CP1 REGISTER 26

| Legend:           |                  |                          |                    |

|-------------------|------------------|--------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, I | read as '0'        |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared     | x = Bit is unknown |

### bit 31-18 Unimplemented: Read as '0'

bit 17-12 **CAUSE<5:0>:** FPU Exception Cause bits These bits indicated the exception conditions that arise during execution of an FPU arithmetic instruction.

- bit 17 E: Unimplemented Operation bit

- bit 16 V: Invalid Operation bit

- bit 15 **Z:** Divide-by-Zero bit

- bit 14 **O:** Overflow bit

- bit 13 **U:** Underflow bit

- bit 12 I: Inexact bit

- bit 11-7 Unimplemented: Read as '0'

- bit 6-2 FLAGS<4:0>: FPU Flags bits

These bits show any exception conditions that have occurred for completed instructions since the flag was last reset by software.

- bit 6 V: Invalid Operation bit

- bit 4 **Z:** Divide-by-Zero bit

- bit 4 O: Overflow bit

- bit 3 U: Underflow bit

- bit 2 I: Inexact bit

- bit 1-0 Unimplemented: Read as '0'

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |  |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|--|

| 04-04        | R/W-x             | R/W-x             | R/W-x             | R/W-x             | R/W-x             | R/W-x             | R/W-x            | R/W-x            |  |

| 31:24        |                   |                   |                   | FCC<7:1>          |                   |                   |                  | FS               |  |

| 00.40        | R/W-x             | R/W-x             | R/W-x             | R-0               | R-1               | R-1               | R/W-x            | R/W-x            |  |

| 23:16        | FCC<0>            | FO                | FN                | MAC2008           | ABS2008           | NAN2008           | CAUSE<5:4>       |                  |  |

|              | R/W-x             | R/W-x             | R/W-x             | R/W-x             | R/W-x             | R/W-x             | R/W-x            | R/W-x            |  |

| 15:8         |                   | CAUSE             | .2.0.             |                   | S<4:1>            |                   |                  |                  |  |

|              |                   | CAUSE             | <3.0>             | V                 | Z                 | 0                 | U                |                  |  |

|              | R/W-x             | R/W-x             | R/W-x             | R/W-x             | R/W-x             | R/W-x             | R/W-x            | R/W-x            |  |

| 7:0          | ENABLES<0>        |                   |                   | FLAGS<4:0>        |                   | -1.0              |                  |                  |  |

|              | I                 | V                 | Z                 | U                 |                   | RM<1:0>           |                  |                  |  |

### REGISTER 3-10: FCSR: FLOATING POINT CONTROL AND STATUS REGISTER; CP1 REGISTER 31

| Legend:           |                  |                        |                    |

|-------------------|------------------|------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, | read as '0'        |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared   | x = Bit is unknown |

### bit 31-25 FCC<7:1>: Floating Point Condition Code bits

These bits record the results of floating point compares and are tested for floating point conditional branches and conditional moves.

### bit 24 **FS:** Flush to Zero control bit

1 = Denormal input operands are flushed to zero. Tiny results are flushed to either zero or the applied format's smallest normalized number (MinNorm) depending on the rounding mode settings.

0 = Denormal input operands result in an Unimplemented Operation exception.

### bit 23 FCC<0>: Floating Point Condition Code bits

These bits record the results of floating point compares and are tested for floating point conditional branches and conditional moves.

- bit 22 **FO:** Flush Override Control bit

- 1 = The intermediate result is kept in an internal format, which can be perceived as having the usual mantissa precision but with unlimited exponent precision and without forcing to a specific value or taking an exception.

- 0 = Handling of Tiny Result values depends on setting of the FS bit.

### bit 21 FN: Flush to Nearest Control bit

- 1 = Final result is rounded to either zero or 2E\_min (MinNorm), whichever is closest when in Round to Nearest (RN) rounding mode. For other rounding modes, a final result is given as if FS was set to 1.

0 = Handling of Tiny Result values depends on setting of the FS bit.

- bit 20 MAC2008: Fused Multiply Add mode control bit

- 0 = Unfused multiply-add. Intermediary multiplication results are rounded to the destination format.

- bit 19 ABS2008: Absolute value format control bit

- 1 = ABS.fmt and NEG.fmt instructions compliant with IEEE Standard 754-2008. The ABS and NEG functions accept QNAN inputs without trapping.

- bit 18 NAN2008: NaN Encoding control bit

- 1 = Quiet and signaling NaN encodings recommended by the IEEE Standard 754-2008. A quiet NaN is encoded with the first bit of the fraction being 1 and a signaling NaN is encoded with the first bit of the fraction being 0.

### bit 17-12 CAUSE<5:0>: FPU Exception Cause bits

These bits indicated the exception conditions that arise during execution of an FPU arithmetic instruction.

bit 17 E: Unimplemented Operation bit

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|

| 04.04        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 31:24        | —                 | —                 | —                 | —                 | —                 | —                 | —                | —                |

| 00.40        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 23:16        | —                 | —                 | —                 | —                 |                   | —                 | —                | —                |

| 45.0         | U-0               | U-0               | R-0               | R-0               | R-0               | R-0               | R-0              | R-0              |

| 15:8         | —                 | —                 | T13PGV            | T12PGV            | T11PGV            | T10PGV            | T9PGV            | T8PGV            |

| 7.0          | R-0               | R-0               | R-0               | R-0               | R-0               | R-0               | R-0              | R-0              |

| 7:0          | T7PGV             | T6PGV             | T5PGV             | T4PGV             | T3PGV             | T2PGV             | T1PGV            | T0PGV            |

### REGISTER 4-2: SBFLAG: SYSTEM BUS STATUS FLAG REGISTER

## Legend:

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, read as '0' |

|-------------------|------------------|------------------------------------|

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared               |

bit 31-14 Unimplemented: Read as '0'

bit 13-0 **TxPGV:** Target 'x' Permission Group Violation Status bits ('x' = 0-13)

Refer to Table 4-6 for the list of available targets and their descriptions.

- 1 = Target is reporting a Permission Group (PG) violation

- 0 = Target is not reporting a PG violation

Note: All errors are cleared at the source (i.e., SBTxELOG1, SBTxELOG2, SBTxECLRS, or SBTxECLRM registers).

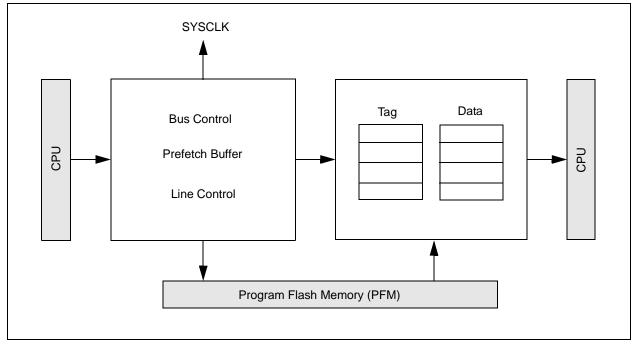

# 9.0 PREFETCH MODULE

Note: This data sheet summarizes the features of the PIC32MZ EF family of devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to Section 41. "Prefetch Module for Devices with L1 CPU Cache" (DS60001183) in the "PIC32 Family Reference Manual", which is available from the Microchip web site (www.microchip.com/PIC32).

The Prefetch module is a performance enhancing module that is included in the PIC32MZ EF family of devices. When running at high-clock rates, Wait states must be inserted into Program Flash Memory (PFM) read transactions to meet the access time of the PFM. Wait states can be hidden to the core by prefetching and storing instructions in a temporary holding area that the CPU can access quickly. Although the data path to the CPU is 32 bits wide, the data path to the PFM is 128 bits wide. This wide data path provides the same bandwidth to the CPU as a 32-bit path running at four times the frequency.

The Prefetch module holds a subset of PFM in temporary holding spaces known as lines. Each line contains a tag and data field. Normally, the lines hold a copy of what is currently in memory to make instructions or data available to the CPU without Flash Wait states.

The following are key features of the Prefetch module:

- 4x16 byte fully-associative lines

- One line for CPU instructions

- · One line for CPU data

- Two lines for peripheral data

- 16-byte parallel memory fetch

- Configurable predictive prefetch

- Error detection and correction

A simplified block diagram of the Prefetch module is shown in Figure 9-1.

### FIGURE 9-1: PREFETCH MODULE BLOCK DIAGRAM

# TABLE 12-22: PERIPHERAL PIN SELECT INPUT REGISTER MAP (CONTINUED)

| sse                         |                      |           |       |       |       |       |       |       |      | E    | Bits |      |      |      |            |        |          |      |            |

|-----------------------------|----------------------|-----------|-------|-------|-------|-------|-------|-------|------|------|------|------|------|------|------------|--------|----------|------|------------|

| Virtual Address<br>(BF80_#) | Register<br>Name     | Bit Range | 31/15 | 30/14 | 29/13 | 28/12 | 27/11 | 26/10 | 25/9 | 24/8 | 23/7 | 22/6 | 21/5 | 20/4 | 19/3       | 18/2   | 17/1     | 16/0 | All Resets |

| 14DC                        | SS6R <sup>(1)</sup>  | 31:16     | _     | —     | _     |       | —     | —     | —    |      |      | —    |      | —    |            | —      |          |      | 0000       |

| 14DC                        | 220K. /              | 15:0      | _     | —     | _     |       | —     | -     | —    |      |      | —    | —    | —    |            | SS6R   | <3:0>    |      | 0000       |

| 14E0                        | C1RXR <sup>(2)</sup> | 31:16     |       | —     | -     | _     | _     | _     | _    | _    | _    | _    | _    | —    | _          | _      | _        | -    | 0000       |

| 14E0                        | CIRAR'               | 15:0      |       | —     | -     | _     | _     | _     | _    | _    | _    | _    | _    | —    |            | C1RX   | R<3:0>   |      | 0000       |

| 14E4                        | C2RXR <sup>(2)</sup> | 31:16     |       | —     | _     | _     | _     | _     | _    | _    | _    | —    | _    | _    | _          | _      | _        | -    | 0000       |

| 14⊏4                        | CZRAR <sup>V</sup>   | 15:0      |       | —     | _     | _     | _     | _     | _    | _    | _    | —    | _    | _    | C2RXR<3:0> |        | 0000     |      |            |

| 1450                        | REFCLKI1R            | 31:16     |       | —     | _     | _     | _     | _     | _    | _    | _    | —    | _    | —    | _          | _      | _        | -    | 0000       |

| 14E8                        | REFULKIIR            | 15:0      |       | —     | _     | _     | _     | _     | _    | _    | _    | —    | _    | —    |            | REFCLK | l1R<3:0> |      | 0000       |

| 14F0                        | REFCLKI3R            | 31:16     |       | —     | _     | _     | _     | _     | _    | _    | _    | —    | _    | —    | _          | _      | _        | -    | 0000       |

| 14F0                        | REFULNISK            | 15:0      |       | —     | _     | _     | _     | _     | _    | _    | _    | —    | _    | —    |            | REFCLK | l3R<3:0> |      | 0000       |

| 14F4                        | REFCLKI4R            | 31:16     | -     | —     | -     | _     | —     | _     | _    | _    | _    | _    | —    | —    | —          | _      | _        | -    | 0000       |

| 1464                        | KEFULKI4K            | 15:0      | _     | —     | _     |       | _     | -     | —    |      |      | —    | _    | -    |            | REFCLK | l4R<3:0> |      | 0000       |

Legend: x = unknown value on Reset; - = unimplemented, read as '0'. Reset values are shown in hexadecimal.

**Note 1:** This register is not available on 64-pin devices.

2: This register is not available on devices without a CAN module.

| REGISTE   |                                                              | SPI CONTROL REGISTER (CONTINUED)                                                                               |  |  |  |  |  |  |  |

|-----------|--------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------|--|--|--|--|--|--|--|

| bit 17    |                                                              | lse Edge Select bit (Framed SPI mode only)                                                                     |  |  |  |  |  |  |  |

|           |                                                              | tion pulse coincides with the first bit clock                                                                  |  |  |  |  |  |  |  |

|           | 0 = Frame synchronization pulse precedes the first bit clock |                                                                                                                |  |  |  |  |  |  |  |

| bit 16    | ENHBUF: Enhanced Buffer Enable bit <sup>(1)</sup>            |                                                                                                                |  |  |  |  |  |  |  |

|           | 1 = Enhanced Buffer me                                       |                                                                                                                |  |  |  |  |  |  |  |

|           | 0 = Enhanced Buffer me                                       |                                                                                                                |  |  |  |  |  |  |  |

| bit 15    | <b>ON:</b> SPI/I <sup>2</sup> S Module On                    |                                                                                                                |  |  |  |  |  |  |  |

|           | $1 = SPI/I^2S$ module is e<br>$0 = SPI/I^2S$ module is c     |                                                                                                                |  |  |  |  |  |  |  |

| 1.1.4.4   |                                                              |                                                                                                                |  |  |  |  |  |  |  |

| bit 14    | Unimplemented: Read                                          |                                                                                                                |  |  |  |  |  |  |  |

| bit 13    | SIDL: Stop in Idle Mode                                      |                                                                                                                |  |  |  |  |  |  |  |

|           |                                                              | ion when CPU enters in Idle mode                                                                               |  |  |  |  |  |  |  |

| h:+ 40    | 0 = Continue operation                                       |                                                                                                                |  |  |  |  |  |  |  |

| bit 12    | DISSDO: Disable SDO                                          |                                                                                                                |  |  |  |  |  |  |  |

|           | 1 = SDOx pin is not use 0 = SDOx pin is control              | ed by the module. Pin is controlled by associated PORT register                                                |  |  |  |  |  |  |  |

| hi+ 11 10 |                                                              | -                                                                                                              |  |  |  |  |  |  |  |

| bit 11-10 | •                                                            | Bit Communication Select bits                                                                                  |  |  |  |  |  |  |  |

|           | When AUDEN = 1:                                              | Communication                                                                                                  |  |  |  |  |  |  |  |

|           | MODE32 MODE16                                                | Communication                                                                                                  |  |  |  |  |  |  |  |

|           | 1 1<br>1 0                                                   | 24-bit Data, 32-bit FIFO, 32-bit Channel/64-bit Frame<br>32-bit Data, 32-bit FIFO, 32-bit Channel/64-bit Frame |  |  |  |  |  |  |  |

|           | 0 1                                                          | 16-bit Data, 16-bit FIFO, 32-bit Channel/64-bit Frame                                                          |  |  |  |  |  |  |  |

|           | 0 0                                                          | 16-bit Data, 16-bit FIFO, 16-bit Channel/32-bit Frame                                                          |  |  |  |  |  |  |  |

|           |                                                              | · · · · · · · · · · · · · · · · · · ·                                                                          |  |  |  |  |  |  |  |

|           | When AUDEN = 0:                                              |                                                                                                                |  |  |  |  |  |  |  |

|           | MODE32 MODE16                                                | Communication                                                                                                  |  |  |  |  |  |  |  |

|           | 1 x                                                          | 32-bit                                                                                                         |  |  |  |  |  |  |  |

|           | 0 1                                                          | 16-bit                                                                                                         |  |  |  |  |  |  |  |

|           | 0 0                                                          | 8-bit                                                                                                          |  |  |  |  |  |  |  |

| bit 9     | SMP: SPI Data Input Sa                                       | ample Phase bit                                                                                                |  |  |  |  |  |  |  |

|           | Master mode (MSTEN =                                         |                                                                                                                |  |  |  |  |  |  |  |

|           |                                                              | at end of data output time                                                                                     |  |  |  |  |  |  |  |

|           | Slave mode (MSTEN =                                          | at middle of data output time                                                                                  |  |  |  |  |  |  |  |

|           |                                                              | <u>o).</u><br>hen SPI is used in Slave mode. The module always uses SMP = 0.                                   |  |  |  |  |  |  |  |

| bit 8     | CKE: SPI Clock Edge S                                        |                                                                                                                |  |  |  |  |  |  |  |

| DILO      |                                                              | changes on transition from active clock state to Idle clock state (see CKP bit)                                |  |  |  |  |  |  |  |

|           | •                                                            | changes on transition from Idle clock state to active clock state (see CKP bit)                                |  |  |  |  |  |  |  |

| bit 7     | SSEN: Slave Select En                                        |                                                                                                                |  |  |  |  |  |  |  |

|           | $1 = \overline{SSx}$ pin is used for                         |                                                                                                                |  |  |  |  |  |  |  |

|           |                                                              | for Slave mode, pin is controlled by the port function.                                                        |  |  |  |  |  |  |  |

| bit 6     | CKP: Clock Polarity Sel                                      | ect bit <sup>(3)</sup>                                                                                         |  |  |  |  |  |  |  |

|           |                                                              | s a high level; active state is a low level                                                                    |  |  |  |  |  |  |  |

|           | 0 = Idle state for clock                                     | s a low level; active state is a high level                                                                    |  |  |  |  |  |  |  |

|           |                                                              |                                                                                                                |  |  |  |  |  |  |  |

| Note 1:   | •                                                            | tten when the ON bit = 0. Refer to <b>Section 37.0 "Electrical Characteristics"</b> for                        |  |  |  |  |  |  |  |

| 0         | maximum clock frequer                                        |                                                                                                                |  |  |  |  |  |  |  |

| 2:        | mode (FRMEN = 1).                                            | ne Framed SPI mode. The user should program this bit to '0' for the Framed SPI                                 |  |  |  |  |  |  |  |

| э.        | . ,                                                          | SPI/I <sup>2</sup> S module functions as if the CKP bit is equal to '1', regardless of the actual              |  |  |  |  |  |  |  |

| 3:        | value of the CKP bit.                                        | Single of the difference of the the one of the equal to $\pm$ , regardless of the actual                       |  |  |  |  |  |  |  |

| 4:        |                                                              | acy compatibility and is superseded by PPS functionality on these devices (see                                 |  |  |  |  |  |  |  |

| 7.        |                                                              | ral Pin Select (PPS)" for more information).                                                                   |  |  |  |  |  |  |  |

|           |                                                              |                                                                                                                |  |  |  |  |  |  |  |

# 21.0 INTER-INTEGRATED CIRCUIT (I<sup>2</sup>C)

Note: This data sheet summarizes the features of the PIC32MZ EF family of devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to Section 24. "Inter-Integrated Circuit (I<sup>2</sup>C)" (DS60001116) "PIC32 Family Reference the in Manual", which is available from the Microchip web site (www.microchip.com/ PIC32).

The I<sup>2</sup>C module provides complete hardware support for both Slave and Multi-Master modes of the I<sup>2</sup>C serial communication standard.

Each I<sup>2</sup>C module has a 2-pin interface:

- SCLx pin is clock

- SDAx pin is data

Each I<sup>2</sup>C module offers the following key features:

- I<sup>2</sup>C interface supporting both master and slave operation

- I<sup>2</sup>C Slave mode supports 7-bit and 10-bit addressing

- I<sup>2</sup>C Master mode supports 7-bit and 10-bit addressing

- I<sup>2</sup>C port allows bidirectional transfers between master and slaves

- Serial clock synchronization for the I<sup>2</sup>C port can be used as a handshake mechanism to suspend and resume serial transfer (SCLREL control)

- I<sup>2</sup>C supports multi-master operation; detects bus collision and arbitrates accordingly

- Provides support for address bit masking

- SMBus support

Figure 21-1 illustrates the I<sup>2</sup>C module block diagram.

## REGISTER 26-5: CESTAT: CRYPTO ENGINE STATUS REGISTER (CONTINUED)

bit 16 ACTIVE: Buffer Descriptor Processor Status bit

- 1 = BDP is active

- 0 = BDP is idle

- bit 15-0 BDCTRL<15:0>: Descriptor Control Word Status bits

These bits contain the Control Word for the current Buffer Descriptor.

| REGISTER 28-6: | ADCIMCON2: ADC INPUT MODE CONTROL REGISTER 2 (CONTINUED) |

|----------------|----------------------------------------------------------|

|----------------|----------------------------------------------------------|

| bit 6 | SIGN19: AN19 Signed Data Mode bit <sup>(1)</sup> |

|-------|--------------------------------------------------|

|       | 1 = AN19 is using Signed Data mode               |

|       | 0 = AN19 is using Unsigned Data mode             |

| bit 5 | DIFF18: AN18 Mode bit                            |

|       | 1 = AN18 is using Differential mode              |

|       | 0 = AN18 is using Single-ended mode              |

| bit 4 | SIGN18: AN18 Signed Data Mode bit                |

|       | 1 = AN18 is using Signed Data mode               |

|       | 0 = AN18 is using Unsigned Data mode             |

| bit 3 | DIFF17: AN17 Mode bit                            |

|       | 1 = AN17 is using Differential mode              |

|       | 0 = AN17 is using Single-ended mode              |

| bit 2 | SIGN17: AN17 Signed Data Mode bit                |

|       | 1 = AN17 is using Signed Data mode               |

|       | 0 = AN17 is using Unsigned Data mode             |

| bit 1 | DIFF16: AN16 Mode bit                            |

|       | 1 = AN16 is using Differential mode              |

|       | 0 = AN16 is using Single-ended mode              |

| bit 0 | SIGN16: AN16 Signed Data Mode bit                |

|       | 1 = AN16 is using Signed Data mode               |

|       | 0 = AN16 is using Unsigned Data mode             |

|       |                                                  |

Note 1: This bit is not available on 64-pin devices.

### REGISTER 28-32: ADCANCON: ADC ANALOG WARM-UP CONTROL REGISTER (CONTINUED)

- bit 7 ANEN7: Shared ADC (ADC7) Analog and Bias Circuitry Enable bit

- 1 = Analog and bias circuitry enabled. Once the analog and bias circuit is enabled, the ADC module needs a warm-up time, as defined by the WKUPCLKCNT<3:0> bits.

- 0 = Analog and bias circuitry disabled

- bit 5-6 Unimplemented: Read as '0'

- bit 4-0 **ANEN4: ANEN0:** ADC4-ADC0 Analog and Bias Circuitry Enable bits

- 1 = Analog and bias circuitry enabled. Once the analog and bias circuit is enabled, the ADC module needs a warm-up time, as defined by the WKUPCLKCNT<3:0> bits.

- 0 = Analog and bias circuitry disabled

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |  |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|--|

| 31:24        | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |

|              | FLTEN19           | MSEL19<1:0>       |                   | FSEL19<4:0>       |                   |                   |                  |                  |  |

| 00.40        | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |

| 23:16        | FLTEN18           | MSEL18<1:0>       |                   | FSEL18<4:0>       |                   |                   |                  |                  |  |

| 15:8         | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |

|              | FLTEN17           | MSEL1             | 7<1:0>            |                   | I                 | SEL17<4:0>        | >                |                  |  |

| 7:0          | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |

|              | FLTEN16           | MSEL16<1:0>       |                   |                   |                   | SEL16<4:0>        | FSEL16<4:0>      |                  |  |

## REGISTER 29-14: CIFLTCON4: CAN FILTER CONTROL REGISTER 4

### Legend:

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, re | ead as '0'         |

|-------------------|------------------|---------------------------|--------------------|

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared      | x = Bit is unknown |

| bit 31    | FLTEN19: Filter 19 Enable bit                                      |

|-----------|--------------------------------------------------------------------|

|           | 1 = Filter is enabled                                              |

|           | 0 = Filter is disabled                                             |

| bit 30-29 | MSEL19<1:0>: Filter 19 Mask Select bits                            |

|           | 11 = Acceptance Mask 3 selected                                    |

|           | 10 = Acceptance Mask 2 selected                                    |

|           | 01 = Acceptance Mask 1 selected<br>00 = Acceptance Mask 0 selected |

| bit 28-24 | FSEL19<4:0>: FIFO Selection bits                                   |

|           | 11111 = Message matching filter is stored in FIFO buffer 31        |

|           | 11110 = Message matching filter is stored in FIFO buffer 30        |

|           | •                                                                  |

|           | •                                                                  |

|           | •                                                                  |

|           | 00001 = Message matching filter is stored in FIFO buffer 1         |

|           | 00000 = Message matching filter is stored in FIFO buffer 0         |

| bit 23    | FLTEN18: Filter 18 Enable bit                                      |

|           | 1 = Filter is enabled                                              |

| 1 1 00 04 | 0 = Filter is disabled                                             |

| bit 22-21 | MSEL18<1:0>: Filter 18 Mask Select bits                            |

|           | 11 = Acceptance Mask 3 selected<br>10 = Acceptance Mask 2 selected |

|           | 01 = Acceptance Mask 1 selected                                    |

|           | 00 = Acceptance Mask 0 selected                                    |

| bit 20-16 | FSEL18<4:0>: FIFO Selection bits                                   |

|           | 11111 = Message matching filter is stored in FIFO buffer 31        |

|           | 11110 = Message matching filter is stored in FIFO buffer 30        |

|           | •                                                                  |

|           | •                                                                  |

|           | •                                                                  |

|           | 00001 = Message matching filter is stored in FIFO buffer 1         |

|           | 00000 = Message matching filter is stored in FIFO buffer 0         |

|           |                                                                    |

Note: The bits in this register can only be modified if the corresponding filter enable (FLTENn) bit is '0'.

|              |                   | t                 |                   |                   |                   |                   | -                | 1                |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |

| 04-04        | R/W-x             | R/W-x             | R/W-x             | R/W-x             | R/W-x             | R/W-x             | R/W-x            | R/W-x            |

| 31:24        | SID<10:3>         |                   |                   |                   |                   |                   |                  |                  |

| 22:46        | R/W-x             | R/W-x             | R/W-x             | U-0               | R/W-0             | U-0               | R/W-x            | R/W-x            |

| 23:16        | SID<2:0>          |                   |                   | _                 | EXID              | —                 | - EID<17:16>     |                  |

| 45.0         | R/W-x             | R/W-x             | R/W-x             | R/W-x             | R/W-x             | R/W-x             | R/W-x            | R/W-x            |

| 15:8         | EID<15:8>         |                   |                   |                   |                   |                   |                  |                  |

| 7:0          | R/W-x             | R/W-x             | R/W-x             | R/W-x             | R/W-x             | R/W-x             | R/W-x            | R/W-x            |

|              | EID<7:0>          |                   |                   |                   |                   |                   |                  |                  |

### **REGISTER 29-18:** CiRXFn: CAN ACCEPTANCE FILTER 'n' REGISTER 7 ('n' = 0-31)

### Legend:

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, r | ead as '0'         |

|-------------------|------------------|--------------------------|--------------------|

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared     | x = Bit is unknown |

bit 31-21 SID<10:0>: Standard Identifier bits

- 1 = Message address bit SIDx must be '1' to match filter

- 0 = Message address bit SIDx must be '0' to match filter

- bit 20 Unimplemented: Read as '0'

- bit 19 **EXID:** Extended Identifier Enable bits

- 1 = Match only messages with extended identifier addresses

- 0 = Match only messages with standard identifier addresses

- bit 18 Unimplemented: Read as '0'

- bit 17-0 EID<17:0>: Extended Identifier bits

- 1 = Message address bit EIDx must be '1' to match filter

- 0 = Message address bit EIDx must be '0' to match filter

**Note:** This register can only be modified when the filter is disabled (FLTENn = 0).

NOTES:

## 36.2 MPLAB XC Compilers

The MPLAB XC Compilers are complete ANSI C compilers for all of Microchip's 8, 16, and 32-bit MCU and DSC devices. These compilers provide powerful integration capabilities, superior code optimization and ease of use. MPLAB XC Compilers run on Windows, Linux or MAC OS X.

For easy source level debugging, the compilers provide debug information that is optimized to the MPLAB X IDE.

The free MPLAB XC Compiler editions support all devices and commands, with no time or memory restrictions, and offer sufficient code optimization for most applications.

MPLAB XC Compilers include an assembler, linker and utilities. The assembler generates relocatable object files that can then be archived or linked with other relocatable object files and archives to create an executable file. MPLAB XC Compiler uses the assembler to produce its object file. Notable features of the assembler include:

- Support for the entire device instruction set

- Support for fixed-point and floating-point data

- Command-line interface

- · Rich directive set

- Flexible macro language

- MPLAB X IDE compatibility

## 36.3 MPASM Assembler

The MPASM Assembler is a full-featured, universal macro assembler for PIC10/12/16/18 MCUs.

The MPASM Assembler generates relocatable object files for the MPLINK Object Linker, Intel<sup>®</sup> standard HEX files, MAP files to detail memory usage and symbol reference, absolute LST files that contain source lines and generated machine code, and COFF files for debugging.

The MPASM Assembler features include:

- Integration into MPLAB X IDE projects

- User-defined macros to streamline assembly code

- Conditional assembly for multipurpose source files

- Directives that allow complete control over the assembly process

## 36.4 MPLINK Object Linker/ MPLIB Object Librarian

The MPLINK Object Linker combines relocatable objects created by the MPASM Assembler. It can link relocatable objects from precompiled libraries, using directives from a linker script.

The MPLIB Object Librarian manages the creation and modification of library files of precompiled code. When a routine from a library is called from a source file, only the modules that contain that routine will be linked in with the application. This allows large libraries to be used efficiently in many different applications.

The object linker/library features include:

- Efficient linking of single libraries instead of many smaller files

- Enhanced code maintainability by grouping related modules together

- Flexible creation of libraries with easy module listing, replacement, deletion and extraction

# 36.5 MPLAB Assembler, Linker and Librarian for Various Device Families

MPLAB Assembler produces relocatable machine code from symbolic assembly language for PIC24, PIC32 and dsPIC DSC devices. MPLAB XC Compiler uses the assembler to produce its object file. The assembler generates relocatable object files that can then be archived or linked with other relocatable object files and archives to create an executable file. Notable features of the assembler include:

- · Support for the entire device instruction set

- · Support for fixed-point and floating-point data

- Command-line interface

- · Rich directive set

- Flexible macro language

- MPLAB X IDE compatibility

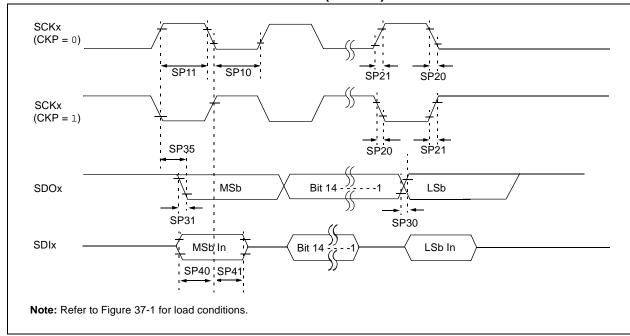

## FIGURE 37-10: SPIX MODULE MASTER MODE (CKE = 0) TIMING CHARACTERISTICS

# 39.0 252 MHz ELECTRICAL CHARACTERISTICS

This section provides an overview of the PIC32MZ EF electrical characteristics for devices running at 252 MHz. Additional information will be provided in future revisions of this document as it becomes available.

The specifications for 252 MHz are identical to those shown in **37.0** "Electrical Characteristics" including absolute maximum ratings, with the exception of the parameters listed in this chapter.

Parameters in this chapter begin with the letter "M", which denotes 252 MHz operation. For example, parameter DC27a in **37.0** "Electrical Characteristics", is the up to 200 MHz operation equivalent for MDC27a.

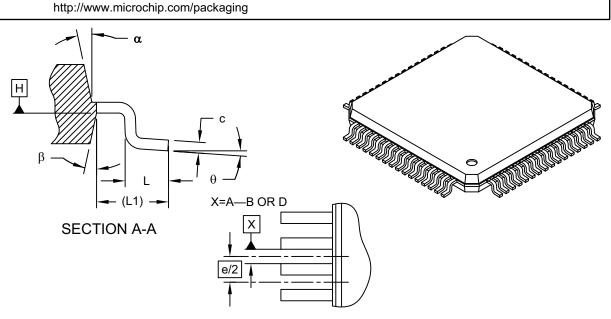

## 64-Lead Plastic Thin Quad Flatpack (PT)-10x10x1 mm Body, 2.00 mm Footprint [TQFP]

For the most current package drawings, please see the Microchip Packaging Specification located at

DETAIL 1

|                          | Units     | 1         | MILLIMETER | S    |  |

|--------------------------|-----------|-----------|------------|------|--|

| Dimensi                  | on Limits | MIN       | NOM        | MAX  |  |

| Number of Leads          | Ν         |           | 64         |      |  |

| Lead Pitch               | е         | 0.50 BSC  |            |      |  |

| Overall Height           | А         | -         | -          | 1.20 |  |

| Molded Package Thickness | A2        | 0.95      | 1.00       | 1.05 |  |

| Standoff                 | A1        | 0.05      | -          | 0.15 |  |

| Foot Length              | L         | 0.45      | 0.60       | 0.75 |  |

| Footprint                | L1        | 1.00 REF  |            |      |  |

| Foot Angle               | ¢         | 0°        | 3.5°       | 7°   |  |

| Overall Width            | E         | 12.00 BSC |            |      |  |

| Overall Length           | D         | 12.00 BSC |            |      |  |

| Molded Package Width     | E1        | 10.00 BSC |            |      |  |

| Molded Package Length    | D1        | 10.00 BSC |            |      |  |

| Lead Thickness           | С         | 0.09      | -          | 0.20 |  |

| Lead Width               | b         | 0.17      | 0.22       | 0.27 |  |

| Mold Draft Angle Top     | α         | 11°       | 12°        | 13°  |  |

| Mold Draft Angle Bottom  | β         | 11°       | 12°        | 13°  |  |

Notes:

Note:

1. Pin 1 visual index feature may vary, but must be located within the hatched area.

2. Chamfers at corners are optional; size may vary.

3. Dimensions D1 and E1 do not include mold flash or protrusions. Mold flash or protrusions shall not exceed 0.25mm per side.

4. Dimensioning and tolerancing per ASME Y14.5M

BSC: Basic Dimension. Theoretically exact value shown without tolerances.

REF: Reference Dimension, usually without tolerance, for information purposes only.

Microchip Technology Drawing C04-085C Sheet 2 of 2

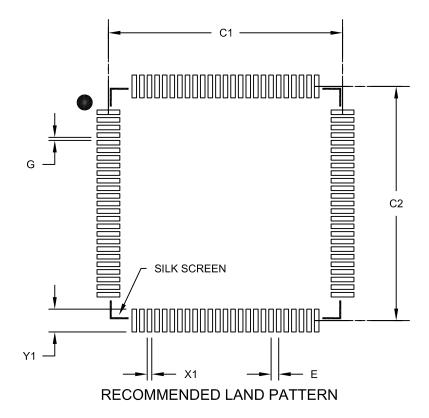

100-Lead Plastic Thin Quad Flatpack (PF) - 14x14x1 mm Body 2.00 mm Footprint [TQFP]

**Note:** For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

|                           | Units            | Ν    | <b><i>MILLIMETER</i></b> | S    |

|---------------------------|------------------|------|--------------------------|------|

| Dimensior                 | Dimension Limits |      | NOM                      | MAX  |

| Contact Pitch             |                  |      | 0.50 BSC                 |      |

| Contact Pad Spacing       | C1               |      | 15.40                    |      |

| Contact Pad Spacing       | C2               |      | 15.40                    |      |

| Contact Pad Width (X100)  | X1               |      |                          | 0.30 |

| Contact Pad Length (X100) | Y1               |      |                          | 1.50 |

| Distance Between Pads     | G                | 0.20 |                          |      |

Notes:

1. Dimensioning and tolerancing per ASME Y14.5M

BSC: Basic Dimension. Theoretically exact value shown without tolerances.

Microchip Technology Drawing No. C04-2110B

| Section Name                                                 | Update Description                                                                                                                                                             |

|--------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 27.0 "Random Number Generator<br>(RNG)"                      | The TRNGMODE bit was added to the RNGCON register (see Register 27-2).                                                                                                         |

| 28.0 "12-bit High-Speed                                      | The S&H Block Diagram was updated (see Figure 28-2).                                                                                                                           |

| Successive Approximation<br>Register (SAR) Analog-to-Digital | The registers, ADCTRG4 through ADCTRG8, were removed.                                                                                                                          |

| Converter (ADC)"                                             | The bit value definitions for the ADCSEL<1:0> and CONCLKDIV<5:0> bits in the ADCCON3 register were updated (see Register 28-3).                                                |

|                                                              | The bit names in the ADC Status registers (Register 28-12 and Register 28-13) were updated to match the names in the SFR summary table.                                        |

|                                                              | The ADCTRGSNS register was updated (see Register 28-26).                                                                                                                       |

|                                                              | The POR values were changed in the ADC System Configuration registers (see Register 28-34 and Register 28-35).                                                                 |

| 34.0 "Special Features"                                      | The FDBGWP bit was removed from the DEVCFG0/ADEVCFG0 registers (see Register 34-3).                                                                                            |

| 37.0 "Electrical Characteristics"                            | V-Temp (-40°C $\leq$ TA $\leq$ +105°C) information was removed from all tables.                                                                                                |

|                                                              | The operating conditions voltage range was updated in the Absolute Maximum Ratings and in all tables to: 2.1V to 3.6V.                                                         |

|                                                              | Notes on Maximum value operating conditions were added to the Operating,<br>Idle, and Power-Down Current tables (see Table 37-6, Table 37-7, and<br>Table 37-8, respectively). |

|                                                              | The conditions for System Timing Requirement parameters OS55a and OS55b were updated (see Table 37-18).                                                                        |

|                                                              | The Internal FRC Accuracy specifications were updated (see Table 37-20).                                                                                                       |

|                                                              | The Internal LPRC Accuracy specifications were updated (see Table 37-21).                                                                                                      |

|                                                              | The ADC Module Specifications were updated (see Table 37-38).                                                                                                                  |

|                                                              | The Analog-to-Digital Conversion Timing Requirements were updated (see Table 37-39).                                                                                           |

| Appendix B: "Migrating from<br>PIC32MZ EC to PIC32MZ EF"     | This appendix was added, which provides an overview of considerations for migrating from PIC32MZ EC devices to the PIC32MZ EF family of devices.                               |

|                                                              |                                                                                                                                                                                |

# TABLE C-1: MAJOR SECTION UPDATES (CONTINUED)